Professional Program Session Record

## New Developments in Programmable Logic

Electronics Show & Convention/September 14-1 Convention Center Marriott Hotel Hilton Inn at the Park Anaheim, California

#### A UNIVERSAL LANGUAGE FOR PROGRAMMABLE LOGIC

Robert Osann Assisted Technology, Inc. 2381 Zanker Road, Suite 150 San Jose, CA 95131

#### INTRODUCTION

During this year we have seen Programmable Logic Devices (PLDs) enter a very significant growth phase. A number of major semiconductor companies have entered this rapidly expanding marketplace in order to second-source existing products and provide proprietary designs. Competition has greatly increased causing a corresponding decrease in prices. This era bears many similarities to that of the micro-This era bears many processor around 1975. It took years, however, before the need for high level languages (by definition, universal) and universal microprocessor development systems became painfully apparent. These lessons must be applied if PLDs are to fulfill their potential and emerge as the most significant advance in Systems Design of the early 80's.

In recent years, different families of PLD's (PALs, FPLAs, etc.) have been supported by different languages. A universal language for PLDs eliminates confusion, while increasing design flexibility and providing an upward growth path to even higher level design languages. These higher level tools will support entire sub-systems where PLDs from different families are intermixed to provide the best overall design solution. Such a growth path will be necessary if the industry is to ever reach the goal of an integrated and efficient computer-aided engineering environment. The CUPL language (pronounced "couple") is a hardware compiler specifically designed for programmable logic. As the first programmable logic. universal language of its kind it will provide the most-important first step toward the higher-level design tools of the future.

#### MAJOR CONSIDERATIONS

#### Device Independence

Device independence is the most im-portant aspect of a "universal" language and implies that a PLD source specification should not be tied to a particular PLD type or family. In practice, however, some dependent consideration must be given to pin assignment at this This is due to some point in time. devices having more product terms associated with some pins than with others. The actual specification, however, bears no mention of device type as this is only required upon invoking the compiler to create a fuse pattern for a particular device type.

Device independence is also enhanced by a pin declaration format which allows a pin to be defined as active high with the corresponding equation written in positive logic, even though the target device may have an inverting output structure. This is accomplished by the compiler's ability to perform deMorgan's Theorem and subsequently minimize the result by removing duplicate, zero, and contained product terms. Such an operation does, however, tend to use a lot of product terms. If a product term limitation arises, an appropriate error message is given.

#### Flexibility/Ease of Use

In order to accomplish universal support, a language must first gain acceptance among the engineering community. This is best accomplished by incorporating features which make the hardware engineer more productive while making his or her task less difficult. A variety of shorthand notations and macro-type features have therefore been incorporated into the language. These features reduce the amount of source code which must be written, in turn reducing the possibilities of errors. The

language is also relatively free-form and relies no more than necessary on position dependence. Another potential restriction has been removed by allowing names up to 31 significant characters in length.

Shorthand notations are provided for use in representing groups of variables, the most useful being that for a list such as:

#### [a19..12]

which is used in place of:

#### a19,a18,a17,a16,a15,a14,a13,a12

The above list may also be represented by a single variable name when the field function is utilized as in:

field addr = [a19..12];

Subsequently, "addr" can be used to represent the list of address bit names.

Since one of the most common applications for PLDs at this time is address decoding, a simple range function has been provided which will work for even binary boundaries as long as the target PLD contains a sufficient number of product terms. If the range of E4000 thru E7FFF hexadecimal were to be decoded from the field "addr" shown previously, the function would be written:

addr:[E4000..E7FFF]

where the boundaries are  $E4\emptyset\emptyset\emptyset$  (lower) and E7FFF (upper), inclusively.

A variation on, and subset of, the range function is the equality function which is expressed in general as:

variable\_field:constant\_field

This function is especially usefull in specifications for state machines as in:

where ST had been previously defined as follows:

field ST=[state\_bitØ..2]

For both the range and equality functions, constants are understood to be in hexadecimal unless it is otherwise stated that they are in octal or binary.

Probably contributing the most to ease of use are the following properties of the language: parenthetical operations and expression substitution. The distributive property A&B#A&C=A&(B#C) greatly reduces the number of names which must be typed when entering a PLD source specification if there are common subsets among groups of product terms. Expression substitution also reduces the size of equations while enhancing readability. This is accomplished by allowing a symbolic name to be used in one expression, that same symbolic name being elsewhere defined as equal to a different expression. As an example: chip\_select = inrange & strobe & !inh where. inrange = !al5 & !al3 & al2

and, strobe = memr # memw

Another feature which makes the language easier to use concerns the handling of outputs with programmable tri-state enables. If an output is to be always enabled, as is most often the case, no declaration is written. Otherwise, the enable function is used and takes the form of:

Using this function, a PLD whose output is connected to a data bus might use the following enable format:

[D7, D6, D5, D4, D3, D2, D1, DØ].oe = out\_en;

or, better yet:

[D7...Ø].oe = out\_en;

where out\_en is elsewhere defined using the expression substitution feature.

Another important feature of the CUPL language is the manner in which flip-flop related functions are handled. This is somewhat similar to the output enable function in that an extension is added to the variable name associated with the "Q" output of the flip-flop. The following is a list of the various extensions:

#### Extension Function

| .d  | d-type, "d"input  |

|-----|-------------------|

| •j  | jk-type,"j"input  |

| .k  | jk-type, "k"input |

| . 5 | set input         |

| .r  | reset input       |

| ٠P  | preset input      |

An example of the equation for the "Q" output of a D-type flip-lop would be as follows:

#### out.d = inl & (in2 # in3)

These and other features of the language will become more apparent in the application examples to be presented later.

#### Documentation

Good documentation is always important when a product enters production, but in today's fast moving engineering community with its high employee turnover rate, documentation is more important than ever. The CUPL language includes a free-form provision for comments, borrowed from high level programming languages, which takes the form:

#### /\* Comment \*/

and may be placed anywhere within the PLD source specification. Although this feature is important, engineers are not well known for their willingness to document their work. It's therefore important for a PLD language to be self-documenting wherever possible. Most of the capabilities mentioned thus far, in particular expression substitution and the range and equality functions, enhance the self-documenting aspect of the language.

Finally, the engineering environment of the future will rely on a common, integrated data base. Having a different language for each family of PLDs would make it difficult to reach this goal. A better choice is CUPL, a universal language.

#### Expandability

As the technology of digital electronics never stands still, neither should the tools of the designer who uses that technology. Eventually, support tools for PLDs will grow to the point where multiple PLDs will be programmed as the result of a single source specification. Establishing the data structures which properly support the device characteristics and design rules for all families of PLDs provides an easier growth path toward such higher level capabilities.

Key words and operators must also be considered when planning for the future. Words such as "if", "else", and "goto" are reserved for higher level languages supporting sequential machines. Operators such as "+", "\*", and "/" will be eventually supported in higher level languages in their true arithmetic sense. Other operators are therefore required to support the basic logical operations. The language utilizes a set of operators which borrow mostly from high-level software programming languages. A portion of the list is shown below:

| And                  | æ   | Add      | + |

|----------------------|-----|----------|---|

| OR                   | #   | Subtract | - |

| <b>Exclusive-O</b> R | XOR | Multiply | * |

| Assignment           | =   | Divide   | 1 |

| NOT                  | 1   |          |   |

The CUPL pre-processor will also allow a personal choice of operators without compromising the effectiveness of having a standardized set.

#### Testing Considerations

As larger quantities of PLDs are used in specific designs, testing becomes an issue of ever increasing importance. Simu ati apability will also be included to allow the designer to further test the accuracy of a source specification before a device is actually programmed. Later versions of this universal language will support testing of non-registered parts by automatically generating test vectors using variations on standard semiconductor test patterns. Registered PLDs will initially be handled by allowing the designer to create a function table of states and transitions which the compiler will convert into test vector format.

In the future, higher level versions of the language will provide a state-machine modelling capability allowing the compiler to automatically generate test vectors for registered PLDs.

#### CONCLUSION

The CUPL language, just described, does more than provide the engineer with a unified approach to PLD-based designs upon which future products may build. It also includes numerous features which make logic design easier and less error prone with results that are more understandable and therefore easier to maintain.

#### AN ADDRESS DECODING EXAMPLE

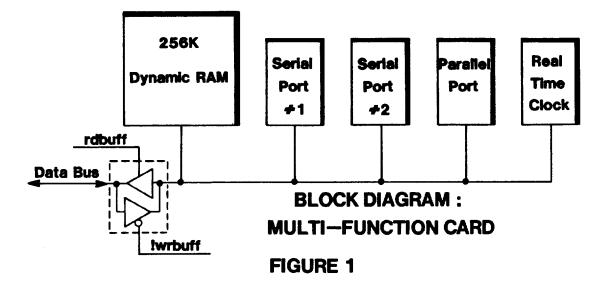

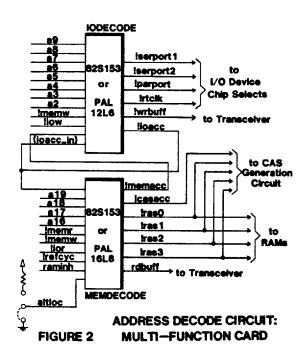

As this type of application is probably the most common for PLDs at this time, a reasonable choice for an example is the sub-system shown in Figure 1. This block diagram depicts a multi-function board similar to that found in many bus-oriented microcomputer systems. The 256K memory consists of four banks of 64K dynamic RAMS, the entire grouping being mappable to either the first or second 256K block of addressable space according to a jumper called "altloc". This memory resides on the same 8-bit bus as four I/O devices.

The two PLDs shown in Figure 2 provide the RAS control signals for the RAMs, the chip select signals for the I/O devices and the enable signals for both paths through the data bus transceiver. These devices could either be two 82S153s or a PAL16L8 and a PAL12L6 with no changes required of the source specifications.

name mdecode ; 01 ; rev 5/12/82 7 date Osann/Kahl ; designer Assisted Technology ; company \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* /\* This device generates the memory RAS signals and \*/ /\* /\* initiates the generation of CAS. It also enables \*/ the data bus transceiver for both the memory and \*/ /\* \*/ pin 1 = lioacc ; = [al9..16] ; pin [2..5] = altloc ; /\* map RAM to 40000 thru 7FFFF \*/ pin 6 = !refcyc ; /\* memory refresch cycle \*/ pin 7 pin [8,9] = ![memw,memr] ; = lior ; pin ll pin 14 = raminh ; /\* system RAM inhibit signal \*/ pin 13 = Imemacc ; /\* on-board memory being accessed \*/ = !casacc ; /\* output to CAS circuitry \*/ = ![ras0..3] ; /\*RAM RAS signals \*/ = rdbuff ; /\* transceiver enable for reads \*/ pin 12 pin [15..18] pin 19 field memaddr = [al9..16]; = memw # memr ; memreq = !raminh & !refcyc & (memaddr:[00000..3FFFF] & memacc\_eqn laltloc # memaddr:[40000..4FFFF] & altloc) ; casacc = memreq & memacc\_eqn ; rdbuff = memacc & memr # ioacc & ior ; /\* note memacc feeds-back internally \*/ memacc = memacc\_eqn ; ras3 = !raminh & memreq & !refcyc & (memaddr:[30000..3FFFF] & laltloc # memaddr:[70000..7FFFF] & altloc) # refcyc ; ras2 = !raminh & memreq & !refcyc & (memaddr:[20000..2FFFF] & laltloc # memaddr:[60000..6FFFF] & altloc) # refcyc ; rasl = !raminh & memreq & !refcyc & (memaddr:[10000..lFFFF] & laltloc # memaddr: [50000..5FFFF] & altloc) # refcyc ; ras0 = !raminh & memreq & !refcyc & (memaddr:[00000..0FFF] & laltloc # memaddr:[40000..4PFFF] & altloc) # refcyc ;

partno

pl1000153 ;

Figure 3

Partno PL00000154 ; Name IODECODE ; 01 ; Rev 5/12/82 Date Designer Osann/Kahl ; Company Assisted technology ; \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* /\* This device generates the chip select signals for the I/O \*/ \*/ /\* functions. It also enables the data bus transceiver for \*/ pin [1..8] = [a9..2] ; pin 9 = imemw ; = liow ; pin 11 = lioacc\_in ; /\* same signal as ioacc \*/ pin 12 = Imemacc ; /\* on-board memory being accessed \*/ pin 19 = !serport1 ; /\* serial port #1 chip select \*/ = !serport2 ; /\* serial port #2 chip select \*/ = !rtclk ; /\* real-time clock chip select \*/ pin 17 pin 16 pin 15 = !parport ; /\* parallel port chip select \*/ pin 14 = lwrbuff ; /\*xceiver enable for write cycles \*/ = lioacc ; /\* on-board I/O being accessed \*/ pin 18 pin 13 field ioaddr = [a9..2];serportl\_eqn \*/ = ioaddr:[3F8..3FF] ; /\* I/O Address serport2\_eqn /\* \*/ = ioaddr:[100..11F] ; rtclk\_eqn Ranges \*\*\*\*/ = ioaddr:[lF4..lF7] ; /\*\*\*\*\*\*\*\*\*\* parport\_eqn wrbuff = memacc & memw # ioacc\_in & iow ; = serportl\_eqn # serport2\_eqn # rtclk\_eqn # ioacc parport\_eqn ;

= serportl\_eqn ; serportl serport2 = serport2\_eqn ; rtclk = rtclk\_eqn ; parport = parport\_eqn ;

#### Figure 4

6

Figure 3 is the source specification for the PLD named "MEMDECODE" which creates the four RAS signals according to the CPU's address range and the "altloc" jumper. This device also gen-erates "casacc" which signals the CAS circuitry that the appropriate CAS signals should be generated. The "memacc" signal includes no control strobes and is used by both devices for generating the buffer enables. It should be noted the "rdbuff", the transceiver enable for reads, is defined as "true" even though the pin list also defines it as true. If a PAL16L8 were used, the compiler would generate the equivalent of:

| lrdbuff | E | Imemacc | 8 | lioacc | ŧ |

|---------|---|---------|---|--------|---|

|         |   | Imemacc | 6 | lior # |   |

|         |   | Imemr   | 6 | !ioacc | # |

|         |   | !memr   | 6 | lior;  |   |

Also note that the field function has been used to define "memaddr" which is subsequently operated on by the range function.

Expression substitution is used in that "memreq" is created and then used in many of the equations. In most cases this reduces the equation size by approximately a factor of two. The expression for "memacc" is initially defined in a similar way as the intermediate variable "memacc\_eqn".

21/3

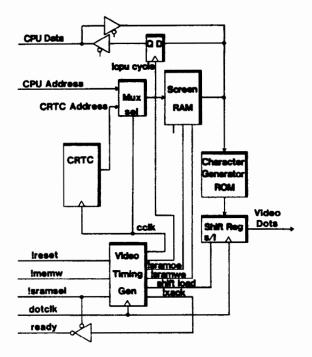

FIGURE 5- VIDEO SUBSYSTEM

This expression comprises almost all of the equation for "casacc" and is therefore used in the "casacc" expression. The variable "memacc\_eqn" is then equated to "memacc", the output pin, which in turn is fed back internally to be combined with the "memr" signal in the expression for "rdbuff". Figure 4 is the source specifica-tion for the PLD "IODECODE" which generates chip selects for the I/O functions as well as the transceiver enable for CPU write cycles. Note that the equations defining the I/O chip selects are first defined as intermediate variables (as in "serportl\_eqn = "). This allows "ioacc" to be defined in terms of these variables thereby reducing the size of that expression while also making more apparent the intent of the designer. In fact, both Figures 3 and 4 utilize no comments, except in the pin list, in order to emphasize the self-documenting nature of the language.

#### A SEQUENTIAL MACHINE EXAMPLE

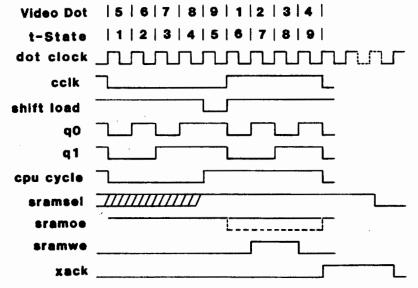

A common application for a simple state machine exists in CRT display circuits where the video timing generator also arbitrates access to the screen RAM between the CPU and the CRT controller chip. The circuit of Figure 5 represents such an application. In this example the screen RAM is fast enough that two accesses may be made during one complete cycle of the charac-ter clock ("cclk"). This is more obvious from the timing diagram of Figure 6. CRT controller read cycles from the screen RAM are always made during the period where "cclk" in Figure 6 is low. CPU accesses are made only while "cclk" is high.

#### FIGURE 6- VIDEO GENERATOR TIMING DIAGRAM

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Partno<br>Name<br>Date<br>Revision<br>Designer<br>Company                                                                                                                                                                                              | PL0000257;<br>VIDTIM;<br>4/20/82;<br>03;<br>R. Osann;<br>Assisted Technology, Inc.;                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>/* character clock a</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nd screen Shif<br>he CPU and CR                                                                                                                                                                                                                        | **************************************                                                                                                                                                                                                                                                                   |

| pin 4       = !sra         pin 5       = !men         pin [18,19]       = ![q]         pin 17       = !cpu         pin 16       = shif         pin 15       = cclk         pin 14       = !sra         pin 13       = !sra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <pre>msel ; /* CPU w ; ,q0] ; /* stat _cycle ; /* Ci t_load ; /* Ci .; /* CRTC cha moe ; /* scree mwe ; /* scree k ; /* transfe</pre>                                                                                                                  | m reset signal*/<br>access to screen RAM */<br>te variable bits */<br>PU cycle where VIDTIM<br>erforms arbitration */<br>hift/Load signal to video S/R */<br>aracter clock */<br>en RAM output enable */<br>en RAM write enable */<br>er acknowledge signal, used for<br>g system ready signal active */ |

| $\begin{array}{rcl} t2 & = q(\\ t3 & = 1q(\\ t4 & = q(\\ t5 & = q(\\ t6 & = 1q(\\ t7 & = q(\\ t8 & = 1q(\\ t$ | & !ql & !ccl!         & !ql & !ccl!         & !ql & !ccl!         & ql & !ccl!         & ql & !ccl!         & ql & !ccl!         & ql & !ccl!         & lql & ccl!         & iql & ccl!         & iql & ccl!         & iql & ccl!         & iql & ccl! | <pre>k &amp; shift_load ; k &amp; shift_load ; k &amp; shift_load ; k &amp; shift_load ; k &amp; lshift_load ; k &amp; lshift_load ; k &amp; shift_load ;</pre>                                                      |

| ql.d= ireshift_load.d= i(i)cclk.d= i(i)cpu_cycle.d= ire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <pre>set &amp; (t2 # t) reset &amp; t4) ; reset &amp; (t9 #</pre>                                                                                                                                                                                      | 3 # t4 # t6 # t8) ;<br>3 # t4 # t7 # t8) ;<br>tl # t2 # t3 # t4)) ;<br>ramsel & !xack # cpu_cycle &<br>t8)) ;                                                                                                                                                                                            |

| sramwe.d = cpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _cycle & memw                                                                                                                                                                                                                                          | 4 # t9 # cpu_cycle & Imemw ;<br>& (t6 # t7) ;<br>xack & sramsel ;                                                                                                                                                                                                                                        |

Figure 7

21/3

•

The basic operation of the circuit is based around a character block that would be nine dots wide when displayed on the CRT screen. The character font normally displayed in such a block would be seven dots wide leaving two dots between characters. The timing diagram of Figure 6 shows "cclk" divided into nine states labeled "tl" thru "t9". The "shift\_load" signal occurs during state t5 and subsequently causes the shift register of Figure 5 reload during t6. The nine states (tl..9) are defined as intermediate variables in the source specification of Figure 7. This greatly reduces the overall size of the specification while making it a simple task to write equations for the generated signals directly from the timing diagram. Registered PLDs such as the PAL16R8 and 82S159 may be used here. A "d" type flip-flop structure is chosen as both types of PLDs have this capability. Remembering that for a "q" output to be active in a given t-state the corresponding "d" input must be active during the previous t-state, the timing diagram of Figure 6 provides sufficient information to write the source specification of Figure 7.

Signals "qg" and "ql" are state variable bits used in conjunction with "shift\_load" and "cclk" to create nine unique states without using any more outputs than necessary. The "sramsel" signal indicates that the CPU is attempting to access the screen RAM and, if present at the end of t4, will cause "cpu\_cycle" to become active during the second half of "cclk" as shown in Figure Also, when "sramsel" is active, the 6. buffer driving the CPU ready signal in Figure 5 is enabled allowing "xack" currently inactive, to place the CPU in a wait state. The CPU access then occurs during the time "cclk" is high with "xack" becoming active at the completion of "cpu\_cycle" thereby remov-ing the wait state. The "xack" signal then remains active until ("sramsel") becomes inactive. The output enable ("sramoe") and write enable ("sramwe") signals for the screen RAM occur as shown in Figure 6. Here a read is always performed by the CRT controller while "cclk" is low and either a read or write cycle is performed while "cclk" is high depending on the type of CPU access.

### **List File**

Cupl 1.0 Assisted Technology, Inc. Copyright (c) 1982 \$0001\$ Partno PL00000154 ; \$0002\$ Name IODECODE ; \$0003\$ 01 ; Rev \$0004\$ Date 5/12/82 ; \$0005\$ Company Assisted technology ; \$0006\$ \$0007\$ \$0008\$ /\* This device generates the chip select signals for the I/O \*/ /\* functions. It also enables the data bus transceiver for \$0009\$ \*/ /\* both memory and I/O write cycles. \$0010\$ \*/ \$0011\$ \$0012\$ \$0013\$ pin [1...8] = [a9...2];\$0014\$ pin 9 = lmemw ; \$0015\$ pin ll = liow ; \$0016\$ pin 12 = lioacc\_in ; /\* same signal as ioacc \*/ = !memacc ; /\* on-board memory being accessed \*/ \$0017\$ pin 19 \$0018\$ pin 17 = !serportl ; /\* serial port #1 chip select \*/ = !serport2 ; /\* serial port #2 chip select \*/ \$0019\$ pin 16 \$0020\$ pin 15 = !rtclk ; /\* real-time clock chip select \*/ \$0021\$ pin 14 = !parport ; /\* parallel port chip select \*/ \$0022\$ pin 18 = !wrbuff ; /\*xceiver enable for write cycles \*/ \$0023\$ pin 13 = !ioacc ; /\* on-board I/O being accessed \*/ \$0024\$ \$0025\$ = [a9..2];field ioaddr \$0026\$ \$0027\$ = ioaddr:[2F8..2FF] ; /\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* serportl\_eqn \$0028\$ = ioaddr:[3F8..3FF] ; /\* serport2\_eqn \*/ I/O Address rtclk\_eqn \$0029\$ = ioaddr:[100..11F] ; /\* \*/ Ranges /\*\*\*\*\*\*\*\*\* \$0030\$ parport\_eqn = ioaddr:[1F4..1F7] ; \$0031\$ \$0032\$ wrbuff = memacc & memw # ioacc\_in & iow ; \$0033\$ ioacc = serportl\_eqn # serport2\_eqn # rtclk\_eqn # \$0034\$ parport\_eqn ; \$0035\$ serportl = serportl\_eqn ; \$0036\$ serport2 = serport2\_eqn ; \$0037\$ rtclk = rtclk\_eqn ; \$0038\$ parport = parport\_eqn ;

| ~ | partno<br>name<br>rev<br>date<br>designer<br>company                                                | 10<br>01<br>5/  | 12/82                     | DE<br>2                                            | hnold    | bav                     |                          |                    |   | <br>Fuse Plot for<br>PAL12L6                                                                     |  |  |  |

|---|-----------------------------------------------------------------------------------------------------|-----------------|---------------------------|----------------------------------------------------|----------|-------------------------|--------------------------|--------------------|---|--------------------------------------------------------------------------------------------------|--|--|--|

|   | company                                                                                             | <b>n</b> .      | 51500                     |                                                    |          | ,91                     |                          |                    |   |                                                                                                  |  |  |  |

|   | column                                                                                              |                 | 0123                      | 4567                                               |          |                         |                          | 2222<br>0123       |   |                                                                                                  |  |  |  |

|   | row<br>row                                                                                          | -               |                           | x                                                  |          |                         |                          |                    |   | ioacc_in&iow<br>memacc&memw                                                                      |  |  |  |

|   | row                                                                                                 | 16              | -xx-                      | x                                                  | x -      | <b>x</b> –              | <b>x</b> –               | x -                |   | <br><b>!a8&amp;a9&amp;a7&amp;a6&amp;a5&amp;a4&amp;a</b> 3                                        |  |  |  |

|   | row 2                                                                                               | 24              | x - x -                   | x                                                  | x-       | x-                      | x -                      | x-                 |   | <br>a8&a9&a7&a6&a5&a4&a3                                                                         |  |  |  |

|   | row                                                                                                 | 32              | x                         | -x                                                 | -x       | -x                      |                          |                    |   | <br>a8&1a7&1a6&1a5                                                                               |  |  |  |

|   | row                                                                                                 | 40              | xx                        | x                                                  | x-       | x-                      | x-                       | -x                 | x | <br>a8&1a9&a7&a6&a5&a4&1a3&a2                                                                    |  |  |  |

| • | row<br>row                                                                                          | <b>49</b><br>50 | x<br>x - x -              | x<br>-x<br>x<br>x                                  | -x<br>x- | x -<br>-x<br>x -<br>x - | x -<br>x -<br>x -<br>x - | -x<br><br>x-<br>x- |   | <br>a8&!a9&a7&a6&a5&a4&!a3&a2<br>a8&!a7&!a6&!a5<br>a8&a9&a7&a6&a5&a4&a3<br>!a8&a9&a7&a6&a5&a4&a3 |  |  |  |

|   | pins<br>polarity                                                                                    |                 |                           | 11<br>3399<br>HLHL                                 |          |                         |                          |                    |   |                                                                                                  |  |  |  |

|   | pin:1pin:2pin:3pin:4pin:5pin:6pin:7pin:8pin:9pin:11pin:12pin:13pin:14pin:15pin:16pin:17pin:18pin:19 |                 | ioad<br>par<br>rtc<br>ser | cc_in<br>cc<br>port<br>lk<br>port2<br>port2<br>uff |          |                         |                          |                    |   |                                                                                                  |  |  |  |

| *P 00 *I *BIL- *BO AAAAA<br>*P 01 *I *BI LL *BO AAAAA<br>*P 02 *I -HHHHLH *BI *BO AAAAA<br>*P 03 *I -HHHHHH *BI *BO AA.AAAA<br>*P 04 *ILLH- *BI *BO AA.AAAA<br>*P 05 *I HLHHHHL *BI *BO AA.AAAA<br>*P 05 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 07 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 08 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 09 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 11 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 12 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 12 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 13 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 14 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 15 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 16 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 17 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 13 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 14 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 15 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 13 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 25 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 27 *I 0000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAAAAA<br>*P 27 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 26 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 27 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 0000000000 *BO AAAAA                                                                                                                                                                               | <b>*</b> PC | LLLLLL        | LLLL     |     |             |             |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|----------|-----|-------------|-------------|-------------|

| *P 02 *I -HHHHHH *BI *BO A.AAAAA<br>*P 03 *I -HHHHHHH *BI *BO AA.AAA<br>*P 04 *ILLLH *BI *BO AA.AAA<br>*P 05 *I HLHHHHH *BI *BO AAAAA<br>*P 05 *I HLHHHHHL *BI *BO AAAAA<br>*P 07 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 08 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 09 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 10 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 11 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 12 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 12 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 13 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 13 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 14 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 15 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 16 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 17 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 16 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 17 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 12 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 21 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 21 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 22 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 25 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 00000000 *BI 0000000000 *BO AAAAAAAAAAA<br>*P 29 *I 00000000                                                                                                                                                     |             |               |          | *BI | LL-         | *BO         | AAAAA       |

| *P 03 *I -HHHHHHH *BI *BO AAAAAA<br>*P 03 *ILLLH- *BI *BO AA.AAAA<br>*P 05 *I HLHHHHH *BI *BO AA.AAAA<br>*P 05 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 07 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 09 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 10 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 10 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 11 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 12 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 13 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 14 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 15 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 15 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 16 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 17 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 13 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 13 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 13 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 20 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 21 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 22 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 25 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 27 *I 0000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 28 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAAAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAAAAAAAA<br>*P 20 *I 00000000 *BI 0000000000 *BO AAAAAAAAAAAAA                                                                                                                                   | *P          | 01 *I         |          | *BI | LL          | *BO         | AAAAA       |

| *P 04 *ILLLH- *BI *BO AA.AAAA<br>*P 05 *I HLHHHHL *BI *BO AAAAAA<br>*P 06 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 07 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 09 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 10 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 11 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 12 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 13 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 13 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 14 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 15 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 16 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 17 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 20 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 21 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 22 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 25 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 00000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 19 1*I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 20 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAAAAAAAA<br>*P 21 *I *BI                                                                                                                                               | *P          | 02 *I         | -ннннгн  | *BI |             | <b>*</b> BO | A.AAAAA     |

| *P 05 *I HLHHHHL *BI *BO AAAAAA<br>*P 06 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 07 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 09 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 10 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 11 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 12 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 13 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 14 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 15 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 16 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 17 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 19 17 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 20 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 20 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 20 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 22 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 24 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 24 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 25 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 25 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 26 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAAAAAAAAAAAA<br>*P 00 *I                                                                                                                                                                           | *P          | 03 *I         | -нннннн  | *BI |             | *BO         | AAAAAA      |

| <pre>*P 06 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br/>*P 07 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br/>*P 08 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br/>*P 10 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br/>*P 11 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br/>*P 12 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br/>*P 13 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br/>*P 14 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br/>*P 15 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br/>*P 16 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br/>*P 16 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br/>*P 17 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br/>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 19 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br/>*P 19 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br/>*P 21 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br/>*P 21 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 22 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 27 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 31 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 31 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 31 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br/>*P 29 *I 00000000 *BI 0000000000 *BO</pre> | *P          | 04 *I         | LLLH-    | *BI |             | *BO         | AA.AAAA     |

| *P 07 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 08 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 09 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 10 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 11 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 12 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 13 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 14 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 15 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 16 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 17 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 18 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 19 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 20 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 21 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 22 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 23 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 24 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 23 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 24 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 25 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 24 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 25 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 26 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 27 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 29 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAAAAA<br>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 30 *I 0000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 30 *I 0000000 *BI 000000000 *BO AAAAAAAAAAAAAAAA<br>*P 30 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 31 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 30 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 30 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 09 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAAAAAAAAA<br>*P 09 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAAAAAAAAA<br>*P 00 *I *BI                                                                                                                                                                                          | *P          | 05 *I         | HLHHHHHL | *BI |             | *BO         | АААААА      |

| *P 08 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 09 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 10 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 11 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 12 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 13 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 14 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 15 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 16 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 17 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 20 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 21 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 22 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 23 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 24 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 25 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 24 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 25 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 26 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 27 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 30 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 30 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 30 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 31 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 09 *I 00000000 *BI 0000000000 *BO AAAAAAAAAAAAAAAAA<br>*P 09 *I 00000000 *BI 0000000000 *BO AAAAAAAAAAAAAAAAA                                                                                                                                           | *P          | 06 *I         | 00000000 | *BI | 0000000000  | *BO         | АААААААААА  |

| *P 09 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 10 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 11 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 12 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 13 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 15 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 15 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 16 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 16 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 17 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 20 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 21 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 22 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 25 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 27 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 27 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 00 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 00 *I 0000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 00 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 00 *I 0000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 00 *I 0000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 00 *I 0000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 00 *I 00000000 *BI 0000000000 *BO AAAAAAAAAAAAAAA                                                                                                                        | *P          | 07 *I         | 00000000 | *BI | 0000000000  | *BO         | АААААААААА  |

| *P 10 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 11 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 12 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 13 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 14 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 16 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 16 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 17 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 20 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 21 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 22 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 25 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 27 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 30 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 31 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 31 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 05 *I *BI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | *P          | 08 <b>*</b> I | 00000000 | *BI | 0000000000  | *BO         | АААААААААА  |

| <pre>*P 11 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br/>*P 12 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 13 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 14 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 15 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 16 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 17 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 20 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 21 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 22 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 25 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 25 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 27 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br/>*P 29 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 11 I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 20 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 14 *I *BI</pre>                                                                                                                       | *P          | 09 *I         | 00000000 | *BI | 0000000000  | *BO         | АААААААААА  |

| *P 12 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 13 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 14 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 15 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 16 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 17 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 20 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 21 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 22 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 25 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 27 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 27 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 30 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 31 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 19 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 19 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 19 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 19 *I 00000000 *BI 0000000000 *BO AAAAAAAAAAAAA<br>*P 19 *I 00000000 *BI 00000000000000000000000                                                                                                                                                                          | _           |               | 00000000 | *BI | 0000000000  | *BO         | АААААААААА  |

| <pre>*P 13 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br/>*P 14 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br/>*P 15 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 16 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 17 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 20 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 21 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 22 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 25 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 27 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 31 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 09 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br/>*P 19 1 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 31 *I 00000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 19 1 *I 00000000 *BI 00000000000000000000000</pre>                                                                                                                                                                                  | _           |               | 00000000 | *BI | 0000000000  | *BO         | аааааааааа  |

| *P 14 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 15 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 16 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 17 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 20 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 21 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 22 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 25 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 27 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br>*P 30 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 31 *I 00000000 *BI 0000000000 *BO AAAAAAAAAAAA<br>*P 31 *I 00000000 *BI 0000000000 *BO AAAAAAAAAAA<br>*P 31 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 31 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 10 *I 00000000 *BI 0000000000 *BO AAAAAAAAAAAAAAAA                                                                                                                                                                                  | *P          |               |          |     |             | *BO         | АААААААААА  |

| <pre>*P 15 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br/>*P 16 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br/>*P 17 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br/>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 20 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 21 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 25 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 27 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 30 *I 0000000 *BI 000000000 *BO AAAAAAAAAA<br/>*P 31 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 19 *I *BI</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _           |               |          |     |             | *BO         | алаааааааа  |

| <pre>*P 16 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br/>*P 17 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 18 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 19 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 20 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 21 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 23 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 25 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 27 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 29 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 30 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 31 *I 0000000 *BI 000000000 *BO AAAAAAAAAAAA<br/>*P 31 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br/>*P 31 *I 00000000 *BI 000000000 *BO AAAAAAAAAAAA<br/>*P 30 *I</pre>                                                                                                                                                                                                                                                                   | -           |               |          |     |             |             |             |

| *P 17 *I 0000000 *BI 00000000 *BO AAAAAAAAAA<br>*P 18 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 19 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 20 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 21 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 23 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 23 *I 0000000 *BI 00000000 *BO AAAAAAAAAAA<br>*P 24 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 25 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 26 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 27 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 28 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 30 *I 0000000 *BI 000000000 *BO AAAAAAAAAAA<br>*P 31 *I 0000000 *BI 000000000 *BO AAAAAAAAAAAA<br>*P 10 *I *BI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _           |               |          |     |             |             | ааааааааааа |