WAFERSCALE INTEGRATION, INC.

# HIGH SPEED 32K × 8 CMOS EPROM

#### **KEY FEATURES**

- Fast Access Time

45 ns

- Low Power Consumption

- DESC SMD No. 5962-86063

- EPI Processing

- Latch-Up Immunity Up to 200 mA

- FSD Protection Exceeds 2000V

- Standard EPROM Pinout

## **GENERAL DESCRIPTION**

The WS27C256F is a 32K  $\times$  8 CMOS EPROM which has been speed-enhanced to 45 ns. It is based upon WaferScale's patented CMOS Split Gate EPROM technology.

The 45 ns access time of the WS27C256F is a key parameter. Traditionally, as memory densities increase, memory access times become slower. This forces microprocessors to insert Wait States which negatively impact system throughput. Real Time applications cannot afford Wait States regardless of memory density. WSI's unique memories can keep pace with the fastest microprocessors. The combination of speed and density available in the WS27C256F enables the use of more complex and comprehensive algorithms in real time applications.

WSI's patented CMOS Split-Gate EPROM technology not only enables the development of fast and dense memory products, it also provides a higher level of Quality and Reliability. Tests have proven that WSI EPROM products program very efficiently and quickly. Also, the WSI EPROM retains its data an order of magnitude better than traditional EPROM technologies. This combination of speed, density, quality and reliability make WSI the obvious choice when selecting a non-volatile memory supplier.

The WS27C256F is configured in the JEDEC standard EPROM pin configuration. It is also easily programmed on popular EPROM programmers as well as the MagicPro™ IBM PC compatible engineering programmer offered by WSI.

#### **MODE SELECTION**

| PINS<br>MODE    | CE/<br>PGM      | ŌĒ              | V <sub>PP</sub> | V <sub>CC</sub> | OUTPUTS          |

|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|

| Read            | V <sub>IL</sub> | ٧ <sub>٤</sub>  | V <sub>CC</sub> | $v_{cc}$        | D <sub>OUT</sub> |

| Output Disable  | Х               | $V_{IH}$        | $V_{CC}$        | ٧ <sub>cc</sub> | High Z           |

| Standby         | V <sub>IH</sub> | Х               | V <sub>CC</sub> | $V_{CC}$        | High Z           |

| Program         | V <sub>IL</sub> | V <sub>IH</sub> | $V_{PP}$        | Vcc             | D <sub>IN</sub>  |

| Program Verify  | Х               | $V_{1L}$        | $V_{PP}$        | $V_{CC}$        | D <sub>OUT</sub> |

| Program Inhibit | V <sub>IH</sub> | $V_{\text{IH}}$ | $V_{PP}$        | $V_{CC}$        | High Z           |

| Signature*      | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>CC</sub> | V <sub>CC</sub> | Encoded<br>Data  |

X can be either  $V_{IL}$  or  $V_{IH}$ .

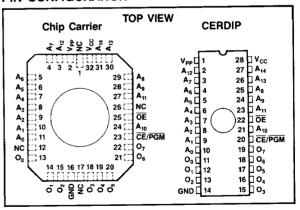

#### PIN CONFIGURATION

#### PRODUCT SELECTION GUIDE

| PARAMETER                 | WS27C256F-45 | WS27C256F-55 | WS27C256F-70 | WS27C256F-90 |

|---------------------------|--------------|--------------|--------------|--------------|

| Address Access Time (Max) | 45 ns        | 55 ns        | 70 ns        | 90 ns        |

| Chip Select Time (Max)    | 45 ns        | 55 ns        | 70 ns        | 90 ns        |

| Output Enable Time (Max)  | 25 ns        | 25 ns        | 30 ns        | 30 ns        |

<sup>\*</sup>For Signature, A $_9$  = 12V, A $_0$  is toggled, and all other addresses are at TTL low. A $_0$  = V $_{\rm IL}$  = MFGR 23H, A $_0$  = V $_{\rm HH}$  = DEVICE E0H.

## ABSOLUTE MAXIMUM RATINGS

| Storage Temperature                 | 65° to +150°C |

|-------------------------------------|---------------|

| Voltage on Any Pin with             |               |

| Respect to GND                      | 0.6V to +7V   |

| V <sub>PP</sub> with respect to GND | 0.6V to +13V  |

| ESD Protection                      | >2000V        |

\*Notice: Stresses above those listed here may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. -Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

#### **OPERATING RANGE**

| RANGE    | TEMPERATURE     | V <sub>cc</sub> |

|----------|-----------------|-----------------|

| Comm'l   | 0°C to +70°C    | +5V ± 5%        |

| Military | -55°C to +125°C | +5V ± 10%       |

## **DC READ CHARACTERISTICS** Over Operating Range with $V_{PP} = V_{CC}$ .

| SYMBOL           | PARAMETER                                     | TEST CONDITIONS                      | MIN                   | MAX             | UNITS |

|------------------|-----------------------------------------------|--------------------------------------|-----------------------|-----------------|-------|

| V <sub>OL</sub>  | Output Low Voltage                            | I <sub>OL</sub> = 2.1 mA             |                       | 0.4             | V     |

| V <sub>OH</sub>  | Output High Voltage                           | I <sub>OH</sub> = -400 μA            | 2.4                   |                 | V     |

| I <sub>SB1</sub> | V <sub>CC</sub> Standby Current CMOS          | CE = V <sub>CC</sub> ± 0.3V (Note 1) |                       | 500             | μА    |

| I <sub>SB2</sub> | V <sub>CC</sub> Standby Current TTL           | CE = V <sub>IH</sub> (Note 2)        |                       | 5               | mA    |

| 1                | V <sub>CC</sub> Active Current <sup>(3)</sup> | Commercial                           |                       | 30              | mA    |

| ICC1             | VCC Active Currents                           | Military                             |                       | 40              | mA    |

| lpp              | V <sub>PP</sub> Supply Current                | $V_{PP} = V_{CC}$                    |                       | 100             | μА    |

| $V_{PP}$         | V <sub>PP</sub> Read Voltage                  |                                      | V <sub>CC</sub> - 0.4 | V <sub>CC</sub> | V     |

| l <sub>Li</sub>  | Input Load Current                            | V <sub>IN</sub> = 5.5V or Gnd        | -10                   | 10              | μA    |

| lo               | Output Leakage Current                        | V <sub>OUT</sub> = 5.5V or Gnd       | -10                   | 10              | μА    |

**NOTES:** 1. CMOS inputs: GND  $\pm$  0.3V or  $V_{CC}$   $\pm$  0.3V.

## AC READ CHARACTERISTICS Over Operating Range with $V_{PP} = V_{CC}$ .

| PARAMETER                      | SYMBOL           | 27C256F-45 |     | 27C256F-55 |     | 27C256F-70 |     | 27C256F-90 |     |       |

|--------------------------------|------------------|------------|-----|------------|-----|------------|-----|------------|-----|-------|

| PARAMETER                      |                  | MIN        | MAX | MIN        | MAX | MIN        | MAX | MIN        | MAX | UNITS |

| Address to Output Delay        | t <sub>ACC</sub> |            | 45  |            | 55  |            | 70  |            | 90  |       |

| CE to Output Delay             | t <sub>CE</sub>  |            | 45  |            | 55  |            | 70  |            | 90  |       |

| OE to Output Delay             | t <sub>OE</sub>  |            | 25  |            | 25  |            | 30  |            | 30  | ns    |

| Output Disable to Output Float | t <sub>DF</sub>  |            | 25  |            | 25  |            | 30  |            | 30  |       |

| Address to Output Hold         | t <sub>он</sub>  | 0          |     | 0          |     | 0          |     | 0          |     |       |

<sup>2.</sup> TTL inputs:  $V_{IL} \le 0.8V$ ,  $V_{IH} \ge 2.0V$ .

<sup>3.</sup> Add 3 mA/MHz for A.C. power component.

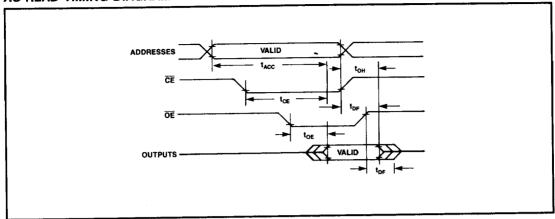

#### AC READ TIMING DIAGRAM

# CAPACITANCE(4) TA = 25°C, f = 1 MHz

| SYMBOL           | PARAMETER                   | CONDITIONS            | TYP <sup>(5)</sup> | MAX | UNITS |

|------------------|-----------------------------|-----------------------|--------------------|-----|-------|

| C <sub>IN</sub>  | Input Capacitance           | V <sub>IN</sub> = 0V  | 4                  | 6   | pF    |

| Cout             | Output Capacitance          | V <sub>OUT</sub> = 0V | 8                  | 12  | pF    |

| C <sub>VPP</sub> | V <sub>PP</sub> Capacitance | $V_{PP} = 0V$         | 18                 | 25  | pF    |

NOTES: 4. This parameter is only sampled and is not 100% tested.

5. Typical values are for  $T_A = 25^{\circ}$ C and nominal supply voltages.

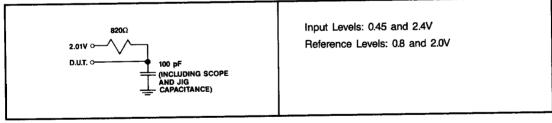

# TEST LOAD (High Impedance Test Systems)

## **TIMING LEVELS**

#### PROGRAMMING INFORMATION

**DC CHARACTERISTICS** ( $T_A$  = 25  $\pm$  5°C,  $V_{CC}$  = 5.5V  $\pm$  5%,  $V_{PP}$  = 12.5  $\pm$  0.5V)

| PARAMETER                                                                              | SYMBOLS           | MIN  | MAX                  | UNIT |

|----------------------------------------------------------------------------------------|-------------------|------|----------------------|------|

| Input Leakage Current $(V_{IN} = V_{CC} \text{ or Gnd})$                               | l <sub>LI</sub> ~ | -10  | 10                   | μА   |

| V <sub>CC</sub> Supply Current During<br>Programming Pulse (CE/PGM = V <sub>IL</sub> ) | Icc               |      | 60                   | . mA |

| V <sub>CC</sub> Supply Current                                                         | Icc               |      | 35                   | mA   |

| Input Low Level                                                                        | V <sub>IL</sub>   | -0.1 | 0.8                  | V    |

| Input High Level                                                                       | V <sub>iH</sub>   | 2.0  | V <sub>CC</sub> +0.3 | V    |

| Output Low Voltage During Verify (I <sub>OL</sub> = 16 mA)                             | V <sub>OL</sub>   |      | 0.45                 | ٧    |

| Output High Voltage During Verify $(I_{OH} = -4 \text{ mA})$                           | V <sub>OH</sub>   | 2.4  |                      | V    |

NOTES: 6. V<sub>CC</sub> must be applied either coincidentally or before V<sub>PP</sub> and removed either coincidentally or after V<sub>PP</sub>.

7. V<sub>PP</sub> must not be greater than 14 volts including overshoot. During CE/PGM = V<sub>IL</sub>, V<sub>PP</sub> must not be switched from 5 volts to 12.5 volts or vice-versa.

8. During power up the CE/PGM pin must be brought high (≽V<sub>IH</sub>) either coincident with or before power is applied to V<sub>PP</sub>.

# AC CHARACTERISTICS ( $T_A$ = 25 $\pm$ 5°C, $V_{CC}$ = 5.5V $\pm$ 5%, $V_{PP}$ = 12.5 $\pm$ 0.5V)

| PARAMETER                                | SYMBOLS                           | MIN | TYP | MAX | UNIT |

|------------------------------------------|-----------------------------------|-----|-----|-----|------|

| Address Setup Time                       | t <sub>AS</sub>                   | 2   |     |     | μs   |

| CE High to OE High                       | t <sub>сон</sub>                  | 2   |     |     | μs   |

| Output Enable Setup Time                 | toes                              | 2   |     |     | μs   |

| Data Setup Time                          | tos                               | 2   |     |     | μs   |

| Address Hold Time                        | t <sub>AH</sub>                   | 0   |     |     | μS   |

| Data Hold Time                           | t <sub>OH</sub>                   | 2   |     |     | μS   |

| Chip Disable to Output Float Delay       | t <sub>DF</sub>                   | 0   |     | 130 | ns   |

| Data Valid From Output Enable            | t <sub>OE</sub>                   |     |     | 130 | ns   |

| V <sub>PP</sub> Setup Time/CE Setup Time | t <sub>VS</sub> /t <sub>CES</sub> | 2   |     |     | μs   |

| PGM Pulse Width                          | t <sub>PW</sub>                   | 1   | 3   | 10  | ms   |

| OE Low to CE "Don't Care"                | tocx                              | 2   |     |     | μS   |

NOTE: These values are for standard programming — actual programming algorithm may use different limitations.

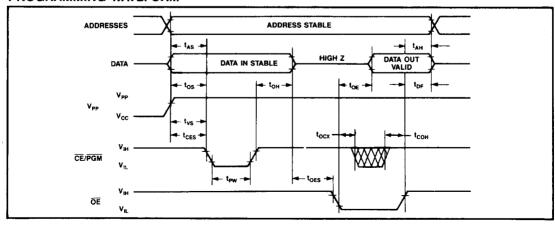

#### PROGRAMMING WAVEFORM

# PROGRAMMING/ERASURE/PROGRAMMERS

Refer to Section 5.

## ORDERING INFORMATION

| PART NUMBER     | SPEED (ns) | PACKAGE<br>TYPE     | PACKAGE<br>DRAWING | OPERATING<br>TEMPERATURE<br>RANGE | WSI<br>MANUFACTURING<br>PROCEDURE |

|-----------------|------------|---------------------|--------------------|-----------------------------------|-----------------------------------|

| WS27C256F-45D*  | 45         | 28 Pin CERDIP. 0.6" | D2                 | Comm'l                            | Standard                          |

| WS27C256F-55D   | 55         | 28 Pin CERDIP, 0.6" | D2                 | Comm'l                            | Standard                          |

| WS27C256F-70D   | 70         | 28 Pin CERDIP, 0.6" | D2                 | Comm'l                            | Standard                          |

| WS27C256F-70DMB | 70         | 28 Pin CERDIP, 0.6" | D2                 | Military                          | MIL-STD-883C                      |

| WS27C256F-90CMB | 90         | 32 Pad CLLCC        | C2                 | Military                          | MIL-STD-883C                      |

| WS27C256F-90DMB | 90         | 28 Pin CERDIP, 0.6" | D2                 | Military                          | MiL-STD-883C                      |

| WS27C256F-90LMB | 90         | 32 Pin CLDCC        | L3                 | Military                          | MIL-STD-883C                      |

<sup>\*</sup>This product is Advance Information.