# UM2364/A

# 8K × 8 NMOS ROM

- 8192 x 8 Bit organization

- Single +5 Volt Supply

- Access Times: 200/300/450 ns (max.)

- Totally static operation

- Completely TTL compatible

- 24 Pin JEDEC approved pinout

# General Description

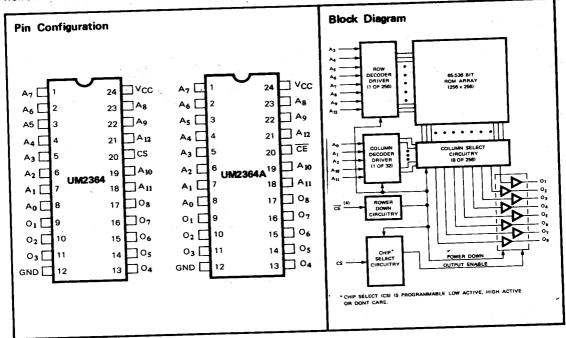

The UM2364 and UM2364A series high performance Read Only Memories are organized 8192 words by 8 bits with access times from 200 ns to 450 ns. The ROMs are designed to be compatible with all microprocessor and similar applications where high performance, large bit storage and simple interfacing are important design considerations. Both ROMs conform to the JEDEC approved pinout for 24 pin 64K ROMs.

The UM2364 offers the simplest operation (no power down.) Its programmable chip select allows two 64K ROMs to be OR-tied without external decoding.

- UM2364A Automatic power down (CE)

- UM2364 non power down version

- programmable chip select (CS)

- Three-state outputs for wire-OR expansion

- EPROMs accepted as program data input

- 2564 EPROM compatible

The UM2364A offers an automatic power down feature. Power down is controlled by the Chip Enable (CE) input. When CE goes high, the device will automatically power down and remain in a low power standby mode as long as CE remains high. This unique feature provides system level power savings as much as 90%.

Both the UM2364 and UM2364A are pin compatible with the 2564 EPROM thus eliminating the need to redesign printed circuit boards for volume mask programmed ROMs after prototyping with EPROMs.

# Absolute Maximum Ratings\*

| Temperature Under Bias             |

|------------------------------------|

| Storage Temperature                |

| Voltage on Any Pin with Respect to |

| Ground                             |

| Power Discipation                  |

# \*Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# D.C. Characteristics

$(T_A = 0^{\circ}C \text{ to } +70^{\circ}C, \ V_{CC} = +5V \pm 10\%)$

| Symbol          | Parameter                    | Min.             | Тур. | Max.            | Units    | 04141                                    |

|-----------------|------------------------------|------------------|------|-----------------|----------|------------------------------------------|

| VoH             | Output HIGH Level            | 2.4              |      |                 | Oints    | Conditions                               |

| VoL             | Output LOW Level             | <del> </del>     |      | V <sub>CC</sub> | V        | I <sub>OH</sub> = -1.0 mA                |

| VIH             | Input HIGH Level             | 2.0              |      | 0.4             | V        | $I_{OL} = 3.2 \text{ mA}$                |

| VIL             | Input LOW Level              | -0.5             |      | V <sub>CC</sub> | V        |                                          |

| ILI             | Input Leakage Current        | <del>  0.0</del> |      | 10              | - V      |                                          |

| lLO             | Output Leakage Current       |                  |      | 10              | μΑ       | $V_{IN} = 0V \text{ to } V_{CC}$         |

| Icc             | Operating Supply Current     | <del>   </del>   |      | 100             | μA<br>mA | V <sub>OUT</sub> = 0V to V <sub>CC</sub> |

| I <sub>SB</sub> | Standby Supply Current       | <u> </u>         |      | 12              | mA       | Note 1                                   |

| os              | Output Short Circuit Current | <del>   </del>   |      | 90              | mA       | Note 2<br>Note 3                         |

#### Capacitance

$(T_A = 25^{\circ}C, f = 1.0 \text{ MHz})$

| Symbol | Parameter          | Min. | Max. | Unit | Conditions            |

|--------|--------------------|------|------|------|-----------------------|

| CI     | Input Capacitance  |      | 5    | nf   | V <sub>IN</sub> = 0V  |

| Co     | Output Capacitance |      | 5    | pf   | V <sub>OUT</sub> = 0V |

Note: This parameter is periodically sampled and is not 100% tested.

# A.C. Characteristics

$(T_A = 0^{\circ}C \text{ to } +70^{\circ}C, \ V_{CC} = +5V \pm 10\%) \text{ (Note 4)}$

| Symbol          | Parameter                        | UM2364-2<br>UM2364A-2         |      | UM2364-1<br>UM2364A-1 |       | UM2364<br>UM2364A |      | Unit                                             | 0          |

|-----------------|----------------------------------|-------------------------------|------|-----------------------|-------|-------------------|------|--------------------------------------------------|------------|

|                 |                                  | Min.                          | Max. | Min.                  | Max.  | Min.              | Max. |                                                  | Conditions |

| tCYC            | Cycle Time                       | 200                           |      | 300                   |       | 450               | 1    | ns                                               |            |

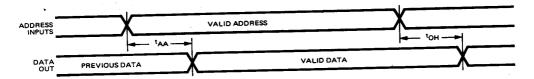

| <sup>t</sup> AA | Address Access Time              |                               | 200  | <del></del>           | 300   |                   | 450  | <del>                                     </del> |            |

| tOH             | Output Hold After Address Change | 10                            |      | 10                    | - 300 | 10                | 450  | ns                                               |            |

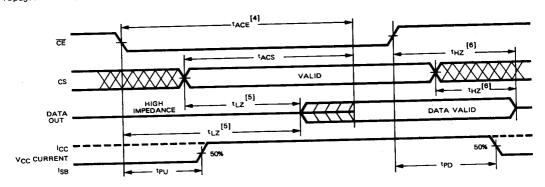

| †ACE            | Chip Enable Access Time          | +                             | 200  |                       | 200   | 10                | L    | ns                                               |            |

| tACS            | Chip Select Access Time          | <del> </del>                  | 85   |                       | 300   |                   | 450  | ns                                               | Note 5     |

| tLZ             | Ouput LOW Z Delay                |                               | 60   |                       | 100   |                   | 150  | ns                                               |            |

|                 |                                  | 10                            |      | 10                    |       | 10                |      | ns                                               | Note 6     |

| tHZ             | Output HIGH Z Delay              |                               | 85   |                       | 100   |                   | 150  | ns                                               | Note 7     |

| tPU .           | Power Up Time                    | 0                             | -    | 0                     |       |                   | 100  |                                                  |            |

| . tPD           | Power Down Time                  | <del>                  </del> |      |                       |       | 0                 |      | ns                                               | Note 5     |

| . 10            | . ottor Down Time                |                               | 85   |                       | 100   |                   | 150  | ns                                               | Note 5     |

#### Notes:

- 1. Measured with device selected and outputs unloaded.

- 2. Applies to "A" versions only and measured with  $\overline{CE} = 2.0V$ .

- 3. For a duration not to exceed one second.

- A minimum 0.5 ms time delay is required after application of V<sub>CC</sub> (+5V) before proper device operation is achieved.

- Applies to "A" versions (power down) only.

- Output low impedance delay (tLZ) is measured form  $\overline{\text{CE}}$  going low or CS going active.

- 7. Output high impedance delay (tHZ) is measured from  $\overline{\text{CE}}$  going high or CS going inactive.

#### Timing Diagrams

Propagation Delay from Address (CE LOW or CS = Active)

Propagation Delay from Chip Enable, Chip Select (Address Valid)

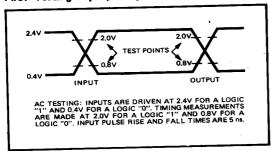

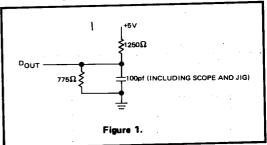

# A.C. Testing Input, Output Waveform

# A.C. Testing Load Circuit

# **Programming Instructions**

All UMC Read Only Memories (ROM) utilize computer asided techniques to manufacture and test custom bit patterns. The customer's bit pattern and address information can be supplied to UMC in a number of different ways. UMC can process customer inputs in EPROM, ROM, PROM, paper tape, and computer punched cards. Contact your UMC sales representative for complete details on each of the various data input formats.

Programming instructions are listed at the end of the Memory Section.

# Package Availability

#### Ordering Information

| Order     | Access | Operating | Standby | Package |

|-----------|--------|-----------|---------|---------|

| Number    | Time   | Current   | Current | Type    |

| UM2364    | 450 ns | 100 mA    | N.A.*   | Plastic |

| UM2364-1  | 300 ns | 100 mA    | N.A.    | Plastic |

| UM2364-2  | 200 ns | 100 mA    | N.A.    | Plastic |

| UM2364A   | 450 ns | 100 mA    | 12mA    | Plastic |

| UM2364A-1 | 300 ns | 100 mA    | 12 mA   | Plastic |

| UM2364A-2 | 200 ns | 100 mA    | 12 mA   | Plastic |

<sup>\*</sup> Not Applicable.