## Signetics

# 1024X8 STATIC READ ONLY MEMORY | 2608

2608 1

## N CHANNEL SILICON GATE MOS 2600 SERIES

#### DESCRIPTION

The 2608 is a fully decoded, static, mask programmable read-only memory. It has a capacity of 8192 bits organized 1024 X 8. The 2608 is fabricated with low threshold N-Channel silicon gate MOS technology which allows extreme ease of use with low voltage logic families such as transistor-transitor logic.

Requiring only 5 volts and ground power connections, the 2608 features a maximum access time of 650ns. Since the 2608 uses static logic throughout, no clocks are required. Four mask programmable chip selects are provided for easy word expansion. All 2608 inputs and outputs are TTL-compatible.

#### **FEATURES**

- 1024 X 8 ORGANIZATION

- STATIC OPERATION NO CLOCKS

- 400ns ACCESS TIME

- SINGLE 5V POWER SUPPLY

- TTL COMPATIBLE INPUTS AND OUTPUTS

- 400mW MAXIMUM POWER DISSIPATION

- TRI-STATE OUTPUTS

- 4 MASK PROGRAMMABLE CHIP SELECTS FOR **EASY WORD EXPANSION**

- N-CHANNEL SILICON GATE TECHNOLOGY

- STANDARD 24-PIN PACKAGE

#### MAXIMUM GUARANTEED RATINGS<sup>1</sup>

Operating Ambient Temperature

0°C to +70°C

Storage Temperature

-65°C to +150°C

All Input, Output, and Supply Voltages

with Respect to Ground Pin -0.5V to +7V

#### PART IDENTIFICATION

| TYPE  | OPERATING<br>TEMPERATURE RANGE | PACKAGE            |

|-------|--------------------------------|--------------------|

| 26081 | 0°C - +70°C                    | 24-pin ceramic dip |

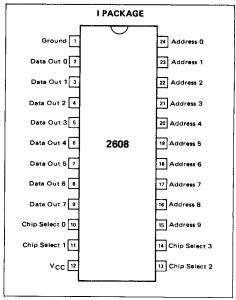

#### PIN CONFIGURATION

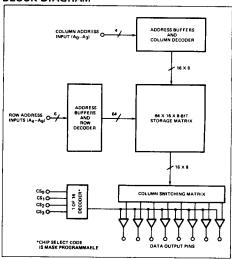

#### **BLOCK DIAGRAM**

## 1024X8 STATIC READ ONLY MEMORY = 2608

## DC OPERATING CHARACTERISTICS TA = 0°C to +70°C, V<sub>CC</sub> = +5V ±5% (Unless Otherwise Noted)<sup>3,4</sup>,5,6,7

| PARAMETER        |                        | TEST CONDITIONS                               | LIMITS |     |      |      |

|------------------|------------------------|-----------------------------------------------|--------|-----|------|------|

|                  |                        | TEST COMDITIONS                               | MIN    | TYP | MAX  | UNIT |

| I <sub>IN</sub>  | Input Load Current     | 0 ≤ V <sub>IN</sub> ≤ 5.25 V                  |        |     | 10   | μΑ   |

| I <sub>LOH</sub> | Output Leakage Current | V <sub>0</sub> = 2.4V, Device Deselected      |        |     | 10   | μΑ   |

| LOL              | Output Leakage Current | V <sub>0</sub> = 0.4V, Device Deselected      |        | i i | 10   | μΑ   |

| Icc              | Supply Current         | V <sub>CC</sub> = 5.25V, T <sub>A</sub> = 0°C |        |     | 80   | mA   |

| VIL              | Input Low Voltage      |                                               | -0.5   |     | 0.65 | V    |

| $V_{IH}$         | Input High Voltage     |                                               | 2.2    |     |      | V    |

| VOL              | Output Low Voltage     | I <sub>OL</sub> = 1.6mA                       |        |     | 0.45 | V    |

| VoH              | Output High Voltage    | I <sub>OH</sub> = -100μA                      | 2.4    |     |      | V    |

| CIN              | Input Capacitance      | V <sub>IN</sub> = 0V                          |        |     | 7.5  | pF   |

| Cout             | Output Capacitance     | V <sub>OUT</sub> ≃ 0V                         |        |     | 15   | pF   |

#### NOTES:

- Stresses above those listed under "Maximum Guaranteed Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operation sections of this specification is not implied.

- For operating at elevated temperatures the device must be derated based on a +150°C maximum junction temperature and a thermal resistance of 50°C/W junction to ambient.

- This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying any voltages larger than the rated maxima.

- 4. Parameter valid over operating temperature range unless otherwise specified.

- 5. All voltage measurements are referenced to ground.

- 6. Manufacturer reserves the right to make design and process improvements.

- 7. Typical values are at +25°C, nominal supply voltages, and nominal processing parameters.

## AC OPERATING CHARACTERISTICS TA = 0°C to +70°C, VCC = +5V ±5% (See Notes A, B & C)

| SYMBOL          | PARAMETER                     | MIN | MAX | UNITS | NOTES  |

|-----------------|-------------------------------|-----|-----|-------|--------|

| t <sub>R</sub>  | Read Cycle Time               | 650 |     | ns    |        |

| tco             | Chip Select to Output Enable  |     | 300 | ns    | Note D |

| t <sub>CD</sub> | Chip Select to Output Disable | 10  | 150 | ns    | Note D |

| $t_{A}$         | Access Time                   | 100 | 400 | ns    | Note D |

#### NOTES:

- A. Input levels swing between 0.65 volts and 2.2 volts.

- B. Input signal transition times are 20 nsec.

- C. Timing reference level is 1.5 volts.

- D. Output load is one standard TTL load plus 130pF,

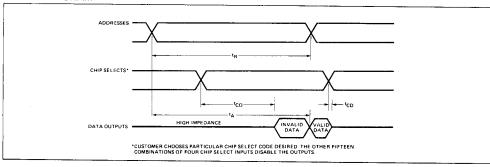

#### TIMING DIAGRAM

#### PIN DESCRIPTION

#### **ADDRESSES**

These ten TTL-compatible inputs are decoded on-chip to select one of 1024 eight-bit bytes. Since the 2608 utilizes static logic throughout, a change in addresses results in a change in data as long as the chip is selected. Access time is measured from the point where the last address input became stable. Cycle time and access time are equal in a static ROM design.

#### **CHIP SELECTS**

There are four TTL-compatible chip select inputs for the 2608. Only one combination of these four signals enables the chip. The other fifteen disable the chip. The particular enabling combination is chosen by the customer and specified on the first punched card of the customer card deck (see following page). A positive logic convention is assumed.

#### **DATA OUTPUTS**

The eight data outputs are push-pull buffers capable of driving one standard TTL-load plus a 130pF load capacitance. These outputs are placed in the high impedance state when any one of the disabling combinations of the chip select inputs is present.

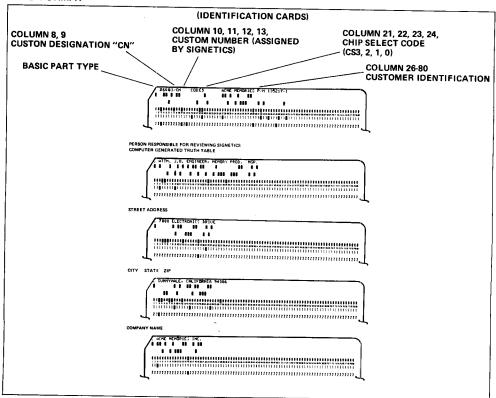

#### **CODING FORMAT**

Coding data for the 2608 may be sent to Signetics via punched cards or via a written truth table. Cards are preferred since errors are essentially eliminated.

On receipt of a card deck, Signetics will translate the card deck to a truth table using the Signetics Computer Aided Design (CAD) facility. The truth table will then be sent to the customer for final approval. On receipt of final approval, Signetics will produce masks and proceed with manufacturing.

#### **CARD FORMAT**

## 1024X8 STATIC READ ONLY MEMORY = 2608

#### **DATA CARDS**

Columns

12—75 Hexadecimal data coding 77—78 Card number (starting 01) 79—80 Total number of cards (32)

Column 12 on the first card contains the hexadecimal equivalent of bits D7 thru D4 of byte 0, while column 13 contains the hexadecimal equivalent of bits D3 thru D0. Columns 14 and 15 contain byte 1, columns 16 and 17 byte 2, and so on.

The first card contains the first 32 bytes. Columns 12 and 13 on the second card will contain byte 32 (the 33rd byte). A total of 32 cards wiff contain 1024 bytes of 8 bits.

## **BINARY TO HEXADECIMAL CONVERSION**

| BINARY<br>COMBINATION<br>D0-D3 OR D4-D7 |   |   |     | HEXADECIMAL<br>CHARACTER |

|-----------------------------------------|---|---|-----|--------------------------|

| 0                                       | 0 | 0 | 0   | 0                        |

| 0                                       | 0 | 0 | 1   | 1                        |

| 0                                       | 0 | 1 | 0   | 2                        |

| 0                                       | 0 | 1 | 1 1 | 3                        |

| 0                                       | 1 | 0 | 0   | 4                        |

| 0                                       | 1 | 0 | 1   | 5                        |

| 0                                       | 1 | 1 | 0   | 6                        |

| 0                                       | 1 | 1 | 1   | 7                        |

| 1                                       | 0 | 0 | 0   | 8                        |

| 1                                       | 0 | 0 | 1   | 9                        |

| 1                                       | 0 | 1 | 0   | Α Ι                      |

| 1                                       | 0 | 1 | 1   | В                        |

| 1                                       | 1 | 0 | 0   | С                        |

| 1                                       | 1 | 0 | 1   | D                        |

| 1                                       | 1 | 1 | 0   | E                        |

| 1                                       | 1 | 1 | 1   | F                        |