# MICROCOMPUTER RAYTHEON COMPONENTS

### **TABLE OF CONTENTS**

| Introduction         | , , , , , , , , , , , ,                                      |

|----------------------|--------------------------------------------------------------|

| Am2901               | Four-Bit Bipolar Microprocessor Slice                        |

| Am2902               | High-Speed Look-Ahead Carry Generator                        |

| Am2905               | Quad Two-Input OC Bus Transceiver With Three-State Receiver  |

| Am2906               | Quad Two-Input OC Bus Transceiver With Parity                |

| Am2907               | Quad Bus Transceiver With Three-State Receiver And Parity 29 |

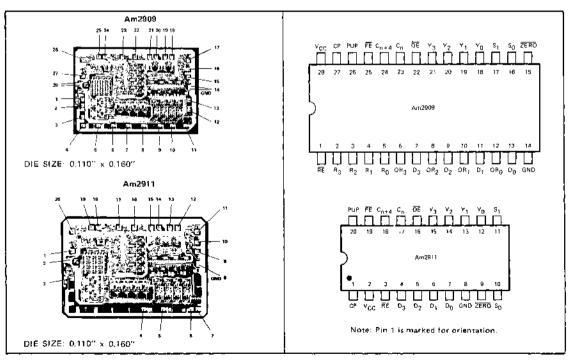

| Am2909               | Microprogram Sequencer                                       |

| Am2911               | Microprogram Sequencer                                       |

| Am2915               | Quad Three-State Bus Transceiver With Interface Logic        |

| Am2916               | Quad Three-State Bus Transceiver With Interface Logic        |

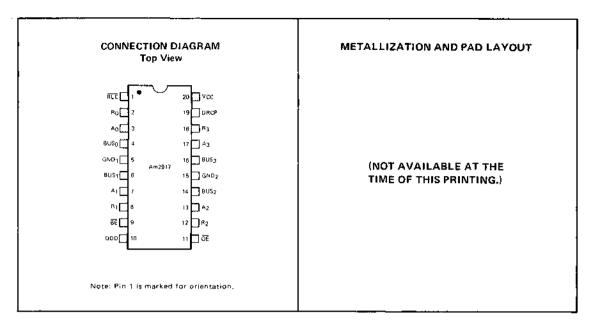

| Am2917               | Quad Three-State Bus Transceiver With Interface Logic        |

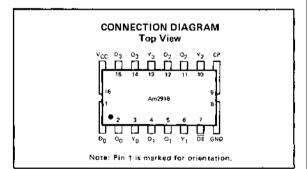

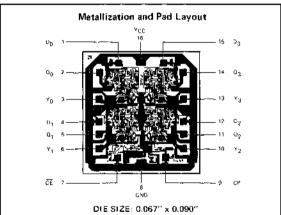

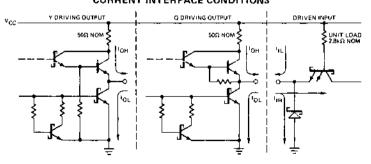

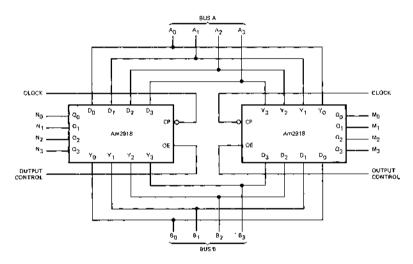

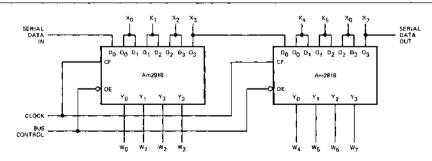

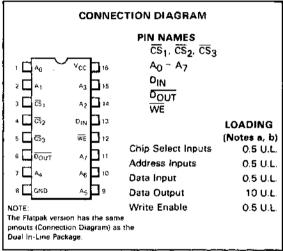

| Am2918               | Quad D Register With Standard And Three-State Outputs 62     |

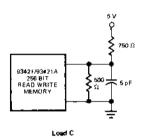

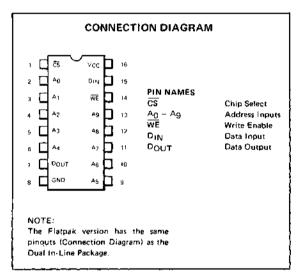

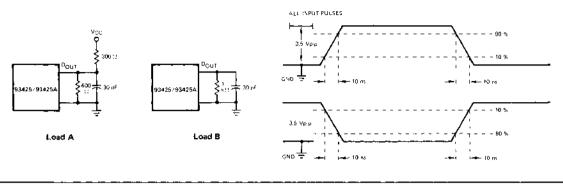

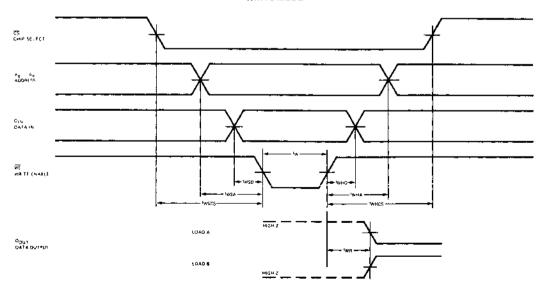

| 93411                | 256 Bit Random Access Memories                               |

| 93411A               | 256 Bit Random Access Memories                               |

| 93415                | 1024 Bit Random Access Memories                              |

| 93415A               | 1024 Bit Random Access Memories                              |

| 93421                | 256 Bit Random Access Memories                               |

| 93421A               | 256 Bit Random Access Memories                               |

| 93425                | 1024 Bit Random Access Memories                              |

| 93425A               | 1024 Bit Random Access Memories                              |

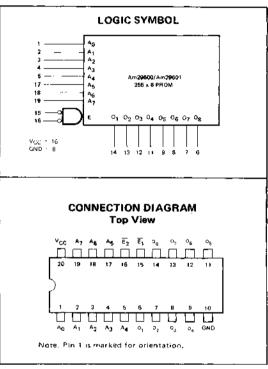

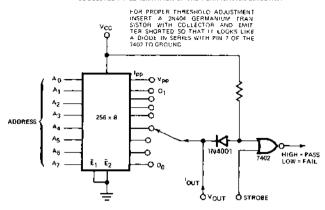

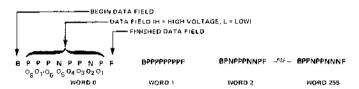

| R29600/601           | 256 Word By 8 Bit Proms                                      |

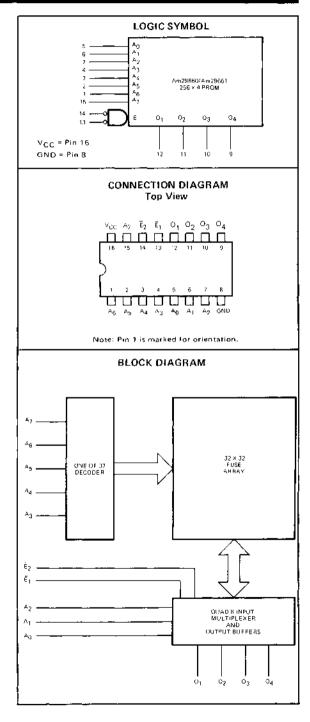

| R29660/661           | 256 Word By 4 Bit Proms                                      |

| R29690/691           | 16 IN By 8 OUT By 48 Term FPLA                               |

| Application Notes:   |                                                              |

| Using the Am29       | <b>01</b>                                                    |

| Using the Am 29      | 09                                                           |

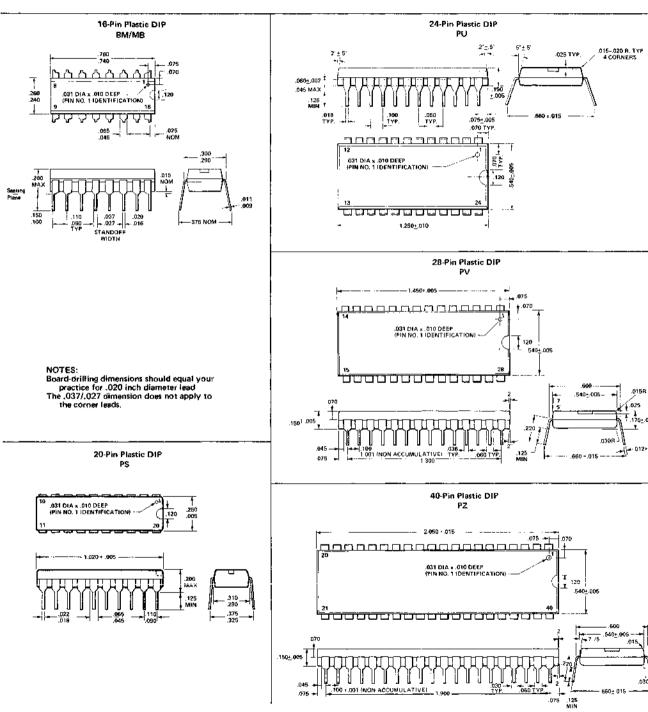

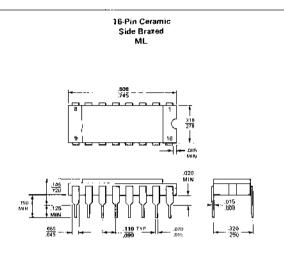

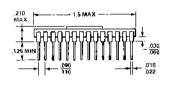

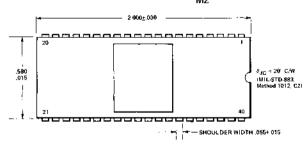

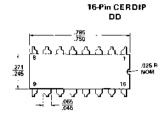

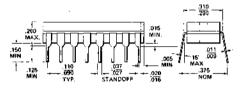

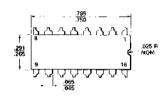

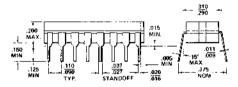

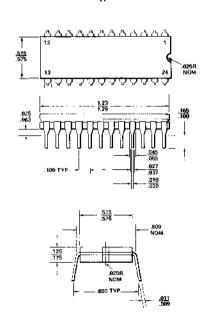

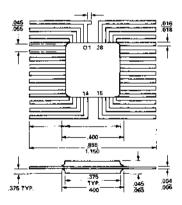

| Package Information  | n                                                            |

| Sales Offices and Di | stributors 118                                               |

#### INTRODUCTION

#### THE THIRD REVOLUTION

Over the past three years, the semiconductor industry has experienced the third revolutionary period of its relatively short history. The first of these occurred in the fifties with the introduction of mass-produceable transistors, which not only revolutionized the computer and communications industries, but also spawned a number of new companies and expanded the horizons of a number of older ones who elected to participate in this infant technology.

The second revolution occurred in the sixties when the first integrated circuits appeared. These first I.C.'s, featuring one or two gates per chip and selling for \$20 to \$30, created an even greater impact than the transistor itself. From the users' standpoint, I.C.'s allowed an order-of-magnitude increase in the complexity of the equipment they were designing (or an order-of-magnitude decrease in size, depending on the nature of that equipment) and, simultaneously, an order-of-magnitude improvement in cost-effectiveness. Coupled with this was a change in the engineering disciplines required by the user, since circuit designers, as such, were being replaced by logic designers and systems architects.

The second revolution caused a similar change in the semiconductor industry since it was now hiring the circuit designers who were leaving the end-equipment field. In addition, manufacturing, reliability and marketing skills began to expand, converting the industry from one dominated by the semi-conductor "black-art" specialists to one somewhat more balanced in its approach to business. Those companies that recognized the revolution (including many new ones) survived and prospered while those that didn't dropped out.

Similar changes are occurring today during the third revolution—this one created by the development of microprocessors. Once again order-of-magnitude improvements are being enjoyed by those users who have recognized the significance of microcomputer technology, and once again the engineering disciplines employed by the end user are changing, the emphasis now being placed on programming and other software development activities.

From the semiconductor manufacturer's standpoint, the changes are equally significant. Logic design and system architecture are becoming necessary skills for those who hope to succeed in the seventies. Marketing and sales will also be upgraded as semiconductor manufacturers begin selling "systems" rather than "components." Applications, training, software and hardware development tools and development systems are all new demands placed on the semiconductor manufacturer who hopes to survive the third revolution.

As with the first two revolutions, the inception of the microprocessor was characterized by the introduction of many different device types from many different manufacturers using many different technologies. Some of these will become high volume, multi-sourced, industry standard products (like TTL) and others will survive at lower volumes because they have certain performance advantages

which the "standard" devices cannot match in selected applications (similar to the role played by CMOS and ECL).

Most, however, will fall by the wayside as manufacturing efficiency and competitive pressures force the price to a point where the non-standard types become unprofitable. This point is rapidly approaching in the microprocessor area. The selection of the right microprocessor, therefore, is one of the current challenges facing today's system designer.

There are, today, basically two markets for microprocessors and two basic approaches being employed by semiconductor manufacturers to satisfy those markets. The two markets can best be defined as the *logic replacement market* and the *performance market*. The logic replacement market is best characterized by a certain cost-performance inelasticity which states that once a certain minimal performance level is achieved, no additional cost (and presumably selling price) can be justified in terms of additional units sold. Thus, the emphasis in the logic replacement market is either cost reduction at a given performance level or increased performance at no increase in cost. (This market, for example, would use TTL logic in applications where TTL performance was not required, but where TTL was the lowest cost solution.)

In the performance market, cost-performance is relatively elastic; i.e. additional end-equipment performance can demand a higher selling price and still provide the manufacturer with added volume and/or revenue. Here, the tendency would be to use the highest performance technology available in an effort to gain a performance edge over competition.

The two basic technologies which today compete for the total microprocessor market are Metal-Oxide-Semiconductor (MOS) and bipolar. While some overlap does exist, the market generally has accepted MOS in the logic replacement segment and bipolar in the performance segment.

With the large number of MOS alternatives available, the system designer has no simple chore in determining the best solution for his application. Not only does he have a choice of 4, 8, 12, and 16 bit devices, but once settling on the size of his data word, he'll have up to a dozen different n-bit designs to choose from. As with most alternatives of this nature, any one of a number of different designs will meet his system requirements and the designer will be apt to choose one of the two or three types within each category that appear to be "industry standards."

The situation is not quite as confusing in the bipolar arena simply because there are not as many alternatives as with the MOS approach. This is partially explained by the fact that most bipolar designs are bit-slice oriented thus eliminating the need to fix the size of the data word prior to selecting a particular bit slice design.

Perhaps even more significant in explaining the relatively small number of bipolar alternatives is the nature of the performance market which uses the technology. Since this

market tends to be smaller than the logic replacement market in terms of the number of users, the breadth of applications and the total amount of end-user equipment shipped, there is not the need for nor the incentive to create a large number of different device types. Thus, the semiconductor industry—at least to this point in time—has elected to concentrate their efforts on a relatively small number of device types.

One of these types (in fact the only one currently supported by more than two manufacturers) is the 2900 family, a bit slice approach introduced to the market in 1975. This state-of-the art family consists of a series of MSI/LSI devices designed to complement and enhance one another in typical microcomputer applications.

Recognizing the need for multi-sourcing in the market served by bipolar microprocessors, Raytheon, in 1975, became the first alternate source for 2900 family products and today has more 2900 family parts than any other semi-conductor manufacturer in the industry except for AMD who originated the series. In addition, Raytheon is committed to the continued support of the family, not only to the extent of providing all 2900 series devices, but also in the equally important areas of bipolar memory, logic, and the development tools required for both hardware and software design.

#### THE 2900 FAMILY

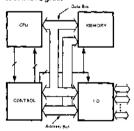

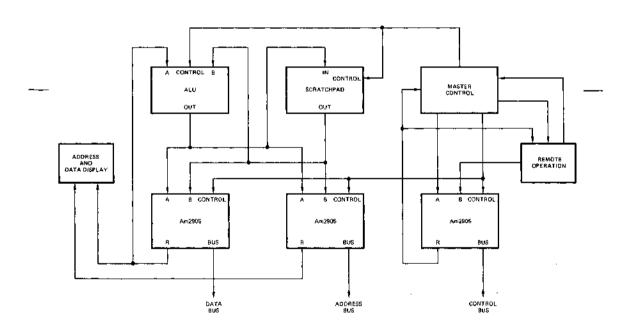

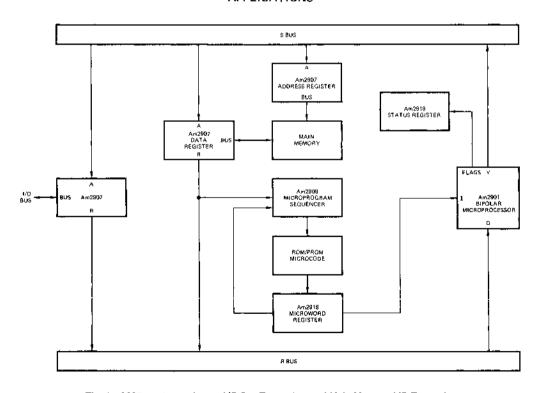

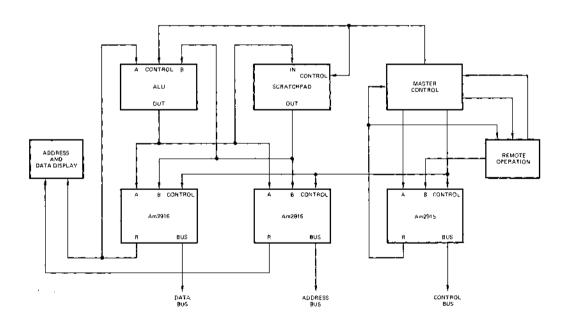

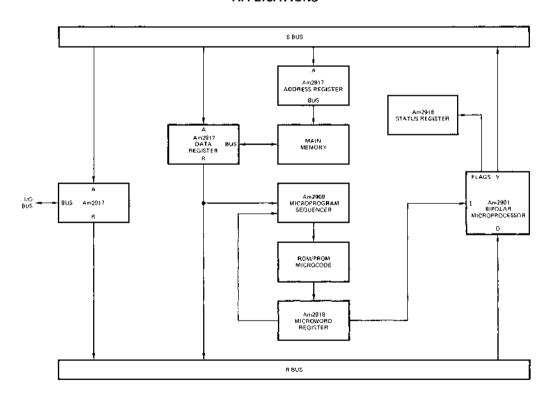

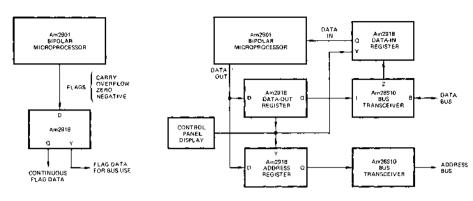

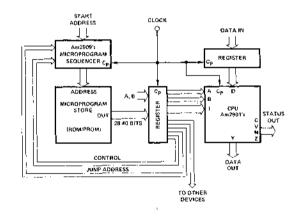

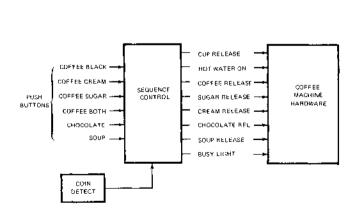

All microcomputers (in fact all practical digital computers) consist of four basic functions—central processing unit (CPU), control, memory, and input/output (I/O), (See Figure 1) Connecting the various functions are the address and data busses plus various control lines. While all microcomputers have essentially the same general architecture (i.e., perform the four functions shown in Figure 1), there are a number of differences in the way the various functions are implemented. The most obvious differences occur between MOS and bipolar technologies.

Figure 1, Typical Computer Functions.

In the MOS approach, for example, the most common implementation places the CPU and control function both on one chip. This chip—which was the original "microprocessor"—inputs instructions and data, performs the operation required by the instruction, and outputs the resulting data, It also provides the addressing function to locate the instructions in memory, and to read or write data in memory and/or i/O. Because the decoding circuitry for the instruc-

tions (the main portion of the control section) is hardwired on the chip, the same instruction (set of "1's" and "0's") will always cause the same operation (Add, Subtract, Compare, etc.) to be performed, and therefore, the instruction set is said to be "fixed". This is one of the major distinctions between MOS and bipolar microprocessors.

The microprocessor, however, is not a computer until one adds the memory and I/O circuits. In the case of MOS, this normally consists of ROM or PROM for program storage, RAM for data storage, and either discrete logic or special purpose LSI chips for I/O.\*

\*Some newer MOS devices include some memory and I/O capability or the same chip as the CPU and control. While somewhat limited in capability, these new chips can realistically be called microcomputers without the necessity of external memory or I/O.

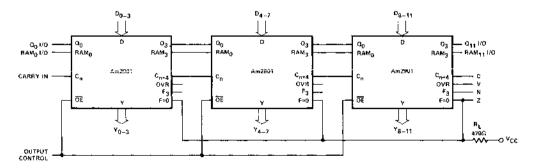

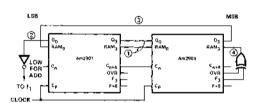

With the more popular bipolar microprocessors, such as the 2900 family, the CPU and control function are implemented differently. The CPU, for example, rather than being a fixed number of data bits wide (4, 8, 12, or 16 as in MOS) is actually a 2 or 4 bit slice that can be cascaded to any width that is a multiple of the basic slice. A four bit slice such as the 2901, for example, can be used to implement 4, 8, 12, 16...... 32, etc. bit microcomputers.

There are some obvious advantages and disadvantages to a bit slice approach when compared to the fixed data word, MOS approach. The disadvantage is, of course, that more chips are required per CPU.

Not only does the CPU function usually require more chips in bipolar designs, but also the control function is not even included on the chip as it is with the MOS devices. There are, however, advantages to bit slices over fixed data word machines; one of the most obvious being the capability of building larger, more powerful machines. In MOS, there simply isn't anything available over 16 bits, while 24, 32, and even 48 bit bipolar microcomputers have been designed and manufactured. Since wider data paths usually mean higher throughput, the bipolar approach can usually provide higher performance simply by building a bigger machine.

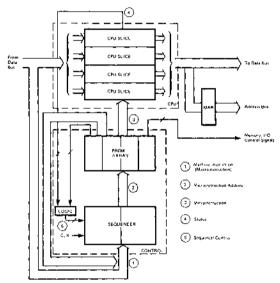

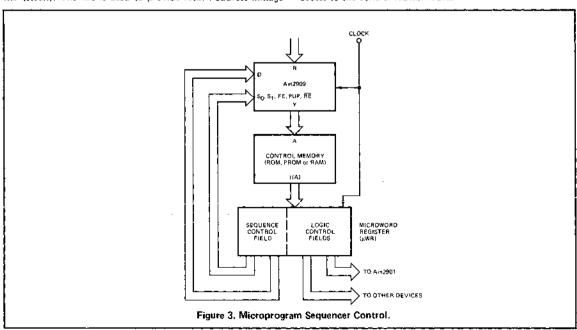

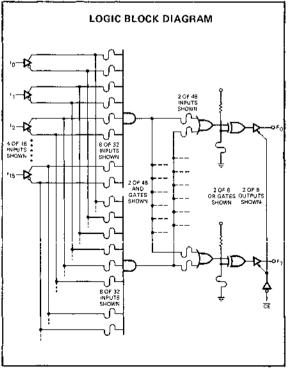

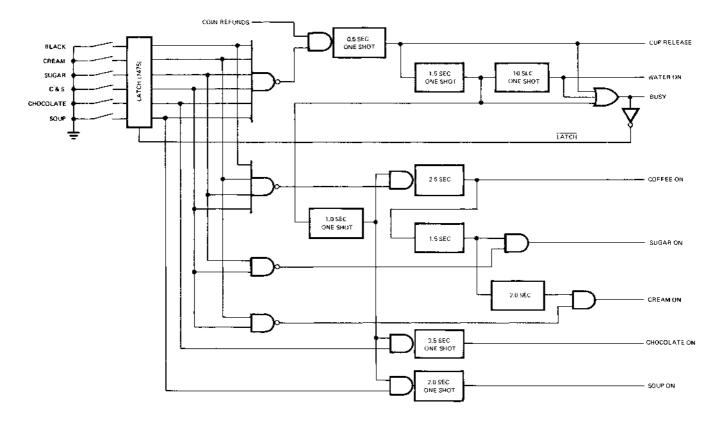

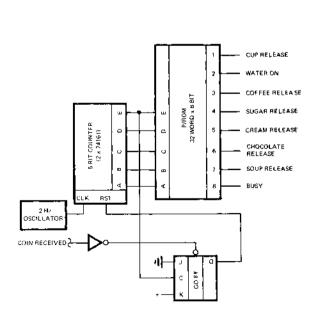

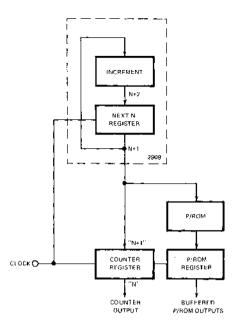

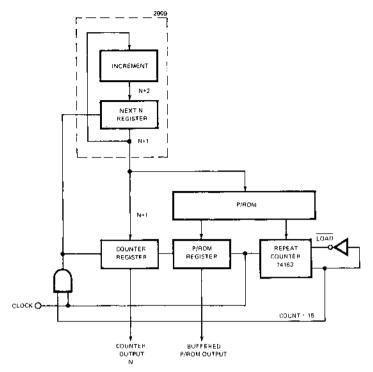

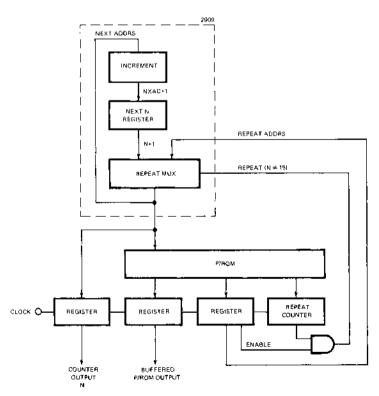

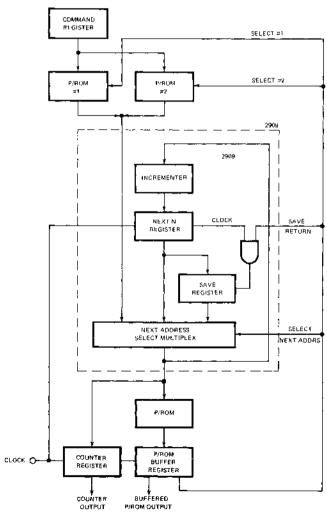

The other major architectural difference between MOS and bipolar is in the implementation of the control function. As mentioned previously, the MOS controller shares the same chip with the CPU and features a fixed instruction decoder. The bit slice controller, on the other hand, is constructed using a number of devices including PROMs, registers, and sequencers. (See Figure 2)

As in the case of the MOS controller, the main function of the bipolar equivalent is to accept instructions from memory via the data bus, decode the instruction, and then provide the individual control signals to the CPU, memory, and I/O. These control signals are generated by combining the decoded instruction with a multi-phase clock to provide a properly timed sequence of control words to the various system elements.

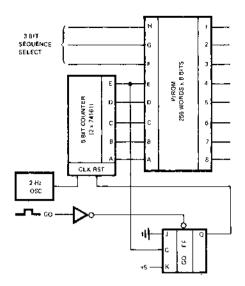

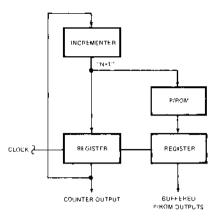

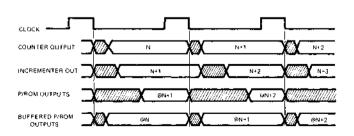

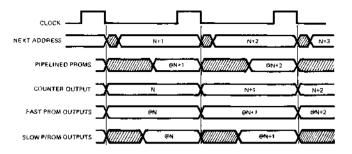

As shown in Figure 2, (\*) the control signals for the CPU, memory, and I/O are actually outputs from an array of PROMs (3). Each set of these control signals will cause a specific action to occur during a given clock period. Since it normally takes a series of these signals to actually accomplish what is normally considered to be a machine instruction (add, subtract, etc.), the individual sets are referred to as microinstructions. Thus, a machine instruction (or macroinstruction) consists of a series of microinstructions emanating from the PROM array.

\*Figure 2 shows only the major system elements for clarity. Various register and other logic elements will be required in an actual design.

Figure 2. Typical Bit-Slice Implementation for CPU and Control.

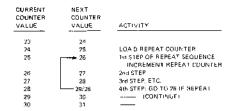

As one might expect, the series of microinstructions to accomplish a common machine instruction would be stored in consecutive address locations in the PROMs. Thus to accomplish a machine instruction—say an ADD—one would simply set a counter with the address of the first microinstruction of the ADD sequence and then simply increment the counter as each microinstruction is completed. This would continue until the final microinstruction of the ADD series was executed at which time the control would be set to accept the next machine instruction.

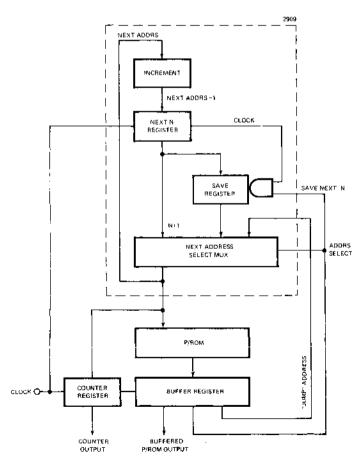

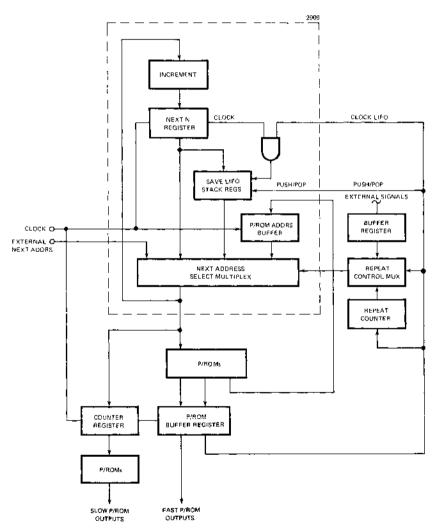

The circuitry that provides the addressing and counting functions is called a sequencer and most bipolar microprocessor families provide special LSI chips to accomplish this function. For example, the 2900 family currently provides two such circuits—the 2909 and 2911—and a third is in development. As with the CPU chips, sequencers are normally provided as slices to allow for a variety of microprogram sizes.

In addition to the addressing and counting functions, most sequencers provide circuitry to accommodate skips, jumps, and branches in the microprogram. This is accomplished by combining CPU status information (4) with a portion of the microcode to exercize control over the source of the next microinstruction address.

As in any microcomputer implementation, the machine instruction is stored in main memory (usually PROM) and is presented to the control circuit via the data bus ①. In most bipolar architectures, the machine instruction is simply the starting address of the sequence of microinstructions which will be used to actually accomplish the machine instruction.

As with the bipolar CPU, there are advantages and disadvantages in the manner in which the control function is implemented. One obvious disadvantage is chip count. It normally requires in excess of 10 packages to construct a bipolar microprocessor controller whereas the MOS controller is provided as part of the CPU chip.

The other factor which is sometimes considered to be a disadvantage is the necessity of generating the microinstructions. While this does, in essence, require twice the programming effort compared with MOS microprocessor programming, it is, at the same time, one of the features which enhances the performance aspects of the bipolar approach. By designing his own instruction set—which is precisely what the microprogrammer is doing—the user can tailor the instructions to his unique application, which improves performance and minimizes macroprogram storage requirements.

The ability to microprogram his machine also allows the user to emulate virtually any computer architecture (including many of today's popular mini's) thus making it possible to utilize existing applications software which often is more costly to generate than the hardware.

#### SUMMARY

In the following pages of this catalog, a detailed description of each member of the 2900 family is presented in the form of a data sheet. Where additional information is required to fully explain the function of a given device, a users guide is also provided.

In addition, data sheet and applications information is provided for Raytheon's bipolar memory products (PROMs and RAMs) since they will form an integral part of any bipolar microcomputer design.

Finally, a simple system design is presented to further clarify the basic operation of the 2900 family and to give a typical example of the procedure used to design bipolar microcomputer systems.

If there are any questions regarding the material presented in this catalog or for any additional information or applications assistance, simply contact Raytheon's Application Staff by calling 415-968-9211 and asking for Microprocessor Applications.

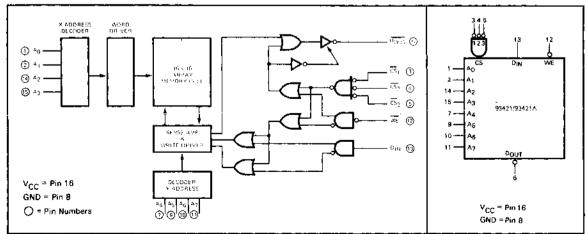

#### GENERAL DESCRIPTION

The four-bit bipolar microprocessor slice is designed as a high-speed cascadable element intended for use in CPU's, peripheral controllers, programmable microprocessors and numerous other applications. The microinstruction flexibility of the Am2901 will allow efficient emulation of almost any digital computing machine.

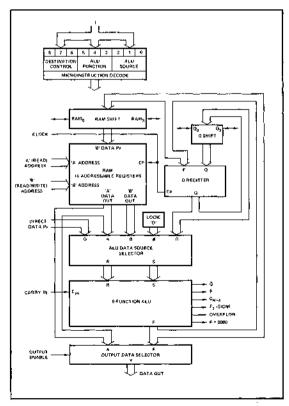

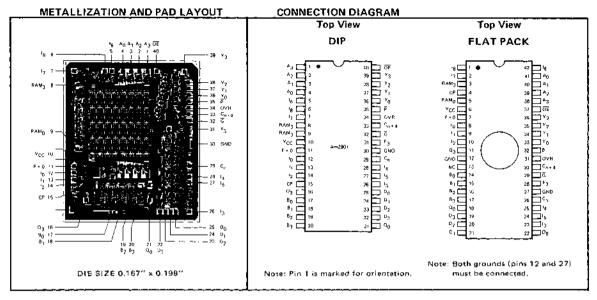

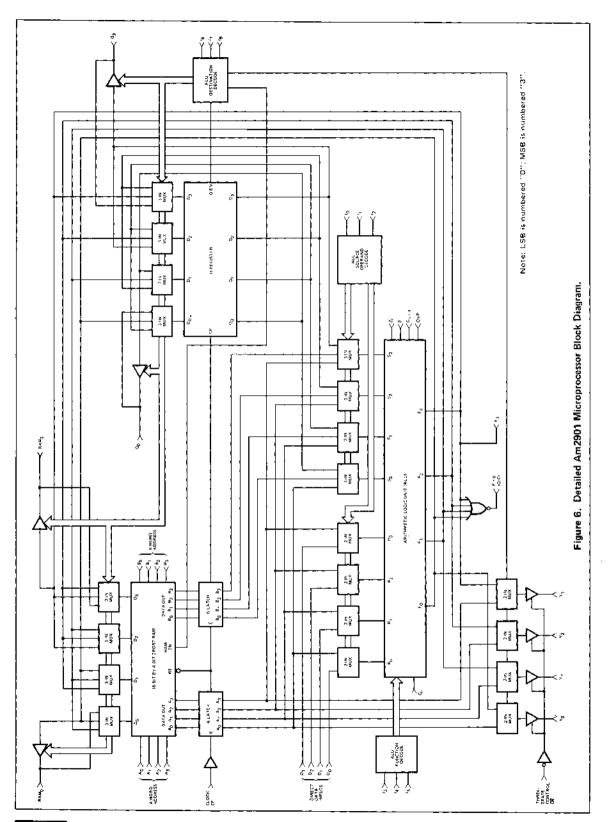

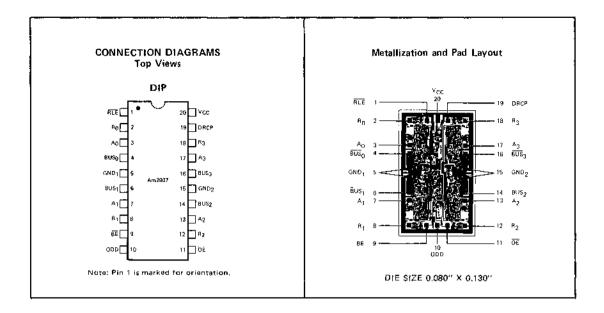

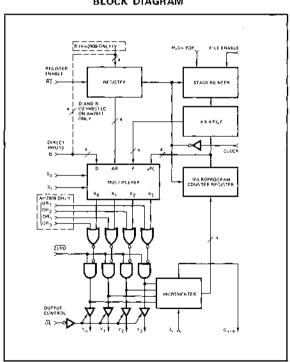

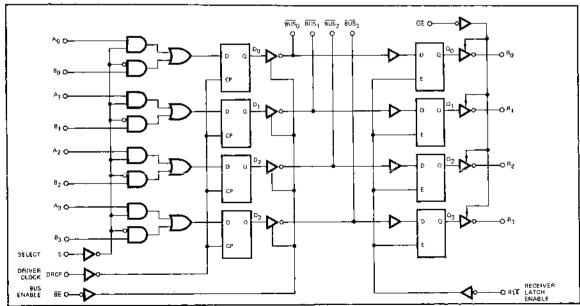

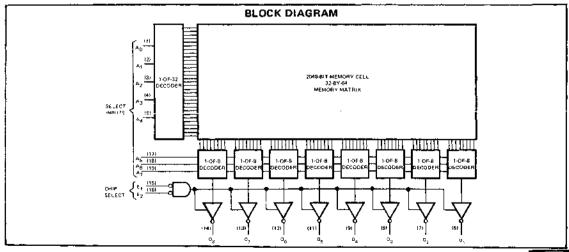

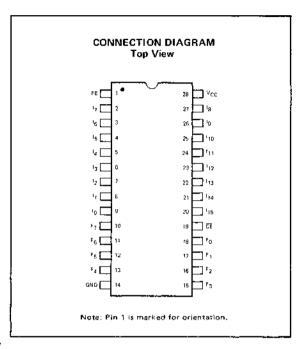

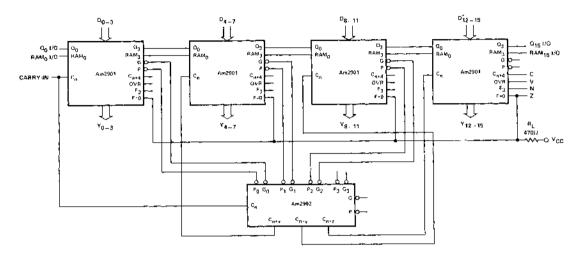

The device, as shown in the block diagram below, consists of a 16-word by 4-bit two-port RAM, a high-speed ALU, and the associated shifting, decoding and multiplexing circuitry. The nine-bit microinstruction word is organized into three groups of three bits each and selects the ALU source operands, the ALU function, and the ALU destination register. The microprocessor is cascadable with full look-ahead or with ripple carry, has three-state outputs, and provides various status flag outputs from the ALU. Advanced low-power Schottky processing is used to fabricate this 40-lead LSI chip.

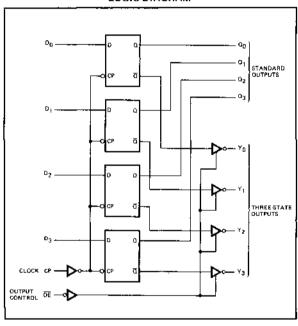

#### MICROPROCESSOR SLICE BLOCK DIAGRAM

#### DISTINCTIVE CHARACTERISTICS

- Two-address architecture

- Independent simultaneous access to two working registers saves machine cycles.

- Eight-function ALU

- Performs addition, two subtraction operations, and five logic functions on two source operands.

- Flexible data source selection -

- ALU data is selected from five source ports for a total of 203 source operand pairs for every ALU function.

- Left/right shift independent of ALU

- Add and shift operations take only one cycle.

- Four status flags

- Carry, overflow, zero, and negative.

- Expandable

- Connect any number of Am2901's together for longer word lengths.

- Microprogrammable

- Three groups of three bits each for source operand, ALU function, and destination control.

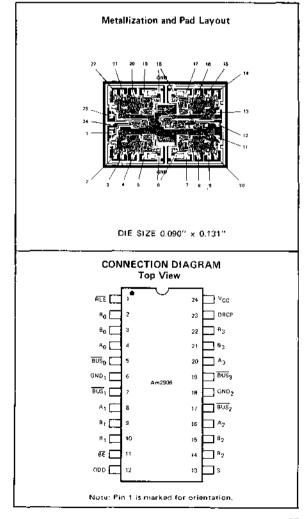

#### ORDERING INFORMATION

| Package<br>Type    | Temperature<br>Range | Order<br>Number |

|--------------------|----------------------|-----------------|

| Molded DIP         | 0°C to +70°C         | AM2901PC        |

| Hermetic DIP       | 0°C to +70°C         | AM2901DC        |

| Hermetic DIP       | –55°C to +125°C      | AM2901DM        |

| Hermetic Flat Pack | –55°C to +125°C      | AM2901FM        |

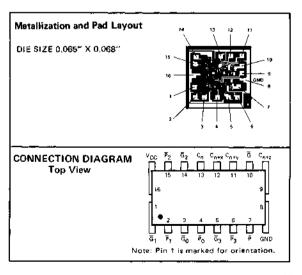

| Dice               | 0°C to +70°C         | AM2901XC        |

## MAXIMUM RATINGS (Above which the useful life may be impaired)

| Storage Temperature                                 | -65°C to +150°C                 |

|-----------------------------------------------------|---------------------------------|

| Temperature (Ambient) Under Bias                    | -55°C to +125°C                 |

| Supply Voltage to Ground Potential                  | -0.5 V to +6.3 V                |

| DC Voltage Applied to Outputs for HIGH Output State | -0.5 V to +V <sub>CC</sub> max. |

| DC Input Voltage                                    | -0.5 V to +5.5 V                |

| DC Output Current, Into Outputs                     | 30 mA                           |

| DC Input Current                                    | -30 mA to +5.0 mA               |

#### **OPERATING RANGE**

| P/N          | Ambient Temperature | V <sub>CC</sub>  |

|--------------|---------------------|------------------|

| Am2901PC, DC | 0°C to +70°C        | 4.75 V to 5.25 V |

| Am2901DM, FM | -55°C to +125°C     | 4,50 V to 5,50 V |

#### STANDARD SCREENING

(Conforms to MIL-STD-883 for Class C Parts)

|                                | MIL-STD-883          |                                               | -           |

|--------------------------------|----------------------|-----------------------------------------------|-------------|

| Step                           | Method               | Conditions                                    | Am2901DM,FM |

| Pre-Seal Visual Inspection     | 2010                 | В                                             | 100%        |

| Stabilization Bake             | 1008                 | C 24-hour<br>150°C                            | 100%        |

| Temperature Cycle              | 1010                 | C65°C to +150°C<br>10 cycles                  | 100%        |

| Centrifuge                     | 2001                 | B 10,000G                                     | 100%        |

| Fine Leak                      | 1014                 | A 5 x 10 <sup>-8</sup> atm-cc/cm <sup>3</sup> | 100%        |

| Gross Leak                     | 1014                 | C2 Fluorocarbon                               | 100%        |

| Electrical Test                | 5004                 | See below for                                 | 100%        |

| Subgroups 1 and 7              | 5004                 | definitions of subgroups                      |             |

| Insert Additional Screening he | re for Class B Parts |                                               |             |

| Group A Sample Tests           | ""   ""              | I                                             |             |

| Subgroup 1                     |                      |                                               | LTPD = 5    |

| Subgroup 2                     | !                    |                                               | LTPD = 7    |

| Subgroup 3                     | FROE                 | See below for                                 | LTPD = 7    |

| Subgroup 7                     | 5005                 | definitions of subgroups                      | LTPD = 7    |

| Subgroup 8                     |                      |                                               | LTPD = 7    |

| Subgroup 9                     | 1                    |                                               | LTPO = 7    |

#### ADDITIONAL SCREENING FOR CLASS B PARTS

| _               | MIL-STD-883 | 0. 15.7                  | Level          |

|-----------------|-------------|--------------------------|----------------|

| Step            | Method      | Conditions               | Am2901DMB, FMI |

| Burn- n         | 1015        | D 125°C<br>160 hours min | 100%           |

| Electrical Test | 5004        |                          | i              |

| Subgroup 1      |             | İ                        | 100%           |

| Subgroup 2      |             |                          | 100%           |

| Subgroup 3      |             |                          | 100%           |

| Subgroup 7      |             | 1                        | 100%           |

| Subgroup 9      |             |                          | 100%           |

GROUP A SUBGROUPS (as defined in MIL-STD-883, method 5005)

| Subgroup | Parameter | Temperature                           |  |  |  |  |

|----------|-----------|---------------------------------------|--|--|--|--|

| 1        | DC        | 25°C                                  |  |  |  |  |

| 2        | DC        | Maximum rated temperature             |  |  |  |  |

| 3        | DC        | Minimum rated temperature             |  |  |  |  |

| 7        | Function  | 25°C                                  |  |  |  |  |

| 8        | Function  | Maximum and minimum rated temperature |  |  |  |  |

| 9        | Switching | 25°C                                  |  |  |  |  |

| 10       | Switching | Maximum Rated Temeperature            |  |  |  |  |

| 11       | Switching | Minimum Rated Temperature             |  |  |  |  |

#### ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE (Unless Otherwise Noted)

(Group A, Subgroups 1, 2 and 3)

| rameters        | Description                               | Test Cond                                                                                         | Test Conditions (Note 1)                                             |                                                  |                 | Typ.<br>(Note 2) | Max.                   | Units      |                        |            |         |  |  |  |     |    |

|-----------------|-------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------|-----------------|------------------|------------------------|------------|------------------------|------------|---------|--|--|--|-----|----|

|                 | ]                                         |                                                                                                   | 1 <sub>OH</sub> =1<br>Y <sub>0</sub> , Y <sub>1</sub> , Y            |                                                  | 2.4             |                  | j                      |            |                        |            |         |  |  |  |     |    |

|                 |                                           |                                                                                                   |                                                                      |                                                  |                 | <del> </del>     | }                      |            |                        |            |         |  |  |  |     |    |

|                 |                                           |                                                                                                   |                                                                      | .0mA, C <sub>n+4</sub>                           | 2,4             | 1                | ——-                    |            |                        |            |         |  |  |  |     |    |

| VOH             | Output HIGH Voltage                       | V <sub>CC</sub> = MIN.<br>VIN = VIH or VIL                                                        |                                                                      | 00µA, OVR, <u>Р</u>                              | 2.4             |                  |                        | Volts      |                        |            |         |  |  |  |     |    |

|                 |                                           | 114 11H 22 11E                                                                                    | 10H * −6                                                             |                                                  | 2.4             |                  |                        |            |                        |            |         |  |  |  |     |    |

|                 |                                           | I <sub>OH</sub> = −6<br>RAM <sub>0, 3</sub>                                                       | , C <sub>0, 3</sub>                                                  | 2.4                                              |                 |                  |                        |            |                        |            |         |  |  |  |     |    |

|                 |                                           |                                                                                                   | 10H = ~1                                                             | .6mA, G                                          | 2.4             |                  |                        |            |                        |            |         |  |  |  |     |    |

| ICEX            | Output Leakage Current for F = 0 Output   | V <sub>CC</sub> = MIN., V <sub>OH</sub> =<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | 5.5V                                                                 |                                                  |                 |                  | 250                    | μА         |                        |            |         |  |  |  |     |    |

|                 |                                           |                                                                                                   | IOL * 16                                                             |                                                  |                 |                  | 0.5                    |            |                        |            |         |  |  |  |     |    |

|                 |                                           | V <sub>CC</sub> = MIN.,                                                                           |                                                                      | mA, C <sub>n+4</sub> , F = 0                     |                 |                  | 0.5                    |            |                        |            |         |  |  |  |     |    |

| VOL             | Output LOW Voltage                        | VIN = VIH or VIL                                                                                  |                                                                      | mA, OVFI, P                                      |                 |                  | 0.5                    | Volts      |                        |            |         |  |  |  |     |    |

|                 |                                           |                                                                                                   | I <sub>OL</sub> = 6.0                                                | lmA, F3                                          |                 |                  | 0.5                    |            |                        |            |         |  |  |  |     |    |

| V <sub>IH</sub> | Input HIGH Level                          | Guaranteed input log voltage for all inputs                                                       |                                                                      |                                                  | 2.0             |                  |                        | Volts      |                        |            |         |  |  |  |     |    |

| ۷۱۲             | Input LOW Level                           | Guaranteed input log                                                                              | ical LOW                                                             | Military                                         | · · · · · - · - | <del> </del>     | 0.7                    | Volts      |                        |            |         |  |  |  |     |    |

| *   L           | input 2011 CEVE                           | voltage for all inputs                                                                            |                                                                      | Commercial                                       |                 |                  | 8.0                    | VOITS      |                        |            |         |  |  |  |     |    |

| v <sub>t</sub>  | Input Clamp Voltage                       | V <sub>CC</sub> = M1N., 1 <sub>IN</sub> = -                                                       | 18mA                                                                 |                                                  |                 |                  | -1.5                   | Volts      |                        |            |         |  |  |  |     |    |

|                 |                                           | Clock, O                                                                                          | Clock, OE                                                            |                                                  |                 | -0.36            |                        |            |                        |            |         |  |  |  |     |    |

|                 |                                           |                                                                                                   | Ag, A1,                                                              | A2, A3                                           |                 |                  | -0.36                  | 1          |                        |            |         |  |  |  |     |    |

|                 |                                           | V <sub>CC</sub> = MAX.<br>V <sub>IN</sub> = 0.5V                                                  | B <sub>0</sub> , B <sub>1</sub> , B <sub>2</sub> , B <sub>3</sub>    |                                                  |                 |                  | -0.36                  | mA         |                        |            |         |  |  |  |     |    |

| 116             | Input LOW Current                         |                                                                                                   | D <sub>0</sub> , D <sub>1</sub> , D <sub>2</sub> , D <sub>3</sub>    |                                                  |                 | <u> </u>         | -0.72                  |            |                        |            |         |  |  |  |     |    |

|                 |                                           |                                                                                                   | 10, 11, 12                                                           |                                                  |                 | <u> </u>         | -0.36                  |            |                        |            |         |  |  |  |     |    |

|                 | }                                         |                                                                                                   | 13, 14, 15                                                           |                                                  |                 | ļ                | -0.72                  |            |                        |            |         |  |  |  |     |    |

|                 |                                           |                                                                                                   |                                                                      | , Q <sub>0, 3</sub> (Note 4)                     |                 | ļ <b>i</b>       | 0.8                    |            |                        |            |         |  |  |  |     |    |

|                 |                                           |                                                                                                   | c <sub>n</sub>                                                       |                                                  |                 |                  | -3.6                   |            |                        |            |         |  |  |  |     |    |

|                 | 1                                         |                                                                                                   | Clock, OE                                                            |                                                  |                 |                  | 20                     |            |                        |            |         |  |  |  |     |    |

|                 |                                           |                                                                                                   | A <sub>0</sub> , A <sub>1</sub> ,                                    | A <sub>2</sub> , A <sub>3</sub>                  |                 |                  | 20                     | μΑ         |                        |            |         |  |  |  |     |    |

|                 |                                           | V <sub>CC</sub> = MAX.                                                                            | 8 <sub>0</sub> , B <sub>1</sub> , 6                                  | 3 <sub>2</sub> , B <sub>3</sub>                  |                 |                  | 20                     |            |                        |            |         |  |  |  |     |    |

| Iн              | Input HIGH Current                        |                                                                                                   | D <sub>0</sub> , D <sub>1</sub> ,                                    | · ·                                              |                 |                  | 40                     |            |                        |            |         |  |  |  |     |    |

|                 | į l                                       | V <sub>IN</sub> = 2.7V                                                                            | 10, 11, 12                                                           |                                                  |                 |                  | 20                     |            |                        |            |         |  |  |  |     |    |

|                 |                                           |                                                                                                   | 13, 14, 15                                                           |                                                  |                 |                  | 40                     |            |                        |            |         |  |  |  |     |    |

|                 |                                           |                                                                                                   |                                                                      | , Q <sub>0, 3</sub> (Note 4)                     |                 |                  | 100                    |            |                        |            |         |  |  |  |     |    |

| 1.              | Input HIGH Current                        | V <sub>CC</sub> * MAX., V <sub>IN</sub> =                                                         | C <sub>n</sub>                                                       |                                                  |                 |                  | 1.0                    |            |                        |            |         |  |  |  |     |    |

| <u>'lı</u>      | inpocition content                        | *CC - MXV-1 * IN =                                                                                | 1                                                                    | Vo = 2 411                                       |                 |                  | 50                     | MA         |                        |            |         |  |  |  |     |    |

|                 |                                           |                                                                                                   | Y <sub>0</sub> , Y <sub>1</sub> ,<br>Y <sub>2</sub> , Y <sub>3</sub> |                                                  |                 | <del>  </del>    |                        |            |                        |            |         |  |  |  |     |    |

| tan:            |                                           |                                                                                                   | - 2, 3                                                               | V <sub>O</sub> = 0.5V                            |                 |                  | -50                    |            |                        |            |         |  |  |  |     |    |

|                 | Off State (High Impedance) Output Current | V <sub>CC</sub> = MAX.                                                                            | V <sub>CC</sub> = MAX.                                               | VCC = MAX.                                       | VCC = MAX.      | VCC = MAX.       | V <sub>CC</sub> = MAX. | VCC = MAX. | V <sub>CC</sub> = MAX. | VCC = MAX. | RAMo, s |  |  |  | 100 | μА |

|                 |                                           |                                                                                                   | Ω <sub>0,3</sub>                                                     | V <sub>O</sub> = 0.5V<br>(Note 4)                |                 |                  | -800                   |            |                        |            |         |  |  |  |     |    |

|                 |                                           |                                                                                                   | Y <sub>0</sub> , Y <sub>1</sub> ,                                    | Y <sub>2</sub> , Y <sub>3</sub> , $\overline{G}$ | 15              |                  | -40                    |            |                        |            |         |  |  |  |     |    |

|                 |                                           | V+0 - <b>6.7</b> 5V                                                                               | Cn+4                                                                 |                                                  | -15             | I                | -40                    |            |                        |            |         |  |  |  |     |    |

| IOS             | Output Short Circuit Current<br>(Note 3)  | V <sub>CC</sub> = 5.75V<br>V <sub>O</sub> = 0.5V                                                  | OVR, P                                                               |                                                  | -15             |                  | -40                    | mA         |                        |            |         |  |  |  |     |    |

|                 | 1.3545 67                                 | , U 4.04                                                                                          | F3                                                                   |                                                  | -15             | L                | -40                    |            |                        |            |         |  |  |  |     |    |

|                 | <u> </u>                                  |                                                                                                   | RAM <sub>0, 3</sub>                                                  | , Q <sub>0, 3</sub>                              | -15             |                  | _ <b>4</b> 0           |            |                        |            |         |  |  |  |     |    |

|                 | ,                                         |                                                                                                   | Military                                                             |                                                  |                 | 185              | 280                    |            |                        |            |         |  |  |  |     |    |

Notes: 1. For conditions shown as MIN, or MAX,, use the appropriate value specified under Electrical Characteristics for the applicable device type.

These are three-state outputs internally connected to TTL inputs. Input characteristics are measured with 1678 in a state such that the

three-state output is OFF.

<sup>2.</sup> Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

<sup>3.</sup> Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

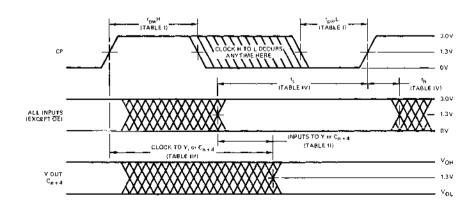

**TABLE I**

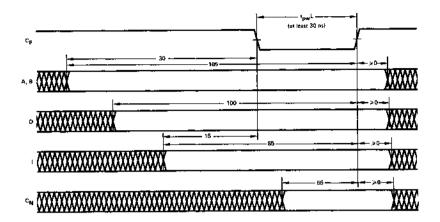

Tables 1, 11, and 111 below define the timing requirements of the Am2901 in a system. The Am2901 is guaranteed to function correctly over the operating range when used within the delay and set-up time constraints of these tables for the appropriate device type. The tables are divided into three types of parameters; clock characteristics, combinational delays from inputs to outputs, and set-up and hold time requirements. The latter table defines the time prior to the end of the cycle (i.e., clock LOW-to-HIGH transition) that each input must be stable to guarantee that the correct data is written into one of the internal registers.

The performance of the Am2901 within the limits of these tables is guaranteed by the testing defined as "Group A, Subgroup 9" Electrical Testing. For a copy of the tests and limits used for subgroup 9, contact Product Marketing.

#### CYCLE TIME AND CLOCK CHARACTERISTICS

| TIME                                                                                     | Am2901DC,PC | Am2901DM,FM |

|------------------------------------------------------------------------------------------|-------------|-------------|

| Read-Modify-Write Cycle<br>(time from selection of<br>A, B registers to end of<br>cycle) | 105 ns      | 120ns       |

| Maximum Clock Frequency to<br>Shift Q Register (50% duty<br>cycle)                       | 9.5MHz      | 8.3MHz      |

| Minimum Clock LOW Time                                                                   | 30ns        | 30 ns       |

| Minimum Clock HIGH Time                                                                  | 30ns        | 30 ns       |

| Minimum Clock Period                                                                     | 105ns       | 120ns       |

TABLE 11 MAXIMUM COMBINATIONAL PROPAGATION DELAYS (all in ns, CL  $\leq$  15 pF)

|                            | 1     | Am2901DC, PC (0°C to +70°C; 5 V ±5%) |                  |      |     |     |                                      |          | Am    | 29010 | M, FM | (-55° | C to +     | 125°C;   | 5 V ±1                               | 0%)      |

|----------------------------|-------|--------------------------------------|------------------|------|-----|-----|--------------------------------------|----------|-------|-------|-------|-------|------------|----------|--------------------------------------|----------|

| To Output                  | v     |                                      |                  | G, ₽ | F≖0 | OVD | Shift<br>Outputs                     |          |       | F.    |       | Ĝ, P  | F=0        |          | Shift<br>Outputs                     |          |

| From<br>Input              | Y     | F3                                   | C <sub>n+4</sub> | G, F | 470 | OVR | RAM <sub>O</sub><br>RAM <sub>3</sub> |          | Y     | F3    | Cn+4  | G, P  | RL≃<br>470 | i        | RAM <sub>0</sub><br>RAM <sub>3</sub> |          |

| A, B                       | 110   | 85                                   | 80               | 80   | 110 | 75  | 110                                  | _        | 120   | 95    | 90    | 90    | 120        | 85       | 120                                  | _        |

| D (arithmetic mode)        | 100   | 70                                   | 70               | 70   | 100 | 60  | 95                                   | _        | 110   | 80    | 75    | 75    | 110        | 65       | 105                                  | <u> </u> |

| D (I = X37) (Note 5)       | 60    | 50                                   |                  | _    | 60  |     | 60                                   |          | 65    | 55    | -     |       | 65         | <b>-</b> | 65                                   |          |

| Cn                         | 55    | 35                                   | 30               |      | 50  | 40  | 55                                   |          | 60    | 40    | 30    | -     | 55         | 45       | 60                                   | -        |

| l <sub>012</sub>           | 85    | 65                                   | 65               | 65   | 80  | 65  | 80                                   | _        | 90    | 70    | 70    | 70    | 85         | 70       | 85                                   |          |

| 1345                       | 70    | 55                                   | 60               | 60   | 70  | 60  | 65                                   | <u> </u> | 75    | 60    | 65    | 65    | 75         | 65       | 70                                   |          |

| 1678                       | 55    |                                      | -                | -    | _   |     | 45                                   | 45       | 60    | _     | _     | _     | _          | _        | 50                                   | 50       |

| OE Enable/Disable          | 40/25 | _                                    | _                |      | _   | -   | -                                    | _        | 40/25 | _     | _     | _     | -          | . –      | -                                    | -        |

| A bypassing ALU (I = 2xx). | 60    | -                                    | _                |      | _   | -   | _                                    |          | 65    |       | -     | -     |            | _        | _                                    | -        |

| Clock 🍜 (Note 6)           | 115   | 85                                   | 100              | 100  | 110 | 95  | 105                                  | 60       | 125   | 95    | 110   | 110   | 120        | 105      | 115                                  | 65       |

#### SET-UP AND HOLD TIMES (all in ns) (Note 1)

#### TABLE III

| From Input                              | Notes                                   | Am2901DC, PC (0°C      | to +70°C, 5V ±5%) | Am2901DM,FM (-55°C to +125°C,5V, ±10% |           |  |  |

|-----------------------------------------|-----------------------------------------|------------------------|-------------------|---------------------------------------|-----------|--|--|

|                                         | IAD(62                                  | Set-Up Time            | Hold Time         | Set-Up Time                           | Hold Time |  |  |

| A, B<br>Source                          | 2, 4 105<br>3, 5 t <sub>pw</sub> L + 30 |                        | 0                 | 120<br>t <sub>pw</sub> L + 30         | 0         |  |  |

| B Dest.                                 | 2, 4                                    | tpwL + 15              | 0                 | t <sub>pw</sub> L +15                 | 0         |  |  |

| D (arithmetic mode)                     |                                         | 100                    | 0                 | 110                                   | 0         |  |  |

| D (I = X37) (Note 5)                    |                                         | 60                     | 0                 | 65                                    | 0         |  |  |

| Cn                                      |                                         | 55                     | 0                 | 60                                    | 0         |  |  |

| I <sub>012</sub>                        |                                         | 85                     | 0                 | 90                                    | 0         |  |  |

| <sup>1</sup> 345                        |                                         | 70                     | 0                 | 75                                    | 0         |  |  |

| <sup>1</sup> 678                        | 4                                       | t <sub>pw</sub> L + 15 | 0                 | t <sub>pw</sub> L + 15                | 0         |  |  |

| RAM <sub>0, 3</sub> , Q <sub>0, 3</sub> |                                         | 30                     | 0                 | 30                                    | 0         |  |  |

Notes: 1. See Figure 11 and 12.

- 2. If the B address is used as a source operand, allow for the "A, B source" set-up time; If it is used only for the destination address, use the "B dest." set-up time.

- 3. Where two numbers are shown, both must be met.

- 4. "tpwL" is the clock LOW time.

- 5. DV0 is the fastest way to load the RAM from the D inputs. This function is obtained with I = 337.

- 6. Using Q register as source operand in arithmetic mode. Clock is not normally in critical speed path when Q is not a source.

SET-UP AND HOLD TIMES (minimum cycles from each input)

Set-up and hold times are defined relative to the clock LOW-to-HIGH edge. Inputs must be steady at all times from the set-up time prior to the clock until the hold time after the clock. The set-up times allow sufficient time to perform the correct operation on the correct data so that the correct ALU data can be written into one of the registers.

Figure 1. Minimum Cycle Times from Inputs. Numbers Shown are Minimum Data Stable Times for Am2901 DC, in ns. See Table III for Detailed Information.

- Notes: 1. This delay is the max,  $t_{pd}$  of the register containing A, B, D, and I. For the Am2918, use 13ns.

- 2. 10ns for look-ahead carry. For ripple carry over 16 bits use  $2 \times (C_n \rightarrow C_{n+4})$ , or 60ns.

- This is the delay associated with the multiplexer between the shift outputs and shift inputs on the Am2901s. See Figure 19.

- 4. Not applicable for logic operations.

- 5. Clock rising edge may occur here if add and shift do not occur on same cycle.

Figure 2. Switching Waveforms for 16-Bit System Assuming A, B, D and I are all Driven from Registers with the same Propagation Delay, Clocked by the Am2901 Clock.

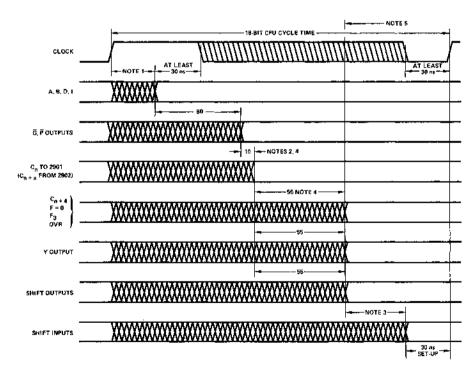

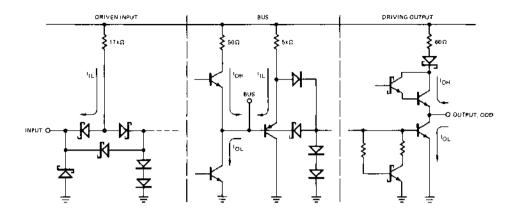

Figure 3. Am2901 Input/Output Current Interface Conditions.

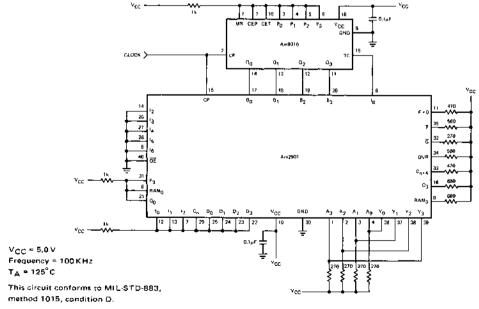

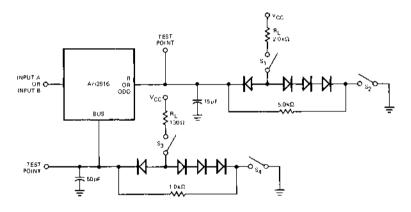

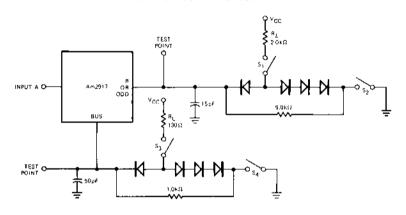

Figure 4. Am2901 Burn-In Circuit.

Figure 5.

#### DEFINITIONS

- A<sub>0-3</sub> The four address inputs to the register stack used to select one register whose contents are displayed through the A-port.

- B<sub>0-3</sub> The four address inputs to the register stack used to select one register whose contents are displayed through the B-port and into which new data can be written when the clock goes LOW.

- I<sub>0-8</sub> The nine instruction control lines to the Am2901, used to determine what data sources will be applied to the ALU (I<sub>012</sub>), what function the ALU will perform (I<sub>345</sub>), and what data is to be deposited in the Q-register or the register stack (I<sub>678</sub>).

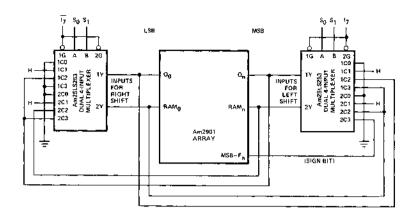

- Q<sub>3</sub> A shift line at the MSB of the Q register (Q<sub>3</sub>) and the register stack (RAM<sub>3</sub>). Electrically these lines are three-state outputs connected to TTL inputs internal to the Am2901. When the destination code on I<sub>678</sub> indicates an up shift (octal 6 or 7) the three-state outputs are enabled and the MSB of the Q register is available on the Q<sub>3</sub> pin and the MSB of the ALU output is available on the RAM<sub>3</sub> pin. Otherwise, the three-state outputs are OFF (high-impedance) and the pins are electrically LS-TTL inputs. When the destination code calls for a down shift, the pins are used as the data inputs to the MSB of the Q register (octal 4) and RAM (octal 4 or 5).

- Q<sub>0</sub> Shift lines like Q<sub>3</sub> and RAM<sub>3</sub>, but at the LSB of the Q-register and RAM. These pins are tied to the Q<sub>3</sub> and RAM<sub>3</sub> pins of the adjacent device to transfer data between devices for up and down shifts of the Q-register and ALU data.

- D<sub>0-3</sub> Direct data inputs. A four-bit data field which may be selected as one of the ALU data sources for entering data into the Am2901. D<sub>0</sub> is the LSB.

- Y<sub>0-3</sub> The four data outputs of the Am2901. These are three-state output lines. When enabled, they display either the four outputs of the ALU or the data on the A-port of the register stack, as determined by the destination code I<sub>678</sub>.

- Output Enable. When OE is HIGH, the Y outputs are OFF; when OE is LOW, the Y outputs are active (HIGH or LOW).

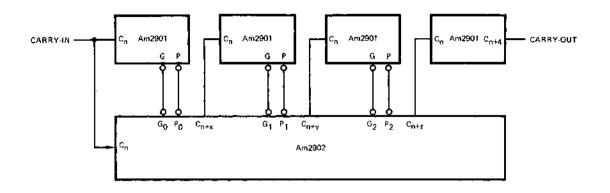

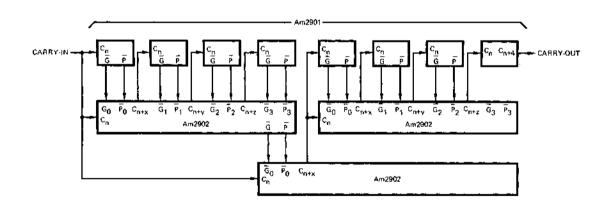

- P, G The carry generate and propagate outputs of the Am2901's ALU. These signals are used with the Am2902 for carry-lookahead. See Figure 8 for the logic equations.

- OVR Overflow. This pin is logically the Exclusive-OR of the carry-in and carry-out of the MSB of the AŁU. At the most significant end of the word, this pin indicates that the result of an arithmetic two's complement operation has overflowed into the sign-bit. See Figure 8 for logic equation.

- F=0 This is an open collector output which goes HIGH (OFF) if the data on the four ALU outputs  $F_{0-3}$  are all LOW. In positive logic, it indicates the result of an ALU operation is zero.

- C<sub>n</sub> The carry-in to the Am2901's ALU.

- C<sub>n+4</sub> The carry-out of the Am2901's ALU. See Figure 8 for equations.

- CP The clock to the Am2901. The Q register and register stack outputs change on the clock LOW-to-HIGH transition. The clock LOW time is internally the write enable to the 16 x 4 RAM which comprises the "master" latches of the register stack. While the clock is LOW, the "slave" latches on the RAM outputs are closed, storing the data previously on the RAM outputs. This allows synchronous master-slave operation of the register stack.

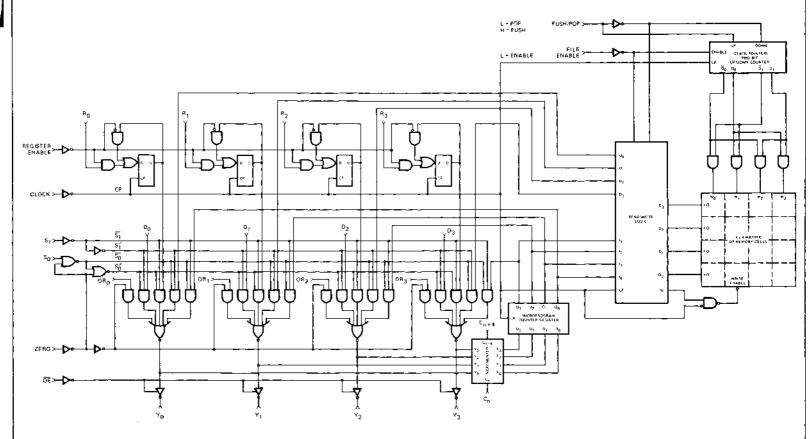

A detailed block diagram of the bipolar microprogrammable microprocessor structure is shown in Figure 1. The circuit is a four-bit slice cascadable to any number of bits. Therefore, all data paths within the circuit are four bits wide. The two key elements in the Figure 1 block diagram are the 16-word by 4-bit 2-port RAM and the high-speed ALU.

Data in any of the 16 words of the Random Access Memory (RAM) can be read from the A-port of the RAM as controlled by the 4-bit A address field input. Likewise, data in any of the 16 words of the RAM as defined by the B address field input can be simultaneously read from the B-port of the RAM. The same code can be applied to the A select field and B select field in which case the identical file data will appear at both the RAM A-port and B-port outputs simultaneously.

When enabled by the RAM write enable (RAM EN), new data is always written into the file (word) defined by the B address field of the RAM. The RAM data input field is driven by a 3-input multiplexer. This configuration is used to shift the ALU output data (F) if desired. This three-input multiplexer scheme allows the data to be shifted up one bit position, shifted down one bit position, or not shifted in either direction.

The RAM A-port data outputs and RAM B-port data outputs drive separate 4-bit latches. These latches hold the RAM data while the clock input is LOW. This eliminates any possible race conditions that could occur while new data is being written into the RAM.

The high-speed Arithmetic Logic Unit (ALU) can perform three binary arithmetic and five logic operations on the two 4-bit input words R and S. The R input field is driven from a 2-input multiplexer, while the S input field is driven from a 3-input multiplexer. Both multiplexers also have an inhibit capability; that is, no data is passed. This is equivalent to a "zero" source operand.

Referring to Figure 6, the ALU R-input multiplexer has the RAM A-port and the direct data inputs (D) connected as inputs. Likewise, the ALU S-input multiplexer has the RAM A-port, the RAM B-port and the Q register connected as inputs.

This multiplexer scheme gives the capability of selecting various pairs of the A, B, D, Q and "O" inputs as source operands to the ALU. These five inputs, when taken two at a time, result in ten possible combinations of source operand pairs. These combinations include AB, AD, AQ, AD, BD, BQ, BQ, DQ, DQ and QQ. It is apparent that AD, AQ and AQ are somewhat redundant with BD, BQ and BQ in that if the A address and B address are the same, the identical function results. Thus, there are only seven completely non-redundant source operand pairs for the ALU. The Am2901 microprocessor implements eight of these pairs. The microinstruction inputs used to select the ALU source operands are the IQ, I1, and I2 inputs. The definition of IQ, I1, and I2 for the eight source operand combinations are as shown in Figure 7. Also shown is the octal code for each selection.

The two source operands not fully described as yet are the D input and Q input. The D input is the four-bit wide direct data field input. This port is used to insert all data into the working registers inside the device. Likewise, this input can be used in the ALU to modify any of the internal data files. The Q register is a separate 4-bit file intended primarily for multiplication and division routines but it can also be used as an accumulator or holding register for some applications.

The ALU itself is a high-speed arithmetic/logic operator capable of performing three binary arithmetic and five logic functions. The I<sub>3</sub>, I<sub>4</sub>, and I<sub>5</sub> microinstruction inputs are used to select the

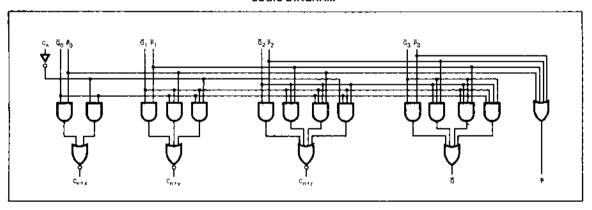

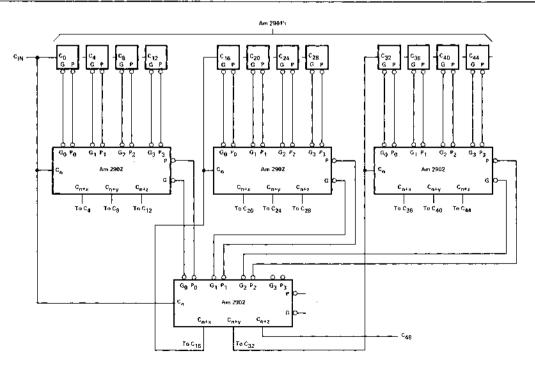

ALU function. The definition of these inputs is shown in Figure 8. The local code is also shown for reference. The normal technique for cascading the ALU of several devices is in a look-ahead carry mode. Carry generate,  $\vec{F}$ , and carry propagate,  $\vec{F}$ , are outputs of the device for use with a carry-look-ahead-generator such as the Am2902 ('182). A carry-out,  $C_{n+4}$ , is also generated and is available as an output for use as the carry flag in a status register. Both carry-in  $(C_n)$  and carry-out  $(C_{n+4})$  are active HIGH.

The ALU has three other status-oriented outputs. These are  $F_3$ , F=0, and overflow (OVR). The  $F_3$  output is the most significant (sign) bit of the ALU and can be used to determine positive or negative results without enabling the three-state data outputs.  $F_3$  is non-inverted with respect to the sign bit output  $Y_3$ . The F=0 output is used for zero detect. It is an open-collector output and can be wire OR'ed between microprocessor stices. F=0 is HIGH when all F outputs are LOW. The overflow output (OVR) is used to flag arithmetic operations that exceed the available two's complement number range. The overflow output (OVR) is HIGH when overflow exists. That is, when  $C_{n+3}$  and  $C_{n+4}$  are not the same polarity.

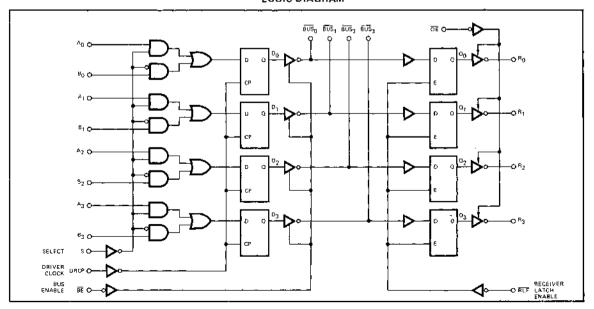

The ALU data output is routed to several destinations. It can be a data output of the device and it can also be stored in the RAM or the Q register, Eight possible combinations of ALU destination functions are available as defined by the 16, 17, and 18 microinstruction inputs. These combinations are shown in Figure 9.

The four-bit data output field (Y) features three-state outputs and can be directly bus organized. An output control (OE) is used to enable the three-state outputs. When OE is HIGH, the Y outputs are in the high-impedance state.

A two-input multiplexer is also used at the data output such that either the A-port of the RAM or the AŁU outputs (F) are selected at the device Y outputs. This selection is controlled by the I<sub>6</sub>, I<sub>7</sub>, and I<sub>8</sub> microinstruction inputs. Refer to Figure 4 for the selected output for each microinstruction code combination.

As was discussed previously, the RAM inputs are driven from a three-input multiplexer. This allows the ALU outputs to be entered non-shifted, shifted up one position (X2) or shifted down one position ( $\dot{\tau}2$ ). The shifter has two ports; one is labeled RAM0 and the other is labeled RAM3. Both of these ports consist of a buffer-driver with a three-state output and an input to the multiplexer. Thus, in the shift up mode, the RAM3 buffer is enabled and the RAM0 multiplexer input is enabled. Likewise, in the shift down mode, the RAM0 buffer and RAM3 input are enabled. In the no-shift mode, both buffers are in the high-impedance state and the multiplexer inputs are not selected. This shifter is controlled from the  $t_{\rm B}$ ,  $t_{\rm T}$  and  $t_{\rm B}$  microinstruction inputs as defined in Figure 9.

Similarly, the Q register is driven from a 3-input multiplexer. In the no-shift mode, the multiplexer enters the ALU data into the Q register. In either the shift-up or shift-down mode, the multiplexer selects the Q register data appropriately shifted up or down. The Q shifter also has two ports; one is labeled  $Q_0$  and the other is  $Q_3$ . The operation of these two ports is similar to the RAM shifter and is also controlled from  $I_6$ ,  $I_7$ , and  $I_8$  as shown in Figure 9.

The clock input to the Am2901 controls the RAM, the Q register, and the A and B data latches. When enabled, data is clocked into the Q register on the LOW-to-HIGH transition of the clock. When the clock input is HIGH, the A and B latches are open and will pass whatever data is present at the RAM outputs. When the clock input is LOW, the latches are closed and will retain the last data entered. If the RAM-EN is enabled, new data will be written into the RAM file (word) defined by the B address field when the clock input is LOW.

|    | MICE                                          | o cod |          | DURCE<br>ANDS |   |  |

|----|-----------------------------------------------|-------|----------|---------------|---|--|

| 12 | 2 I <sub>1</sub> I <sub>D</sub> Octal<br>Code |       |          | R             | s |  |

| L  | L                                             | L     | 0        |               | Q |  |

| L  | L                                             | н     | 1        | A             | 8 |  |

| L  | н                                             | L     | 2        | 0             | Ω |  |

| L  | н                                             | н     | 3        | 0             | 6 |  |

| н  | Ł                                             | L     | 4        | 0             | Α |  |

| н  | Ł                                             | н     | 5        | 5             | A |  |

| н  | н                                             | L     | 6        | D             | a |  |

| н  | н                                             | н     | 17   5 0 |               |   |  |

| Figure 7. | ALU Source                              | Operand Control. |

|-----------|-----------------------------------------|------------------|

|           | , , , , , , , , , , , , , , , , , , , , |                  |

|    | MICE           | RO COD                             | E   | ALU        |        |  |

|----|----------------|------------------------------------|-----|------------|--------|--|

| 15 | l <sub>4</sub> | l <sub>4</sub> l <sub>3</sub> Octa |     | Function   | Symbol |  |

| L  | L              | Ĺ                                  | 0   | R Plus S   | R+5    |  |

| L  | L              | н                                  | 1   | S Minus R  | 5 – R  |  |

| Ł  | H              | L.                                 | 2   | R Minus \$ | R - \$ |  |

| C  | H              | H                                  | 3   | RORS       | RVS    |  |

| н  | L              | L                                  | 1 4 | FI AND S   | RA \$  |  |

| н  | L              | н                                  | 5   | FI AND \$  | R∧s    |  |

| н  | H              | L.                                 | 6   | R EX-OR S  | R ¥ 5  |  |

| н  | н              | н                                  | 7   | R EX-NOR S | R∀S    |  |

Figure 8. ALU Function Control.

|                | MI |   | MICRO CODE |               |       | RAM<br>FUNCTION |       | Q-REG.<br>FUNCTION Y |        |                 | AM<br>FTER       | SHIF  | )<br>TER        |

|----------------|----|---|------------|---------------|-------|-----------------|-------|----------------------|--------|-----------------|------------------|-------|-----------------|

| l <sub>8</sub> | ı  | 7 | 16         | Octal<br>Code | Shift | Load            | Shift | Load                 | ОИТРИТ | RAMO            | RAM <sub>3</sub> | ao    | 03              |

| L              | ı  |   | L          | 0             | ×     | NONE            | NONE  | F→Q                  | F      | ×               | ×                | х     | ×               |

| L              | ı  | - | н          | 1             | ×     | NONE            | ×     | NONE                 | F      | ×               | х                | Х     | ×               |

| L              | 1  | 4 | L          | 2             | NONE  | F→B             | ×     | NONE                 | А      | ×               | х                | х     | ×               |

| ι              | ·  | 1 | н          | 3             | NONE  | F→B             | ×     | NONE                 | F      | х               | ×                | x     | х               |

| Н              |    | L | L          | 4             | DOMN  | F/2 → 8         | DOWN  | 0/2→0                | F      | F <sub>0</sub>  | IN <sub>3</sub>  | $a_0$ | IN <sub>3</sub> |

| н              | l  | - | н          | 5             | DOWN  | F/2 → B         | ×     | NONE                 | F      | Fo              | IN <sub>3</sub>  | ao    | x               |

| н              | ŀ  | - | L          | 6             | UP    | 2 F → B         | UP    | 20 → 0               | F      | INO             | F <sub>3</sub>   | ING   | α <sub>3</sub>  |

| н              | 1  | 4 | н          | 7             | UP    | 2F → B          | ×     | NONE                 | F      | 1N <sub>O</sub> | F <sub>3</sub>   | ×     | a <sub>3</sub>  |

X\* Don't care. Electrically, the shift pin is a TTL input internally connected to a three-state output which is in the high-impedance state.

Figure 9, ALU Destination Control.

| $\sum$  | 210 OCTAL                        | 0     | 1     | 2    | 3 -  | 4    | 5     | 6     | 7    |

|---------|----------------------------------|-------|-------|------|------|------|-------|-------|------|

| OCT 4 3 | ALU<br>Source<br>ALU<br>Function | A, Q  | А, В  | 0, 0 | О, В | O, A | Ð, A  | D, Q  | D, O |

| 0       | Cn≖L<br>RPlesS                   | A+Q   | A+B   | a    | В    | A    | D+A   | D+Q   | D    |

| L       | C <sub>n</sub> = H               | A+Q+1 | A+B+1 | Q+1  | B+1  | A+1  | D+A+1 | D+Q+1 | D+1  |

| 1       | Cn = L<br>S Minus R              | Q-A-1 | B-A-1 | Q1   | 8-1  | A-1  | A~D~1 | Q-0-1 | 7-0- |

|         | C <sub>n</sub> = H               | Q-A   | B-A   | a    | В    | A    | A-D   | Q-D   | p    |

| 2       | Cn = L<br>R Minus S              | A-Q-1 | A-8-1 | -Q-1 | -B-1 | -A-1 | D-A-1 | D-Q-1 | D-1  |

|         | Cn=H                             | A-O   | A-B   | Q    | -8   | -A   | D-A   | D-G   | D    |

| 3       | RORS                             | DVA   | ΑVΒ   | a    | 6    | А    | D∨A   | ο∨α   | D    |

| 4       | R AND S                          | ΑΛQ   | A ^ 8 | 0    | 0    | 0    | D^A   | D ^ C | o.   |

| 5       | R AND S                          | Ā∧ū   | ĀAB   | ā    | В    | A    | ō∧a   | ō∧q   | 0    |

| 6       | R EX-OR S                        | A 4 Q | AYB   | a    | 8    | A    | D∀A   | D∀Q   | ۵    |

| 7       | R EX-NORS                        | DYA   | A V B | ā    | Ē    | Ā    | D∀À   | ō∀ō   | ۵    |

<sup>+ =</sup> P1us; -- = Minus; V = OR; A = AND; ₩ = EX-OR

Figure 10. Source Operand and ALU Function Matrix.

B = Register Addressed by B inputs.

Up is toward MSB, Down is toward LSB.

| Octal<br> 543,  210      | Group  | Function                         |

|--------------------------|--------|----------------------------------|

| 4 0<br>4 1<br>4 5<br>4 6 | AND    | A \ Q<br>A \ B<br>D \ A<br>D \ Q |

| 3 0<br>3 1<br>3 5<br>3 6 | OR     | AVQ<br>AV8<br>DVA<br>DVQ         |

| 6 0<br>6 1<br>6 5<br>6 6 | EX-OR  | A ♥ Q<br>A ♥ B<br>D ♥ A<br>D ♥ Q |

| 7 0<br>7 1<br>7 5<br>7 6 | EX-NOR | Ā∀Q<br>Ā∀B<br>□∀Ā<br>□∀Q         |

| 7 2<br>7 3<br>7 4<br>7 7 | INVERT | B A D                            |

| 6 2<br>6 3<br>6 4<br>6 7 | PASS   | Q<br>B<br>A<br>D                 |

| 3 2<br>3 3<br>3 4<br>3 7 | PASS   | Q<br>B<br>A<br>D                 |

| 4 2<br>4 3<br>4 4<br>4 7 | "ZERO" | 0<br>0<br>0                      |

| 5 0<br>5 1<br>5 5<br>5 6 | MASK   | Ā∧Q<br>Ā∧B<br>Ō∧A<br>Ō∧Q         |

Figure 11. ALU Logic Mode Functions. (Cn Irrelevant)

# SOURCE OPERANDS AND ALU FUNCTIONS

There are eight source operand pairs available to the ALU as selected by the  $I_0$ ,  $I_1$ , and  $I_2$  instruction inputs. The ALU can perform eight functions; five logic and three arithmetic. The  $I_3$ ,  $I_4$ , and  $I_5$  instruction inputs control this function selection. The carry input,  $C_n$ , also affects the ALU results when in the arithmetic mode. The  $C_n$  input has no effect in the logic mode. When  $I_0$  through  $I_5$  and  $C_n$  are viewed together, the matrix of Figure 10 results. This matrix fully defines the ALU/source operand function for each state.

The ALU functions can also be examined on a "task" basis, i.e., add, subtract, AND, OR, etc. In the arithmetic mode, the carry will affect the function performed while in the logic mode, the carry will have no bearing on the ALU output. Figure 11 defines the various logic operations that the Am2901 can perform and Figure 12 shows the arithmetic functions of the device. Both carry-in LOW ( $C_{\rm R}=0$ ) and carry-in HIGH ( $C_{\rm R}=1$ ) are defined in these operations.

| Octal                              | C <sub>n</sub> = 0 | (Low)      | C <sub>n</sub> = 1 | (High)     |

|------------------------------------|--------------------|------------|--------------------|------------|

| <sup>1</sup> 543, <sup>1</sup> 210 | Group              | Function   | Group              | Function   |

| 0.0                                |                    | A+Q        |                    | A+Q+1      |

| 0 1                                | ADD                | A+B        | ADD plus           | A+B+1      |

| 0.5                                |                    | D+A        | опе                | D+A+1      |

| 0.6                                |                    | D+Q        |                    | D+Q+1      |

| 0 2                                |                    | a          |                    | Q+1        |

| 0 3                                | PASS               | В          | Increment          | B+1        |

| 0.4                                |                    | A          |                    | A+1        |

| 0 7                                |                    | D          |                    | D+1        |

| 1 2                                |                    | Ω-1        | •                  | a          |

| 1 3                                | Decrement          | B-1        | PASS               | B          |

| 14                                 |                    | A-1        | !                  | Α          |

| 2 7                                |                    | D-1        |                    | D          |

| 2 2                                |                    | <b>Q-1</b> |                    | -0         |

| 2 3                                | 1's Comp.          | _B—1       | 2's Comp.          | <b>–</b> В |

| 2 4                                |                    | A-1        | (Negate)           | -A         |

| 1 7                                |                    | _D_1       |                    | –D         |

| 1.0                                |                    | Q-A-1      |                    | Q-A        |

| 1 1 1                              | Subtract           | B-A-1      | Subtract           | B-A        |

| 1.5                                | (1's Comp)         | A-D-1      | (2's Comp)         | A-D        |

| 1.6                                |                    | Q-0-1      | ļ                  | Q-D        |

| 2 0                                |                    | A-Q-1      |                    | A-Q        |

| 2 1                                |                    | A-8-1      |                    | A-B        |

| 2.5                                |                    | D-A-1      | l                  | D-A        |