# 8085A

8-Bit Microprocessor

#### MILITARY INFORMATION

## DISTINCTIVE CHARACTERISTICS

- SMD/DESC qualified

- 3- and 5-MHz selections available

- On-chip system controller; advanced cycle status information available for large system control

- Four vectored interrupts (one is non-maskable)

- On-chip clock generator (with external crystal, LC or A/C network)

- · Serial-in/serial-out port

- Decimal, binary, and double-precision arithmetic

- Direct addressing capability to 64K bytes of memory

- 1.3 µs instruction cycle (8085A)

- 0.8 μs instruction cycle (8085A-2)

- 100% software-compatible with 8080A

Single +5 V power supply

#### GENERAL DESCRIPTION

The 8085A is a new generation, complete 8-bit parallel central processing unit (CPU). Its instruction set is 100% software compatible with the 8080A microprocessor. Specifically, the 8085A incorporates all of the features that the 8224 (clock generator) and 8228 (system controller) provided for the 8080A. The 8085A-2 is a faster version of the 8085A. The 8085A is a 3-MHz CPU with 10% supply tolerances and lower power consumption.

The 8085A uses a multiplexed data bus. The address is split between the 8-bit address bus and the 8-bit data bus. The on-chip address latches of 8155H/56H memory products allow a direct interface with 8085A. The 8085A components, including various timing-compatible support chips, allow system speed optimization.

# **BLOCK DIAGRAM** POWER | --- 444 SUPPLY | --- GHO BD003790 Publication # 09231 Rev. Issue Date: November 1987

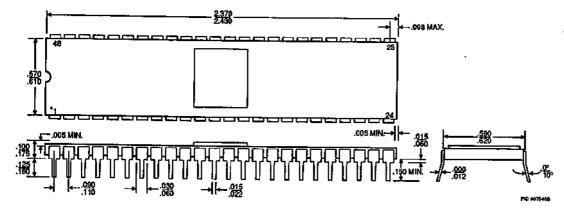

#### CONNECTION DIAGRAM Top View DIPs

CD005564

Note: Pin 1 is marked for orientation.

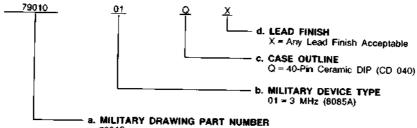

#### MILITARY ORDERING INFORMATION

#### Standard Military Drawing (SMD)/DESC Products

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. Standard Military Drawing (SMDI/DESC products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for SMD/DESC products is formed by a combination of: a. Military Drawing Part Number b. Device Type c. Case Outline d. Lead Finish

#### 8-Bit Microprocessor

#### Valid Combinations

| Valid Combinations |  |  |    |  |  |  |

|--------------------|--|--|----|--|--|--|

| 7901001            |  |  | QΧ |  |  |  |

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released valid combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### MILITARY ORDERING INFORMATION (Cont'd.)

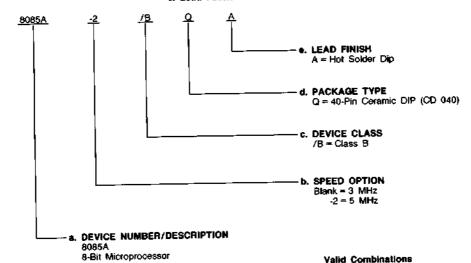

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

#### Valid Combinations 6085A 8085A-2

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, B, 9, 10, 11.

#### ABSOLUTE MAXIMUM RATINGS

####

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Military (M) Devices          |              |

|-------------------------------|--------------|

| Temperature (T <sub>C</sub> ) | 55 to +125°C |

| Supply Voltage (VCC)          | 5 V ±10%     |

| Supply Current (ICC)          | 200 mA       |

Operating ranges define those limits between which the functionality of the device is guaranteed.

**DC CHARACTERISTICS** over operating range (for SMD/DESC and APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol | Parameter<br>Description    | Test Conditions                                                      | Min.         | Max.                   | Unit       |

|---------------------|-----------------------------|----------------------------------------------------------------------|--------------|------------------------|------------|

| V <sub>IL</sub>     | Input LOW Voltage           | V <sub>CC</sub> = 5 V ± 10%                                          | -0.5*        |                        |            |

| ViH                 | Input HIGH Voltage          | V <sub>CC</sub> = 5 V ± 10%                                          |              |                        |            |

| V <sub>OL</sub>     | Output LOW Voltage          | IOL = 2 mA, VCC = 5 V ± 1090                                         | - 18         | 0 45                   | <u>v</u> - |

| Voн                 | Output HIGH Voltage         | I <sub>OH</sub> = -400 μA, V <sub>O</sub> = 5 V 10 %                 | 24           | 043                    |            |

| lcc                 | Power Supply Current        | Vcc (No. )                                                           | <b>*</b> *** | 200                    | <u>v</u>   |

| հլ 1                | Input Leakage, Except Pin 1 | NIN = CC to 0 V                                                      | · .          | ± 10                   | MA         |

| 11.2                | Input Leakage, Pin 1        | V, VIN = VCC to 0 V                                                  |              | ±70                    | <u>μ</u> Α |

| 110                 | Output Legica               | V <sub>CC</sub> = 5.5 V, V <sub>OUT</sub> = V <sub>CC</sub> to .45 V |              | ±10                    | μA         |

| VILR                | Inpet OW seed, NESST        | V <sub>CC</sub> = 5 V ±10%                                           | -0.5*        | +0.8                   | <u>μA</u>  |

| V <sub>IHR</sub>    | Inpute firm Nevel RESET     | Vcc = 5 V ±10%                                                       | 2.4          |                        | <u>`</u>   |

| VHY                 | Hysteresis, RESET           | Vcc = 5 V ±10%                                                       | 0.25         | V <sub>CC</sub> + 0.5* |            |

\*Guaranteed by design; not tested.

Notes: 1, Icc is measured while running a functional pattern with no loads applied.

#### SWITCHING CHARACTERISTICS over operating range (for SMD/DESC and APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted)

| I MI MILLOTOT    |                                                              | 8085A<br>(Note 2) |                                                   | 8085A-2<br>(Note 2) |                |               |

|------------------|--------------------------------------------------------------|-------------------|---------------------------------------------------|---------------------|----------------|---------------|

|                  | Parameter Description                                        | Min.              | Max.                                              | Min.                | Max.           | Unit          |

|                  | CLK Cycle Period                                             | 320               | 2000                                              | 200                 | 2000           | ns            |

| lcyc             | CLK LOW Time (Standard CLK Loading)                          | 60                |                                                   | 40                  |                | ns            |

| <u> </u>         | CLK HIGH Time (Standard CLK Loading)                         | 120               |                                                   | 70                  |                | ns            |

| <u>l2</u>        | CLK Rise and Fall Time                                       |                   | 30                                                |                     | 30             | ns            |

| <u>կ, կ</u>      | X <sub>1</sub> Rising to CLK Rising                          | 20                | 120                                               | 20                  | 100            | ns            |

| XKPI             | X <sub>1</sub> Rising to CLK Falling                         | 20                | 150                                               | 20                  | 110            | ns            |

| XKF              | A <sub>8-15</sub> Valid to Leading Edge of Control (Note 1)  | 270               |                                                   | 115                 |                | ns            |

| tac              | A <sub>0.7</sub> Valid to Leading Edge of Control            | 240               |                                                   | 115                 |                | ns            |

| tacl             |                                                              |                   | 575                                               |                     | 350            | ns            |

| IAD              | A <sub>0-15</sub> Valid to Valid Data In                     |                   |                                                   |                     | 0              | nes           |

| <sup>t</sup> afr | Address Float After Leading Edge of READ (INTA)              |                   | 0 _                                               | 50                  | ļ              | ns            |

| lal .            | A <sub>8-15</sub> Valid Before Trailing Edge of ALE (Note 1) | 90                |                                                   | 50                  | <del> </del>   | ns            |

| TALL             | A <sub>0-7</sub> Valid Before Trailing Edge of ALE           | 70                | L 4                                               | 20                  | 100            | ns            |

| YBA              | READY Valid from Address Valid                               |                   | 220                                               |                     | 100            | ns            |

| 1CA              | Address (A <sub>8-15</sub> ) Valid After Control             | 120               |                                                   | 50                  | <del> </del>   | 165           |

| toc              | Width of Control LOW (RD, WR, INTA) Edge of ALE              | 400               | Y                                                 | 230                 |                | ns            |

| lcr              | Trailing Edge of Control to Leading Edge of ALE              | 50                | 690                                               | 25                  |                | ns            |

| tow              | Data Valid to Trailing Edge of WRITE                         | .420              |                                                   | 230                 | <del></del>    | ns.           |

| 1HABE            | HLDA to Bus Enable                                           |                   | 210                                               |                     | 150            | ns            |

|                  | Bus Float After HLDA                                         |                   | 210                                               |                     | 150            | ns            |

| LHABF            | HLDA Valid to Trailing Edge of CLK                           | 110               |                                                   | 40                  | <u> </u>       | n\$           |

| thack            | HOLD Hold Time                                               | <b>3</b> 0        |                                                   | 0                   | <u> </u>       | n\$           |

| thOH             | HOLD Setup Time to Trailing Edge of CLK                      | 170               |                                                   | 120                 |                | n\$           |

| thos             | INTR Hold Time                                               | 0                 |                                                   | 0                   |                | ns            |

| tins             | INTR. RST, and TRAP Setup Time to                            | 160               |                                                   | 150                 | T              | ns            |

| - CP/III         | Falling Edge of CLK                                          | 100               | <del></del>                                       | 50                  | 1              | nş            |

| tla              | Address Hold Time After 45 Trailing Edge of ALE 40 120       | 130               | <u> </u>                                          | 60                  |                | ns            |

| 1LC              | of Control                                                   | l                 | <del>                                      </del> | 50                  |                | ns            |

| tLCK             | ALE LOW Dunna CLASSIC HOLD                                   | 100               | 160                                               | 1                   | 270            | ns            |

| LDA              | ALE to Valid Data Read                                       | ļ                 | 460                                               | <del>- </del> -     | 120            | ns            |

| tLOW             | ALE to Valid Data During Write                               | <del> </del>      | 200                                               | 80                  | 120            | ns            |

| †LL              | ALE Width                                                    | 140               | +                                                 |                     | 30             | ns            |

| tLRY             | ALE to READY Stable                                          | ļ                 | 110                                               | ┦                   | <del>  ~</del> | <del>-1</del> |

| TRAE             | Trailing Edge of READ to Re-Enabling of Address              | 150               |                                                   | 90                  | <u> </u>       | n\$           |

| IRD              | READ (or INTA) to Valid Data                                 |                   | 300                                               |                     | 150            | ns            |

| tev              | Control Trailing Edge to Leading Edge of Next Control        | 400               |                                                   | 220                 |                | ns            |

|                  | Data Hold Time After READ INTA (Note 6)                      | 0                 |                                                   | 0                   |                | ns            |

| URIDH            | READY Hold Time                                              | 0                 |                                                   | 0                   |                | n-s           |

| tays             | READY Setup Time to Leading Edge                             | 110               |                                                   | 100                 |                | ns            |

|                  | of CLK  Data Valid After Trailing Edge of WRITE              | 100               | +                                                 | 60                  |                | ns            |

| two              | LEADING Edge of WRITE to Data Valid                          | +                 | 40                                                | 1                   | 20             | ns            |

Notes: 1. A<sub>6</sub> -A<sub>15</sub> address Specs apply to ID/M. S<sub>0</sub>, and S<sub>1</sub>, except A<sub>8</sub> -A<sub>15</sub> are undefined during T<sub>4</sub> -T<sub>6</sub> of OF cycle; whereas, IO/M. S<sub>0</sub>, and S<sub>1</sub> are stable.

2. Test conditions: I<sub>CYC</sub> = 320 ns (8085A)/200 ns (8085A-2); C<sub>L</sub> = 100 pF, V<sub>CC</sub> = 5 V ±10%, V<sub>IL</sub> = .45 V, V<sub>IH</sub> = 2.4 V; V<sub>OL</sub> = .8 V, V<sub>OH</sub> = 2.0 V.

3. For all output timing where C<sub>L</sub> = 150 pF use the following correction factors:

25 pF < C<sub>L</sub> < 150 pF: -0.10 ns/pF

150 pF < C<sub>L</sub> < 300 pF; +0.30 ns/pF

- 4. Output timings are measured with purely capacitive load.

- 5. To calculate timing specifications at other values of toyo use Table 3 on page 3-191 of the MOS Microprocessors and Peripherals Data Book (Order #09067A)

- 6. Data hold time is guaranteed under all loading conditions.

# **CHAPTER 6**

# **General Information**

T-90-20

#### **PACKAGE OUTLINES\***

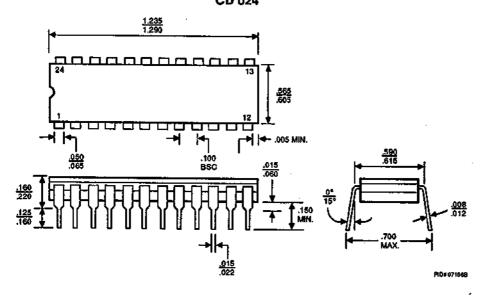

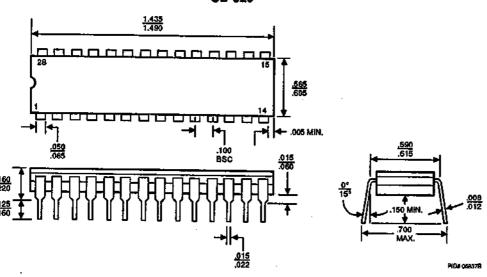

Ceramic DIPs (CD) **CD 024**

**CD 028**

\* For reference only.

CHAPTER 6

General Information

T-90-20

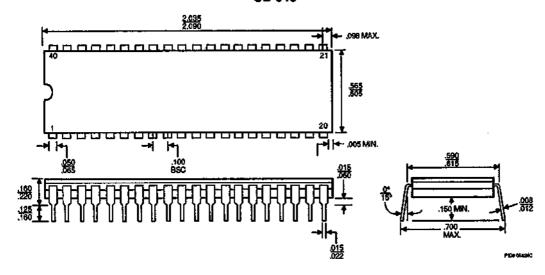

#### **PACKAGE OUTLINES (Continued)**

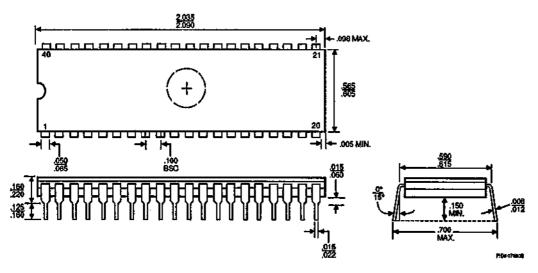

# Ceramic DIPs (CD) (Continued) CD 040

#### **CDV040**

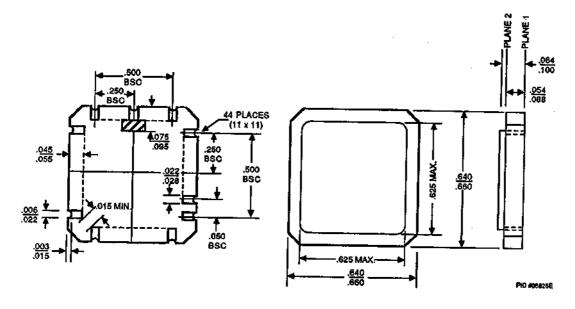

#### **PACKAGE OUTLINES (Continued)**

T-90-20

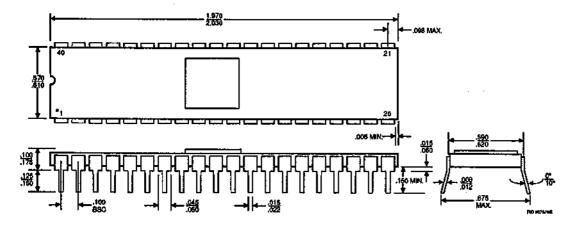

# Ceramic Sidebrazed DIPs (SD)

SD 040

SD 048

96D D

T-90-20

CHAPTER 6

General Information

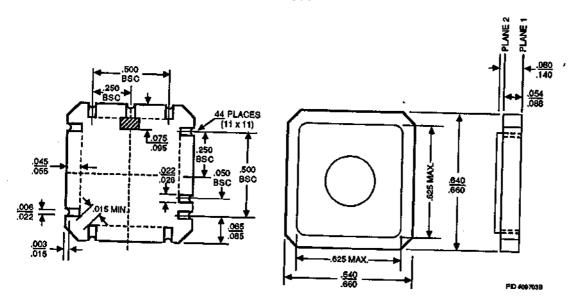

## **PACKAGE OUTLINES (Continued)**

#### Ceramic Leadless Chip Carriers (CL/CLV) **CL 044**

**CLV044**

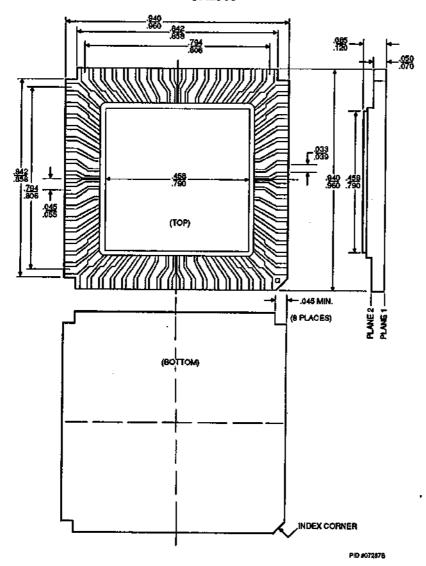

#### **PACKAGE OUTLINES (Continued)**

# 68-Pin Square Leadless Chip Carrier (CA2) CA2068

T-90-20

**CHAPTER 6** General Information

#### **PACKAGE OUTLINES (Continued)**

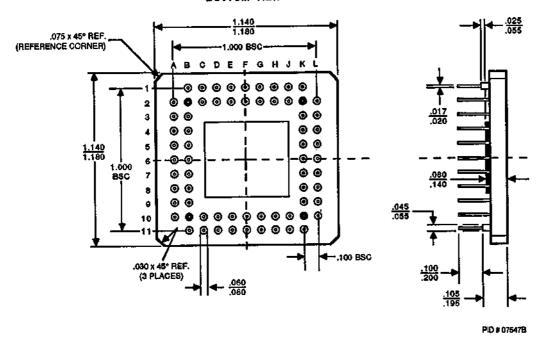

#### Ceramic Pin-Grid-Array Package (CG/CGX) **CGX068**

#### **BOTTOM VIEW**