# Word Alterable 16K Bit Electrically Erasable and Programmable ROM

#### **FEATURES**

- No high voltages +5V only operation in all modes

- Electrically Word or Block Erasable

- 2048 word x 8 bit organization, fully decoded

- Access time: 300ns maximum

- 20ms Erase and Write times

- Minimum of 10 years' non-volatile data retention

- N-Channel, Si-Gate SNOS technology

- Unlimited Read capability

- Conforms to JEDEC byte-wide pinout standards

- Functionally equivalent to Intel 2816 EEPROM

- Similar pinout to 2716 EPROM

#### DESCRIPTION

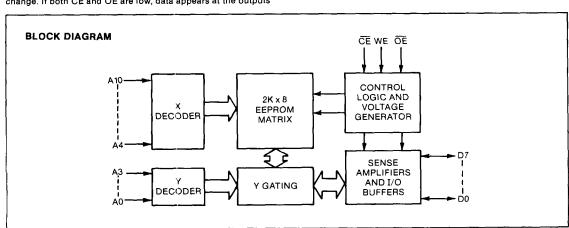

The ER5916 is a high speed electrically word or block erasable and programmable memory fabricated in General Instrument's SNOS technology. Its microprocessor and microcomputer compatible architecture makes it very easy to interface with most popular processors, as does its 300ns maximum access time.

Making it even more attractive to the system design engineer is its +5V only operation in all modes; no high voltages are required for erasing and writing. The ER5916, therefore, offers increased flexibility and opportunities for innovation in new designs since a large amount of data can now be stored in a non-volatile medium and selected portions of it altered with great ease during normal system operation.

This device conforms to JEDEC byte-wide family standards and is functionally compatible with the ER5816 and the Intel 2816 EEPROM. Some differences of pin functions and control logic levels are necessary due to the ER5916's 5V only operation. Refer to the comparison of these two devices included in this data sheet.

Bus contention problems are minimized by the two-line control provided by CHIP ENABLE  $(\overline{\text{CE}})$  and OUTPUT ENABLE  $(\overline{\text{OE}})$ . Programming operations are controlled by one TTL level input, WRITE ENABLE (WE).

### OPERATION

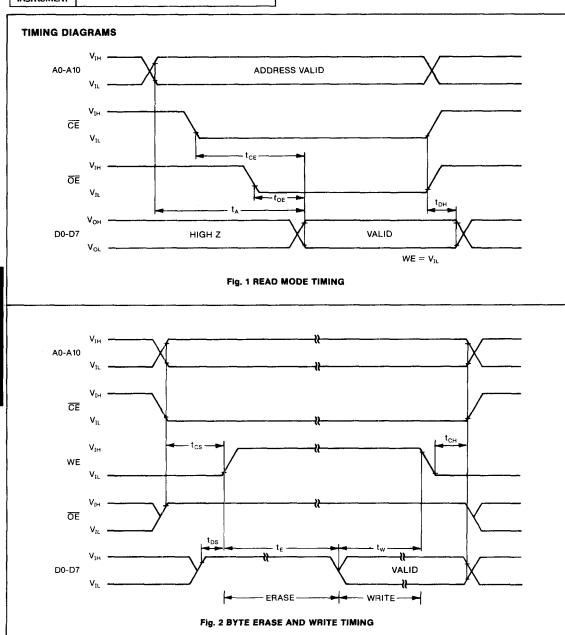

Reading is a ripple-through operation initiated by an address change. If both CE and OE are low, data appears at the outputs

| 24 PIN DUAL IN LINE        |                          |

|----------------------------|--------------------------|

| Тор                        | View                     |

| A7 □ •1                    | 24 (+5V) V <sub>CC</sub> |

| A6 □ 2                     | 23 A8                    |

| A5 □ 3                     | 22 🗖 A9                  |

| A4 □4                      | 21 D WE                  |

| АЗ □ 5                     | 20 D OE                  |

| A2 ☐ 6                     | 19 🗀 A10                 |

| A1 口7                      | 18 🗗 🙃                   |

| A0 ☐8                      | 17 🗗 07                  |

| ₽0 🗗 9                     | 16 🖰 06                  |

| D1 🗖 10                    | 15 D5                    |

| D2 🗆 11                    | 14 D4                    |

| V <sub>ss</sub> (GND) ☐ 12 | 13 D3                    |

after the normal access time,  $T_A$  has elapsed.  $\overline{OE}$ , when held high, disables the outputs and allows fast access to data when pulsed low.

Erasing and writing of one byte are essentially the same except that all input data bits must be held high for an erase operation.

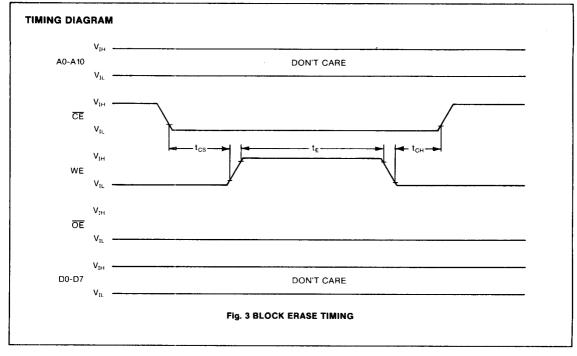

A chip erase mode is also provided for applications such as program storage in which software updates are made at infrequent intervals. In this mode, all locations are erased into the '1' state with the same, 20ms pulse as required for a single byte erase.

There is a trade-off to be made between the data retention time and the number of Erase/Write cycles performed per location. A gradual, logarithmic reduction in retention time is experienced as the number of Erase/Write cycles increases. The specified limit is merely one point on this curve and does not imply a sudden cut-off or end of life. After 10<sup>5</sup> cycles a typical retention time is 1 year.

## PIN CONFIGURATION

| DEVICE          | 2716            |                  |                      |                  |                   | ER              | ER5916                  |                  |                 |                 |                 |                  |

|-----------------|-----------------|------------------|----------------------|------------------|-------------------|-----------------|-------------------------|------------------|-----------------|-----------------|-----------------|------------------|

| MODE            | CE<br>(18)      | ŌĒ<br>(20)       | V <sub>PP</sub> (21) | 1/0              | CE<br>(18)        | ŌĒ<br>(20)      | V <sub>PP</sub><br>(21) | I/O              | CE<br>(18)      | ŌE<br>(20)      | WE<br>(21)      | 1/0              |

| READ            | V <sub>IL</sub> | V <sub>I)</sub>  | +5                   | D <sub>OUT</sub> | VIL               | VIL             | +4 to +6                | D <sub>out</sub> | V <sub>IL</sub> | V <sub>IL</sub> | VIL             | D <sub>OUT</sub> |

| BYTE ERASE      | _               | -                | _                    | <b>i</b> - i     | V <sub>IL</sub>   | V <sub>IH</sub> | +21                     | $V_{IH}$         | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub>  |

| BYTE WRITE      | Pulsed          | $V_{IH}$         | +25                  | DIN              | $V_{IL}$          | V <sub>IH</sub> | +21                     | D <sub>IN</sub>  | V <sub>1∟</sub> | V <sub>IH</sub> | VIH             | DIN              |

| CHIP ERASE      | 1               | ULTRAVI          | OLET                 | ļ                | $V_{IL}$          | +8 to +15       | +21                     | V <sub>IH</sub>  | VIL             | V <sub>IL</sub> | V <sub>IH</sub> | Don't Care       |

| STANDBY         | V <sub>IH</sub> | Don't Care       | +5                   | High-Z           | $V_{\mathrm{IH}}$ | Don't Care      | +4 to +6                | High-Z           | V <sub>IH</sub> | Don't           | Care            | High-Z           |

| PROGRAM INHIBIT |                 | V <sub>I-4</sub> | +25                  | High-Z           | VIH               | Don't           | Care                    | High-Z           | VIH             | Don't           | Care            | High-Z           |

| T       | op View |                          | Top View    |                          | Top View                   |                          |

|---------|---------|--------------------------|-------------|--------------------------|----------------------------|--------------------------|

| A7 🗆 •1 | 0       | 24 V <sub>CC</sub> (+5V) | A7 🗖 •1     | 24 V <sub>CC</sub> (+5V) | A7 🗆 •1                    | 24 V <sub>CC</sub> (+5V) |

| A6 🗆 2  |         | 23 A8                    | A6 🗖 2      | 23 A8                    | A6 □ 2                     | 23 🗀 A8                  |

| A5 🗖 3  |         | 22 A9                    | A5 🗖 3      | 22 A9                    | A5 □3                      | 22 🗖 A9                  |

| A4 🗖 4  |         | 21 Vpp                   | A4 🗖 4      | 21 VPP                   | A4 🗖 4                     | 21 D WE                  |

| A3 🗆 5  |         | 20 □ 0 ₺                 | A3 🗗 5      | 20 DE                    | A3 ☐ 5                     | 20 D OE                  |

| A2 🗖 6  | 0740    | 19 A10                   | A2 G ER5816 | 19 🗖 A10                 | A2 G ER5916                | 19 🗖 A10                 |

| A1 🗆 7  | 2716    | 18 □ CE                  | A1 07       | 18 🗖 ČE                  | A1 🗆 7                     | 18 🗖 CE                  |

| A0 🗆 8  |         | 17 🖸 D7                  | A0 🗖 8      | 17 🗖 07                  | A0 🗖 8                     | 17 🗀 D7                  |

| D0 🛮 9  |         | 16 D6                    | oo d э      | 16 D D6                  | D0 🗖 9                     | 16 🗀 D6                  |

| D1 🖸 10 |         | 15 D5                    | D1 🗖 10     | 15 🗖 D5                  | D1 ☐ 10                    | 15 D5                    |

| D2   11 |         | 14 D D4                  | D2 🗔 11     | 14 🗁 🖸                   | D2 🗖 11                    | 14 🗖 D4                  |

| GND 12  |         | 13 🗖 🖂                   | GND [ 12    | 13 D3                    | V <sub>ss</sub> (GND) ☐ 12 | 13 D3                    |

# MODES OF OPERATION

| CE | ŌĒ    | WE   | D0-D7            | OPERATING MODE  |                                                                                                                                                                                  |  |  |  |  |  |

|----|-------|------|------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0  | 0     | 0    | D <sub>out</sub> | READ            | $-$ Data stored at the addressed location appears at the output pins a time, $t_{\text{A}}$ after an address change.                                                             |  |  |  |  |  |

| 0  | 1     | 1    | $D_{IN} = 1$     | BYTE ERASE      | - Only the selected word is erased to the '1' state.                                                                                                                             |  |  |  |  |  |

| 0  | 1     | 1    | D <sub>IN</sub>  | BYTE WRITE      | <ul> <li>Data at the data inputs is written into the selected location.</li> <li>Note that correct writing may only occur if the location has been previously erased.</li> </ul> |  |  |  |  |  |

| 0  | 0     | 1    | Don't Care       | BLOCK ERASE     | - The entire contents of memory is erased to the '1' state.                                                                                                                      |  |  |  |  |  |

| 1  | Don't | Care | High-Z           | CHIP DESELECTED |                                                                                                                                                                                  |  |  |  |  |  |

# PIN FUNCTIONS

| NAME            | FUNCTION                                                         |

|-----------------|------------------------------------------------------------------|

| A0-A10          | 11-Bit Word Address                                              |

| D0-D7           | Data input and output ports — high impedance in deselected mode. |

| V <sub>cc</sub> | Power supply input. Normally $\pm 5 \pm 10\%$ volts.             |

| V <sub>ss</sub> | Supply pin. Normally at ground potential.                        |

| CE              | Chip enable input.                                               |

| ÕĒ              | Output enable input.                                             |

| WE              | Write enable input.                                              |

only and is not guaranteed.

implied.

\*Exceeding these ratings could cause permanent dam-

age. Functional operation of this device at these condi-

tions, or any other conditions outside those indicated in

the operational sections of this specification, is not

Data labeled "typical" is presented for design guidance

#### **ELECTRICAL CHARACTERISTICS**

### Maximum Ratings\*

All inputs and outputs with respect to Ground except pins 20 and 21 ......+6V to -0.3V Input voltage, pins 20 and 21 with respect to Ground ..... +24V to -0.3V Storage Temperature (unpowered and without data retention) .....-65°C to +150°C Soldering Temperature of Leads (10 seconds) . . . . . . . . . +300° C

#### Standard Conditions (unless otherwise noted):

$V_{SS} = GND$

$V_{CC} = +5 \pm 5\%$  volts

Operating Temperature Ranges (T<sub>A</sub>): 0° C to +70° C -40°C to +85°C

-55°C to +125°C

### DC CHARACTERISTICS

| Characteristic                          | Sym             | Min             | Тур | Max                  | Units | Conditions              |

|-----------------------------------------|-----------------|-----------------|-----|----------------------|-------|-------------------------|

| Input Logic "1" (except pins 20 and 21) | V <sub>IH</sub> | 2.0             |     | V <sub>CC</sub> +0.3 | V     |                         |

| Input Logic "1" (pins 20 and 21)        | V <sub>IC</sub> | 2.0             | l – | + 22                 | V     | Į.                      |

| nput Logic "0"                          | V <sub>IL</sub> | -0.1            | -   | + 0.8                | ٧     |                         |

| Output Logic "1"                        | V <sub>OH</sub> | 2.4             |     | V <sub>cc</sub>      | ν     | $I_{OH} = -400 \mu A$   |

| Output Logic "0"                        | V <sub>OL</sub> | V <sub>ss</sub> |     | 0.4                  | ٧     | I <sub>OL</sub> = 2.1mA |

| nput Leakage Current                    | IIL             | <u> </u>        |     | 10                   | μΑ    | $V_{IN} = 5.25V$        |

| ower Supply Requirements                | 1               |                 | [   | 1                    |       | ł                       |

| CC Supply:                              |                 | 1               | ļ   |                      |       |                         |

| Chip Selected                           | Icc             | <u> </u>        | 40  | 90                   | mΑ    |                         |

| Chip Deselected                         | Icc             | l –             | 15  | 25                   | mA    | Į.                      |

| Power Dissipation:                      | "               |                 |     | 1                    |       |                         |

| Chip Selected                           | P <sub>D</sub>  | <u> </u>        | 200 | 450                  | mW    | 1                       |

| Chip Deselected                         | P <sub>D</sub>  |                 | 75  | 125                  | mW    |                         |

NOTE 1:  $(T_A) = -40$  to  $+85^{\circ}$  C  $V_{CC} = +5 \pm 5\%$ , unless otherwise specified.

#### **AC CHARACTERISTICS**

| Characteristic                        | Sym              | Min         | Тур | Max | Units | Conditions                                      |  |  |

|---------------------------------------|------------------|-------------|-----|-----|-------|-------------------------------------------------|--|--|

| Input capacitance                     | C <sub>I</sub>   | <del></del> | 4   | 6   | pF    | V <sub>IN</sub> = 0V                            |  |  |

| Output capacitance                    | Co               | -           |     | 10  | pF    | $V_{OUT} = 0V$                                  |  |  |

| Read Mode                             | 1                | <b>[</b>    | İ   |     |       | All AC Test conditions:                         |  |  |

| Access time — Address to output delay | l t <sub>A</sub> | _           | -   | 300 | ns    | Output load: 1TTL gate + C <sub>L</sub> = 100pF |  |  |

| CE to output delay                    | t <sub>CE</sub>  | i –         | i – | 350 | ns    |                                                 |  |  |

| OE to output delay                    | toE              | 10          |     | 120 | ns    | Input pulse levels: 0.5V to 2.2V                |  |  |

| Data hold time                        | t <sub>DH</sub>  | -           | -   | 100 | ns    |                                                 |  |  |

| Byte Erase/Write Mode                 | 1                |             | 1   | ì   | ì     |                                                 |  |  |

| Address, CE and OE setup time         | tcs              | 200         | -   | -   | ns    |                                                 |  |  |

| Data setup time                       | tos              | 100         | -   | -   | ns    |                                                 |  |  |

| Address, data, CE and OE hold time    | t <sub>CH</sub>  | 2           | -   | -   | μs    | 1                                               |  |  |

| Erase time                            | t <sub>E</sub>   | 20          | 25  | 30  | ms    | İ                                               |  |  |

| Write time                            | tw               | 20          | 25  | 30  | ms    |                                                 |  |  |

| Block Erase Mode                      |                  |             | l   | ţ.  | 1     |                                                 |  |  |

| CE setup time                         | tcs              | 200         | -   | _   | ns    |                                                 |  |  |

| CE hold time                          | t <sub>CH</sub>  | 2           | ] - | -   | μs    |                                                 |  |  |

| Block erase time                      | t <sub>BE</sub>  | 20          | 25  | 30  | ms    |                                                 |  |  |

#### **MEMORY CHARACTERISTICS**

| Characteristic                             | Sym             | Min      | Тур                               | Max | Units | Conditions |

|--------------------------------------------|-----------------|----------|-----------------------------------|-----|-------|------------|

| Erase time — byte or block                 | t <sub>E</sub>  | 20       | 25                                | 30  | ms    |            |

| Erased state                               | V <sub>E</sub>  |          | V <sub>1H</sub> , V <sub>OH</sub> | _   | -     |            |

| Write time                                 | tw              | 20       | 25                                | 30  | ms    |            |

| Written state                              | V <sub>w</sub>  | <u> </u> | VIL VOL                           | _   | · –   |            |

| Data retention time (powered or unpowered) | ts              | 10       | -                                 |     | Yrs   |            |

| Number of Erase/Write cycles per byte      | N <sub>EW</sub> | 10⁴      | 1 - 1                             | _   | l –   | See Note 1 |

| Number of Read accesses between refresh    |                 | -        | -                                 | _   | –     | Unlimited  |

### NOTE: