# EMM8108

# SEMI 8108 300NSEC, STATIC, TTL IN/OUT 1024 x 8 N-MOS RAM SEMI 8108 500NSEC, STATIC, TTL IN/OUT 1024 x 8 N-MOS RAM

# **FEATURES**

- 1024 words X 8 bits

- EPROM, PROM, ROM pinout compatible

- Common I/O bus

- Single +5V power supply

- No maximum limit on Chip Enable (CE) pulse width

- 300 or 500 nsec maximum access time

- Less than 60 mW power (disabled)

- Less than 270 mW power (enabled)

#### **GENERAL DESCRIPTION**

EMM SEMI'S 8108 is a 8192-bit static RAM, ideally suited for microprocessor applications, with a choice of 300 or 500 nanosecond maximum access time. The 8108 has common data input/output pins for connection to a data bus. It requires only a single +5 volt power supply, and is TTL compatible on all inputs and outputs. This device also has a low power disabled mode which dissipates less than 60 mW power.

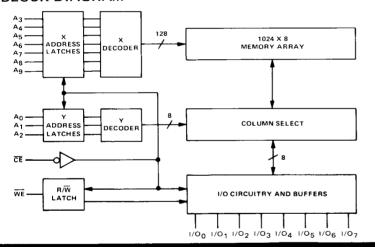

## **BLOCK DIAGRAM**

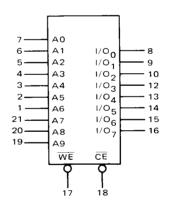

### LOGIC SYMBOL

# PIN CONFIGURATION

| CE | WE            | I/O <sub>n</sub> | STATUS   | MODE       |

|----|---------------|------------------|----------|------------|

| Н  | Don't<br>Care | High<br>Z        | Disabled | Standby    |

| L  | Н             | Data             | Enabled  | Read       |

| L  | Ĺ             | L                | Enabled  | Write<br>O |

| L  | L.            | Н                | Enabled  | Write<br>1 |

# PIN NAMES

| An | Address Inputs                    |

|----|-----------------------------------|

| CE | Chip Enable Input                 |

| WE | Write Enable Control Input        |

|    | · · · · · · · · · · · · · · · · · |

1/O<sub>n</sub> Data Bus Input/Output PinsVCC +5V Power Supply

Vcc OV Power Supply

| A6 □   | 1  | 22 | □ v <sub>cc</sub>  |

|--------|----|----|--------------------|

| A5 🗆   | 2  | 21 | □ A7               |

| A4 🗀   | 3  | 20 | □ A8               |

| A3 🗀   | 4  | 19 | □ A <sub>9</sub>   |

| A2 🗀   | 5  | 18 | □ cĒ               |

| A1 🗆   | 6  | 17 | □ ME               |

| A0 □   | 7  | 16 | 1/07               |

| 1/00 □ | 8  | 15 | 1/06               |

| 1/01   | 9  | 14 | □ 1/0 <sub>5</sub> |

| 1/02   | 10 | 13 | □ 1/0 <sub>4</sub> |

| ∨ss □  | 11 | 12 | <u></u> 1/0₃       |

8108

# EMM SEMI, INC.

A Subsidiary of Electronic Memories & Magnetics Corporation • 2000 West 14th Street, Tempe, Arizona 85281 • (602) 968-4431

# EMM SEMI 8108 300/500 NSEC, STATIC, TTL IN/OUT 1024x8 N-MOS RAM

# RECOMMENDED OPERATING CONDITIONS: (T<sub>AMB</sub> = 0°C to 70°C)

| PARAMETER        | SYMBOL          | MIN  | NOM | MAX  | UNIT |

|------------------|-----------------|------|-----|------|------|

| Supply Voltage   | v <sub>cc</sub> | 4.75 | 5.0 | 5.25 | V    |

| Input High Level | V <sub>IH</sub> | 2.0  | _   | 5.25 | V    |

| Input Low Level  | VIL             | -0.5 | -   | 0.8  | V    |

# DC CHARACTERISTICS: $T_A = 0^{\circ}C$ to +70°C. $V_{CC} = +5V \pm +5\%$ , unless otherwise noted.

| · PARAMETER                              | SYMBOL           | 8108 |     |      |       |                                                                    |

|------------------------------------------|------------------|------|-----|------|-------|--------------------------------------------------------------------|

| FARAMETER                                |                  | MIN  | TYP | MAX  | UNITS | CONDITIONS                                                         |

| Output HIGH Voltage                      | Voн              | 2.4  | _   | 5.25 | V     | I <sub>OH</sub> = -200 μA                                          |

| Output LOW Voltage                       | VoL              | _    | -   | 0.4  | V     | I <sub>OL</sub> = 2.1 mA (NOTE 1)                                  |

| Output Leakage Current                   | <sup>I</sup> LO  | -10  |     | +10  | μΑ    | $V_{I/O} = 0.4 \text{ V to } V_{CC} \overline{CE} = 2.0 \text{ V}$ |

| Input Leakage Current                    | ILI              | -10  | - 1 | +10  | μА    | V <sub>IN</sub> = 0 to 5.25 V                                      |

| Power Supply Current (Device Disabled)   | lcc1             | _    | 5   | 10   | mA    | CE ≥ 2.0 V                                                         |

| Power Supply Current<br>(Device Enabled) | I <sub>CC2</sub> | _    | 25  | 50   | mA    | CE ≤ 0.8 V                                                         |

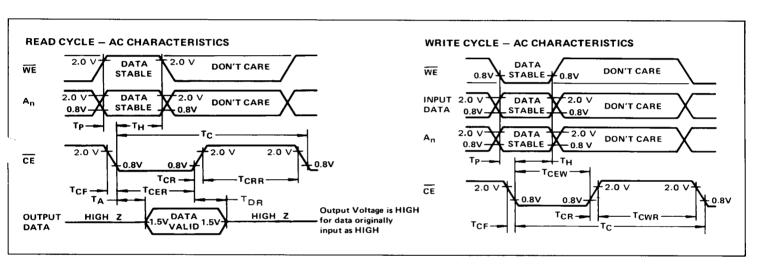

# **READ CYCLE - AC CHARACTERISTICS**

| CHARACTERISTICS                                       | SYMBOL                            | 81  | 8108-3 |     | 8108-5  |      |                        |

|-------------------------------------------------------|-----------------------------------|-----|--------|-----|---------|------|------------------------|

| CHARACTERISTICS                                       | SAMBOL                            | MIN | MAX    | MIN | MIN MAX | UNIT | CONDITIONS             |

| Chip Enable Read Pulse Width                          | TCER                              | 300 | - ∞    | 500 | ∞       | nS   |                        |

| Chip Enable Rise and Fall Time*                       | T <sub>CR</sub> , T <sub>CF</sub> |     | 100    | . – | 100     | nS   |                        |

| Set Up Time                                           | Тр                                | 0   |        | 0   |         | nS   |                        |

| Access Time                                           | TA                                |     | 300    |     | 500     | nS   | Full Operating Voltage |

| Cycle Time, T <sub>CR</sub> = T <sub>CF</sub> = 10 nS | TC                                | 450 |        | 700 | -       | nS   | and Temperature Range  |

| Data Hold Time                                        | T <sub>H</sub>                    | 100 | _      | 100 | _       | nS   | •                      |

| Output Recovery Time                                  | TDR                               | 0   | 75     | 0   | 75      | nS   |                        |

| Read Recovery Time                                    | TCRR                              | 130 | _      | 180 | _       | nS   |                        |

# WRITE CYCLE - AC CHARACTERISTICS

| CHARACTERISTICS                                       | CVMDOL                            | 8108-3 |     | 8108-5 |     |      |                        |

|-------------------------------------------------------|-----------------------------------|--------|-----|--------|-----|------|------------------------|

| CHARACTERISTICS                                       | SYMBOL                            | MIN    | MAX | MIN    | MAX | UNIT | CONDITIONS             |

| Chip Enable Write Pulse Width                         | TCEW                              | 300    | 8   | 500    | ∞   | nS   |                        |

| Chip Enable Rise and Fall Time (NOTE 2)               | T <sub>CR</sub> , T <sub>CF</sub> | _      | 100 | _      | 100 | nS   |                        |

| Set Up Time                                           | Тр                                | 0      | -   | 0      | _   | nS   | Full Operating Voltage |

| Cycle Time, T <sub>CR</sub> = T <sub>CF</sub> = 10 nS | т <sub>С</sub>                    | 450    | _   | 700    | _   | nS   | and Temperature Range  |

| Data Hold Time                                        | Τ <sub>H</sub>                    | 100    | _   | 100    |     | nS   |                        |

| Write Recovery Time                                   | TCWR                              | 130    | _   | 180    | _   | nS   |                        |

#### **CAPACITANCE**

| PARAMETER          | SYMBOL          | MIN | MAX | UNIT | CONDITIONS            |

|--------------------|-----------------|-----|-----|------|-----------------------|

| Input Capacitance  | C <sub>IN</sub> | _   | 5   | pF   |                       |

| Output Capacitance | COUT            | -   | 5   | pF   | V <sub>I/O</sub> = 0V |

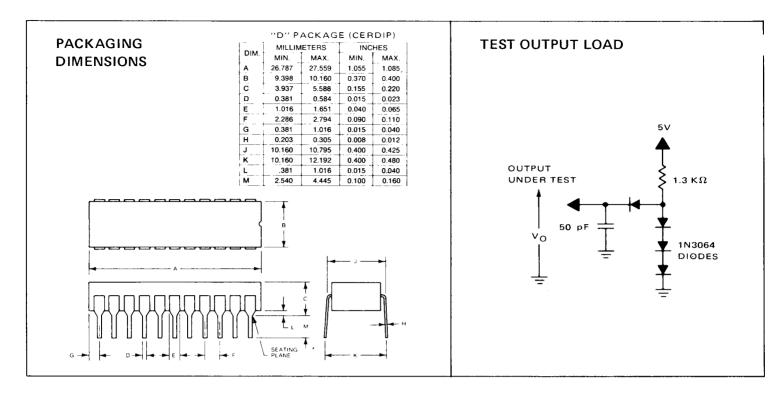

NOTE 1: Output terminated per test output load diagram. Any valid combination of input voltages, V<sub>CC</sub>, and temperature.

NOTE 2: Typical Chip Select Rise and Fall Time ( $T_{CR}$  and  $T_{CF}$ ) is 10 nS For Read and Write Cycle.

A Subsidiary of Electronic Memories & Magnetics Corporation • 2000 West 14th Street, Tempe, Arizona 85281 • (602) 968-4431

# EMM SEMI 8108 300/500 NSEC, STATIC, TTL IN/OUT 1024x8 N-MOS RAM

# ABSOLUTE MAXIMUM RATEINGS (See NOTE 1) (Referenced to GND)

| RATING                                        | VALUE        | UNIT |

|-----------------------------------------------|--------------|------|

| Voltage to Any Pin With                       |              |      |

| Respect to GND                                | -0.5 to +7.0 | Vdc  |

| Power Dissipation                             | 1.6 (NOTE 2) | W    |

| Current Into/From Output                      | 50           | ma   |

| Operating Ambient<br>Temperature Range (Тамв) | 0 to 70      | °C   |

| Storage Temperature<br>(Tstor)                | -65 to +150  | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages.

NOTE 1: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended or maximum voltages for extended periods of time could affect device reliability.

NOTE 2: At 25°C Ambient. Derate 13.5 mW/°C.

# **FUNCTIONAL DESCRIPTION**

The EMM SEMI 8108 is an 8192-bit static RAM with memory cells organized in eight arrays of 128 rows by 8 columns (1024 words X 8 bits). Each eight-bit word is addressed by simultaneously decoding the X addresses (A3 through A9) for the rows, and the Y addresses (A0 through A2) for the columns. Data is written or read in parallel on eight common input/output pins (I/On). The operation of the 8108 is controlled by  $\overline{\text{Chip}}$  Enable (CE) and Write Enable (WE).

When  $\overline{CE}$  is high, all outputs are in an inoperative high impedance state, and power is supplied only to the memory elements. When  $\overline{CE}$  is low, the memory is enabled for reading and writing.

The negative going edge of  $\overline{CE}$  begins timing for a read cycle. Data on  $\overline{WE}$  and address pins  $(A_n)$  must be stable for time  $T_H$ .  $\overline{WE}$  and  $A_n$  will then have been latched into "D" type flip flops and no longer need to be held stable. Output data will be presented on the eight output pins  $(I/O_n)$  within time  $T_A$  and will remain until time  $T_{OTD}$  after  $\overline{CE}$  goes high. Data will then be invalid. After time  $T_C$  another read or write cycle can be initiated.

The negative going edge of  $\overline{CE}$  also begins timing for a write cycle.  $\overline{WE}$  and I/O must be held stable for time  $T_H$ . These inputs will then have been latched and I/O will be entered within time  $T_{CEW}$ . Another read or write cycle can be initiated after time  $T_C$ .

A Subsidiary of Electronic Memories & Magnetics Corporation • 2000 West 14th Street, Tempe, Arizona 85281 • (602) 968-4431

# EMM SEMI 8108 300/500 NSEC, STATIC, TTL IN/OUT 1024x8 N-MOS RAM

# **ORDERING INFORMATION**

|          | ACCESS | CYCLE |         | TEMP.       |

|----------|--------|-------|---------|-------------|

| DEVICE   | TIME   | TIME  | PACKAGE | RANGE       |

| 8108-3CD | 300    | 450   | CERDIP  | 0°C to 70°C |

| 8108-5CD | 500    | 700   | CERDIP  | 0°C to 70°C |

#### **WARNING:**

MOS CIRCUITS ARE SUBJECT TO DAMAGE FROM STATIC DISCHARGE

Internal static discharge circuits are provided to minimize part damage due to environmental static electrical charge build-ups. Industry established recommendations for handling MOS circuits include:

- Ship and store product in conductive shipping tubes or in conductive foam plastic. Never ship or store product in non-conductive plastic containers or non-conductive plastic foam material.

- 2. Handle MOS parts only at conductive work stations.

- Ground all assembly and repair tools.

Represented in your area by:

A Subsidiary of Electronic Memories & Magnetics Corporation

2000 West 14th Street, Tempe, Arizona 85281 Telephone (602) 968-4431

Revised November 1978

Published in U.S.A. August 1978

4

MAY 0 4 1993

020307 <u>/</u> L