AMI MOS Products Catalogue Winter 1979

# **EDGE INDEX**

# 1 GENERAL INFORMATION

AMI Sales Offices

Domestic Distributors

Domestic Reps

International Reps

Ordering Information

Packaging

Terms of Sale

Product Assurance Program

MOS Processes

- 2 MEMORIES

RAMs, ROMs and EPROMs

- **3** S6800 FAMILY

- **4** S2000 FAMILY

- **5** S9900 FAMILY

- 6 TELECOMMUNICATIONS

- 7 CONSUMER INTERFACE PRODUCTS

- 8 APPLICATION NOTES

| Copyright@1978 American Microsystems, Inc. (All rights reserved.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trade Marks Registered®                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Information furnished by AMI in this catalog is believed to be accurate and reliable. Devices sold by AMI are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale. AMI makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. AMI reserves the right to change specifications and prices at any time and without notice. Advanced Product Desription means that this product has not been produced in volume, the specifications are preliminary and subject to change, and device characterization has not been done. Therefore, prior to designing any product into a system, it is necessary to check with AMI for current information. |

| This estalog prepared for American Microsystems, Inc., by Briteday, Inc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## MOS/LSI is the Business of AMI

... and MOS/LSI is AMI's only business. The first company to produce commercial quantities of MOS circuits starting in 1966, AMI has ever since been among the leaders in circuit design, process technology and new product and market development. Today, the company is a major producer of standard products for the electronic data processing, telecommunications, and consumer product industries.

DESIGN EXPERIENCE — Many areas of applications in which MOS is used today were pioneered with an AMI-designed device. This accumulated experience results in a line of high performance standard products and imaginatively designed, cost-effective custom circuits.

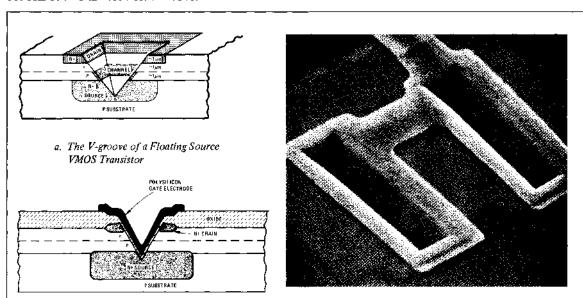

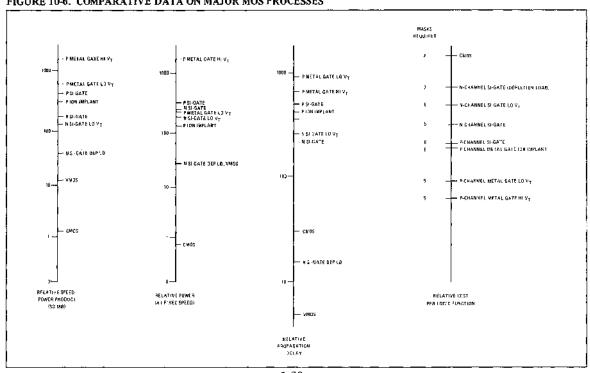

PROCESS VERSATILITY — AMI's head start in the industry gives it a mature capability in every one of the major production processes: P-channel — high voltage and ion implanted metal gate, and silicon gate; N-channel — silicon gate, ion implanted silicon gate with depletion loads, high density and narrow geometry "H" MOS; and CMOS — metal and silicon gate, and high density, isoplanar silicon gate. AMI's new patented process, VMOS, is already producing high speed, low power state-of-the-art memory products.

PRODUCTION CAPABILITY — AMI has three major facilities worldwide. Headquarters in Santa Clara, California has 327,000 square feet of office and manufacturing space and about 1,000 employees. Administration, R&D, the majority of the engineering staff, one of the company's two wafer fabrication facilities, pilot assembly and a final test facility are located there. The other major fabrication facility is at Pocatello, Idaho with 103,000 square feet and about 600 employees. The plant includes an engineering group, four fabricating lines and some final test activity. Located at Inchon, Korea is KMI, the company's major circuit assembly plant. It covers 116,000 square feet, employs about 1,300 persons. This combination of facilities can produce over 2,000,000 LSI circuits per month using the latest production equipment to maximize yields in today's more complex circuits.

PRODUCT RELIABILITY — By designing reliability into the product — a standard procedure for AMI, the most experienced designer of custom MOS circuits — problems are minimized or climinated. Process control (and we run more processes than any other MOS manufacturer) is the second most important step in maintaining our reputation for reliability. Design and process control are buttressed by a closed feedback loop that continually collects AMI internal data and field data from our customers to analyze and solve design, layout and process problems. These activities are further supported by accelerated tests to determine failure rates and the activation energies for observed failure modes.

IT'S STANDARD AT AMI — The company's dedication to the design and manufacture of high performance MOS/LSI products is reflected in the variety of products listed in this catalog.

## AMI and Made-to-Order MOS

Since 1966, AMI has designed and manufactured over 1,000 custom MOS circuits. The largest design engineering staff in the industry has helped to keep AMI in the number one position among custom MOS producers.

If your product can be controlled by an MOS circuit, and you plan to manufacture it in high volume, you should contact your nearest AMI Sales Office or the main office in Santa Clara, California. AMI will be happy to discuss the possibility of designing a custom circuit for your application, or manufacturing such a circuit from your tooling.

# **Numerical Index**

| Device  | Page    | Device   | Page | Device | Page  |

|---------|---------|----------|------|--------|-------|

| TCK 100 | . 7.9   | S2601    | 7.3  | S6820  | 3.2   |

| S1103A  | . 2.3   | S2709    | 7.2  | S6821  | 3.39  |

| S1424A  | . 7.2   | S2733    | 7.2  | S68A21 | 3.39  |

| S1424C  | , 7.2   | S2742    | 7.26 | S68B21 | 3.39  |

| S1425A  | . 7.2   | S2743    | 7.26 | S6830  | 2.3   |

| S1427A  | . 7.2   | S2811    | 6.39 | \$6831 | 2.3   |

| S1856   | . 7.2   | S2900 ,  | 6.40 | S6831A | 2.41  |

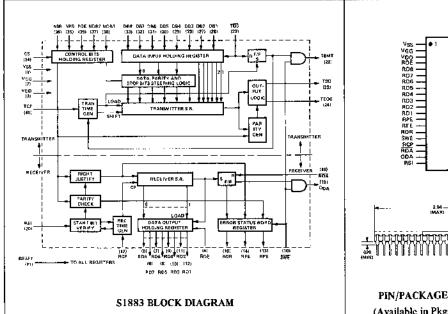

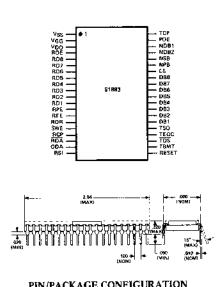

| S1883   | . 3.170 | S2901    | 6.40 | S6831B | 2.41  |

| S1998A  | . 7.2   | S3514    | 2.3  | S6831C | 2.3   |

| S1998B  | . 7.2   | S4006    | 2.3  | S6834  | 2.55  |

| S10110  | . 7.2   | S4008    | 2.3  | S6840  | 3.53  |

| S10111  |         | S4015 ,  | 2.13 | S6846  | 3.68  |

| S10129  | . 7.2   | S4017    | 2.16 | S6850  | 3.88  |

| S10130  | . 7.2   | S4025    | 2.13 | S68A50 | 3.98  |

| S10131  |         | S4028    | 2.19 | S68B50 | 3.98  |

| S10377  | . 7.2   | S4216B   | 2.35 | S6852  | 3.109 |

| S10430  | . 7.2   | S4264    | 2.38 | S6854  | 3.124 |

| S2000   | . 4.1   | S4532    |      | S68A54 | 3.124 |

| S2000A  |         | S4716    |      | S68047 | 3.147 |

| S2114   | . 2.4   | S5101    | 2.20 | S68332 | 2.44  |

| S2114H  |         | S5204A   | 2.49 | S68488 | 3.159 |

| S2147   | . 2.10  | S5232    | 2.3  | S8564  | 2.3   |

| S2150   | . 4.2   | S50145   | 7.2  | S8771  | 2.3   |

| S2150A  | . 4.2   | S50240   | 7.2  | S8773  | 2.3   |

| S2193   | . 7.2   | S50241   | 7.2  | \$8865 | 2.3   |

| S2200   | . 4.2   | S50242   | 7.2  | S8890  | 7.2   |

| S2200A  | . 4.2   | S50243   | 7.2  | S8996  | 2.3   |

| S2222   | . 2.2   | S50244 , |      | S9260  | 7.13  |

| S2222A  | . 2.2   | S6508    | 2.25 | S9261  | 7.13  |

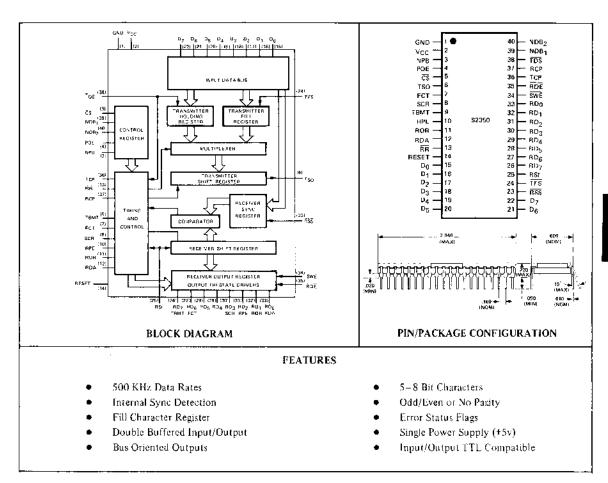

| S2350   | . 3.171 | S6508A   | 2.25 | S9262  | 7.19  |

| S2400   | . 4.2   | S6518    | 2,30 | S9263  | 7.13  |

| S2400A  | . 4.2   | S6518A   | 2.30 | S9264  | 7.13  |

| S2559A  | . 6.3   | S6800    | 3.3  | S9265  | 7.13  |

| S2559B  | . 6.3   | S68A00   | 3.3  | S9266  | 7.19  |

| S2559C  |         | S68B00   | 3.3  | S9660  | 7.2   |

| S2559D  | . 6.3   | S6801    | 3.21 | S9900  | 5.3   |

| S2560A  |         | S6802    |      | S9901  | 5.33  |

| S2560B  | . 6.13  | S6809    | 3.31 | S9902  | 5.44  |

| S2561   | . 6.21  | \$6810A  | 3.32 | S9903  | 5.68  |

| S2562   | . 6.29  | S6810A-1 | 3.32 | S9940  | 5.69  |

| S2567   | . 7.2   | S68A10   | 3.36 | S9980  | 5.70  |

| S2600   | . 7.3   | S68B10   |      | \$9981 | 5.70  |

## **Functional Index**

| Device             | Page   | Device            | Page    | Device                   | Page   |

|--------------------|--------|-------------------|---------|--------------------------|--------|

| RAMs               |        | S6800 Microcomput | er      | Telecommunication        |        |

| S1103A             | . 2.3  | Family            |         | S2559A                   | . 6.3  |

| S2114              | 2.4    | S6800             | 33      | S2559B                   |        |

| S2114H             |        | S68A00            |         | S2559C                   |        |

|                    |        | S68B00            |         | S2559D                   |        |

| S2147              |        |                   |         |                          | _      |

| S2222              |        | \$6801            | ***     | S2560A                   |        |

| S2222A             |        | S6802             |         | S2560B                   |        |

| S4006              |        | \$6809            |         | S2561                    |        |

| S4008              | . 2.3  | S6810A            | . 3.32  | S2562                    | . 6.29 |

| S4015              | . 2.13 | S6810A-1          | 3.32    | S2811                    | . 6.39 |

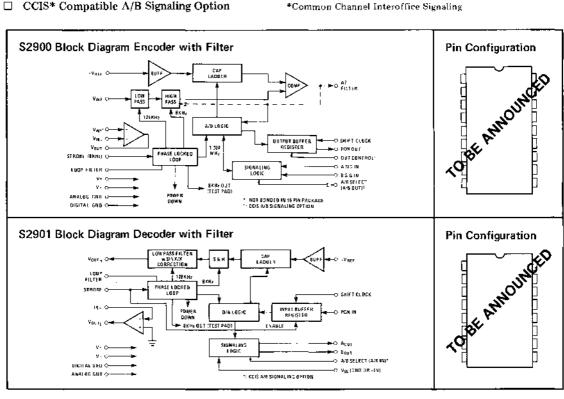

| S4017              | . 2.16 | S68A10            | . 3.36  | S2900                    | 6.40   |

| S4025              |        | S68B10            | 3.36    | S2901                    |        |

| S4028              |        | \$6820            |         |                          |        |

| S5101              |        | S6821             |         |                          |        |

|                    |        | _                 |         | Remote Control Cir       | cuits  |

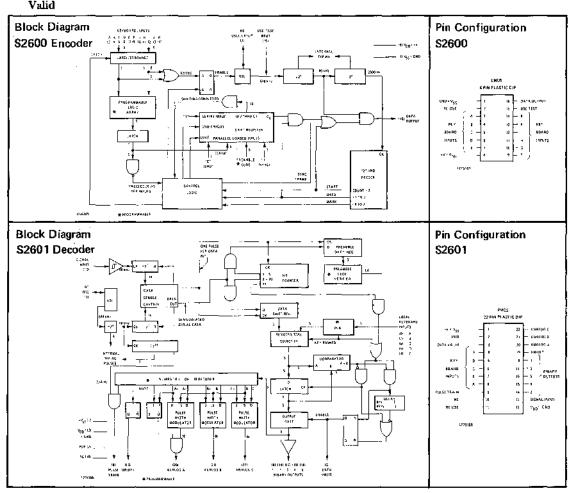

| S6508              |        | S68A21 ,          |         | S2600                    | . 7.3  |

| S6508A             |        | S68B21            |         | S2601                    |        |

| S6518              |        | S6830             |         | S2742                    |        |

| S6518A             |        | S6831             |         | S2743                    |        |

| S68A10             | . 3.36 | S6831A            | 2.41    | 32140                    | . 1.20 |

| S68B10             | . 3.36 | S6831B            | . 2.41  | Table Circles            |        |

|                    |        | S6831C            | . 2.3   | Interface Circuits       |        |

| ROMs               |        | S6834             |         | (TouchControl)           |        |

| S3514              | 2.3    | S6840             |         | TCK100                   |        |

| S4216B             |        | S6846             |         | S9260                    | . 7.13 |

| . S4264            |        | S6850             |         | S9261                    | . 7.13 |

|                    |        |                   |         | S9262                    | . 7.19 |

| S5232              |        | S68A50            |         | S9263                    | . 7.13 |

| S6830              |        | S68B50            |         | S9264                    | . 7.13 |

| S6831              |        | S6852             |         | S9265                    |        |

| S6831A             |        | S6854             |         | S9266                    |        |

| S6831B             |        | S68A54            |         | 55200                    | , 1.10 |

| S6831C             |        | S68047            |         | Onnon Cinosito           |        |

| S68332             | . 2.44 | S68332            | . 2.44  | Organ Circuits<br>S10110 | 70     |

| S8564              | . 2.3  | S68488            | . 3.159 |                          |        |

| S8771              | . 2.3  |                   |         | S10111                   |        |

| S8773              | . 2.3  | S2000 Family      |         | S10129                   |        |

| S8865              |        | S2000             | . 4.2   | S10130                   |        |

| S8896              |        | S2000A            | . 4.2   | S10131 .,                | . 7.2  |

| 00000              | . 2.0  | S2150             | . 4.2   | S10377                   | . 7.2  |

| EDDOM.             |        | S2150A            | . 4.2   | S10430                   | . 7.2  |

| EPROMs             | 0.45   | S2200             |         | S50145                   | . 7.2  |

| \$4532             | _      | S2200A            |         | S50240                   |        |

| S4716              |        | S2400             |         | S50241                   |        |

| S5204A             |        | _                 |         | S50242                   |        |

| S6834 .,           | . 2.55 | S2400A            | . 4.2   | S50243                   |        |

|                    |        | S9900 Family      |         |                          |        |

| Character Generate | or     | S9900             | 5.3     | S50244                   | . 12   |

| S8564              | . 2.3  | S9901             |         |                          |        |

|                    |        |                   |         | Watch/Clock Circuit      | te     |

|                    |        | \$9902            |         | S1424A                   | . 7.2  |

|                    |        | S9903             |         | S1424C                   |        |

|                    |        | S9940             |         | S1425A                   |        |

|                    |        | S9980             |         | S1427A                   |        |

|                    |        | S9981             | . 5.70  | S1856                    |        |

|                    |        | Data Co           |         | S1998A                   |        |

|                    |        | Data Communicatio | п       |                          |        |

|                    |        | Circuits          | 0.450   | \$1998B ,,               |        |

|                    |        | S1883             |         | \$2709                   |        |

|                    |        | S2350             | . 3.171 | S2733                    | . 7.2  |

## **General Information**

**AMI Sales Offices**

**Domestic Distributors**

**Domestic Reps**

**International Reps**

**Ordering Information**

**Packaging**

**Terms of Sale**

**Product Assurance Program**

**MOS Processes**

### DOMESTIC

### Western Area

100 East Wardlow Rd., Suite 203 Long Beach, California 90807 Tel: (213) 595-4768 TWX: 910-341-7668 3800 Homestead Road Santa Clara, California 95051 Tel: (408) 249-4550 TWX: 910-338-0018 20709 N.E. 232nd Avenue Battleground, Washington 98604

### Central Area

Tel: (206) 687-3101

500 Higgins Road, Suite 210 Elk Grove Village, Illinois 60007 Tel: (312) 437-6496 TWX: 910-222-2853 Suite Number 204 408 South 9th Street Noblesville, Indiana 46060 Tel: (317) 773-6330 TWX: 810-260-1753 29200 Vassar Ave., Suite 303 Livonia, Michigan 48152 Tel: (313) 478-9339 TWX: 810-242-2903

### 725 So. Central Expressway, Suite A-9 Richardson, Texas 75080 Tel: (214) 231-5721

(214) 231-5285 TWX: 910-867-4766

### Eastern Area

237 Whooping Loop Altamonte Springs, Florida 32701 Tel: (305) 830-8889 TWX: 810-853-0269

1420 Providence Turnpike, Suite 220 Norwood, Massachusetts 02062 Tel: (617) 762-0726 TWX: 710-336-0073

20 Robert Pitt Drive, Room 212 Monsey, New York 10952 Tel: (914) 352-5333

TWX: 710-577-2827

Axe Wood East Butler & Skippack Pikes, Suite 230 Ambler Pennsylvania 19002 Tel: (215) 643-0217 TWX: 510-661-3878

### INTERNATIONAL

### England

AMI Microsystems, Ltd. 108 A Commercial Road Swindon, Wiltshire Tel: (793) 31345 or 25445 TLX: 851-449849

### France

AMI Microsystems, S.A.R.L. 124 Avenue de Paris 94300 Vincennes ,France Tel: (01) 374 00 90 TLX: 842-670500

### Holland

AMI Microsystems, Ltd. Calandstraat 62 Rotterdam, Holland Tel: 010-36 14 83 TLX: 844-27402

### italy

AMI Microsystems, S.p.A. Via Pascoli 60 20133 Milano Tel: 29 37 45 or 2360154 TLX: 843 32644

### Japan

AMI Japan Ltd. 502 Nikko Sanno Building 2-5-3, Akasaka Minato-ku, Tokyo 107 Tel: Tokyo 586-8131 TLX: 781-242-2180 AMI J

### West Germany

AMI Microsystems, GmbH Rosenheimer Strasse 30/32, Suite 237 8000 Munich 80, West Germany Tel: (89) 483081 TLX: 841-522743 Rapifax: (89) 486591

### ALABAMA

Huntsville

Resistaçap (205) 881-9270

### ARIZONA

Phoenix

Kierulff (602) 243-4101

Sterling Electronics (602) 258-4531

R.V. Weatherford Co. (602) 272-7144

#### CALIFORNIA

Anaheim

R.V. Weatherford Co. (714) 634-9600 Glendale

R.V. Weatherford Co. (213) 849-3451

Schweber Electronics (213) 537-4320 or

(714).556.3880Los Angeles

Kierulff (213) 685-5511

Palo Alto

Rierulff (415) 968-6292

R.V. Weatherford Co. (415) 493-5373

R.V. Weatherford Co. (714) 623-1261 or (213) 966-8461

San Diego

Intermark Electronics (714) 279-5200 Kierulff (714) 278-2112

R.V. Weatherford Co. (714) 278 7400 Santa Ana

Intermark Electronics (714) 540-1322 or (213) 436-5275

Sunnyvale

Intermark Electronics (408) 738-1111 Western Microtechnology (408) 737-1660

### Kierulff (714) 731-5711

### COLORADO

Denver

Kierulff (303) 371-6500

Englewood

R.V. Weatherford Co. (303) 770-9762

Wheatridge

Century Electronics (303) 424-1985

### CONNECTICUT

Danbury

Schweber Electronics (203) 792 3500 Hamden

Arrow Electronics (203) 248-3801

### FLORIDA

Ft. Lauderdale

Arrow Electronics (305) 776-7790 Hollywood

Schweber Electronics (305) 927-0511 Palm Bay

Arrow Electronics (305) 725 1480 St. Petersburg

Kierulff Electronics (813) 576-1966

### GEORGIA

Atlanta

Schweber Electronics (404) 449-9170

Arrow Electronics (404) 455-4054

### ILLINOIS

Elk Grove Village

Kierulff (312) 640 0200

Schweber Electronics (312) 593-2740

Schaumburg Arrow Electronics (312) 893-9420

Westmont R/M Electronics (312) 323-9670

### INDIANA

Indianapolis

R/M Electronics (317) 247-9701

### LOUISIANA

Metairie

Sterling Electronics (504) 887-7610

## MARYLAND

Baltimore

Arrow Electronics (301) 247-5200

Gaithersburg

Schweber Electronics (301) 840 5900

### MASSACHUSETTS

Natick

Future Electronics Corp. (617) 237-6340 Waltham

Schweber Electronics (617) 890-8484 Sterling Electronics (617) 894-6200

Wohurn

Arrow Electronics (617) 933-8130

### MICHIGAN

Ann Arbor

Arrow Electronies (313) 971-8220

Schweber Electronics (313) 525-8100

Wyoming

R/M Electronics (616) 531-9300

### MINNESOTA

Bloomington Arrow Electronics (612) 887-6400

Schweber Electronics (612) 941-5280

### NEW HAMPSHIRE

Manchester

Arrow Electronics (608) 668-6968

### NEW JERSEY

Moorestown

Arrow Electronics (609) 235-1900 Perth Ambov

Sterling Electronics (201) 442-8000 Saddlebrook

Arrow Electronics (201) 797-5800 Somerset

Schweber Electronics (201)469-6008

### NEW MEXICO

Albuquerque Century Electronics (505) 292 2700

Sterling Electronics (505) 345-6601 NEW YORK

Farmingdale

Arrow Electronics (516) 694-6800

Fishkill

Arrow Electronics (914) 896-7530

Rochester

Schweber Electronics (716) 424-2222 Westbury

Schweber Electronics (516) 334-7474

### NORTH CAROLINA

Kernersville

Arrow Electronies (919) 996-2039 оню

### Beechwood

Schweber Electronics (216) 464-2970 Kettering

Arrow Electronics (513) 253-9176 Solon

Arrow Electronics (216) 248-3990

### OREGON

Beaverton

Parrott (503) 641-3355

#### PENNSYLVANIA

Schweber Electronics (215) 441-0600

### TEXAS Dallas

Component Specialities, Inc.

(214) 357 6511

Schweber Electronics (214) 661-5010 Sterling Electronics (214) 357-9131 R.V. Weatherford Co. (214) 243-1571

Houston

Component Specialities, Inc.

(713) 771-7237

Schweber Electronics (713) 784-3600 Sterling Electronics (713) 627 9800 R.V. Weatherford Co. (713) 688-7406

UTAH

Salt Lake City

Century Electronics (801) 972-6969 Kierulff (801) 973-6913

### VIRGINIA Richmond

Sterling Electronics (804) 226-2190

### WASHINGTON

Seattle

Kierulff (206) 575-4420

R.V. Weatherford Co. (206) 575-1340

WISCONSIN

Oak Creek Arrow Electronics (414) 764-6600

### CANADA

Alberta

Bowtek Electric Co. (403) 452-9050

British Columbia

Vancouver

Bowtek Electric Co. (604) 736-1141

Manitoba

Winnepeg

Bowtek Electric Co. (204) 633-9525

### Ontario

Downsview Cesco Electronics, Ltd. (416) 661-0220. Future Electronics Corp. (416) 663-5563

Cesco Electronics, Ltd. (613) 729-5118

Future Electronics Corp. (613) 820-9471

Quebec

Montreal Cesco Electronics, Ltd. (514) 735 5511 Future Electronics, Corp. (514) 785-5775

Cesco Electronics, Ltd. (418) 524-4641

ALABAMA

Huntsville

Rep, Inc.

Tel: (205) 881-9270

TWX: 810-726-2101

ARIZONA

Phoenix

Hecht, Henschen & Assoc., Inc.

Tel: (602) 275-4411 TWX: 910-951-0635

CALIFORNIA

Long Beach

Application Representatives

Tel: (213) 594-6608 TWX: 910-341-6599

Mt. View

Thresum Associates, Inc.

Tel: (415) 965-9180 TWX: 910-379-6617

San Diego

Hadden Associates

Tel: (714) 565-9445

TWX: 910-335-2057

COLORADO

Parker

R<sup>2</sup>Marketing

Tel: (303) 841 5822

CONNECTICUT

Orange

CPS Corp.

Tel: (203) 795-3515

GEORGIA

Tucker

Rep. Inc.

Tel: (404) 938-4358

ILLINOIS

Elk Grove Village

Oasis Sales Tel: (312) 640-1850

TWX: 910-222-2170

INDIANA

Ft. Wayne

Technical Representatives, Inc.

Tel: (219) 484-1432

Indianapolis

Technical Representatives

Tel: (317) 849-6454 TWX: 810-260-1792

IOWA

Cedar Rapids

Comstrand, Inc.

Tel: (319) 377-1575

KENTUCKY

Louisville

Technical Representatives, Inc.

Tel: (502) 451-9818

MARYLAND

Baltimore

Coulbourn DeGreif, Inc.

Tel: (301) 247-4646

TWX: 710-236-9011

MASSACHUSETTS

Lexington

Circuit Sales Company

Tel: (617) 861-0567

MINNESOTA Minneapolis

Comstrand, Inc.

Tel: (612) 788-9234

TWX: 910-576-0924

MISSOURI

Grandview

Beneke & McCaul

Tel: (816) 765-2998

St. Louis

Beneke & McCaul.

Tel: (314) 434-6242

NEW YORK

Clinton

Advanced Components

Tel: (315) 853-6438

Endicott

Advanced Components

Tel: (607) 785-3191

Melville

Astroren, Inc.

Tel: (516) 423-2266

TWX: 510-226-6147

NEW YORK

North Syracuse

Advanced Components

Tel: (315) 699-2671

TWX: 710-541-0439

Scottsville

Advanced Components

Tel: (716) 889-1429

NORTH CAROLINA

Raleigh

Rep, Inc.

Tel: (919) 851-3007

Centerville

S.A.I. Marketing

Tel:(513) 435-3181

TWX: 810-459-1647

Shaker Heights

S.A.I. Marketing

Tel: (216) 751-3633 TWX: 810-421-8289

Zanesville

S.A.I. Marketing

Tel: (614) 454-8942

OKLAHOMA

Oklahoma City Ammon & Rizzos

Tel: (405) 942-2552

OREGON

Portland

SD-R<sup>2</sup> Products & Sales

Tel: (503) 246-9305

PENNSYLVANIA

Pittsburgh

S.A.I. Marketing

Tel: (412) 782-5120

TEXAS Austin

Ammon & Rizos

Tel: (512) 454-5131

Dallas

Ammon & Rizos

Tel: (214) 233-5591 TWX: 910-860-5137

Houston

Ammon & Rizos

Tel: (713) 781-6240

TWX: 910-881-6382

TENNESSEE

Jefferson City

Rep, Inc.

Tel: (615) 475-4105

TWX: 810-570-4203

Salt Lake City

R<sup>2</sup> Marketing Tel: (801) 972-5646

TWX: 910-925-5607

VIRGINIA

Charlottesville

Coulbourn DeGreif, Inc.

Tel: (804) 977-0031

WASHINGTON

Bellevue

SD-R<sup>2</sup> Products & Sales.

Tel: (206) 747-9424 or (206) 624-2621

TWX: 810-443-2483

WISCONSIN

Menomonee Falls

Oasis Sales Tel: (414) 251-9431

CANADA

Ottowa, Ontario

Cantec Reps, Inc.

Tel: (613) 225-0363

TWX: 610-562-8967

Point Claire, Quebec

Cantec Reps, Inc.

Tel: (514) 694-4049 Tlx: 58-22790

Toronto, Ontario

Cantec Reps, Inc.

Tel: (416) 675-2460 or 2461 TWX: 610-492-2655

AUSTRALIA

Rifa Pty. Ltd. 202 Bell Street

Preston, Victoria 3072

Tel: (03)480 1211 TLX: AA31001

BRAZII.

Datronix Electronica Ltda.

Av. Pacaembu, 746 - Conj. 11 Sao Paulo

Tel: 209-0134

TLX: 391-1122372

CENTRAL AMERICA

ROW, Inc.

3421 Lariat

Shingle Springs, Calif. 95682

Tel: (916) 677-2827

ENGLAND

Ritro Electronics (U.K.)

Grefell Place Maidenhead

Berkshire

Tel: (0628) 36227

FINLAND

OY Atomica AB

PL 22

02171 Espoo 17 Tel: 80-423533

TLX: 12-1080

FRANCE

Produits Electronique Professionals S.A.R.L.

2 · 4 Rue Barthelemy

92120 Montrouge

Tel: 8353320

TLX: 204534

HOLLAND

AMI Microsystems, Inc.

Calandstraat 62

Rotterdam

Tel: 010-36 14 83

TLX: 844-27402

HONG KONG

Apcom Systems, Ltd.

1201 Kimberly Center

35 Kimberly Road

Kowloon

Tel: 3-694659

TLX: 64095

INDIA

**ROW** International

149 Kimble Rd.

Los Gatos, Calif.

Tel: (408) 354-7698

CVS Technologies (1974) Ltd.

9 Jobotinsky St.

Box 946 Bnei Brak

Tel: 799156

TLX: 341109

ITALY

Paolo Meoni & Associates

Giovanni Pascoli 60

20133 Milano

Tel: 29 37 45 TLX: 843-32644

**JAPAN**

Micro-Systems, Inc.

15-29 Mita 4-Chome

Minato-ku, Tokyo 108

Tel: (03) 452-4994

Matsushita Electric

Trading Company, Ltd.

71, 5-Chome, Kawaramachi

Higashi-ku

Osaka

Tel: (06) 204-5510

TLX: 781-63417

MALAYSIA

Dynamar International Ltd.

208 Shaw House, Orchard Rd.

Singapore 9,

Tel: 2351139

TLX: RS26283

MEXICO

ROW, Inc.

3421 Lariat

Shingle Springs, Calif. 95682

Tel: (916) 677-2827

NEW ZEALAND

David P. Reid (NZ) Ltd.

Box 2630, Auckland 1

Tel: 492-189

TLX: 791 2612

SINGAPORE

Dynamar International Ltd.

208 Shaw House, Orchard Rd.

Singapore 9 Tel: 2351139

TLX; RS 26283

SOUTH AFRICA

Tecnetics

P.O. Box 56310

Pinegowrie 2123, Transvaal

Johannesburg

Tel: 48-5712

TLX: 960-80838

SOUTH AMERICA

ROW, Inc.

3421 Lariat

Shingle Springs, Calif. 95682 Tel: (916) 677-2827

**SWEDEN**

A.B. Rifa

Fack, S-16300 Spanga

Tel: (08) 751 00 20

TLX: 13690

SWITZERLAND

W. Moor AG

Bahnstrasse 58.

8105 Regensdorf Zurich

Tel: (01) 8406644

TLX: 52042

TAIWAN Dynamar (Taiwan) Ltd.

2nd Flr., No. 14, Lane 164

Sung Chiang Road Taipei, 104

Tel: 541-8252 thru 54

TLX: 785-11064

WEST GERMANY

Aktiv Electronics GmbH

Leonorenstrasse 49

D-1000 Berlin 46

Tel: (030) 771 4408 TLX: 185327

Gustav Beck KG

Eltersdorfer Strasse 7

8500 Nurnberg 15

Tel: (0911) 34966

TLX: 622334 Ultratronik

Munchenerstr, 6

D-8031 Oberalting-Seefeld

Tel: (08152) 7696

TLX: 526459

Ditronic, GmbH

Im Asemwald 48

D-7000 Stuttgart 70

Tel: (0711) 724844

TLX: 7255638

Miktrotec, GmbH Johannesstr. 91

D-7000 Stuttgart 1

Tel: (0711) 22807

TLX: 722818

YUGOSLAVIA

Iskra Standard

Celovska 122

61000 Ljubljana

Tel: (061) 551093 TLX: 31300 YU-ISKRA Any product in this MOS Products Catalog can be ordered using the simple system described below. With this system it is possible to completely specify any standard device in this catalog in a manner that is compatible with AMI's order processing methods. The example below shows how this ordering system works and will help you to order your parts in a manner that can be expedited rapidly and accurately.

All orders (except those in sample quantities) are normally shipped in plastic carriers or aluminum tube containers, which protect the devices from static electriticy damage under all normal handling conditions. Either container is compatible with standard automatic IC handling equipment.

Any device described in this catalog is an AMI Standard Product. However, ROM devices that require mask preparation or programming to the requirements of a particular user, devices that must be tested to other than AMI Quality Assurance standard procedures, or other devices requiring special masks are sold on a negotiated price basis.

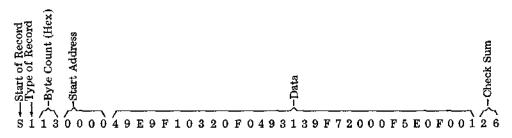

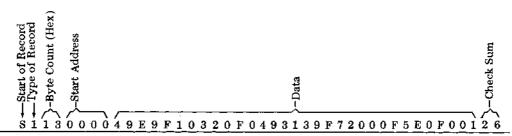

Device Number — prefix S, followed by four (or five\*) numeric digits that define the basic device type. If there are versions to the basic device, the numeric digits will be followed by additional alphanumeric digits, in this example A-1. The last digit should always be followed by a space.

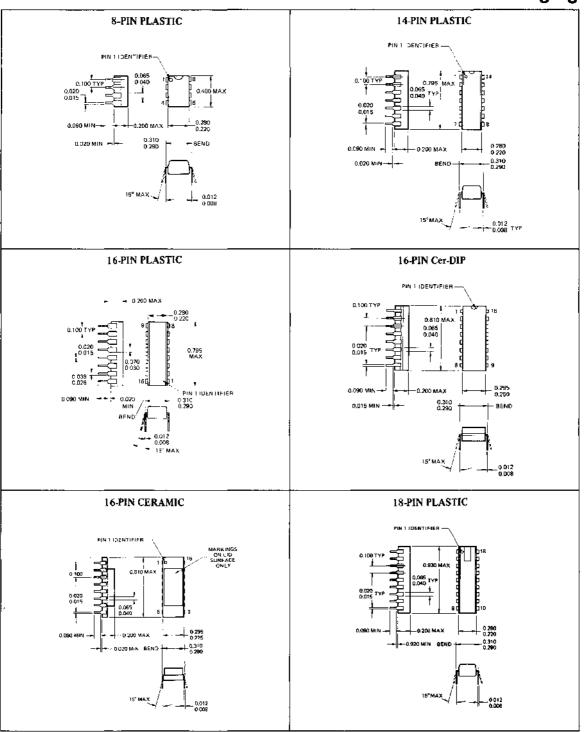

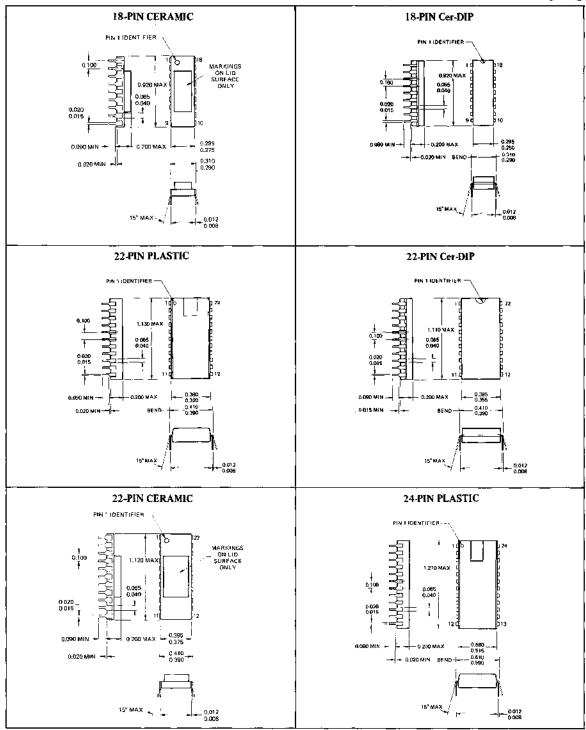

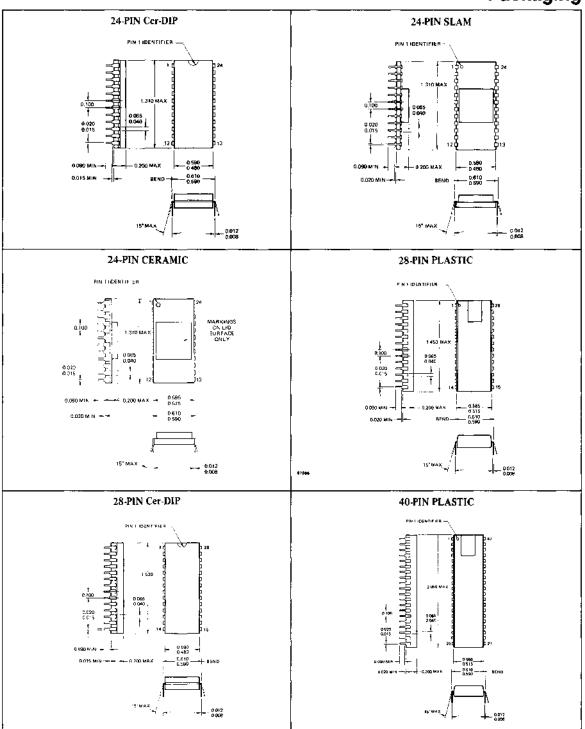

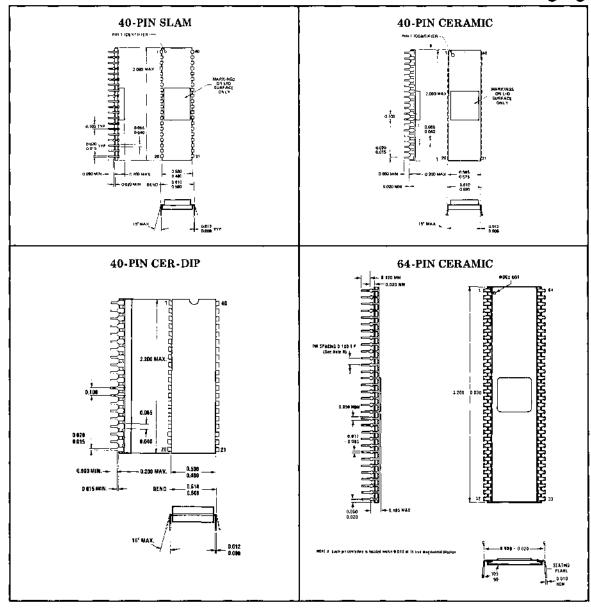

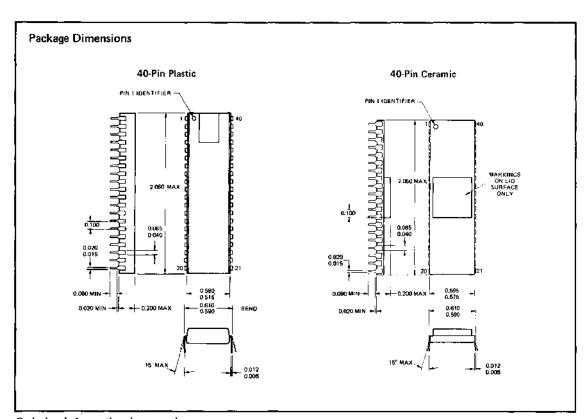

Package Type — a single letter designation which identifies the basic package type. The letters are coded as follows:

P - Plastic package

E - Cer-DIP package

S - SLAM package

C - Ceramic (three-layer) package

T-TO type package

\*Organ Circuits

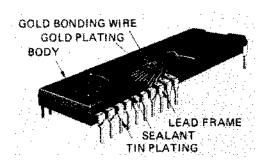

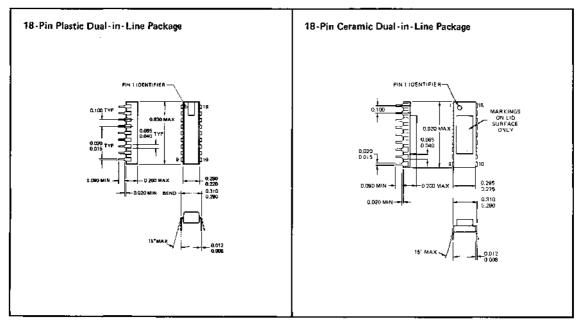

### PLASTIC PACKAGE

The AMI plastic dual-in-line package is the equivalent of the widely accepted industry standard, refined by AMI for MOS/LSI applications. The package consists of a plastic body, transfer-molded directly onto the assembled lead frame and die. The lead frame is Kovar or Alloy 42, with external pins tin plated. Internally, there is a 50µin, gold spot on the die attach pad and on each bonding fingertip. Gold bonding wire is attached with the thermocompression gold ball bonding technique.

Materials of the lead frame, the package body, and the die attach are all closely matched in thermal expansion coefficients, to provide optimum response to various thermal conditions. During manufacture every step of the process is rigorously monitored to assure maximum quality of the AMI plastic package.

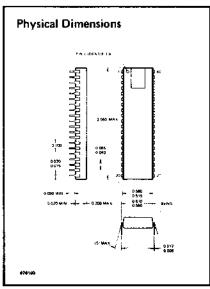

Avaliable in:  $\mathbf{8}$ ,  $\mathbf{14}$ ,  $\mathbf{16}$ ,  $\mathbf{18}$ ,  $\mathbf{22}$ ,  $\mathbf{24}$ ,  $\mathbf{28}$  and  $\mathbf{40}$  pin configurations.

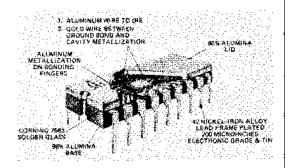

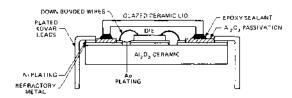

### Cer-DIP PACKAGE

The Cer-DIP dual-in-line package has the same high performance characteristics as the standard three-layer ceramic package, yet approaches plastic in cost. It is a military approved type package, with excellent reliability characteristics. Although the Cer-DIP concept has been around for a number of years, AMI leads the technology with this package, having eliminated the device instability and corrosion problems of earlier Cet-DIP processes.

The package consists of an Alumina  $(Ai_2O_3)$  base and the same material lid, hermetically fused onto the base with low temperature solder glass. Inert gasses are sealed inside the die cavity.

Available in: 16, 18, 22, 24, 28 and 40 pin configurations.

### SLAM PACKAGE

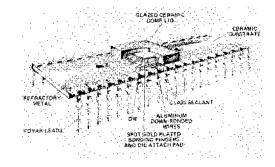

The SLAM (single layer metallization) dual-in-line package is an AMI innovation that offers a lower cost alternative to three-layer ceramic packages, without sacrifice of performance or reliability.

The SLAM package uses the same basic materials as ceramic, but is constructed in a simpler and thereby more reliable manner. It uses a 96% Alumina base, one basic refractory metallization layer, coated with an Alumina passivation layer, and brazed-on Kovar leads. The leads are suitable for either socket insertion or soldering. Either a ceramic or a Kovar lid is used to hermetically seal the package. The ceramic lid is attached with an epoxy resin sealant, but a gold-silicon eutectic solder is used for Kovar lids.

Avaliable in: various 14 to 40 pin configurations.

**EPOXY SEAL PACKAGE**

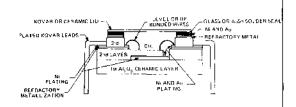

### CERAMIC PACKAGE

Industry standard high performance, high reliability package, made of three layers of  $Al_2O_3$  ceramic and nickel-plated refractory metal. Either a low temperature glass sealed ceramic lid or a gold tin eutectic sealer Kovar lid is used to form the hermetic cavity of this package. Package leads are available with gold over nickle or tin plating for socket insertion or soldering.

ACCEPTANCE THE FROMS OF SALE CONTAINED HERREIN APPLY TO ALL OUR TATHONS MADE AND PURCHAST DIBINES ENTERED INTO BY THE SPELER SOME OF THE TERMS SET OUT HER BAND DIFFELL HOM THOSE IN BUYER'S PURCHASE ORDER AND SOUR MAY BE NEW THIS ACCEPTANCE IS CONDITIONAL ON BUYER'S PASSENT TO THE TRANSSET OUT HERE IN LIEU OF THOSE IN RUYER'S PURCHASE ORDER SET OUT HERE IN LIEU OF THOSE IN RUYER'S PURCHASE ORDER AND COMMUNICATION FROM BUYER SHALL NOT BE DEEMED A WAIVER OF THE PROMISIONS OF THIS ACCEPTANCE. AND CHANGES IN THE LIEWS CONTAINED IS ADDITIONAL OF THE PROMISIONS OF THIS ACCEPTANCE. AND CHANGES IN THE LIEWS CONTAINED HEREIN MUST SPECIFICALLY BE AGREED TO IN WRITING BY AN OFFICER OF THE SELLER BEFORE BECOMING BINDING OF THIS SELLER BEFORE BECOMING BINDING OF THIS SELLER BEFORE BECOMING BINDING OF THE BUYER. All orders of contained the appropriate of accounted by the Self as dischoole office These terms shall all appropriate whether one things the state of the one discharge and acknowledged maskly are from eight support of a subject of a state of the propriate of the reference of other propriates.

#### 2. PAYMENT

Lift Unless otherwise agreed, a fill rivoldes are thut and pavable thirty (30) days from date of involve. Moridisculants are authorized. Shipments, achieving, and performance of work shall still times be subject to the approval of the Salter's credit department and the Salter has the decline to make any shipment or deliveries or perform any work excess appointed by private the upon terms and confidence at the other salters are performed.

and conditions or security satisfactory to such disparchient. (O) If, in the judgment of the Seller, the financial condition of the Bover at any time does not justify continuation of production or shipment on the terms of payment originally specified, the Seller may require full or partial payment in accounce and, in the event of the Seller may require full or partial payment in event any proceeding is brought by or against the Boyer under the teat kniptcy or insoftwork laws, the Seller shall be entitled to cancer any proceeding to the full be entitled to cancer any order then constanting and shall receive reimborrement for its concellation changes.

(c) Fach thipmont shall be considered a separate and independent transaction, and payment therefor shall be made accordingly. If showness are delayed by the Buyer, payments shall become due on the date when the Selfer's prepared to make at prients. If the work covered by the purchase order is delayed by the Buyer, payments shall be maile based on the purchase order is delayed by the Buyer, by the products held for the Buyer shall be at the risk and expense of the Buyer.

- 3. TAXES: Unless otherwise provided herein, the amount of any potential or future was revinue excised other taxes, test, or other charges of any nature, imposed by any public auditionity, instoner state, local or other, applicable to the anothers covered by this order, or the manufacturer or safe chereof, shall be added for the purchase price and shall be paid by the Buyer, or in less thereof, the Buyer shall showed the Seffer with a tex exemption certificate acceptable to the taxing authority.

- 4 F.O.B. POINT: All sales or made F.O.B. point of supment. Select's trip passes to Buyer, and Seller's liability as to delivery ocases upon making delivery of material purchased heroundor to carrier of shipping soint, the carrier acting as Buyer's agent. All claims for domages must be filed with the carrier. Shipments will normally be made by Parcel Fost, Ballway Express, Arr Express, or Air Freight. Ubdess specific instructions from Buyer specify which of the foregoing methods of shipment is to be used, the Seller will exercise but eavy discretion.

- 5. DELIVERY: Shipping dates are approximate and are based upon promot receipt from Buyer of all necessary information. In no event will seller be fable for any re-procurement costs, not for datay or non-delivery, due to causes beyond its reasonable control including, but not limited to, acts of Gou, acts of cut or infirstry authority, profites, fires, strikes, lock-outs, slow-downs, shorteses, factory or labor conditions, errors in manufacture, and inability due to quiese beyond the Seller's reasonable control to obtain necessary labor, materials, or manufacturing facilities. In the event of any such delay, the cate of helivery shall, as the request of the Seller, be deferred for a period equal to the time lost by reason of the fellow.

In the event Seller's production is curtailed for any of the above crasons so that Seller cannot deliver the full amount refeased hereunder. Seller may allocate production deliveries an only its verious customers then under contract for smill goods. The allocation will be made in a commerciafly fair and responsible mainer, When allocation was been made, Boyer will be notified of the estimated quipta made available.

6. PATENTS: The Buyer shall hold the Seller hamiless against any expense or loss resulting from infringement of patents, trademarks, or unifair competit or arising from compliance with Buyer's despits, specifications, or instructions. This sale of products by the Seller does not convey any license, by implication, escoppe or intrevivus, unifair patent claims powering combinations of said products with other devices or elements.

Except as otherwise provided in the preciding paragraph, the Seller shall detend any suit or procededing brought against the Buyer, so far as based on a claim that any product, or any part thereof, furnished under this contract constitutes an infiningement of any patent of the United States, if notified promptly in writing and given institutions, information, and assistance for the Seller's expensel for offense of same, and the Seller shall pay all damages and costs awarded therein against the Buyer. In case said product, or any purt thereof, is, in such surf, held to constitute infiningement of patent, and the use of said product is error ned, the Seller's shall act so own expense, either produce of or the Buyer the right to continuous aid product on pair, replace same with non-infringing product, modify it so it becomes unon-infringing, or remove stild product and reflund the purchase price and the transportation and installation costs thereof. In no event shall Seller's total liability to the Buyer under or a result of compliance with the provisions of this paragraph excess the agregate some paid by the Buyer for the allegedly infringing product. The foregoing states the antire liability of the Seller for patent infringement by the said products or any part thereof. THIS

PROVISION IS STATED IN LIFU OF ANY OTHER EXPRESSED, IMPLIED, OR STATILTORY WARRANTY AGAINST INFRINGEMENT AND SHALL BE THE SOLE AND EXCLUSIVE REMEDY FOR PATENT INFRINGEMENT OF ANY SIND.

- 7 INSPECTION. Unlins other easy specified and agreed upon, the manifeld to be forms rad imper this popular shall be subject to the Select's standard impercion at the place of immufacture. If it is belief speed upon and specified in this eader can Bayor is to inspect or provide for impertion at obacc of manifecture such inspection also be to conducted as to not interfere unreasonably worth Selfer's operations and consequent approval or relection shall be made before shipment of the material. Note instand, or the foregoing of, uson relegion of such material by Buyer, the same shall appear not to conform to the contract, the Buyer shall presentedly notify the Selfer's fact such conditions and affect dithe Selfer's consent. Selfer's Return Material Authorization form must accompany seen determined materials.

- 8. WARRANTY: The Selfer variants that the products to be delivered under this processo order will be their from delects in material and workmanship under regimal use and service. Selfer's obligations order this Warranty are financed to realisting or tropaling or giving credit for, at its option, at its factory, any of said products which shall, within and fill year after shipment, be returned to the Selfer's factory of origin, transportation charges prepare, and which are, after examination, displaced to the Selfer's statistication to be this defective. THIS WARRANTY 'S EXPRESSED IN LIEU OF ALL OTHER WARRANTES, EXPRESSED STATUTORY, OR IMPLIED, INCLUDING THE IMPLIED WARRANTES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, AND OF ALL OTHER OBELIGATIONS OR LIABILITIES ON THE SELLER'S PART, AND IT NETTHER ASSUMES NOR AUTHORIZES ANY OTHER "ERSON TO ASSUME FOR THE SELLER ANY OTHER LIABILITIES IN CONNECTION WITH THE SALE OF THE SAID ARTICUSES. This Warranty shall not deplay to any of such products which shall have been repaired or altered, except by the Seller, or which shall have been subjected to inside, original warranty period of any product which has either been repaired or inerical by Seller.

In is uniferstand that if this order calls for the delivery of semiconductor devices which are not finished and fully encapsulated, that no warranty, statutory, expressed or implied, including the implied warranty of inerchantability and it is nest for a particular purpose, shall apply. All such devices are sold as is where is.

#### 9. GENERAL:

(a) The validity, performance and construction of these terms and all sales frequency shall be governed by the laws of the State of California.

(b) The Seller represents that with respect to the profitchion of articles and/or performance of the services covered by this order it will finity comply with all requirements of the Fair Labor Standerds Act of 1938, as amended, Williams Steiger Occupational Sarety and Health Act of 1970, Executive Orders 19376 and 19246. Section 202 and 704.

(c) In no event shall Seller be fiable for consequential or special damages.

(d) The Buyer may not unilaterally make changes in the drawings, distinct specifications for the items to be furnished hereunder without Seller's prior consent.

(e) Except to the extent provided in Paragraph 10, below, this order is not subject to cancellation or termination for convenience.

(f) Briver acknowledges that all or part of the products point-asset hereunder may be manufactured and/or assembled at any of Soller's facilities, thomastic or foreign.

(g) In the evens that the cost of the products are increased as a result of increases in materials, labor costs, or duties, Seller into take the price of the products to gover the cost increases.

(h) It Buyer is in broach of its obligations under this order. Buyer shall remain liable for all unipend charges and sums due to Sellie and will reimburss. Seller for all damages suffered or incurred by Solier as a result of Buyer's broach. The remedies promided herein shall be in section to all other legal means and remed as available to Sellie.

10. GOVERNMENT CONTRACT PROVISIONS: If Buyer's original purchase order indicates by contract in mer, that it is placed under a government contract, only the tollowing provisions of the current Armed Services Produrement Regulation are applicable in accordance with the terms thereof, with an appropriate substruction of purities, as the case may be in its, "Contracting Officer" shall mean "Buyer", "Contractor" shall mean "Seller", and the term "Contract" shall mean this order.

2-103.1, Definitions: 7-103.3, Extras: 7-103.4, Variation in Quantiny: 7-103.8, Assignment of Claims; 7-103.9, Additional Band Sacurity, 7-103.13, Renegotation: 7-103.15, Phodesis and Certain Germanist Areas: 7-103.16, Contract Work Hours and Safety Standards Act. Overtine Compensation; 7-103.17, Watsh Healey Public Contracts Act. 7-103.18, Equal Opportunity Clause: 7-103.19, Ottician Not to Benefit; 7-103.20, Covernant Against Contingent Fee; 7-103.21, Terrimostion for Convenience of the Government (anity to the extent that Bayer's contract; is terminated for the convenience of the government; 7-103.22, Authorization and Consent, 7-103.23, Notice and Assistance Regarding-Patert Infringement; 7-103.24, Responsibility for Inspection, 7-103.25, Commercial Bills of Lading Covering Shipments Under FO3 Origin Contracts; 7-104.27, Listing of Employment Openings; 7-104.4, Notice to the Government of Labor Disputes; 7-104.1, Excess Profit, 7-404.15, Examination of Records by Comptrolis Genera; 7-104.20, Utilization of Labor Surplus Area Concent.

### INTRODUCTION

Quality is one of the most used, least understood, and variously defined assets of the semiconductor industry. At AMI we have always known just how important effective quality assurance, quality control, and reliability monitoring are in the ability to deliver a repeatably reliable product. Particularly, through the manufacture of custom MOS/LSI, experience has proved that one of the most important tasks of quality assurance is the effective control and monitoring of manufacturing processes. Such control and monitoring has a twofold purpose: to assure a consistently good product, and to assure that the product can be manufactured at a later date with the same degree of reliability.

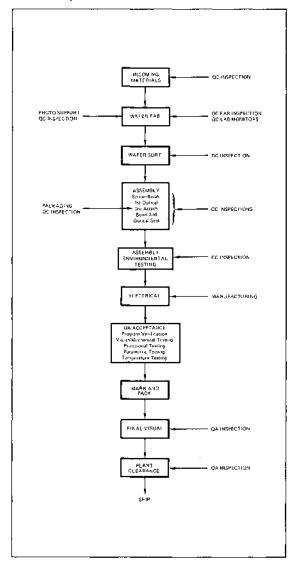

To effectively achieve these objectives, AMI has developed a Product Assurance Program consisting of three major functions:

- Quality Control

- · Quality Assurance

- · Reliability

Each function has a different area of concern, but all share the responsibility for a reliable product.

### The AMI Product Assurance Program

The program is based on MIL-STD-883, MIL-M-38510, and MIL-Q-9858A methods. Under this program, AMI manufactures highest quality MOS devices for all segments of the commercial and industrial market and, under special adaptations of the basic program, also manufactures high reliability devices to full military specifications for specific customers.

The three aspects of the AMI Product Assurance Program — Quality Control, Quality Assurance, and Reliability—have been developed as a result of many years of experience in MOS device design and manufacture.

Quality Control establishes that every method meets, or fails to meet, product parameters - QA checks results.

Quality Control establishes that every method meest, or fails to meet, processing or production standards -QC checks methods.

Reliability establishes that QA and QC are effective - Reliability checks device performance.

One indication that the AMI Product Assurance Program has been effective, is that NASA has endorsed AMI products for flight quality hardware since 1967. The Lunar Landers and Mars Landers all have incorporated AMI circuits, and AMI circuits have also been utilized in the Viking and Vinson programs, as well as many other military airborne and reconnaissance hardware programs.

### QUALITY CONTROL

The Quality Control function in AMI's Product Assurance Program involves constant monitoring of all aspects of materials and production, starting with the raw materials purchased, through all processing steps, to device shipment. There are three major areas of Quality Control:

- Incoming Materials Control

- Microlithography Control

- Process/Assembly Control

### Incoming Materials Control

All purchased materials, including raw silicon, are checked carefully to various test and sampling plans. The purpose of incoming materials inspection is to ensure that all items required for the production of AMI MOS circuits meet such standards as are required for the production of high quality, high reliability devices.

Incoming inspection is performed to specifications agreed to by suppliers of all materials. The Quality Control group continuously analyzes supplier performance, performs comparative analysis of different suppliers, and qualifies the suppliers.

Tests are performed on all direct material, including packages, wire, lids, eutectics, and lead frames. These tests are performed using a basic sampling plan in accordance with MIL-S-19500, generally to a Lot Tolcrance Percent Defective (LTPD) level of 10%. The AQL must be below 1% overall.

Two incoming material inspection sequences illustrate the thoroughness of AMI Quality Control:

- Purchased packages are first inspected visually. Then, dimensional inspections are performed, followed by a full functional inspection, which subjects the packages to an entire production run simulation. Finally, a full electrical evaluation is made, including checks of the insulation, resistance, and lead-to-lead isolation. A package lot which passes these tests to an acceptable LTPD level is accepted.

- Raw silicon must also pass visual and dimensional checks.

In addition, a preferential etch quality inspection is performed. For this inspection, the underlayers of bulk silicon are examined for potential anomalies such as dislocation, slippage, or etch pits. Resistivity of the silicon is also tested.

### Microlithography Control

Microlithography involves the processes which result in finished working plates, used for the fabrication of wafers. These processes are pattern or artwork generation, photoreduction, and the actual printing of the working plates.

## **Product Assurance Program**

Pattern generation now is the most common practice at AMI. The circuit layout is digitized and stored on a tape, which then is read into an automated pattern generator, which prints a highly accurate 10x reticle directly.

In cases where the more traditional method of artwork generation is used whether Rubylith, Gerber Plots, AMI generated or customer generated — the artwork is thoroughly inspected. It is checked for level-to-level registration and dimensional tolerances. Also, a close visual inspection of the workmanship is made. AMI artwork is usually produced at 200x magnification and must conform to stringent design rules, which have been developed over a period of years, as part of the process control requirements.

Acceptable artwork is photographically reduced to a 20x magnification, and then further to a 10x magnification. The resulting 10x reticles are then used for producing 1x masters. The masters undergo severe registration comparisons to a registration master and all dimensions are checked to insure that reductions have been precise. During this step, image and geometry are scrutinized for missing or faded portions and other possible photographic omissions.

For a typical P-channel silicon gate device, master sets are checked at all six geometry levels in various combinations against each other and against a proven master set. Allowable deviations within the die are limited to 0.5 micron, deviations within a plate are limited to 1 micron, and all plate deviations are considered cumulatively.

Upon successful completion of a device master set, it is released to manufacturing where the 1x plates are printed. A sample inspection is performed by manufacturing on each 30-plate lot and the entire lot is returned to Quality Control for final acceptance. Quality Control performs audits on each manufacturing inspector daily, by sample inspection techniques.

The plates can be rejected first by manufacturing, when the 30-plate lots are inspected, or by Quality Control when the lots are submitted for final acceptance. If either group rejects the plates, they are rescreened and then undergo the same inspection sequence. In the rescreening process, the plates undergo registration checks; visual checks for pin holes, protrusions, and faded or missing images, as well as all critical dimension checks.

### Process Control

Once device production has started in manufacturing, AMI Quality Control becomes involved in one of the most important aspects of the Product Assurance Program — the analysis and monitoring of virtually all production processes, equipment, and devices.

Process controls are performed in the fabrication area, by the Quality Control Fabrication Group, to assure adherence to specifications. This involves checks on operators, equipment and environment. Operators are tested for familiarity with equipment and adherence to procedure. Equipment is closely checked both through calibration and maintenance audits. Environmental control involves close monitoring of temperature, relative humidity, water resistivity and bacteria content, as well as particle content in ambient air. All parameters are accurately controlled to minimize the possibility of contamination or adverse effects due to temperature or humidity excesses.

Experience has proven that such close control of the operators, equipment, and environment is highly effective towards improved quality and increased yields.

In addition to the specification adherence activities of the QC Fabrication Group, a QC Laboratory performs constant process monitoring of virtually every step of all processes. Specimens are taken from all production steps and critically evaluated. Sampling frequency varies, depending on the process, but generally, oxidation, diffusion, masking, and evaporization are the most closely monitored steps.

Results are supplied both to manufacturing and engineering. When evidence of a problem occurs, QC provides recommendations for corrections and follows up the corrective action taken.

Optical inspections are performed at several steps; quality control limits are based on a 10% LTPD. The chart-in Figure 1 shows process steps and process control points.

### QUALITY ASSURANCE

The Quality Assurance function in the Product Assurance Program involves checking the ability of manufactured parts to meet specifications. In addition, the QA group also is responsible for calibration of all equipment, and for the maintenance of AMI internal product specifications, to assure that they are always in conformance with customer specifications, or other AMI specifications.

After devices undergo 100% testing in manufacturing, they are sent to Quality Assurance for acceptance. Lots are defined, and using the product specifications, sample sizes are determined, along with the types of tests to be performed and the test equipment to be used. Lots must pass QA testing either with an LTPD or 10%, or less, if the specification requires tighter limits.

Three types of tests are performed on the samples: visual/mechanical, parametric, and functional. All tests are performed both at room temperature and at elevated temperature. In addition, a number of other special temperature tests may be performed, if required by the specification. Generally, high temperature tests are at 125°C.

To perform the tests, QA uses AMI PAFT test systems, ROM test systems, Macrodata testers, Fairchild Sentry systems,

Figure 1. Flowchart of Product Assurance Program Implementation

Western Digital Spartan systems, Impact testers, and various bench test units. In special instances a part may also be tested in a real life environment, in the equipment which is to finally utilize it.

If a lot is rejected during QA testing, it is returned to the production source for an electrical rescreening. It is then returned to QA for acceptance, but is identified as a resubmitted lot. If it fails again, it is discarded and corrective action in engineering is initiated. As evidence of the problem is detected, the parts may also be traced all the way back to the wafer run, to analyze the cause.

When a lot is acceptable, it is sent to packaging and then to finished goods. When parts are sent from finished goods, they are again checked by the QA group to a 10% LTPD, with visual/mechanical tests. Also, all supporting documentation for the parts is verified, including QA acceptance, special customer specifications, certificates of compliance, etc. Only after this last check are devices considered ready for plant clearance.

If there are customer returns, they are first sample tested by QA, to determine the cause of the return. (Many times an invalid customer test will incorrectly cause returns.) After QA evaluates all returns, they are sent to Reliability for failure analysis.

### RELIABILITY

The Reliability function in the Product Assurance Program involves process qualification, device qualification, package qualification, reliability program qualification, and failure analysis. To perform these functions AMI Reliability group is organized into two major areas:

- Reliability Laboratory

- Failure Analysis

### Reliability Laboratory

AMI Reliability Laboratory is responsible for the following functions:

- · New Process Qualification

- Process Change Qualification

- Process Monitoring

- New Device Qualification

- Device Change Qualification

- New Package Qualification

- Device Monitoring

- Package Change Qualification

- Package Monitoring

- High Reliability Programs

There are various closely interrelated and interactive phases involved in the development of a new process, device, package, or reliability program. A process change may affect device performance, a device change may affect process repeatability, and a package change may affect both device performance and process repeatability. To be effective, the Reliability Laboratory must monitor and analyze all aspects of new or changed processes, devices, and packages. It must be determined what the final effect is on product reliability, and then evaluate the metits of the innovation or change.

### Process Qualification

For example, AMI Research and Development group recommends a new process or process alteration when it feels that the change can result in product improvement. The Reliability Laboratory then performs appropriate environmental and electrical evaluations of new process. Typically, a special test vehicle, or "rel chip", generated by R&D during process development, is used to qualify the recommended new process or process change.

The rel chip is composed of circuit elements similar to those that may be required under worst-case circuit design conditions. The rel chip elements are standard for any given process, and thus allow precise comparisons between diffusion runs. The following is an example of what is included on a typical rel chip:

- · A discrete inverter and an MOS capacitor

- · A large P-N junction covered by an MOS capacitor

- A large P-N junction area (identical to the junction area above, but without the MOS capacitor)

- A large area MOS capacitor over substrate

- Several long contact strings with different contact geometries.

- Several long conductor geometries, which cross a series

of eight deeply etched areas.

Each circuit element of a rel chip allows a specific test to be performed. As an example, the discrete inverter and MOS load device accommodate power life tests. As a consequence, any type of parameter drift can be observed. The MOS capacitor, covering the large P-N junction, can serve to indicate the presence of contamination in the oxide, under the oxide, or in the bulk silicon. If unusual drift is evidenced, the location of contamination can be determined through analysis of the additional MOS capacitor and the large P-N junction area. The metal conductor interconnecting contacts is useful for life testing under relatively high current conditions. It facilitates the detection of metal separation when moisture or other contaminants are present.

The conductors crossing deeply etched areas allow the checking of process control. Rather than depending upon optical inspection of metal quality, burned out areas caused by high currents are readily identified and provide a quantitative measure of metal quality.

If the Reliability Laboratory determines that a recommended new process or process change is viable for manufacturing purposes, further analysis is necessary to determine that production devices can be manufactured in high volume, in a repeatable and reliable manner.

### Process Monitoring

In addition to process qualification, the Reliability group also conducts ongoing process monitoring programs. Once every 90 days each major production process is evaluated using relichips as test vehicles. The resulting test data is analyzed for parameter limits and process stability. In this manner AMI can help assure repeatability and high product quality.

### Package Qualification

New packages are also qualified before they are adopted. To analyze packages, a qualification matrix is designed, according to which the new package and an established package (used for control) are tested concurrently. The test matrix consists of a full spectrum of electrical and environmental stress tests, in accordance with MIL-STD-883.

### Failure Analysis

Another important function of the Reliability group is failure analysis. Scanning electron microscopes, high power optical microscopes, diagnostic probe stations, and other equipment is used in failure analysis of devices submitted from various sources. It is the function of the Reliability group to determine the cause of failure and recommend corrective action.

The Reliability group provides a failure anlaysis service for the previously mentioned in-house programs and for the evaluation of customer returns. All AMI customers are provided a failure analysis service for any part that fails within one year from date of purchase and the results of the analysis are returned in the form of a written report.

### SUMMARY

The Product Assurance Program at AMI is oriented towards process control and monitoring, and the evaluation of devices. The Program consists of three major functions: Quality Control, Quality Assurance, and Reliability. Constant monitoring of all phases of production, with information feedback at all levels, allows fast and efficient detection of problems, evaluation and analysis, correction, and verification of the correction. The overall result is a line of products which are highly repeatable and reliable, with a very low reject level.

### PROCESS DESCRIPTIONS

Each of the major MOS processes is described on the following pages. First, the established production proven processes are described, followed by those advanced processes, which are starting to go into volume production now. In each case, the basic processes is described first, followed by an explanation of its advantages, applications, etc.

### P-CHANNEL METAL GATE PROCESS

Of all the basic MOS processes, P-channel Metal Gate is the oldest and the most completely developed. It has served as the foundation for the MOS/LSI industry and still finds use today in some devices. Several versions of this process have

evolved since its earliest days. A thin slice (8 to 10 mils) of lightly doped N-type silicon wafer serves as the substrate or body of the MOS transistor. Two closely spaced, heavily doped P-type regions, the source and drain, are formed within the substrate by selective diffusion of an impurity that provides holes as majority electrical carriers. A thin deposited layer of aluminum metal, the gate, covers the area between the source and drain regions, but is electrically insulated from the substrate by a thin layer (1000-1500 Å) of silicon dioxide. The P-channel transistor is turned on by a negative gate voltage and conducts current between the source and the drain by means of holes as the majority carriers.

The basic P-channel metal gate process can be subdivided in two general categories: high-threshold and low-

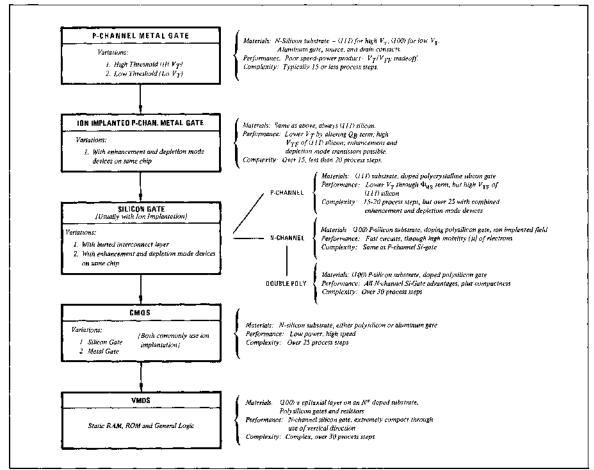

FIGURE 10-1. SUMMARY OF MOS PROCESS CHARACTERISTICS

threshold. Various manufacturers use different techniques (particularly so with the low threshold process) to achieve similar results, but the difference between them always rests in the threshold voltage  $V_T$  required to turn a transistor on. The high threshold  $V_T$  is typically -3 to -5 volts and the low threshold  $V_T$  is typically -1.5 to -2.5 volts.

The original technique used to achieve the difference in threshold voltages was by the use of substrates with different crystalline structures. The high  $V_T$  process used (111) silicon, whereas the low  $V_T$  process used (100) silicon. The difference in the silicon structure causes the surface charge between the substrate and the silicon dioxide to change in such a manner that it lowers the threshold voltages.

One of the main advantages of lowering  $V_T$  is the ability to interface the device with TTL circuitry. However, the use of (100) silicon carries with it a distinct disadvantage also. Just as the surface layer of the (100) silicon can be inverted by a lower  $V_T$ , so it also can be inverted at other random locations—through the thick oxide layers—by large voltages that may appear in the metal interconnections between circuit components. This is undesirable because it creates parasitic transistors, which interfere with circuit operation. The maximum voltage that can be carried in the interconnections is called the parasitic field oxide threshold voltage  $V_{TF}$ , and generally limits the overall voltage at which a circuit can operate. This, then, is the main factor that limits the use of the low  $V_T$  process. A drop in  $V_{TF}$  between a high  $V_T$  and low  $V_T$  process may, for example, be from -28V to -17V.

The low  $V_T$  process, because of its lower operating voltages, usually produces circuits with a lower operating speed than the high  $V_T$  process, but is easier to interface with other circuits, consumes less power, and therefore is more suitable for clocked circuits. Both P-channel metal gate processes yield devices slower in speed than those made by other MOS processes, and have a relatively poor speed/power product. Both processes require two power supplies in most circuit designs, but the high  $V_T$  process, because it operates at a high threshold voltage, has excellent noise immunity.

### ION IMPLANTED P-CHANNEL METAL GATE PROCESS

The P-channel Ion Implanted process uses essentially the same geometrical structure and the same materials as the high  $V_T$  P-channel process, but includes the ion implantation step. The purpose of ion implantation is to introduce P-type impurity ions into the substrate in the limited area under the gate electrode. By changing the characteristics of the substrate in the gate area, it is possible to lower the threshold voltage  $V_T$  of the transistor, without influencing any other of its properties.

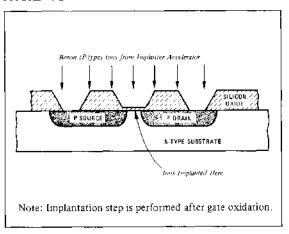

Figure 10-2 shows the ion implantation step in a diagrammatic manner. It is performed after the gate oxide is

deposited, but before the source, gate, and drain metallization deposition. The wafer is exposed to an ion beam which penetrates through the thin gate oxide layer and implants ions into the silicon substrate. Other areas of the substrate are protected both by the thicker oxide layer and sometimes also by other masking means, lon implantation can be used with any process and, therefore could, except for the custom of the industry, be considered a special technique, rather than a process in itself.

The implantation of P-type ions into the substrate, in effect, reduces the effective concentration of N-type ions in the channel area and thus lowers the  $V_{\rm T}$  required to turn the transistor on. At the same time, it does not alter the N-type ion concentration elsewhere in the substrate and therefore, does not reduce the parasitic field oxide threshold voltage  $V_{\rm TF}$  (a

### FIGURE 10-2. DIAGRAM OF ION IMPLANTATION STEP

problem with the low  $V_T$  P-channel Metal Gate process, described above). The (111) silicon usually is used in ion-implanted transistors.

In fact, if the channel area is exposed to the ion beam long enough, the substrate in the area can be turned into P-type silicon (while the body of the substrate still remains N-type) and the transistor becomes a depletion mode device. In any circuit some transistors can be made enhancement type, while others are depletion type, and the combination is a very useful circuit design tool.

The lon-implanted P-channel Metal Gate process is very much in use today. Among all the processes, it represents a good optimization between cost and performance and thus is the logical choice for many common circuits, such as memory devices, data handling (communication) circuits, and others.

Because of its low  $V_{\rm T}$ , it offers the designer a choice of using low power supply voltages to conserve power or increase supply voltages to get more driving power and thus increase speed. At low power levels it is more feasible to implement clock generating and gating circuits on the chip. In most circuit designs only a single power supply voltage is required.

### N-CHANNEL PROCESS

Historically, N-channel process and its advantages were known well at the time when the first P-channel devices were successfully manufactured, however it was much more difficult to produce N-channel. One of the main reasons was that the polarity of intrinsic charges in the materials combined in such a way that a transistor was on at OV and had a  $V_{\rm T}$  of only a few tenths of a volt (positive). Thus, the transistor operated as a marginal depletion mode device, without a well-defined onloff biasing range. Attempts to raise  $V_{\rm T}$  by varying gate oxide thickness, increasing the substrate doping, and back biasing the substrate, created other objectionable results and it was not until research into materials, along with ion implantation, silicon gates, and other improvements came about that N-channel became practical for high density circuits.

The N-channel process gained its strength only after the P-channel process, ion implantation, and silicon gate all were already well developed. N-channel went into volume productions with advent of the 4K dynamic RAM and the microprocessor, both of which required speed and high density. Because P-channel processes were nearing their limits in both of these respects, N-channel became the logical answer.

The N-channel process is structurally different from any of the processes described so far, in that the source, drain, and channel all are N-type silicon, whereas the body of the substrate is P-type. Conduction in the N-channel is by means of electrons, rather than holes.

The main advantage of the N-channel process is that the mobility of electrons is about three times greater than that of holes and, therefore, N-channel transistors are faster than P-channel. In addition, the increased mobility allows more current flow in a channel of any given size, and therefore N-channel transistors can be made smaller. The positive gate voltage allows an N-channel transistor to be completely compatible with TTL.

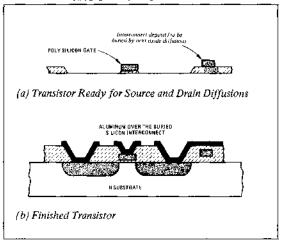

Although metal gate N-channel processes have been used, the predominant N-channel process is a silicon gate process. Among the advantages of silicon gate is the possibility of a buried layer of interconnect lines, in addition to the normal aluminum interconnections deposited on the surface of the chip. This gives the circuit designer more latitude in layout

and often allows the reduction of the total chip size. Because the polysilicon gate electrode is deposited in a separate step, after the thick oxide layer is in place, the simultaneous deposition of additional polysilicon interconnect lines is only a matter of masking. These interconnect lines are buried by later steps, as shown in Figure 10-3.

FIGURE 10-3. CROSSECTION OF A SILICON GATE MOS TRANSISTOR

One minor limitation associated with the buried interconnect lines is their location. Because the source and drain diffusions are done after the polysilicon is deposited [see (a) of Figure 10-3] the interconnect lines cannot be located over these diffusion regions.

A second advantage of a silicon gate is associated with the reduction of overlap between the gate and both the source and drain. This reduces the parasitic capacitance at each location and improves speed, as well as power consumption characteristics. Whereas in the metal gate process, the P region source and drain diffusion must be done prior to deposition of the gate electrode, in silicon gate process, the electrode is in place during diffusion, see (a) of Figure 10-3. Therefore, no planned overlap for manufacturing tolerance purposes need exist and the gate is said to be self-aligned. The only overlap that occurs is due to the normal lateral extension of the source and drain regions during the diffusion process.

The silicon-gate process produces devices that are more compact than metal gate, and are slightly faster because of the reduced gate overlap capacitance. Because the basic silicon gate process is relatively simple, it is also economical. It is a versatile process that is used in memory devices and most any other circuit.

Because N-channel is relatively new, however, its production techniques and variations in applications still are undergoing development. However, the combination of high speed, TTI, compatibility, low power requirements, and compactness have already made N-channel the most widely used process. The cost of N-channel has been coming down also.

In addition to its use in large memory chips and microprocessors, N-channel has become a good general purpose process for circuits in which compactness and high speed are important. The addition of a second layer of polysilicon to this process has allowed the formation of overlapping electrodes making possible charge coupled devices for very compact dynamic memory cells, for filters, and for analog/digital conversion.

### CMQ\$

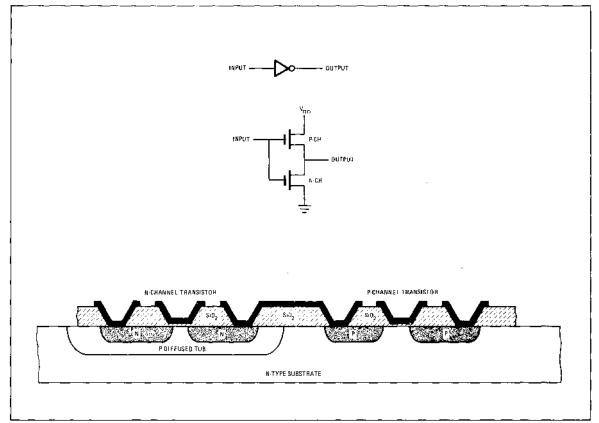

The basic CMOS circuit is an inverter, which consists of two adjacent transistors — one an N-channel, the other a P-channel, as shown in Figure 10-4. The two are fabricated on the same substrate, which can be either N or P type.

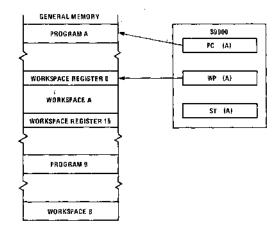

The CMOS inverter in Figure 10-4 is fabricated on an N-type silicon substrate in which a P "tub" is diffused to form the body for the N-channel transistor. All other steps, including the use of silicon gates and ion implantation, are much the same as for other processes.