DV11 communications multiplexer user's manual

Copyright © 1976 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC DECtape PDP

DECCOMM DECUS RSTS

DECsystem-10 DIGITAL TYPESET-8

DECSYSTEM-20 MASSBUS TYPESET-11

UNIBUS

#### CONTENTS

| 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | Pa                                    | ge |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------|----|

| 1.2   DV11 COMMUNICATIONS MULTIPLEXER   1   1.2.1   DV11 Overview Block Diagram   1   1.2.1.1   Establishing the Data Link   1   1.2.1.2   DV11 Operation   1   1.2.2   Reference Documents   1   1.2.2   Reference Documents   1   1.3.3   PHYSICAL DESCRIPTION   1   1.3.1   General Specifications   2   1.3.1   General Specifications and Precautions   2   1.3.1   General Specifications and Signals   2   1.3.1   Interrupt Priorities and Address Assignments   2   1.4.2   Interrupt Priorities and Address Assignments   2   1.4.3   General Specifications   3   1.4.4   General Specifications   3   1.4.5   General Specifications   3   1.4.5   General Specifications   3   1.4.5   General Specif | CHAPTER I | INTRODUCTION AND GENERAL DESCRIPTION  |    |

| 1.2   DV11 COMMUNICATIONS MULTIPLEXER   1   1.2.1   DV11 Overview Block Diagram   1   1.2.1.1   Establishing the Data Link   1   1.2.1.2   DV11 Operation   1   1.2.2   Reference Documents   1   1.2.2   Reference Documents   1   1.3.3   PHYSICAL DESCRIPTION   1   1.3.1   General Specifications   2   1.3.1   General Specifications and Precautions   2   1.3.1   General Specifications and Signals   2   1.3.1   Interrupt Priorities and Address Assignments   2   1.4.2   Interrupt Priorities and Address Assignments   2   1.4.3   General Specifications   3   1.4.4   General Specifications   3   1.4.5   General Specifications   3   1.4.5   General Specifications   3   1.4.5   General Specif | 1.1       | PURPOSE AND SCOPE                     | -1 |

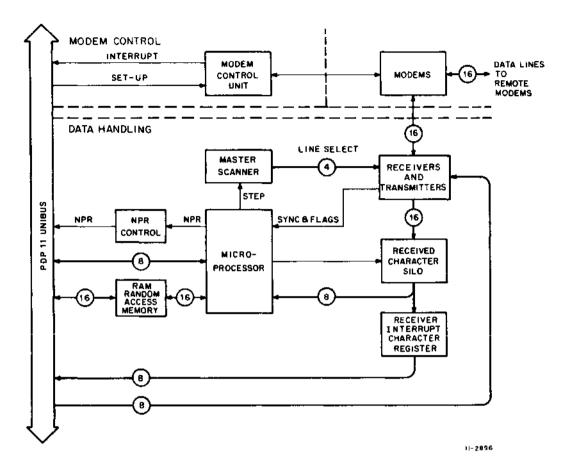

| 1.2.1   DV11 Overview Block Diagram   1   1.2.1.1   Establishing the Data Link   1   1.2.1.2   DV11 Operation   1   1.2.2   Reference Documents   1   1.3.3   PHYSICAL DESCRIPTION   1   1.3.1   General Specifications   2   1.3.1   Minimum Through Maximum Configurations   2   2.1.2   Compatibility Considerations and Precautions   2   2.1.2   Compatibility Considerations and Signals   2   2.1.3   Interface Specifications and Signals   2   2.1.4   Interrupt Priorities and Address Assignments   2   2.1.4.1   Interrupt Priorities and Address Assignments   2   2.1.4.2   Interrupt Vector Address Assignment   2   2.1.4.3   Address Assignments   2   2.1.4.3   Address Assignments   2   2.1.4   Interrupt Vector Address Assignment   2   2   2   UNPACKING AND INSPECTION   2   2   2   2   UNPACKING AND INSPECTION   2   2   2   2   2   3   1   Unibus Cable Interconnections   2   2   4   MODULE INSTALLATION OF BASIC ASSEMBLIES   2   2   2   4   MODULE INSTALLATION AND CUSTOMIZING   2   2   2   2   4   4   Unibus and Interrupt Vector Address Assignments   2   2   2   2   2   4   4   4   Unibus and Interrupt Vector Address Assignments   2   2   2   2   4   4   4   1   4   4   1   4   4   4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.2       |                                       | -1 |

| 1.2.1.1       Establishing the Data Link       1         1.2.1.2       DV11 Operation       1         1.2.2.2       Reference Documents       1         1.3       PHYSICAL DESCRIPTION       1         1.3.1       General Specifications       1         CHAPTER 2       INSTALLATION         2.1       SITE PREPARATION AND PLANNING       2         2.1.1       Minimum Through Maximum Configurations       2         2.1.2       Compatibility Considerations and Precautions       2         2.1.2       Compatibility Considerations and Signals       2         2.1.3       Interrupt Priorities and Address Assignments       2         2.1.4.1       Interrupt Priorities and Address Assignments       2         2.1.4.2       Interrupt Priorities and Address Assignments       2         2.1.4.3       Address Assignments       2         2.1.4.1       Interrupt Vector Address Assignment       2         2.1.5       Environment       2         2.2       UNPACKING AND INSPECTION       2         2.3       INSTALLATION OF BASIC ASSEMBLIES       2         2.3.1       Unibus Cable Interconnections       2         2.4.2       MODULE INSTALLATION AND CUSTOMIZING       2 <td>1.2.1</td> <td></td> <td>-1</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.2.1     |                                       | -1 |

| 1.2.1.2   DV11 Operation   1   1.2.2   Reference Documents   1   1.2.2   Reference Documents   1   1.3   PHYSICAL DESCRIPTION   1   1.3.1   General Specifications   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.2.1.1   |                                       | -2 |

| 1.2.2     Reference Documents     1       1.3     PHYSICAL DESCRIPTION     1       1.3.1     General Specifications     1       CHAPTER 2     INSTALLATION       2.1     SITE PREPARATION AND PLANNING     2       2.1.1     Minimum Through Maximum Configurations     2       2.1.2     Compatibility Considerations and Precautions     2       2.1.3     Interface Specifications and Signals     2       2.1.4     Interrupt Priorities and Address Assignments     2       2.1.4.1     Interrupt Priorities     2       2.1.4.2     Interrupt Vector Address Assignment     2       2.1.4.3     Address Assignments     2       2.1.4.3     Address Assignments     2       2.1.4.5     Environment     2       2.2     UNPACKING AND INSPECTION     2       2.3     INSTALLATION OF BASIC ASSEMBLIES     2       2.3.1     Unibus Cable Interconnections     2       2.4     MODULE INSTALLATION AND CUSTOMIZING     2       2.4.1     Unibus and Interrupt Vector Address Assignments     2       2.4.2     Synchronous Parameter Selection     2       2.4.3     Resistance Checks     2       2.4.4     Installation of Add-On DV11     2       2.5     SYSTEM CHECKOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.2.1.2   |                                       | -2 |

| 1.3       PHYSICAL DESCRIPTION       1         1.3.1       General Specifications       1         CHAPTER 2       INSTALLATION         2.1       SITE PREPARATION AND PLANNING       2         2.1.1       Minimum Through Maximum Configurations       2         2.1.2       Compatibility Considerations and Precautions       2         2.1.3       Interrace Specifications and Signals       2         2.1.4       Interrupt Priorities and Address Assignments       2         2.1.4.1       Interrupt Vector Address Assignments       2         2.1.4.2       Interrupt Vector Address Assignment       2         2.1.4.3       Address Assignments       2         2.1.4.3       Address Assignments       2         2.1.5       Environment       2         2.2       UNPACKING AND INSPECTION       2         2.2       UNPACKING AND INSPECTION       2         2.3.1       Unibus Cable Interconnections       2         2.4       MODULE INSTALLATION AND CUSTOMIZING       2         2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2         2.4.3       Resistance Checks       2 <t< td=""><td>1.2.2</td><td>•</td><td>-3</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.2.2     | •                                     | -3 |

| 1.3.1   General Specifications   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |                                       | -3 |

| 2.1       SITE PREPARATION AND PLANNING       2         2.1.1       Minimum Through Maximum Configurations       2         2.1.2       Compatibility Considerations and Precautions       2         2.1.3       Interface Specifications and Signals       2         2.1.4       Interrupt Priorities and Address Assignments       2         2.1.4.2       Interrupt Vector Address Assignment       2         2.1.4.3       Address Assignments       2         2.1.5       Environment       2         2.2       UNPACKING AND INSPECTION       2         2.3       INSTALLATION OF BASIC ASSEMBLIES       2         2.3.1       Unibus Cable Interconnections       2         2.4       MODULE INSTALLATION AND CUSTOMIZING       2         2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2         2.4.3       Resistance Checks       2         2.4.4       Installation of Add-On DV11       2         2.5       SYSTEM CHECKOUT       2         CHAPTER 3       PROGRAMMING       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3 <t< td=""><td>1.3.1</td><td></td><td>-3</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.3.1     |                                       | -3 |

| 2.1.1       Minimum Through Maximum Configurations       2         2.1.2       Compatibility Considerations and Precautions       2         2.1.3       Interface Specifications and Signals       2         2.1.4       Interrupt Priorities and Address Assignments       2         2.1.4.1       Interrupt Priorities       2         2.1.4.2       Interrupt Vector Address Assignment       2         2.1.4.3       Address Assignments       2         2.1.5       Environment       2         2.2       UNPACKING AND INSPECTION       2         2.3       INSTALLATION OF BASIC ASSEMBLIES       2         2.3.1       Unibus Cable Interconnections       2         2.4       MODULE INSTALLATION AND CUSTOMIZING       2         2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2         2.4.3       Resistance Checks       2         2.4.4       Installation of Add-On DV11       2         2.5       SYSTEM CHECKOUT       2         CHAPTER 3       PROGRAMMING         3.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1 <td< td=""><td>CHAPTER 2</td><td>INSTALLATION</td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CHAPTER 2 | INSTALLATION                          |    |

| 2.1.1       Minimum Through Maximum Configurations       2         2.1.2       Compatibility Considerations and Precautions       2         2.1.3       Interface Specifications and Signals       2         2.1.4       Interrupt Priorities and Address Assignments       2         2.1.4.1       Interrupt Priorities       2         2.1.4.2       Interrupt Vector Address Assignment       2         2.1.4.3       Address Assignments       2         2.1.5       Environment       2         2.2       UNPACKING AND INSPECTION       2         2.3       INSTALLATION OF BASIC ASSEMBLIES       2         2.3.1       Unibus Cable Interconnections       2         2.4       MODULE INSTALLATION AND CUSTOMIZING       2         2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2         2.4.3       Resistance Checks       2         2.4.4       Installation of Add-On DV11       2         2.5       SYSTEM CHECKOUT       2         CHAPTER 3       PROGRAMMING         3.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1 <td< td=""><td>21</td><td>SITE PREPARATION AND PLANNING</td><td>.1</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21        | SITE PREPARATION AND PLANNING         | .1 |

| 2.1.2       Compatibility Considerations and Precautions       2         2.1.3       Interface Specifications and Signals       2         2.1.4       Interrupt Priorities and Address Assignments       2         2.1.4.1       Interrupt Priorities       2         2.1.4.2       Interrupt Vector Address Assignment       2         2.1.4.3       Address Assignments       2         2.1.5       Environment       2         2.2       UNPACKING AND INSPECTION       2         2.3       INSTALLATION OF BASIC ASSEMBLIES       2         2.3.1       Unibus Cable Interconnections       2         2.4       MODULE INSTALLATION AND CUSTOMIZING       2         2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2         2.4.3       Resistance Checks       2         2.4.4       Installation of Add-On DV11       2         2.5       SYSTEM CHECKOUT       2         CHAPTER 3       PROGRAMMING         3.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                                       | -1 |

| 2.1.3       Interface Specifications and Signals       2         2.1.4.1       Interrupt Priorities and Address Assignments       2         2.1.4.2       Interrupt Vector Address Assignment       2         2.1.4.3       Address Assignments       2         2.1.5       Environment       2         2.2       UNPACKING AND INSPECTION       2         2.3       INSTALLATION OF BASIC ASSEMBLIES       2         2.3.1       Unibus Cable Interconnections       2         2.4       MODULE INSTALLATION AND CUSTOMIZING       2         2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2         2.4.3       Resistance Checks       2         2.4.4       Installation of Add-On DV11       2         2.5       SYSTEM CHECKOUT       2         CCHAPTER 3       PROGRAMMING         3.1       PROGRAMMABLE FACILITIES AND FUNCTIONS       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.3.1       Modem Setup and Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | · · · · · · · · · · · · · · · · · · · | -1 |

| 2.1.4.1       Interrupt Priorities and Address Assignments       2         2.1.4.2       Interrupt Vector Address Assignment       2         2.1.4.3       Address Assignments       2         2.1.5       Environment       2         2.2       UNPACKING AND INSPECTION       2         2.3       INSTALLATION OF BASIC ASSEMBLIES       2         2.3.1       Unibus Cable Interconnections       2         2.4       MODULE INSTALLATION AND CUSTOMIZING       2         2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2         2.4.3       Resistance Checks       2         2.4.4       Installation of Add-On DV11       2         2.5       SYSTEM CHECKOUT       2         CCHAPTER 3       PROGRAMMING         3.1       PROGRAMMABLE FACILITIES AND FUNCTIONS       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                                       | -  |

| 2.1.4.1       Interrupt Priorities       2         2.1.4.2       Interrupt Vector Address Assignment       2         2.1.4.3       Address Assignments       2         2.1.5       Environment       2         2.2       UNPACKING AND INSPECTION       2         2.3       INSTALLATION OF BASIC ASSEMBLIES       2         2.3.1       Unibus Cable Interconnections       2         2.4       MODULE INSTALLATION AND CUSTOMIZING       2         2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2         2.4.3       Resistance Checks       2         2.4.4       Installation of Add-On DV11       2         2.5       SYSTEM CHECKOUT       2         CHAPTER 3       PROGRAMMING         3.1.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                                       |    |

| 2.1.4.2       Interrupt Vector Address Assignment       2         2.1.4.3       Address Assignments       2         2.1.5       Environment       2         2.2       UNPACKING AND INSPECTION       2         2.3       INSTALLATION OF BASIC ASSEMBLIES       2         2.3.1       Unibus Cable Interconnections       2         2.4       MODULE INSTALLATION AND CUSTOMIZING       2         2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2         2.4.3       Resistance Checks       2         2.4.4       Installation of Add-On DV11       2         2.5       SYSTEM CHECKOUT       2         CHAPTER 3       PROGRAMMING         3.1       PROGRAMMABLE FACILITIES AND FUNCTIONS       3         3.1.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                                       |    |

| 2.1.4.3       Address Assignments       2         2.1.5       Environment       2         2.2       UNPACKING AND INSPECTION       2         2.3       INSTALLATION OF BASIC ASSEMBLIES       2         2.3.1       Unibus Cable Interconnections       2         2.4       MODULE INSTALLATION AND CUSTOMIZING       2         2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2-         2.4.3       Resistance Checks       2-         2.4.4       Installation of Add-On DV11       2-         2.5       SYSTEM CHECKOUT       2-         CHAPTER 3       PROGRAMMABLE FACILITIES AND FUNCTIONS       3         3.1.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                                       |    |

| 2.1.5       Environment       2         2.2       UNPACKING AND INSPECTION       2         2.3       INSTALLATION OF BASIC ASSEMBLIES       2         2.3.1       Unibus Cable Interconnections       2         2.4       MODULE INSTALLATION AND CUSTOMIZING       2         2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2-         2.4.3       Resistance Checks       2-         2.4.4       Installation of Add-On DV11       2-         2.5       SYSTEM CHECKOUT       2-         CHAPTER 3       PROGRAMMING         3.1.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3 <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |                                       |    |

| 2.2       UNPACKING AND INSPECTION       2         2.3       INSTALLATION OF BASIC ASSEMBLIES       2         2.3.1       Unibus Cable Interconnections       2         2.4       MODULE INSTALLATION AND CUSTOMIZING       2         2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2-         2.4.3       Resistance Checks       2-         2.4.4       Installation of Add-On DV11       2-         2.5       SYSTEM CHECKOUT       2-         CHAPTER 3       PROGRAMMING         3.1       PROGRAMMABLE FACILITIES AND FUNCTIONS       3         3.1.1       Programmable Registers       3         3.1.2.1       Control Table       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |                                       |    |

| 2.3       INSTALLATION OF BASIC ASSEMBLIES       2         2.3.1       Unibus Cable Interconnections       2         2.4       MODULE INSTALLATION AND CUSTOMIZING       2         2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2         2.4.3       Resistance Checks       2         2.4.4       Installation of Add-On DV11       2         2.5       SYSTEM CHECKOUT       2         CHAPTER 3       PROGRAMMING         3.1       PROGRAMMABLE FACILITIES AND FUNCTIONS       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |                                       |    |

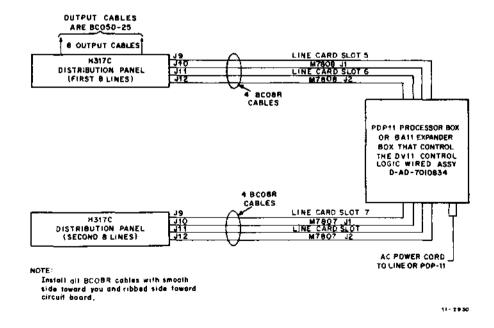

| 2.3.1       Unibus Cable Interconnections       2         2.4       MODULE INSTALLATION AND CUSTOMIZING       2         2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2-         2.4.3       Resistance Checks       2-         2.4.4       Installation of Add-On DV11       2-         2.5       SYSTEM CHECKOUT       2-         CHAPTER 3       PROGRAMMING         3.1       PROGRAMMABLE FACILITIES AND FUNCTIONS       3         3.1.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                                       |    |

| 2.4       MODULE INSTALLATION AND CUSTOMIZING       2         2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2-         2.4.3       Resistance Checks       2-         2.4.4       Installation of Add-On DV11       2-         2.5       SYSTEM CHECKOUT       2-         CHAPTER 3       PROGRAMMING         3.1       PROGRAMMABLE FACILITIES AND FUNCTIONS       3         3.1.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |                                       |    |

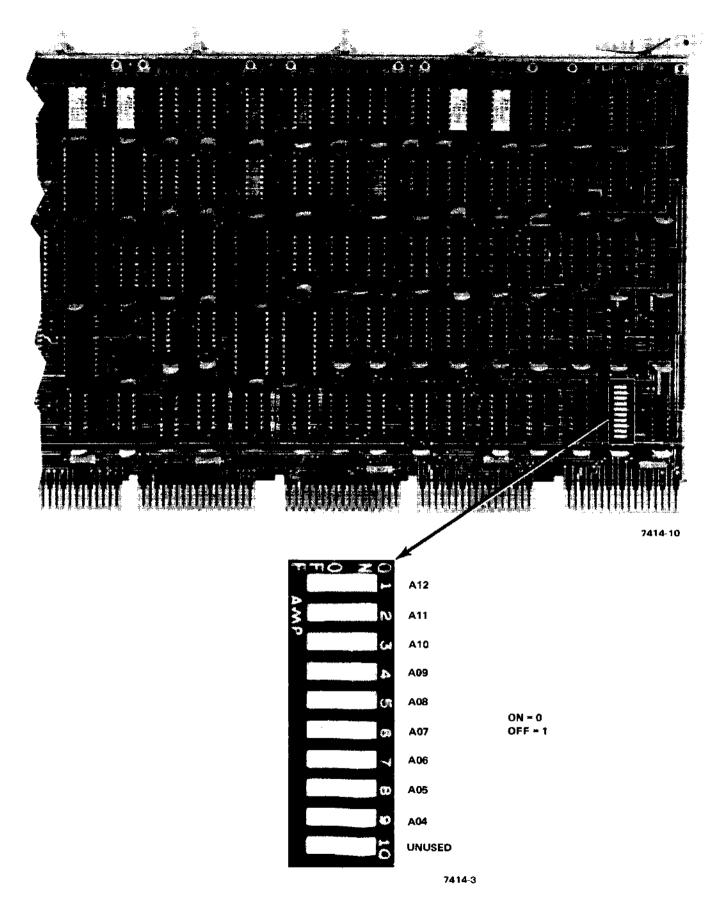

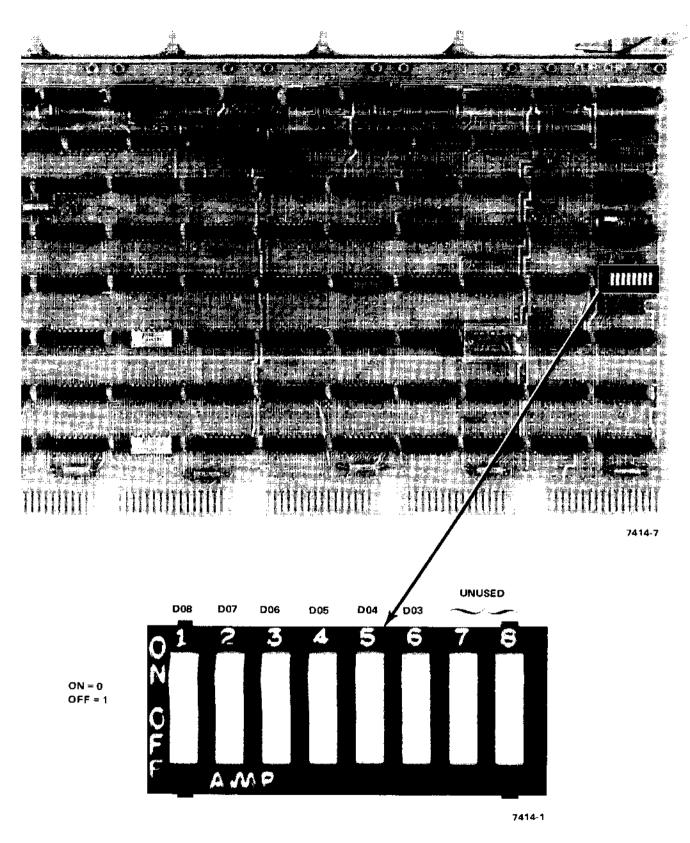

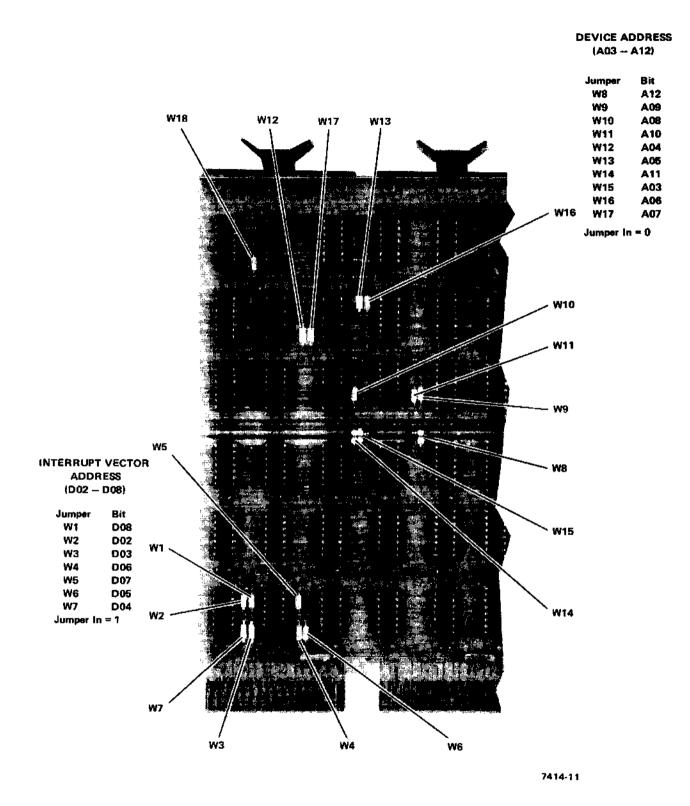

| 2.4.1       Unibus and Interrupt Vector Address Assignments       2         2.4.2       Synchronous Parameter Selection       2-         2.4.3       Resistance Checks       2-         2.4.4       Installation of Add-On DV11       2-         2.5       SYSTEM CHECKOUT       2-         CHAPTER 3       PROGRAMMING         3.1       PROGRAMMABLE FACILITIES AND FUNCTIONS       3         3.1.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                                       | _  |

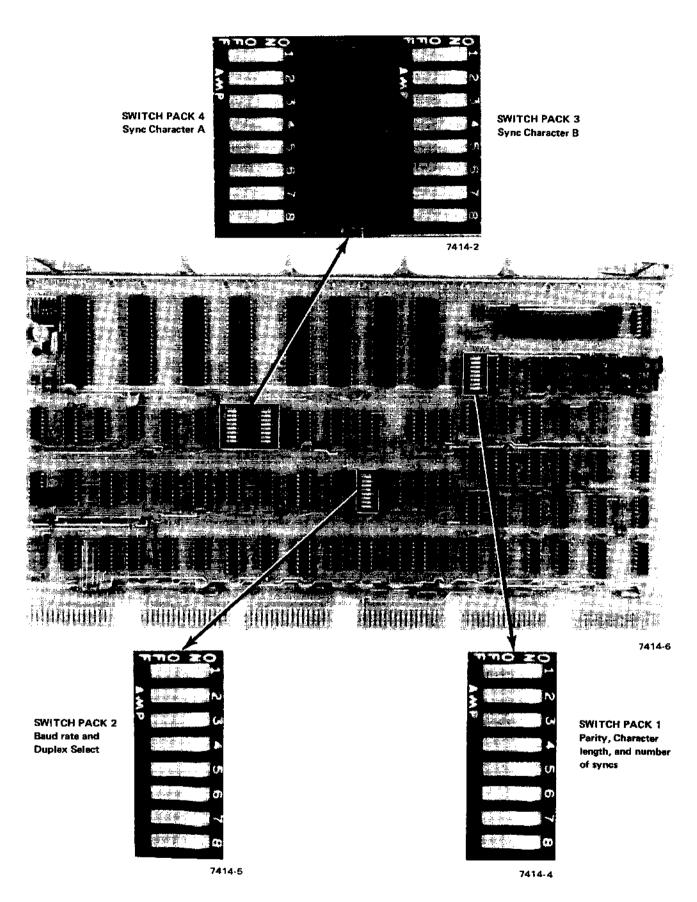

| 2.4.2       Synchronous Parameter Selection       2-         2.4.3       Resistance Checks       2-         2.4.4       Installation of Add-On DV11       2-         2.5       SYSTEM CHECKOUT       2-         CHAPTER 3       PROGRAMMING         3.1       PROGRAMMABLE FACILITIES AND FUNCTIONS       3         3.1.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |                                       | _  |

| 2.4.3       Resistance Checks       2-         2.4.4       Installation of Add-On DV11       2-         2.5       SYSTEM CHECKOUT       2-         CHAPTER 3       PROGRAMMING         3.1       PROGRAMMABLE FACILITIES AND FUNCTIONS       3         3.1.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | · · · · · · · · · · · · · · · · · · · |    |

| 2.4.4       Installation of Add-On DV11       2-         2.5       SYSTEM CHECKOUT       2-         CHAPTER 3       PROGRAMMING         3.1       PROGRAMMABLE FACILITIES AND FUNCTIONS       3         3.1.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           | ·                                     |    |

| 2.5       SYSTEM CHECKOUT       2-         CHAPTER 3       PROGRAMMING         3.1       PROGRAMMABLE FACILITIES AND FUNCTIONS       3         3.1.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -         |                                       |    |

| CHAPTER 3         PROGRAMMING           3.1         PROGRAMMABLE FACILITIES AND FUNCTIONS         3           3.1.1         Programmable Registers         3           3.1.2         Control Table         3           3.1.2.1         Control Table Format         3           3.1.2.2         Receive Control Byte         3           3.1.2.3         Transmit Control Byte         3           3.1.2.4         Control Byte Symmetry         3           3.1.3         Operations With Directly-Addressable Registers         3           3.1.3.1         Modem Setup and Control         3           3.1.3.2         Accessing Secondary Registers         3           3.1.3.3         Data Transfer Enabling         3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                                       |    |

| 3.1       PROGRAMMABLE FACILITIES AND FUNCTIONS       3         3.1.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.5       | SYSTEM CHECKOUT                       | 17 |

| 3.1.1       Programmable Registers       3         3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CHAPTER 3 | PROGRAMMING                           |    |

| 3.1.2       Control Table       3         3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3.1       | PROGRAMMABLE FACILITIES AND FUNCTIONS | -1 |

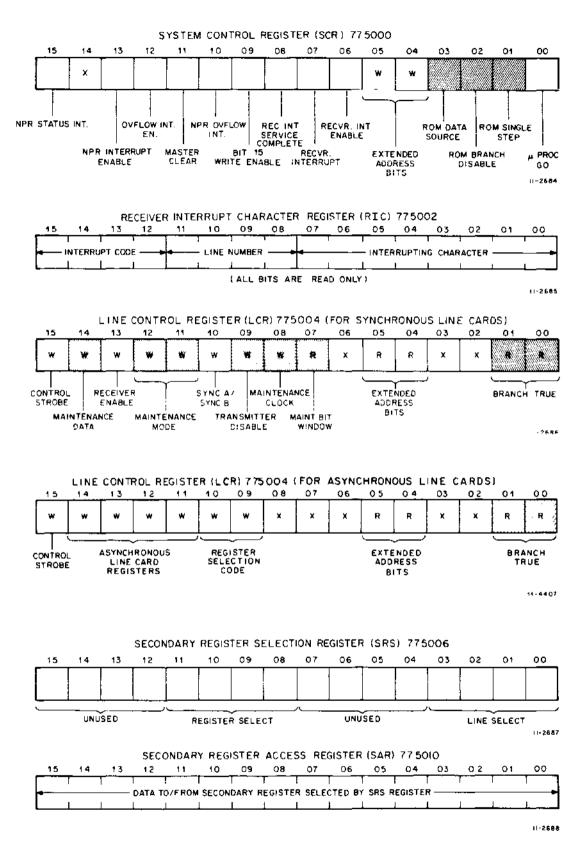

| 3.1.2.1       Control Table Format       3         3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.1.1     | Programmable Registers                | -1 |

| 3.1.2.2       Receive Control Byte       3         3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.1.2     | Control Table                         | -4 |

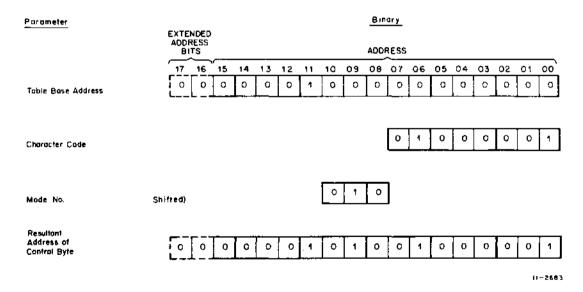

| 3.1.2.3       Transmit Control Byte       3         3.1.2.4       Control Byte Symmetry       3         3.1.3       Operations With Directly-Addressable Registers       3         3.1.3.1       Modem Setup and Control       3         3.1.3.2       Accessing Secondary Registers       3         3.1.3.3       Data Transfer Enabling       3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3.1.2.1   | Control Table Format                  | 4  |

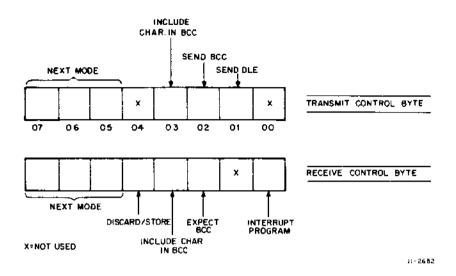

| 3.1.2.4       Control Byte Symmetry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.1,2.2   | Receive Control Byte                  | 4  |

| 3.1.3       Operations With Directly-Addressable Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.1.2.3   | Transmit Control Byte                 | -5 |