D. Vonada

# digital

# INTEROFFICE MEMORANDUM

DATE: 6 November 1967

SUBJECT: PDP-X Processor Description

TO: Distribution Lists A, B, C. FROM: H. Burkhardt

Attached is a revised version of PDP-X Technical Memorandum #13 which is now obsolete and should be destroyed. Many areas of the central processor architecture have been changed, revised or completely changed. It is, therefore, suggested that this document be read fully.

The areas of major change are:

- 1. The elimination of the floating-point registers from the memory address space.

- 2. The addition of several trap conditions and a general re-arrangement of the PSW.

- 3. The addition of an additional mode on the DIV and LDIV instructions allowing for integer operations.

- 4. The elimination of the IOX instruction and the addition of the IORC and IOWC instructions.

- 5. The addition of several IOD class instructions including HALT and CONSOLE SWITCH operations.

- 6. A change in the memory protection instructions.

- The addition of an additional multiplexor channel priority (level 8).

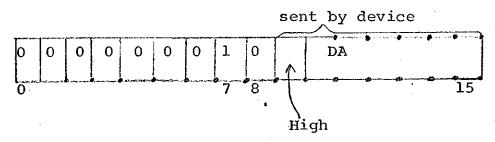

- 8. A change in the way in which a device is granted an interrupt. This includes a change in the Status Registers of all devices previously described in TM's 7, 8, 9, 15 (i.e., the change of the LOW bit to a HIGH bit).

- A reduction to 200<sub>8</sub> (from 400<sub>8</sub>) of the number of memory words reserved for the handling of device interrupts.

This drawing and specifications, herein, are the property of Digital Equipment Comporation and shall not be reproduced or copied or used in whole or in part as the basis for the manufacture or sale of items without written permission.

#### PDP-X Technical Memorandum # 29

Title:

PDP-X Processor Description

Author(s):

H. Burkhardt

L. Seligman

Index Keys:

Architecture

Instruction Set

Processor

Distribution

Keys:

A,B,C

Obsolete:

Technical Memorandum # 13

Revision:

None

Date:

October 16, 1967

#### Index

| 1 | . ( | ገ . | Intr  | റ്ഷാം | ~+ i | Λn       |

|---|-----|-----|-------|-------|------|----------|

| _ | ٠,  | ,   | TILLE | Ouu   |      | $o_{11}$ |

#### 1.1 Models

#### 2.0 Processor Architecture

- 2.1 Instruction Format

- 2.2 Data Formats

- 2.2.1 Fixed-Point Arithmetic Operations

- 2.2.2 Logical Operations

- 2.2.3 Floating-Point Operations

- 2.2.4 Character Operations

- 2.2.5 Byte Pointer

- 2.2.6 Character Set

- 2.3 Addressing

- 2.3.1 Addressing Exceptions

- 2.3.2 Address Calculation

- 2.4 General Registers

- 2.5 Program Status Word

- 2.5.1 Traps

- 2.5.2 Condition Codes

- 2.6 Instructions

- 2.6.1 Basic Instructions

- 2.6.2 Extended Operation Class

- 2.6.3 Extended Arithmetic Group

- 2.6.4 Character Group

- 2.6.5 Logical Compare and Modify Group

- 2.6.6 Push Down Group

- 2.6.7 IO Instructions

- 2.7 Priority (Interrupt) System

- 2.8 Protection Feature

- 2.8.1 \* Instruction Protection

- 2.8.2 Memory Protection

- 2.8.3 Monitor Calls

- 2.8.4 Instructions for Memory Protection System

- 2.8.5 Summary

#### 3.0 IO System

- 3.1 · Devices and Controllers

- 3.2 Modes of Data Transfer

- 3.3 Operation of the Multiplexor Channel and Interrupt 3.3.1 Program Controlled Interrupt Service

- 3.3.2 Multiplexor Channel

- 3.4 Basic Peripheral Structure

- 3.5 Paper Tape Peripherals 3.5.1 Paper Tape Reader/Punch 3.5.2 Keyboard/Printer 3.5.3 Priority Assignments 3.5.4 Paper Tape Peripherals Status Bytes Device Assignment Table 3.6 3.7 IO Bus 3.7.1 General Characteristics 3.7.2 Operation 3.7.3 Line Definitions

- 3.8 IO Configurations

#### 4.0 Appendices

- 4.1 Assembly Language Conventions

- 4.2 Instructions (Alphabetic)

- 4.3 Peripheral Structure (Continued)

- 4.3.1 Flow Chart Conventions

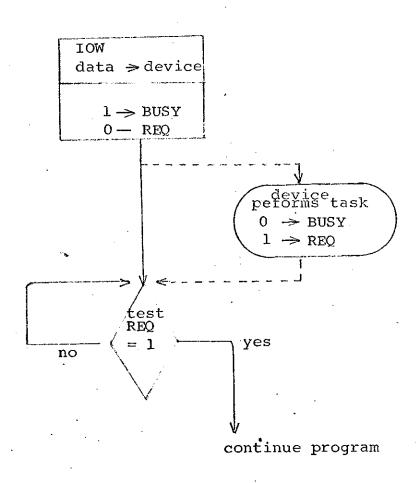

- 4.3.2 Output Device No Interrupt

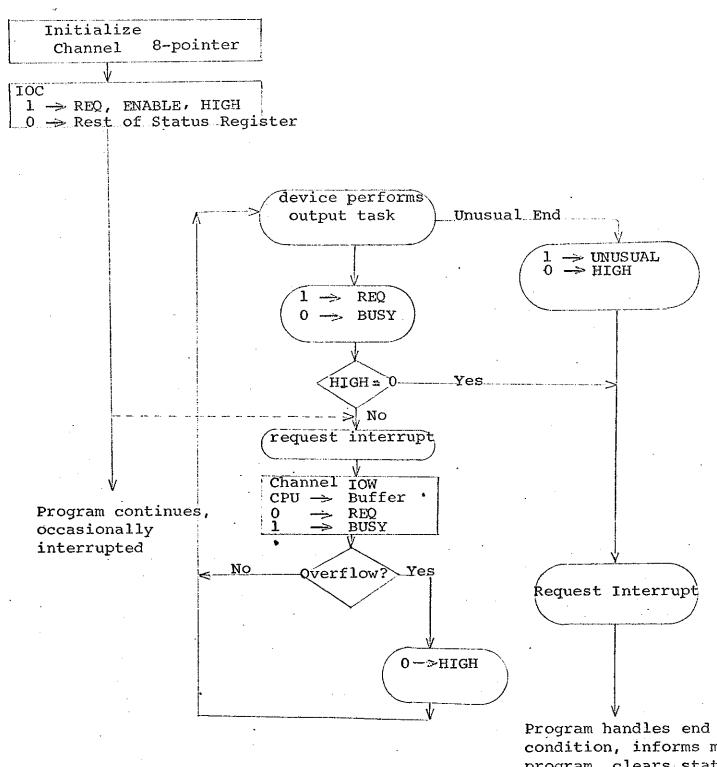

- 4.3.3 Output Device Interrupt Mode

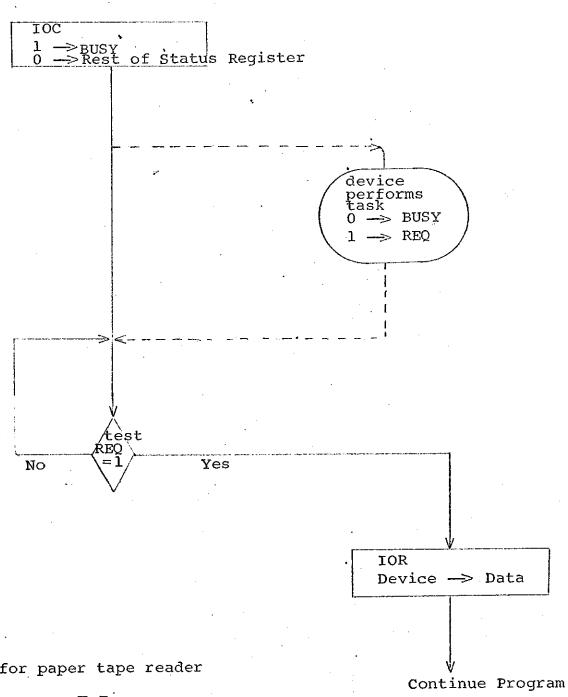

- 4.3.4 Input Device No Interrupt

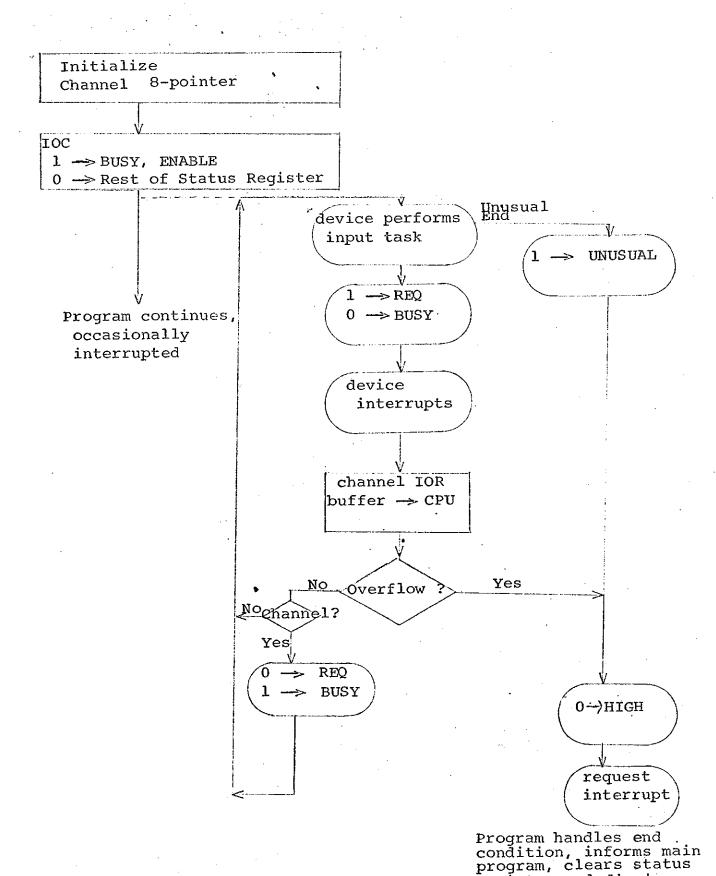

- 4.3.5 Input Device Interrupt Mode

- 4.3.6 Programming Example Punch Routine

- 4.4 Reserved Memory

#### 1.0 Introduction

pDP-X is a modern, very high performance, third generation, binary, two's complement computer family designed for the small computer market. Upward and downward (limited) program compatibility permits easy system growth and enhances application programming. Standard IO and Memory interfaces are used for all processor models and all peripheral devices. The architecture lends itself to fourth generation hardware implementation and the development of multiprocessor systems.

The system architecture of the PDP-X computer family is described below. Two particular members of the family are suggested; however, details of their implementation are beyond the scope of this document. PDP-X/I may be though of as a PDP-8 class machine, PDP-X/II as a PDP-9 class machine.

#### 1.1 Models

The smallest PDP-X model has two priority levels, main program and interrupt level, both general register sets reside in core memory. The Model I instruction set consists of only the basic imstructions; all EOP (Extend OPeration) class instructions trap. Memory is expandable from 4K to 32K. All peripheral equipment will run on Model I within the constraints of the single interrupt level.

The Model I processor may not be upgraded to a Model II processor. All of the other components of the system, however, may be used with a Model II processor.

The medium-sized PDP-X model has two sets of hardware general registers for its two princrity levels: main program and interrupt level. The Model II instruction set consists of both the basic imstructions and extended instructions. The basic configuration includes High-Speed Paper Tape, 33 KSR Telletype, and an 8K memory.

- a. The Priority Interrupt System may be added. This option adds six sets of general registers, the priority interrupt structure, amd special instructions to modify the state of the immterrupt system.

- b. The Protection Option may be added. This option consists of user mode/executive mode, the memory paging system and certain special instructions to alter the state of the paging hardware. The Priority Interrupt system is required before this option may be added.

- c. Power Fail, Memory Parity, Marchine Check hardware may be added.

- d. The memory system may be increased to 32K or to 128K, if the Protection Option is installed.

| Model             | Register<br>Sets   | Instruction<br>Set | Standard<br>Memory | Standard<br>IO                        | Interrupt<br>Structure              | Protection<br>System         | Add<br>Time | Multiply<br>Time<br>(Signed) | Index<br>Time |

|-------------------|--------------------|--------------------|--------------------|---------------------------------------|-------------------------------------|------------------------------|-------------|------------------------------|---------------|

| Ia                | 2, core            | Basic •            | 4k - 2µ            | 33 ASR                                | 2 levels                            | None                         | 8μ          | subroutine                   | 2μ            |

| ı <sub>b</sub>    | 2, core            | Basic              | 4k8μ               | 33 ASR                                | 2 levels                            | None                         | 3.2μ        | subroutine                   | .8μ           |

| II <sub>a</sub> * | 2, hard-<br>ware   | Extended<br>Set    | 8 <b>k</b> 8μ      | 33 ASR<br>High-Speed<br>Paper<br>Tape | 2 levels                            | None                         | 1.6μ        | <7μ                          | 0             |

| II                | 4 or 8<br>hardware | Extended<br>Set    | 8k8µ               | 33 ASR<br>High-Speed<br>Paper<br>Tape | 4 or 8<br>Fully<br>Nested<br>Levels | None                         | 1.6μ        | <b>&lt;</b> 7μ               | 0             |

| IIc               | 4 or 8<br>hardware | Extended<br>Set    | 16k8μ              | 33 ASR<br>High-Speed<br>Paper<br>Tape | 4 or 8<br>Fully<br>Nested<br>Levels | User/Exec<br>Modes<br>Paging | 1.6μ        | <b>&lt;</b> 7µ               | 0 '           |

<sup>\*</sup>Model II includes a byte multiplexor channel.

#### 2.0 Processor Architecture

#### 2.1 Instruction Format

| short form    |         |        |     | `              |      |                  |          |

|---------------|---------|--------|-----|----------------|------|------------------|----------|

|               | OP      | R      | х   | D <sub>1</sub> |      |                  |          |

| basic op      |         |        |     | ş              |      |                  |          |

| long form     | OP      | R      | x   | 10000          | 0001 | $D_2$            | _        |

| extended      |         |        | ,   |                |      |                  |          |

| op form       | 1 1 0   | R      | Х   | EOP            | Ţ    | D <sub>2</sub>   |          |

| •             |         |        |     |                |      |                  |          |

| instruction   | 1 1 1   | R      | х   | SB DA          | I    | D <sub>2</sub>   |          |

| •             |         | ·      |     | long form      |      |                  |          |

| immediate wor | a in Ec | )P, 10 | OL. |                |      | D3               | ,,,,,,,, |

| indirect word | Į.      |        |     | •              | I    | D <sub>2</sub> , |          |

| •             |         |        |     |                |      |                  |          |

| mnem             | bits       | definition                                                                                              |

|------------------|------------|---------------------------------------------------------------------------------------------------------|

| OP               | 3 .        | basic operation code specifying major instruction class                                                 |

| Ŕ                | 3          | general register specification or sub-function selection for non-<br>accumulator reference instructions |

| x                | 2          | index register and address mode selector                                                                |

| D <sub>1</sub> . | 8          | short form address                                                                                      |

| D <sub>2</sub>   | 15         | long form address                                                                                       |

| D <sub>2</sub> , | 15         | indirect word                                                                                           |

| D <sub>3</sub>   | 16         | immediate operand                                                                                       |

| I                | · <u>1</u> | indirect addressing specification                                                                       |

| EOP              | 8          | extended operation code specifying instruction                                                          |

| DA .             | - 6        | IO device address (device selection) .                                                                  |

| SB               | 2          | selects one of four (optional) IO busses. SB is normally 0                                              |

#### 2.2 Data Formats

The hardware and software capabilities include operations on single and double precision fixed-point data, single precision logical data, and character bytes. On the larger processors, most of the operations will be performed by the hardware. On smaller processors, the operations may be performed by resident subroutines.

#### 2.2.1 Fixed-Point Arithmetic Operations

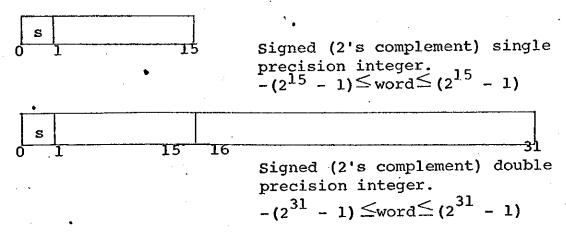

The basic arithmetic operand is the 16-bit fixed-point binary word. To preserve precision, all products and dividends are 32 bits long.

Since the 16-bit word size accommodates a 15-bit address, fixed-point arithmetic can be used both for integer operand arithmetic and for address arithmetic. Since integer and addressing arithmetic often requires repeated references to operands or to intermediate results, the use of multiple registers is advantageous in arithmetic sequences and address calculations.

Additions, subtractions, multiplications, divisions and comparisons are performed upon one operand in a register and another operand either in a register or main storage. Two's complement notation is used to facilitate multi-precision arithmetic.

The address of a double precision quantity is the address of the high-order word. This address must be even (i.e., EF fective  $Address_{15} = 0$ ).

#### 2.2.2 Logical Operations

Logical Operations are performed on 16-bit binary words with one operand in a register and another operand either in a register or in storage.

#### 2.2.3 Floating-Point Operations

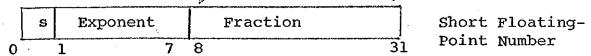

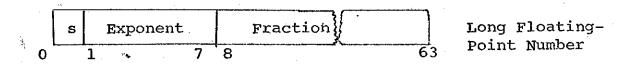

Floating-point numbers occur in either of two fixed length formats - short and long. These formats differ only in the lengths of the fractions

Operands are either 32 (two words) or 64 (four words) bits long. The short form, equivalent to seven decimal places of precision, permits a maximum number of operands to be placed in storage and gives the shortest execution times. The long form gives up to 17 decimal places of precision.

The fraction of floating-point number is expressed in hexadecimal (base 16) digits each consisting of four binary bits and having the values 0-15. In the short format, the fraction consists of six hexadecimal digits occupying bit positions 8-31. In the long format the fraction has 14 hexadecimal digits occupying bit positions 8-63. The fraction is always in positive form, the sign bit (if a 1) indicates that the number is negative.

The radix point of the fraction is assumed to be immediately to the left of the high-order fraction digit (between bits 7 and 8). To provide the proper magnitude for the floating-point number, the fraction is considered to be multiplied by a power of 16. The characteristic portion, bits 1-7 of both formats, is used to indicate the power. The characteristic is treated as an excess 64 number with a range -64 to +63 corresponding to 0-127. This permits representation of decimal numbers with magnitudes in the range of

#### 2.2.3 (Cont.)

10<sup>-78</sup> to 10<sup>75</sup>. Four 64-bit floating-point registers are provided. (This is optional; if the floating-point operations are performed by resident subroutines, the simulated registers are internal to the routines.) Arithmetic operations are performed with one operand in a register and another either in a register or from storage. The result is developed in a register. The availability of several floating-point register eliminates much storing and loading of intermediate results.

The addresses of short-form floating-point numbers must be even (EFA $_{15}$  = 0). The addresses of long form floating-point numbers must be evenly divisible by four (EFA $_{14-15}$  = 0). In either case, the address is the address of the high-order word containing the exponent.

#### 2.2.4 Character Operations

Two 8-bit bytes (characters) may be stored as a single computer word.

Packed Characters

Character 2

Character 1

7 8 15

Data transfers to and from external devices are done through an 8-bit channel. If, during and I/O read or write operation the device requests a two-byte transfer, character 1 is received (transmitted) and then character 2. If the device does not request a two-byte transfer, only character 1 of the effective word is effected.

#### 2.2.5 Byte Pointer

The left 15 bits of the byte pointer select the word address of a byte pair. Bit 15 selects one of the 2 bytes:

0 = right byte

1 = left byte

#### 2.2.6 Character Set

The character set used for PDP-X peripherals (with a few exceptions) is the USASCII character set depicted below

|     | 000   | 020 | 040   | 060 | 100 | 120      | 140 | 160  |

|-----|-------|-----|-------|-----|-----|----------|-----|------|

| ,   | 000   |     | · 040 |     |     | 120      |     |      |

| 00  | NUL   | ĎLE | SP    | 0   | , ė | Р        |     | р    |

| 01  | SOH   | DCI | !     | 1   | Α   | Q        | a   | q    |

| 02  | STX   | DC2 | ti    | 2   | В   | R        | Ь   | r    |

| 03  | ETX   | DC3 | #     | 3   | C   | S        | c   | s    |

| 04  | EOT   | DC4 | \$    | 4   | D   | T        | d   | 1    |

| 05  | ENQ   | NAK | %     | 5   | E   | U        | е   | υ    |

| 06  | ACK   | SYN | &     | 6   | F   | ٧        | f   | V    |

| 07  | BEL   | ETB | ,     | 7   | G   | W        | g   | w ·  |

| 10  | BS ·  | CAN | (     | 8   | H   | Х        | h   | ×    |

| 11  | HT    | EM  | )     | 9   | 1   | Y        | i   | У    |

| 12  | , LF∞ | SUB | *     | ;   | J   | Z        | j   | , Z  |

| 13  | VT.   | ESC | +     | ;   | K   | [        | k   | {    |

| 14  | FF,   | FS  | ,     | <   | L_  | \        | ı   |      |

| 15  | CR ·  | GS  |       | =   | M   | ]        | m   | } :  |

| 16. | SO    | RS  | •     | >   | N   | 1        | n   | ~    |

| 17  | •\$1  | US  | /     | ?   | 0   | <b>—</b> |     | DEL. |

(The octal for a given character is obtained by adding the column heading and the row heading

Ex:

$$M = 100 + 15 = 115$$

$$1.040 + 01 = 041$$

#### 2.2.6 (Cont.)

The abbreviations of the more common special characters is given below:

| BEL |       | Bell, rings bell on 33, 35, 37 Teletypes                               |

|-----|-------|------------------------------------------------------------------------|

| HT  |       | Horizontal Tab, spaces carriage to next tab stop on 35 or 37 Teletypes |

| LF  |       | Line Feed, moves paper up one printing position                        |

| VT  |       | Vertical Tab                                                           |

| FF  |       | Form Feed                                                              |

| CR  |       | Carriage Return, return carriage to beginning of line                  |

| DEL | · Mag | Delete Code                                                            |

See descriptions of particular IO devices to determine their response to these and other special characters.

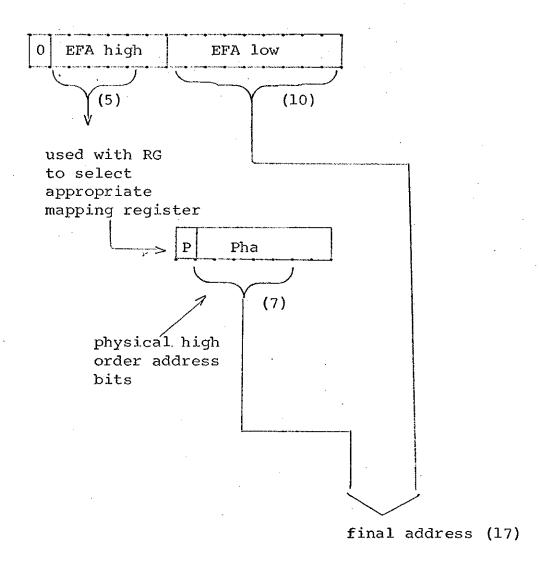

#### 2.3 Addressing

Addresses are generated by either long or short format instructions. In either case, the processor forms a 15-bit EFfective Address (EFA) which it sends to the memory system. The left byte (high order 7 bits) of the address is called the field; there are 128 fields of 256 words each.

The available addressing modes are:

- a. direct (no indexing) to any word in memory

- b. relative  $(\pm 127_{10})$  to the instruction

- c. immediate (the next location is the effective address)

- d. indexed

- e. linked (the subroutine linkage register is used to pick up arguments or to make returns)

In the short format, the displacement (D1) is treated as a sign extended two's complement number ( $|D1| \le 177_8$ ), unless the addressing mode is direct. In this case, D1 is a field 0 address. Long format instructions are specified whenever D1 = 200 or whenever the instruction implicitly forces this format (all IO and extended op code instructions).

The address mode is, thus, a function of format (short or long) and of the X bits of the instruction:

#### Addressing Table (Effective Address Calculation)

| X   | Short                       | Long (Instruction = IO or<br>EOP or D1 = 200 <sub>8</sub> ) |

|-----|-----------------------------|-------------------------------------------------------------|

| Q   | Dl (Field 0)                | D2 (Direct)                                                 |

| 1 . | +Dl + PC (Relative)         | PC + 1 (Immediate)                                          |

| .2  | $+\tilde{D}l + R2$ (Linked) | D2 + R2 (Linked)                                            |

|     | indexed by subroutine       | indexed by subroutine                                       |

|     | linkage register            | linkage register                                            |

| 3   | +Dl + R3 (Indexed)          | D2 + R3 (Indexed)                                           |

#### 2.3 (Cont.)

One of the primary uses of index registers arises from their ability to modify instruction addresses. For this to occur, the instruction must specify the particular register that is to take part in the modifying activity. This is done by placing the appropriate bit configuration in the X field (bit positions 6 and 7) of the instruction.

PDP-X has 2 index registers and provides for relative addressing. Index register coding is:

- 0 non-indexing

- relative addressing (index by program counter) or immediate mode in long form

- 2 index registers

- "3 index registers

The assignment of the appropriate bit configuration in the X field selects the index register to be used in the modifying activity. The instruction is then executed as if its address field contained the stated address plus (two's complement) the contents of the index register. For example, assume that storage location 01000 contains the instruction ADD 02000 and that this instruction has a 2 in its X field. If the contents of index register 2 are 117, the number stored in location 2117 is added into the accumulator when the ADD instruction is executed. However, location 01000 still contains the instruction ADD 2000 in its original form. Address 02117 is called the effective address.

The basic addressable unit is the word (two bytes, 16 bits), although certain instructions do reference bytes or double-words. The contents of the effective address is called the Effective Word (EFW). Words in storage are consecutively numbered starting with 0. The 15-bit address field accommodates a maximum of 32,768 words. When only a part of the maximum storage capacity is available in a given installation, the available storage is continguously addressable from 0.

#### 2.3 (Cont.)

A non-existent memory trap occurs when any effective address points to a location beyond the installed capacity. The EFW of such an address is zero. The invalid address is recognized and a program trap occurs with bit 4 of the Program Status double-Word (PSW) set.

#### 2.3.1 Addressing Exceptions

When the effective address is 0 or 1 or the R bits of the instruction are either 0 or 1, i.e., the PSW, special considerations apply. Refer also to section 2.5.

Address 0 may not be arbitrarily changed. Any attempt to modify bits 10 through 12, the RG section, is ignored. All bits may be read, bits other than 10 through 12 may be written.

Address 1 may not be either read or modified under program control. Any instruction which generates an address of 1 (EFA or R) causes an address exception trap and causes the Program Counter (PC) to be unpredictably modified.

#### 2.4 General Registers

Each level of priority contains a set of 16 general registers, a Register Group (RG), 2 of which may be used as accumulators and index registers, 4 of which may be used just as accumulators and the Program Status double-Word. Two of these words, the Program Status double-Word (PSW) occupy registers 0 and 1. These registers occupy field 0 words 0 to 7 in the memory space as well as the R bits in the instruction; hence, register-to-register instructions are possible. The registers may be stored, loaded, added into, etc., depending on the operation code of the particular in-The second group of 8 registers construction used. tains the trap locations for unimplemented EOP instructions, push-down words, and hardware traps. These may be modified or read as memory words but are not explicitly referenced as accumulators. In Model II, the first 8 registers may be fast (flip-flop) registers instead of core memory as in Model I.

| regi | ster           | use                                                                        |

|------|----------------|----------------------------------------------------------------------------|

| 0    | RO             | status word, contains condition code, etc.                                 |

| 1 .  | R <sub>1</sub> | status word, contains program counter (PC) of the currently active process |

| 2    | R <sub>2</sub> | accumulator, subroutine linkage register, or secondary index               |

| 3    | R <sub>3</sub> | accumulator or main index register                                         |

| 4'   | R <sub>4</sub> | accumulator                                                                |

| 5    | R <sub>5</sub> | accumulator                                                                |

| 6    | R <sub>6</sub> | accumulator                                                                |

| 7    | ·R7            | accumulator                                                                |

| 810  | 108            | EOP, receives the updated program counter                                  |

| 910  | 118.           | EOP, receives instruction itself                                           |

| 1010 | 128            | EOP, receives effective address                                            |

#### 2.4 (Cont.)

| register                         | use                                                                  |

|----------------------------------|----------------------------------------------------------------------|

| 11 <sub>10</sub> 13 <sub>8</sub> | EOP, contains the entry point into the EOP handler, loaded into PC   |

| 1210 148                         | contains the push-down pointer                                       |

| 13 <sub>10</sub> 15 <sub>8</sub> | contains the push-down counter                                       |

| 14 <sub>10</sub> 16 <sub>8</sub> | TRAP, receives the program counter                                   |

| 15 <sub>10</sub> 17 <sub>8</sub> | TRAP, contains the entry point into the TRAP handler, loaded into PC |

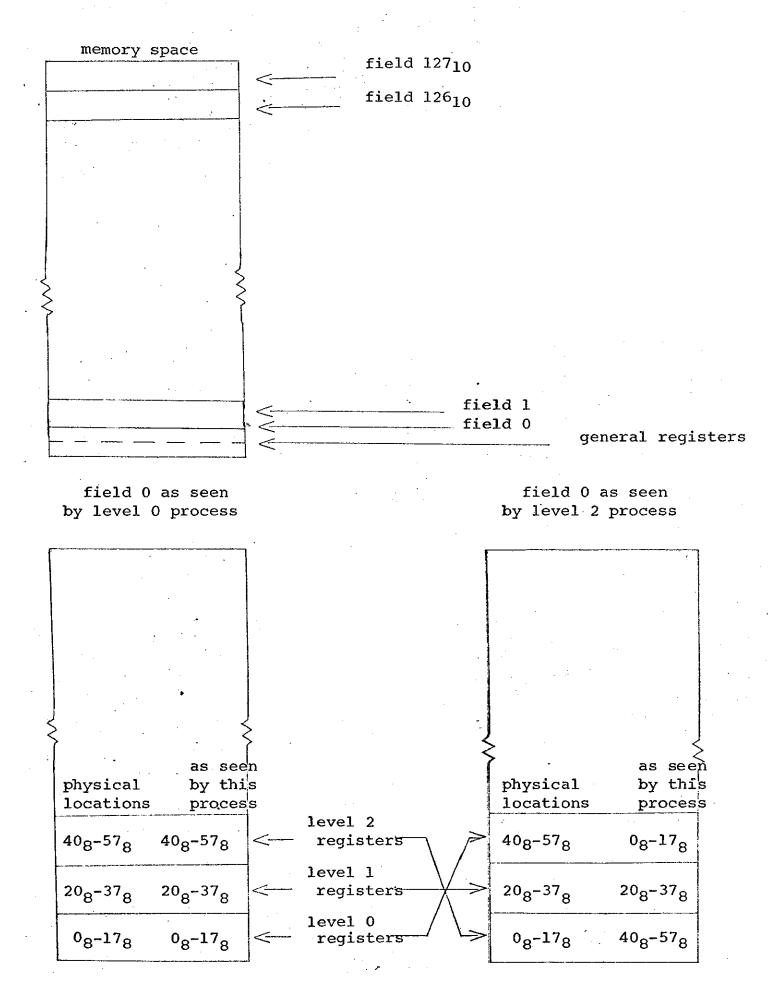

For each level of machine priority, both background and IO, there exists a set of general registers; in addition; the hardware insures that the applicable set is available at locations  $0-15_{10}$  in (apparent) memory address space. Thus, the general registers need not be stored and restored during interrupts. (See section 2.7.)

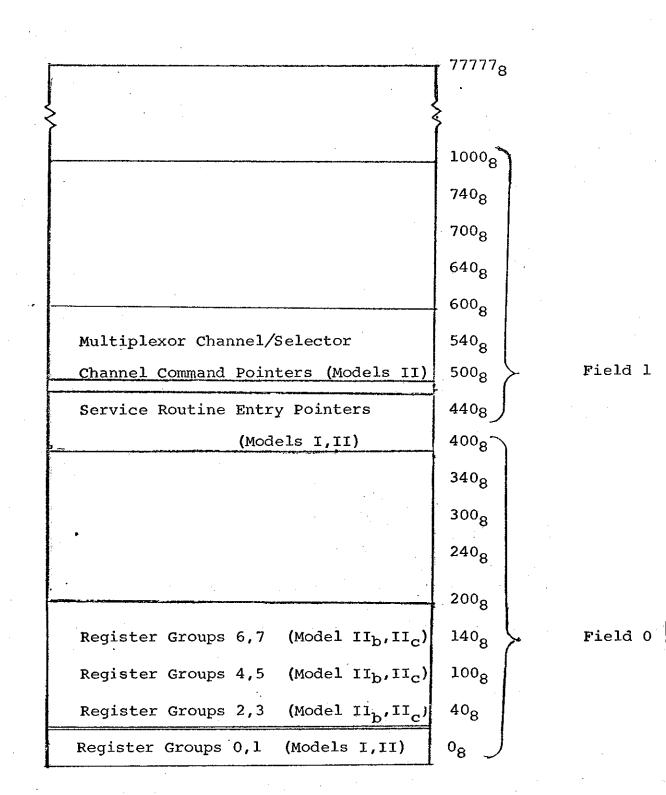

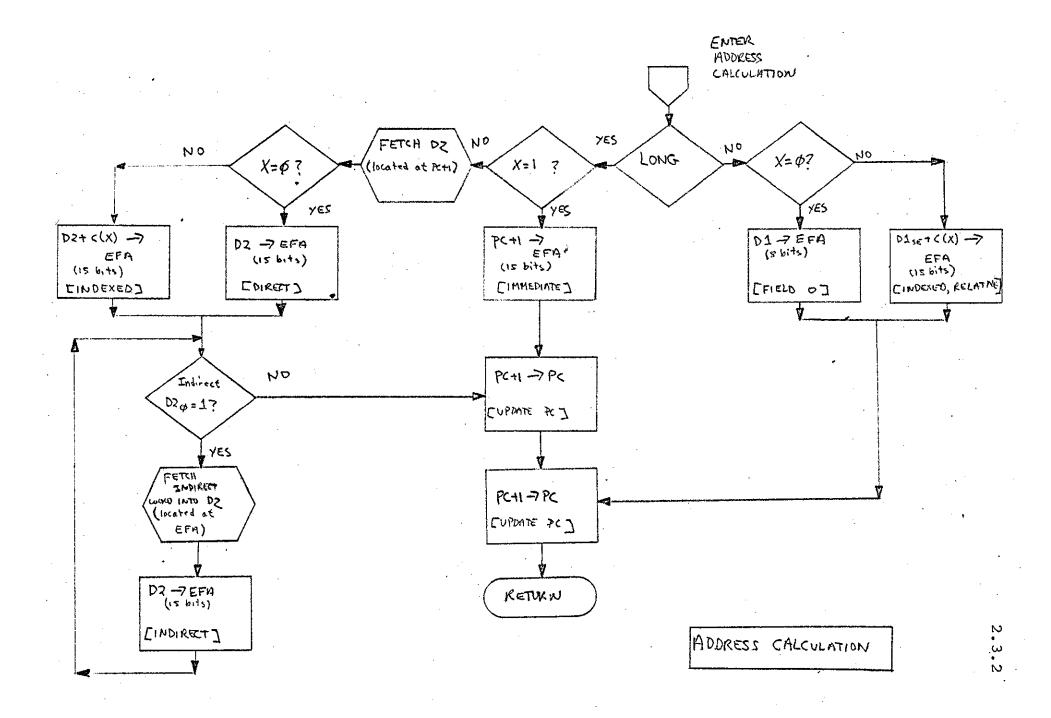

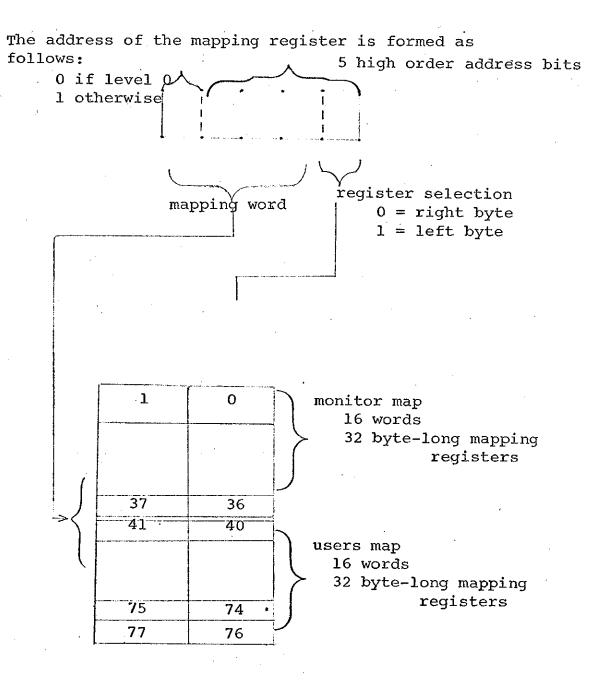

The set of general registers map onto the main memory in field 0. The following figure shows the entire memory space; the figure on the right is an exploded view of physical memory. Apparent memory is the memory space as seen by the running process; this differs from physical memory in the location of its general registers as is shown for a priority level 2 process in the bottom figure. The hardware operates as follows:

- a. whenever an address in the range of 0-15<sub>10</sub> is encountered, the RG bits are added to the address in bit positions 9-11<sub>10</sub>.

- b. whenever bits 9-11 of the address are equal to the RG\* bits and address bits 1-8 are zeros, bits 9-11 of the address are cleared.

#### 2.5 Program Status Word

The collection of bits that constitute the state of the processor between instructions is called, collectively, the Program Status Word (PSW). This state word occupies the double-word at memory locations 0 and 1 of the active process, corresponding to general registers  $R_{\rm O}$  and  $R_{\rm I}$ .

| Location | 0 | ENA    | BLE | S         | TR | AP ( | CON | DIT: | CONS | 5  | * |    | RG | ·  |    | СС |    |

|----------|---|--------|-----|-----------|----|------|-----|------|------|----|---|----|----|----|----|----|----|

|          | 1 | *      |     |           |    |      | PC  |      |      |    |   |    |    |    |    |    |    |

|          | : | 0<br>* |     | ,2<br>sed | 3  | 4    | 5   | 6    | 7    | 8. | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|          | 1 ,2 3 4 5 6 7 8 9 10 11 12 13 14 15<br>Inused                                                                     |

|----------|--------------------------------------------------------------------------------------------------------------------|

| Bit(s)   | Definition                                                                                                         |

| 0        | Arithmetic trap enable (bit 2)                                                                                     |

| 1        | Error trap enable (bits 3-6)                                                                                       |

| <b>2</b> | Arithmetic (add, divide, shift, float-<br>ing, etc.); enabled if bit 0 = 1                                         |

| 3        | Push-down list error; enabled if bit 1 = 1                                                                         |

| 4        | Non-existent memory (reference to an address not in the memory system); enabled if bit 1 = 1                       |

| 5        | Address exception; enabled if bit 1 = 1                                                                            |

| 6        | <pre>IO error (IC device did not respond to IO instruction or a bus parity oc- curred); enabled if bit 1 = 1</pre> |

| 7.       | Privileged instruction (attempt to execute a system instruction while in user mode)                                |

| 8        | Read only violation (attempt to write into a protected memory area)                                                |

| 9        | Unused                                                                                                             |

| 10-12    | Priority of active process (current Register Group)                                                                |

| 13       | Condition code bit 0                                                                                               |

# 2.5 (Cont.)

| Bit(s) | Definition                        |

|--------|-----------------------------------|

| 14     | Condition code bit 1              |

| 15     | Condition code bit 2              |

| 16     | Unused                            |

| 17-31  | Program counter of active process |

#### 2.5.1 Traps

Program status word bits 0-8 constitute the trap indicators and the error trap enable bits; a trap occurs when an unusual condition is detected by the hardware. The trap source bit, and the new register group is given in the table below. Refer to the section on the protection feature for further explanation of the privileged instruction and protection violation traps.

During a trap, the program counter (usually points to the instruction causing the error source) is stored in register  $14_{10}$ , a new address, contained in register  $15_{10}$ , is loaded into the program counter and the appropriate PSW trap bit is set. The trap enable bits (0, 1) are then cleared.

In the case of a protection violation trap (bits 7-8) where priority changes, the change in register groups occurs before the PC is stored and reloaded.

PSW bit

Source

New Priority and RG

2 Arithmetic Error

Same

ADD: Magnitude of sum greater than register capacity .

SUB: Magnitude of difference greater than register capacity

DIV.

LDIV: Magnitude of quotient greater than register capacity

#### PSW bit

#### Source

New Priority and RG

SHFT: (Arit

(Arithmetic left shift only) sign bit (0) changed during shift

#### 3 Push-Down List Error

Same

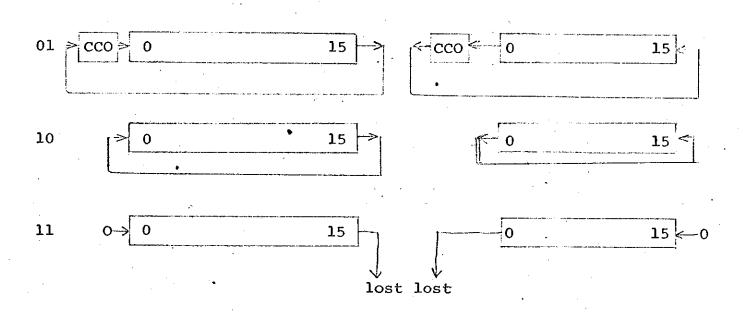

Execution of PUSH type instruction with counter word of form

Execution of POP type instruction with counter word of form

(See section 2.6.6)

#### 4 Non-existent Memory

Same

Attempt to address a word not available in the memory system, i.e., no memory responds to a processor request. In a time-sharing environment, this error indicates an attempt to use a page whose assignment was never requested (see Section 2.8)

#### 5 Address Exception

Same

Attempt to reference location 1, the program counter of the currently active process. The effect of instruction execution depends upon the model. The contents of the PC may be lost.

#### PSW bit

Source

New Priority and RG

6 IO Error

Same

The IO device addressed by an IO class instruction did not respond (see Section 2.6.7) or a parity error was detected on the IO bus (optional).

7 Privileged Instruction

Monitor

Attempt by user mode (see protection system Section 2.8) program to execute an IO class instruction.

8 Read-Only Violation

Monitor

Attempt by the user mode program to write into a read-only page (see Section 2.8).

#### 2.5.2 Condition Codes

The condition codes (PSW bits 13, 14, 15) are used to determine conditional branches as the result of arithmetic and certain other operations. The codes are normally not changed during load, store, and branch instructions; the appendix contains an instruction list which indicates which instructions effect these PSW bits.

These bits, when changed, reflect the result of the operation just performed; previous condition code information is lost. Hence, the code bits must be tested before the next instruction which changes these bits is executed.

| BIT |    | Normal Meaning                                                                  |

|-----|----|---------------------------------------------------------------------------------|

| 13  | V. | Carry during add, borrow during subtract, end bit for certain rotate operations |

| 14  |    | Negative result                                                                 |

| 15  |    | Nonzero result                                                                  |

#### 2.6 Instructions

Instructions may be divided into two groups, basic and extended. The basic instructions appear in both models and may be in either long or short format. Extended instructions are implemented in Model II, they trap when executed in Model I; extended instructions exist in long format only. The instruction class is determined by the three Op Code bits (0,1,2) of the instruction word. EOP (extended) instructions are characterized by a 110 pattern in the Op Code and the specific operation in the D<sub>1</sub> bits.

Instructions may also be classified by the type of the operand effected. These include:

| Class:     | Operand:                                  |

|------------|-------------------------------------------|

| arithmetic | signed words                              |

| logical    | unsigned words                            |

| floating   | floating point double/<br>quadruple words |

| branch     | address pointers                          |

| IO         | IO system                                 |

#### 2.6.1 Basic Instructions

| •             |     |      |                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>a</b> 1556 | ΟD  | mnem | Definition                                                                                                                                                                                                                                                                                                                                                                       |

| Class         | OP_ | mnem | Delinicion                                                                                                                                                                                                                                                                                                                                                                       |

| load          | 0   | LDA  | LoaD specified Accumulator (R) with the effective word; the condition code bits remain unchanged.                                                                                                                                                                                                                                                                                |

| store         | 1   | STA  | STore specified Accumulator (R) into memory at the effective addiress; the condition code bits remain unchanged.                                                                                                                                                                                                                                                                 |

| and           | 2   | AND  | AND specified accumulator (R) with the effective word, place result in specified accumulator; condition code 0 remains unchanged  1 set if negative result, cleared otherwise 2 set if nonzero result, cleared otherwise                                                                                                                                                         |

| add           | 3   | ADD  | ADD contents of specified accumulator (R) with the effective word following the rules of two's complement arithmetic, place re- sult in specified accumulator; condition code 0 sett if carry out of bit 0, cleared other- wise  1 sett if negative result, cleared otherwise 2 sett if nonzero result, cleared otherwise                                                        |

| branc         | h 4 |      | The arithmetic error bit (bit 2 of the PSW) is set if the sign of the result does not agree with the signs of the operands (add overflow).  General conditional branch and subroutine linkage instructions; R bits specify particular operation. If the branch is taken, the effective address is loaded into the program counter, updated to point to the instruction following |

the branch, is saved in accumulator/index register 2; the previous contents of 2 are lost. The condition code bits remain un-

changed for all branch instructions.

| Class OP | mnem | Def | inition                                                        |

|----------|------|-----|----------------------------------------------------------------|

|          |      | Ř   | Condition                                                      |

| •        | BCN  | 0   | branch if condition code bit 0 set (Branch if Carry Monzero)   |

|          | вм   | 1   | branch if condition code bit 1 set (Branch if Minus result)    |

|          | BN   | 2   | branch if condition code bit 2 set (Branch if Nonzero result)  |

|          | B    | 3   | unconditional Branch                                           |

|          | BCZ  | 4   | branch if condition code bit 0 NOT (Branch if Carry Zero)      |

|          | ВР   | 5   | branch if condition code bit 1 NOT (Branch if Positive result) |

|          | BZ   | 6   | branch if condition code bit 2 NOT (Branch if Zero result)     |

|          | BAL  | 7   | Branch And Link                                                |

SUBR:

A subroutine is a program segment that may be used many times during the computation of a program but is written only once in the whole code. As the computer proceeds down the main program the control will occasionally jump to this subroutine and then, after doing the subroutine, will jump back to the main program where it let off. This detour from the main program through the subroutine may occur several times during Hence a subroutine must the computation of the program. have an entrance, a way of getting into it, and an exit, a way of getting out of it. Each time an entrance is made to a subroutine, some initial conditions must be set up that are characteristic of the place in the main program from which the entrance was made. For instance, if the subroutine calculates some function, the initial values of the independent variables at that point in the main program must be given to the subroutine. In addition, as an entrance to a subroutine is made, the exit must be set up; i.e., the subroutine must be told where to transfer back to the main program.

BAL is the basic subroutine call instruction in PDP-X and it is used in the following manner:

BAL SUBR ; CALL

ARG 1 ; FIRST ARGUMENT

ARG N ; N<sup>th</sup> ARGUMENT

; RETURN. INSTRUCTION EXECUTED

; WHEN SUBROUTINE DONE, MORE

; THAN 1 RETURN IS POSSIBLE JUST

; AS THERE MAY BE MORE THAN

; 1 ARGUMENT

: FIRST INSTRUCTION OF SUBROUTINE

B N (2) ; RETURN TO CALLING ROUTINE

In order to nest subroutines, the subroutine linkage register must be stored in a temporary storage memory word, usually within the subroutine.

If the arguments were addresses, rather than data words, the instruction to pick up data would need to specify indirect addressing, i.e.:

LDA 4, @ J (2)

| Class  | OP | mnem  | Definition                                                                                                                                                                                                                                                          |

|--------|----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| modify | 5  |       | General memory modification instruction; the R bits specify a particular operation. Condition code bit 0 is changed only by the two rotate instructions (R = 4,5). Condition bits 1 and 2 are set as follows for all modify instructions:                           |

|        |    |       | 1 set if negative result, cleared otherwise                                                                                                                                                                                                                         |

|        |    |       | 2 set if nonzero result, cleared otherwise                                                                                                                                                                                                                          |

|        |    |       | Note: in short format these instructions may modify the accumulators or other general registers.                                                                                                                                                                    |

|        |    | r vig | R Operation                                                                                                                                                                                                                                                         |

|        |    | TST   | 0 <u>TeST</u> , no operation but condition code<br>bits 1 and 2 are set to reflect the state<br>of the effective word.                                                                                                                                              |

|        |    | COM   | logical <u>COM</u> plement, the effective word<br>is complemented on a bit-by-bit basis.                                                                                                                                                                            |

|        |    | INC   | 2 INCrement, one is added to the effective word.                                                                                                                                                                                                                    |

|        |    | NEG   | NEGate, the effective word is negated (complemented then incremented).                                                                                                                                                                                              |

|        | •  | RR    | A Rotate Right, the effective word and condition code bit 0 are rotated together as a 17-bit register one place to the right, loading condition code bit 0 from bit 15 and bit 0 of the memory word from condition code bit 0. (See Section 2.6.3 rotate with CCO.) |

|        |    | RL    | 5 Rotate Left, the effective word and condition code bit 0 are rotated left together as a 17-bit register, loading condition code bit 0 from bit 0 of the memory word and bit 15 of the memory word from condition code bit 0. (See section 2.6.3 rotate with CCO.) |

|       |    | .3   |          |                                                                              |

|-------|----|------|----------|------------------------------------------------------------------------------|

| Class | OP | mnem | De:      | finition                                                                     |

| *     |    |      |          |                                                                              |

|       |    |      | <u>R</u> | Operation                                                                    |

|       |    | SWP  | 6        | SWaP bytes, the left and right bytes of the effective word are interchanged. |

|       |    | CLR  | 7        | <u>CLeaR</u> , the effective word is set to a zero.                          |

#### 2.6.2 Extended Operation Class

| Class | OP mnem | Definition                                                                                                                                    |

|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| EOP   | 6       | Extended OPeration code class; forced long format; D <sub>1</sub> bits specify particular operation to be performed. The effect on the condi- |

|       |         | tion code bits depends upon the particular operation performed.                                                                               |

$D_1$  codes 0 through  $63_{10}$  are reserved for  $64_{10}$  programmed operators. These codes specify UUO's (UnUsed Operation codes). Codes 0 through  $31_{10}$  are reserved for user program/monitor communication since they can function as protected entry points. (See Section 2.8 on protection features.)

If the operation specified has not been implemented in the machine or if it is UUO, a trap occurs as follows:

location 8<sub>10</sub> receives the updated program counter

9 EOP instruction

10 effective address

11 contains the entry point into the EOP handler. This word is loaded into the program counter.

Note: the effective address must be in the allowable range or bit 4 of the PSW will be set and a trap may occur.

EOP Class Instruction Double-word:

#### 2.6.3 Extended Arithmetic Group

# D1 mnem Definition SUB SUBtract the effective word from the contents of the specified accumulator (R) following the rules of two's complement arithmetic; place result in the specified accumulator. condition code bit 0 set if carry out of bit 0, cleared otherwise 1 set if negative result, cleared otherwise 2 set if nonzero result, cleared otherwise

The arithmetic error bit ( bit 2 of the PSW) may be set as in ADD.

101 MUL

MULtiply. The effective word is algebraically multiplied by the low order word of the double-word specified by R. If R is even, the double-word product replaces the double-word at R and is properly signed. If the specified accumulator (R) is odd, the high order part of the double-word product is discarded. The multiplier and multiplicand are taken to be signed. No overflow is possible.

The condition codes remain unchanged.

Example:

MUL 4, 300

Multiplies the contents of register 5 by the contents of register 300 leaving the double-precision result in register 4 (high-order) and in register 5 (low-order).

MUL 5, 300

Multiplies the contents of register 5 by the contents of register 300 leaving the low-order result in register 5. The high-order result is discarded.

#### 2.6.3 Extended Arithmetic Group

# D<sub>1</sub> mnem Definition 100 LMUL Logical MULtiply. The effective word is logically multiplied by the multiplier as described for MUL, above, except that the operands are taken to be positive 16-bit logical quantities.

The condition codes remain unchanged.

DIV DIVide. The signed arithmetic double-word beginning at the specified accumulator (R) is algebraically divided by the effective word. The

signed quotient developed replaces the low-order

word of the dividend, the remainder, signed the

same as the dividend replaces its high-order part.

When the relative magnitude of dividend and divisor

is such that the quotient cannot be expressed by

a 16-bit signed integer, a divide overflow trap

occurs, no division takes place, and the dividend

may be lost.

If R is odd, the corresponding even word is filled to produce a two's complement double-precision dividend. The divide then proceeds normally. This is equivalent to an integer division.

Examples:

DIV 4, 1137

Divide the signed (two's complement) double-word in locations 4,5 by the comtents of register 1137. Place the remainder in location 4 and the quotient in location 5.

DIV 5, 113?

Divide the signed (two's complement) integer in location 5 by the contents of register 1137. Place the remainder in location 4 and quotient in location 5.

#### 2.6.3 Extended Arithmetic Group

# $D_1$ mnem Definition

The condition codes remain unchanged.

102 LDIV

Logical <u>DIV</u>ide. The logical double-word beginning at the selected register (R) is divided by the effective word. The operation performed is the same as DIV except that the operands are treated as 16 and 32-bit positive integers. The results are also 16-bit positive integers.

The condition codes remain unchanged.

If R is odd, the corresponding even word is filled with zeros to produce a domble-precision logical word. The divide then proceeds normally.

111 CMP

Algebraic CoMPare. The specified accumulator (R) and the effective word are algebraically compared as signed integers. Neither accumulator nor effective word are changed, but the condition code is set according to the result. condition code bit 0 remains unchanged

1 set if register < memory word,

cleared if≥memory word

2 set if register ≠ memory word,

cleared otherwise

110 LCMP

Logical Compare. The specified accumulator (R) and the effective word are logically compared as 16-bit positive integers. Operation proceeds and condition code is set as im CMP.

2.6.3: (Cont.)

# $\mathbf{D}_1$ mnem Definition

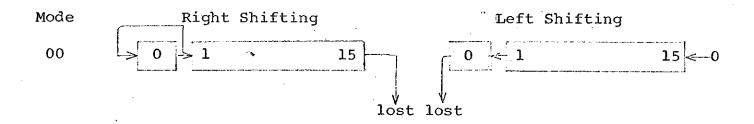

#### 113 SHFT

SHift. The contents of the specified accumulator (R) is shifted as indicated by the effective word. The right half (byte) of the effective word is used as a signed shift count. A positive value indicates a left shift. Bits 6 and 7 of the effective word indicate the type of shift to be performed. (Condition code bit 0 is changed only by the Rotate with CCO mode.) Condition code bits 1 and 2 are set as follows for all shift instructions:

- l if negative result, cleared otherwise

- 2 set if nomzero result, cleared otherwise

- 00 arithmetic shift performs two's complement multiplication by powers of two. The sign is unchanged. When going to the right, the sign is shifted into bit 1. Ones or zeros leaving bit 15 are lost. When going to the left, zeros enter bit 15. The arithmetic error bit (bit 2 of the PSW) is set if, during shifting, the sign bit is changed (left shift only).

- Ol rotate with CCO bits leaving one end enter condition code bit O. CCO enters at the other end.

- 10 rotate bits leaving one end enter at the other end.

- 11 logical shift bits leaving one end are

lost and zeros enter the other end.

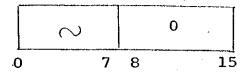

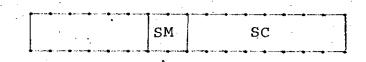

## Shift Control Word

SM = Shift Mode

SC = Signed Shift Count

00 - Arithmetic Shift

>0 **±** Left

01 - Rotate with CCO

<0 : Right

10 - Rotate

=0 : No Shift

11 - Logical Shift

# 2.6.4 Character Group

| D <sub>1</sub> | mnem | Definition                                                                                                                                                                                                                                                                                                              |

|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 114            | LDC  | LoaD Character. The effective word is used as a character pointer to locate an 8-bit                                                                                                                                                                                                                                    |

|                |      | byte. This byte is loaded into the right half of the specified accumulator (R). The left half is cleared. The addressed memory word is left unchanged. The condition code remains unchanged.                                                                                                                            |

| 115            | STC  | STore Character. The effective word is used as a character pointer to locate an 8-bit byte. The right half of the specified accumulator (R) is stored at the indicated character position. The other half of the addressed word is unaltered. The content of R remains unchanged. The condition code remains unchanged. |

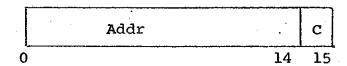

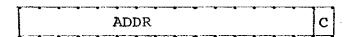

#### CHARACTER (BYTE) POINTER WORD

ADDR = address

C = character selection

O-right byte

1-left byte

Note: This is identical to the BA word in the multiplexor channel.

#### 2.6.5 Logical Compare and Modify Group

Bits of the specified accumulator (R) that are masked by bits of a memory word may be tested and/or modified to determine a conditional branch. The bits to be tested and/or modified are selected by ones in the effective word. Condition code bit 2 is cleared if all of the selected bits of the specified accumulator (R) are zero; otherwise, it is set to a one. Condition'code bit 1 is set to a one if bit 0 is selected and bit 0 of the specified accumulator (R) is a one; otherwise, it is cleared. The selected bits of the specified accumulator (R) are then modified or not depending upon the operation being performed. Condition code bit 0 is undisturbed.

| D <sub>1</sub> | mnem        | Definition                                                                                                                                                                                                                                                                                                                                                                |

|----------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 104            | TSTN ,      | TeST but change Nothing. Test the content of the specified accumulator (R) against the effective word. Set condition code bits 1 and 2 according to the result.                                                                                                                                                                                                           |

| 105            | TSTZ        | TeST and Zero selected bits. Test the content of the specified accumulator against the effective word. Set condition code bits 1 and 2 according to the results. Clear selected bits in the specified accumulator (R) (i.e., for every one in the effective word, clear the corresponding bit in the specified accumulator). This performs the logical extract operation. |

| 106            | <b>TSTO</b> | TeST and set selected bits to Ones. Test the content of the specified accumulator (R) with the effective word. Set condition code bits 1 and 2 according to the result. Set selected bits in the specified accumulator (R) (i.e., for every one in the effective word, set the corresponding bit in the specified accumulator). This performs the logical                 |

function inclusive or.

<u>D</u>1 . mnem Definition

107 TSTC

TeST and Complement selected bits. Test the content of the specified accumulator with the effective word. Set condition code bits 1 and 2 according to the result. Complement selected bits in the specified accumulator (R) (i.e., for every one in the effective word, complement the corresponding bit in the specified accumulator). This performs the logical function exclusive or.

#### 2.6.6 Push-Down Group

Words are pushed into (popped from) memory under control of pointer and counter words. General register 148 is the push-down pointer. Its contents indicate the first free location on the push-down list. General register 158 is the push-down counter which insures that the space allotted to the list is not exceeded. Maximum push-down list length is 256 words. Exceeding the list capacity while either storing or retrieving causes a push-down error trap with bit 3 of the PSW set. The registers are incremented/decremented on each instruction.

The list control registers are initialized by placing the starting (lowest) address of the list in the pointer word and the length of the list (positive integer  $\leq 255_{10}$ ) in the counter word. During a push-type instruction, the pointer is used then incremented; the counter left byte is incremented; the right byte decremented. During a POP-type instruction, the pointer is decremented then used; the counter left byte is decremented, the right byte is incremented. A trap occurs whenever a byte whose value is 0 is decremented.

All 8 (specified by the R field) Push/Pop class instructions manipulate the pointer and counter words. PUL and POL move 2 words onto or off of the push-down list.

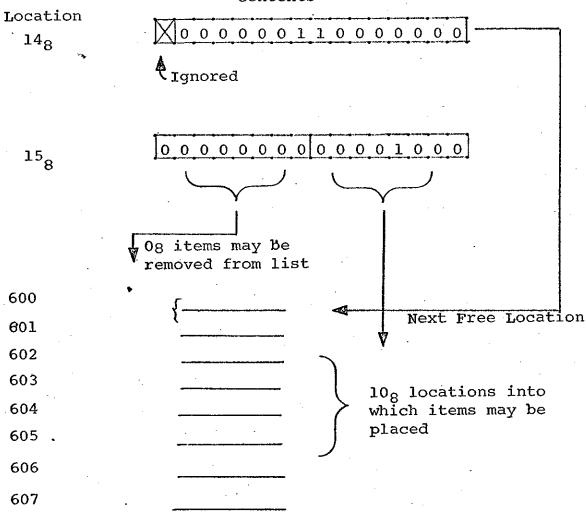

The Push-Down List (PDL) pointer (location 14<sub>8</sub>) always points to the next free call on the push-down list. The right-hand byte of the push-down list counter (bits 8-15 of location 15<sub>8</sub>) contains a count of the number of pushes that may be executed before the list overflows. The left-hand byte of the push-down list counter (bits 0-7 of location 15<sub>8</sub>) contains a count of the number of pops that may be executed before the list underflows.

The PDL pointer is initialized to point to the first cell of the push-down list, the right half of the PDL counter is initialized to contain the length of the list ( $\leq 255_{10}$ ) and the left half is initialized to contain zero.

For example, if the PDL were to start at location  $600_8$  and is  $10_8$  locations long, the initialization sequence could be:

LDA 4, [600]

STA 4, 14 ; STORE POINTER

LDA 4, [10]

STA 4, 15 ; STORE COUNTER

The push-down list counter and pointer would then be: Contents

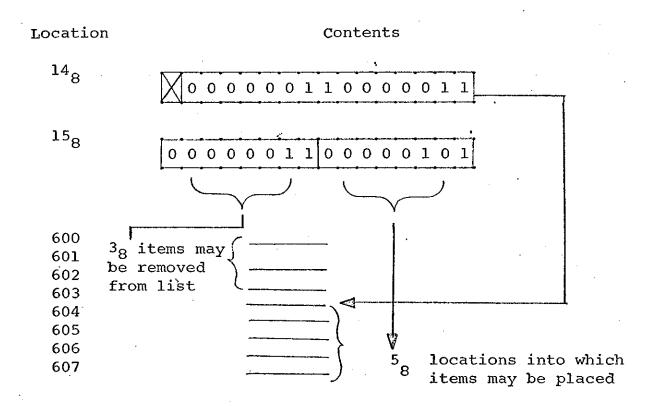

After the execution of instructions that placed three items on the PDL, the situation would be:

| D <sub>1</sub> | mnem | R | Definition                                                                                                                                     |

|----------------|------|---|------------------------------------------------------------------------------------------------------------------------------------------------|

| 116            | PUC  | 0 | PUsh Count. The pointer and counter are modified as for a push type instruction but no data is put onto the list.                              |

|                | PUSH | 1 | PUSH. The effective word is placed in the next location on the push-down list.                                                                 |

|                | PUB  | 2 | PUsh and Branch. The program counter is placed in the next location on the push-down list. The effective address replaces the program counter. |

|                | PUL  | 3 | <u>PUsh</u> , Branch and <u>Link</u> . The subroutine linkage register is placed in the next location on the push-down list.                   |

| mnem | R ` | Definition                                                                                                                                                                                                                                                                 |

|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |     | The program counter is placed in the subroutine linkage register. The program counter is placed in the next location on the push-down list. The effective address replaces the program counter.                                                                            |

| POC  | 4   | POp Count. The pointer and counter are modified as for a POP type instruction but no data is removed from the list.                                                                                                                                                        |

| POP  | 5   | POP. The last word placed on the push-down list is moved to the content of the effective address.                                                                                                                                                                          |

| POB  | 6   | POp and Branch. The sum of the effective word and the last word placed on the pushdown list replaces the program counter. This is the return instruction for PUB.                                                                                                          |

| POL  | 7   | POp, branch, and Link. The sum of the effective word and the last word placed on the push-down list replaces the program counter. Then, the new last word on the push-down list is then placed in the subroutine linkage register. This is the return instruction for PUL. |

| •    |     | ·                                                                                                                                                                                                                                                                          |

PUB and PUL may be used as generalized subroutine calls; PUB when no arguments are passed. PUL when arguments are passed. These calling sequences are "nestable" and re-cursive allowing for re-entrance. The corresponding return instructions are POB and POL. Notice the PUL places two words on the push-down list and that POL removes two words from the push-down list. The pointer and counter words are incremented (decremented) two times during the execution of these instructions.

# 2.6.7 IO Instructions

| _     |    |      |                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Class | OP | mnem | Definition                                                                                                                                                                                                                                                                                                                                                                                    |

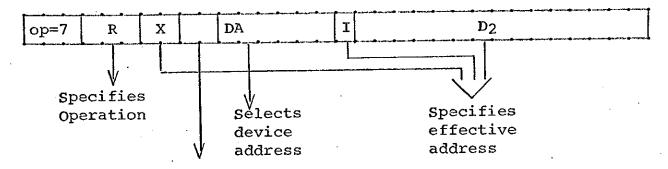

| IO .  | 7  | . ,  | Input/Output instruction class. The R bits of an IO instruction (always long format) specify one of 8 types of operation.                                                                                                                                                                                                                                                                     |

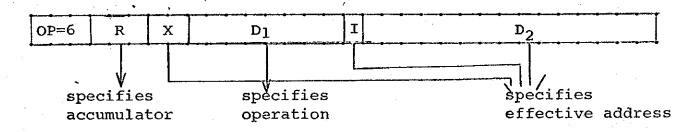

|       |    |      | The D <sub>1</sub> field is interpreted depending upon the type of operation. Normally 6 bits are used to select a particular device connected to the IO bus, two bits (optionally) select one of four busses (see diagram below). In an IOD class instruction, D <sub>1</sub> is used to augment the operation code and R fields of the instruction to specify a specific internal function. |

# IO Class Instruction Double-word

Bus Selection

#### Class OP mnem Definition

If no device responds to the IO instruction, bit 6 of the Program Status double-Word is set indicating an IO error. If the Error Trap Enable bit (1) is on, a trap will occur. (See section 2.5.) This error may be caused by a programming error, a hardware malfunction, or the addressed device may be disconnected.

The only TO class instruction which may set condition codes is TOT:

condition code bit 0 remain unchanged

1 set if bit 0 of

the word resulting

from the operation

is a 1; cleared

otherwise

2 set if the word

resulting from

from the operation

is nonzero; cleared

otherwise

The IO instructions may not be executed by a program operating in User mode on a system with the (optional) protection system installed. An attempt to do so will result in bit 7 of the PSW being set and a trap to the monitor will result. (See section 2.5, 2.8)

#### R Operation

IOR

O <u>IO</u> Read word. The data buffer of the addressed input device (DA) replaces the right-hand byte of the effective word. The left-hand byte is cleared. If this instruction is used to address a device that can only do output, a zero byte is read.

Class OP mnem Definition

#### R Operation

If the addressed input device responds with more than one byte of data, they are placed in memory starting with the byte located in the right half of the effective word. If an odd number of bytes are transferred, the last lefthand byte is left zero.

IORC

1

IO Read Character. The effective word of the IORC instruction is used as a byte pointer that locates a single byte; the data buffer of the addressed input device (DA) replaces the byte so located. other byte in the 16-bit word is unchanged. If this instruction is used to address a device that can only do output, a zero byte is read. If the addressed input device responds with more than one byte of data, they are placed in memory starting at the located byte. byte pointer referenced by this instruction (i.e., the effective word) has the format as indicated in section 2.6.4 and is left unchanged.

WOI

2 <u>IO</u> Write Word. The data buffer of the addressed output device (DA) is replaced by the byte located in the right half of the effective word. If this instruction is used to address a device that can only do input, it has no effect. If the addressed output device requests more than one byte of data, they are taken from memory starting with the byte located in the right half of the effective word.

Class OP mnem Definition

#### R ,Operation

- The effective 3 IO Write Character. IOWC word of the IOWC instruction is used as a byte pointer that locates a single byte; the byte so located replaces the data buffer of the selected output device (DA). this instruction is used to address a device that can only do input, it has no effect. If the addressed output device requests more than one byte of data, they are taken from memory starting with the located byte. The byte pointer referenced by this instruction (i.e., the effective word) has the format as indicated in

- IOS 4 To read Status. The status register of the addressed device (DA) replaces the right-hand byte of the effective word. The left-hand byte is cleared. If the addressed device responds with two bytes of status, the second byte is placed in the left half of the effective word.

section 2.6.4 and is left unchanged.

- IOC 5 TO Command. The status register of the addressed device (DA) is replaced by the right-hand byte of the effective word. If the device requests a second byte of status, it is taken from the left-hand byte of the effective word.

- IOT 6 <u>IO</u> Test status. The status register of the addressed device (DA) is

#### Class OP mnem Definition

#### R Operation

read into the central processor.

If the addressed device responds with a second byte, it is placed into the left half; otherwise, the left half is cleared. This resultant 16-bit word is logically ANDed with the effective word. The resulting condition code bits (1,2) may be tested by a conditional branch instruction to determine the state of a selected status register bit. The effective word and addressed status register remain unchanged.

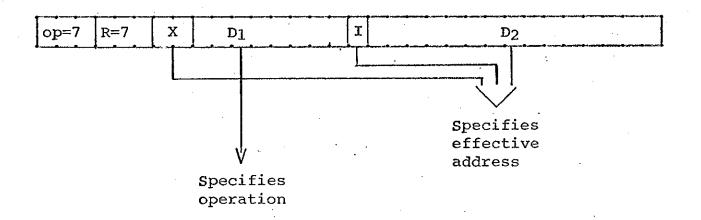

10D 7 internal 10 Device control. The D1 field of this class of IO instruction is used to select one of several functions. Instructions with undefined values of D1 are treated as no-operations. The IOD instructions are used to change the state of the IO system and the memory protection system. (See section 2.8.4)

#### IOD Class Instruction Double-word

IOD Class (OP = 7, R = 7)

mnèm Definition  $\mathtt{p}_1$ Ó RIO Reset IO system; all devices are cleared; no interrupt may occur from any device unless that device is specifically re-initialized. The priority' level internal request indicators, external request indicators, inhibit indicators and active indicators are cleared. If the system has the protection feature, active indicator 1 is set and RG is set to 1, otherwise RG is cleared. The instruction should only be executed at the level which will result, i.e., level 0 for machine without protection, level 1 for machine with protection. This instruction is accomplished by transmitting the reset. code on the IO bus. All devices, both DEC and customer-designed must use this code to reset to a known, non-operating state, i.e., clear ALL flip-flops in the devices and in the controllers.

1 HLT

HaLT; the central processor is halted at the completion of this instruction. The effective word is displayed in the console indicators. The program

|   |     | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • |     | counter is updated to point to the next sequential instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2 | RĆS | Read Console Switches; the contents of the console switches replace the effective word.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3 | WCI | Write Console Indicators; the effective word replaces the contents of the console indicators.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |     | (See section 2.7 for a description of the priority system.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4 | PSI | Priority System Inhibit; the priority of the currently running process is raised by setting an inhibit indicator to the value specified by the effective word (i.e., the content of the effective address). The low order four bits of the effective word is compared with the highest priority level active indicator. If its value is higher than the indicator, then the priority level inhibit indicator corresponding to this value is turned on. If it is less than or equal to the active indicator, no operation results. In either case, the RG bits are not changed. |

Definition

mnem

$\mathbf{p}_1$

#### D<sub>1</sub> mnem Definition

This instruction is normally used together with its return, PSC, in calling a subroutine which is not re-entrant. Such cases occur in changing queue parameters of certain interrupt service routines.

A typical call is of the form:

PSI [N] ; raise priority to N

BAL SUBR ; call subroutine

ARG ; argument(s)

PSC ; restore priority

; N is chosen to be sufficiently high such that no routine entered at a priority level greater than N calls SUBR.

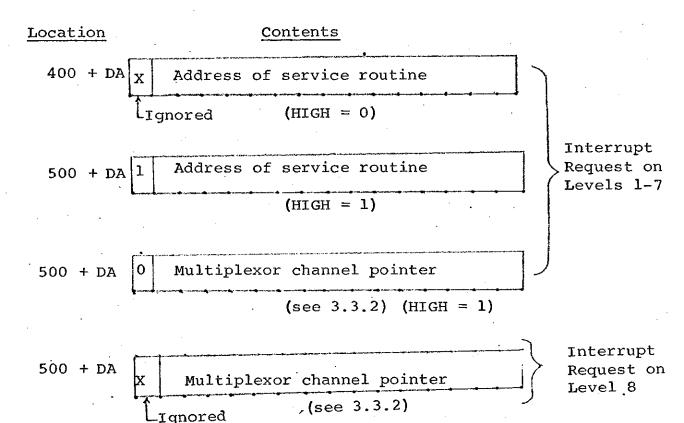

5 PSR

Priority System Request; the priority level request indicator corresponding to the value of the low order three bits of the effective word is set. An interrupt at that level is requested; this request is handled as if it were an external IO device. When the interrupt is granted, the interrupt address is determined according to the following table:

| D <sub>3</sub> | mnem | Definition |

|----------------|------|------------|

|                |      |            |

| Priority Level | Interrupt Address      |

|----------------|------------------------|

| 0              | No interrupt requested |

| 1.             | 401                    |

| 2              | 402                    |

| •              | •<br>•                 |

| *              | •                      |

| •              | •                      |

| 7              | 407                    |

6 PSC

Priority System Clear; the priority level of the currently running process is returned (by clearing an inhibit indicator) to the priority preceding the last PSS instruction issued.

The priority level inhibit indicators are compared with the priority level active indicators. If the highest inhibit level is greater than the highest active level, then that inhibit indicator is turned off.

Note that RG is not changed.

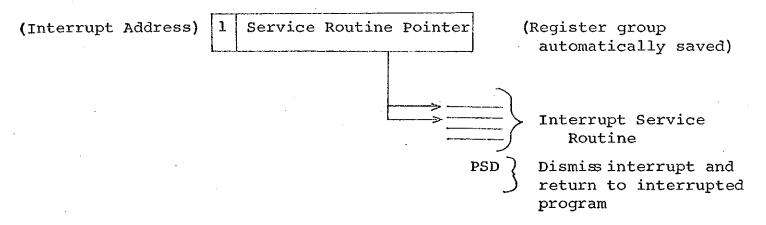

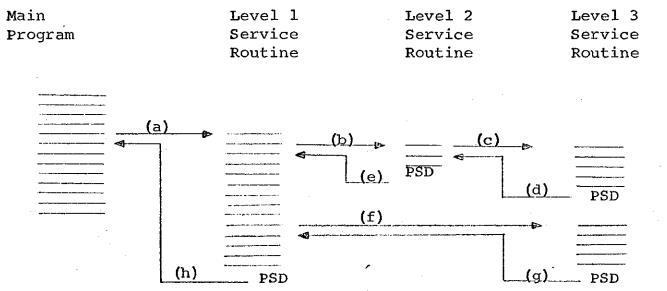

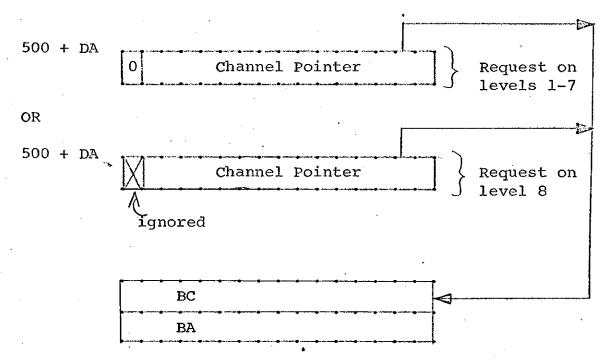

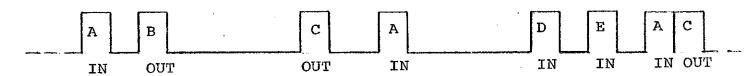

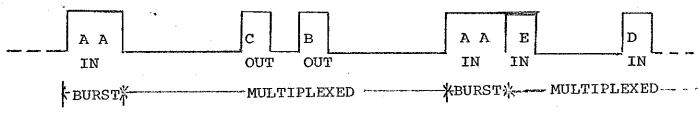

7 PSD