# PDP-8/S MAINTENANCE MANUAL

1st Edition October 1967 2nd Edition March 1968 3rd Edition June 1968 4th Edition August 1969 5th Edition October 1970

Copyright © 1967, 1968, 1969, 1970 by Digital Equipment Corporation

The material in this manual is for information purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP DIGITAL FOCAL COMPUTER LAB

#### CONTENTS

|         |                                          | Page |

|---------|------------------------------------------|------|

| Preface |                                          | ix   |

|         | CHAPTER 1<br>INTRODUCTION                |      |

| 1.1     | Physical Characteristics                 | 1-2  |

| 1.2     | Electrical Characteristics               | 1-2  |

|         | CHAPTER 2<br>SYSTEM OPERATION            |      |

| 2.1     | Programming                              | 2-2  |

| 2.1.1   | Number System                            | 2-4  |

| 2.1.2   | Instruction Format                       | 2-5  |

| 2.1.3   | Addressing                               | 2-6  |

| 2.1.4   | Autoindexing                             | 2-6  |

| 2.1.5   | Operating Speed                          | 2-6  |

| 2.2     | Word Times                               | 2-7  |

| 2.3     | Processor Operation                      | 2-8  |

| 2.3.1   | Indicators, Operating Keys, and Switches | 2-9  |

| 2.4     | Teletype Operation                       | 2-11 |

| 2.4.1   | Таре                                     | 2-16 |

| 2.4.2   | Paper                                    | 2-16 |

| 2.4.3   | Ribbon                                   | 2-17 |

| 2.4.4   | Tabs                                     | 2-17 |

|         | CHAPTER 3<br>SYSTEM LOGIC                |      |

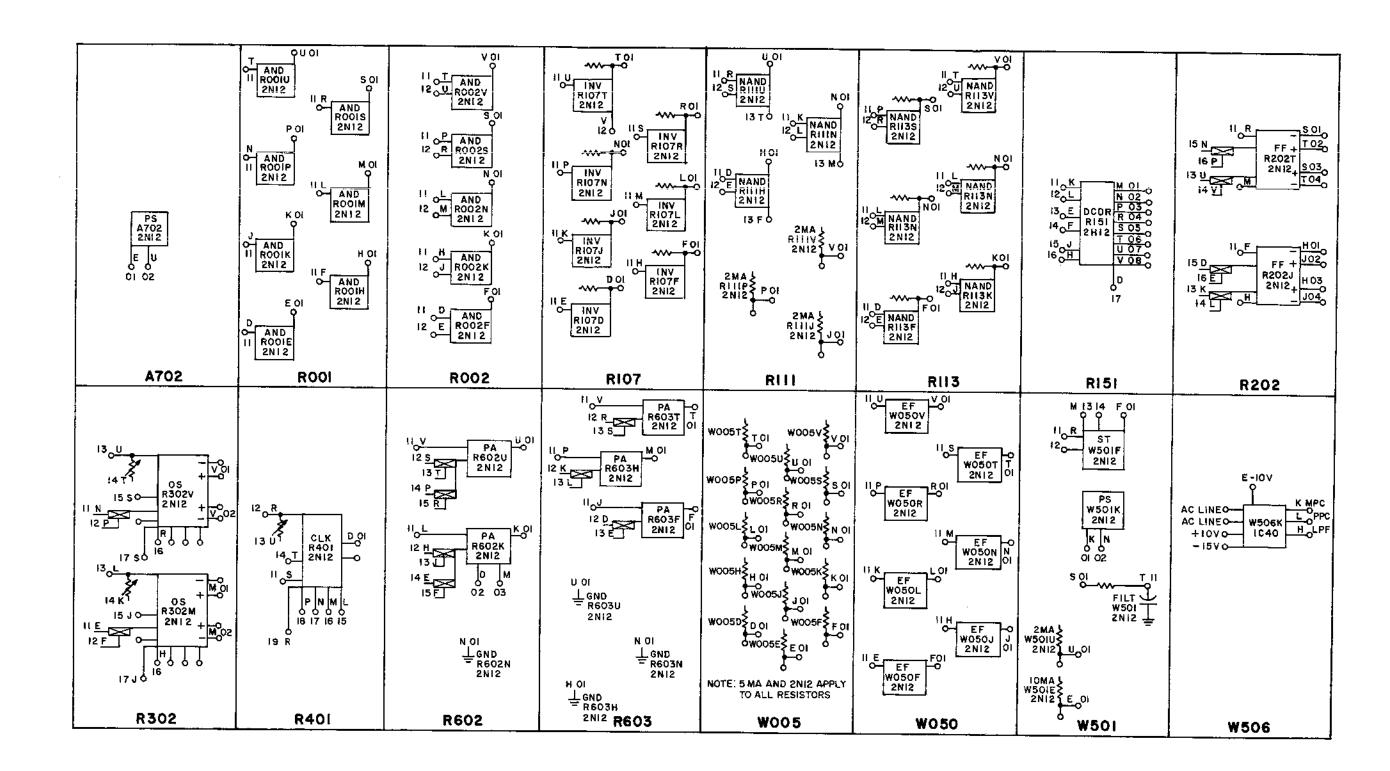

| 3.1     | Drawings                                 | 3–1  |

| 3.1.1   | Logic Drawings                           | 3-2  |

| 3.1.2   | Flow Charts                              | 3-7  |

| 3.2     | Timing                                   | 3-8  |

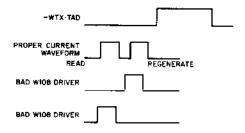

| 3.2.1   | Bit Timing                               | 3-9  |

| 3.2.2   | Word Timing                              | 3-10 |

| 3.3     | Registers                                | 3-11 |

| 3.3.1   | Instruction Register                     | 3-11 |

| 3.3.2   | Memory Buffer                            | 3-12 |

#### CONTENTS (continued)

|       |                                                      | Page |

|-------|------------------------------------------------------|------|

| 3.3.3 | Program Counter                                      | 3-12 |

| 3.3.4 | Memory Address                                       | 3-13 |

| 3.3.5 | Accumulator and Link                                 | 3-13 |

| 3.4   | Control Circuits                                     | 3-14 |

| 3.4.1 | Adder                                                | 3-14 |

| 3.4.2 | Parity Logic                                         | 3-15 |

| 3.4.3 | Skip Logic                                           | 3-15 |

| 3.4.4 | Console                                              | 3-16 |

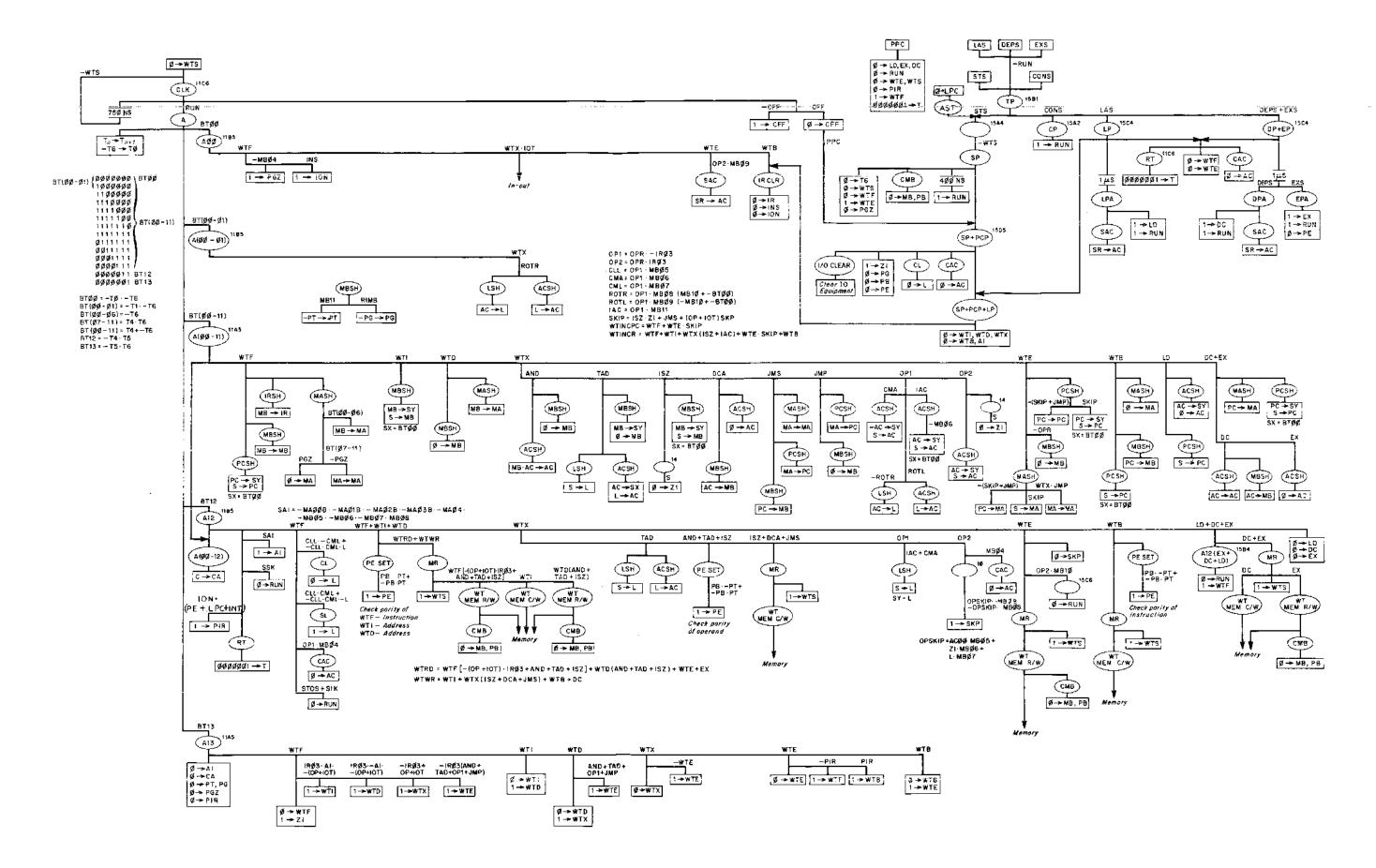

| 3.5   | Main Flow                                            | 3-16 |

| 3.5.1 | Console Operations                                   | 3-17 |

| 3.5.2 | Instruction Flow                                     | 3-17 |

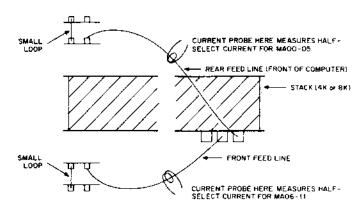

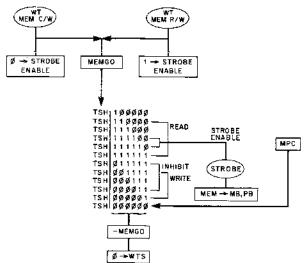

| 3.6   | Memory                                               | 3-20 |

| 3,6,1 | Memory Control                                       | 3-20 |

| 3.6.2 | Core Logic                                           | 3-20 |

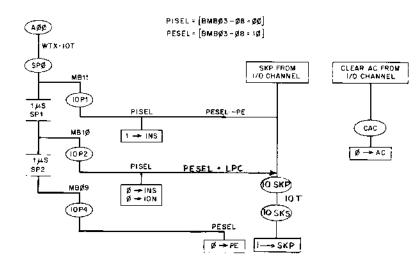

| 3.7   | In-Out                                               | 3-22 |

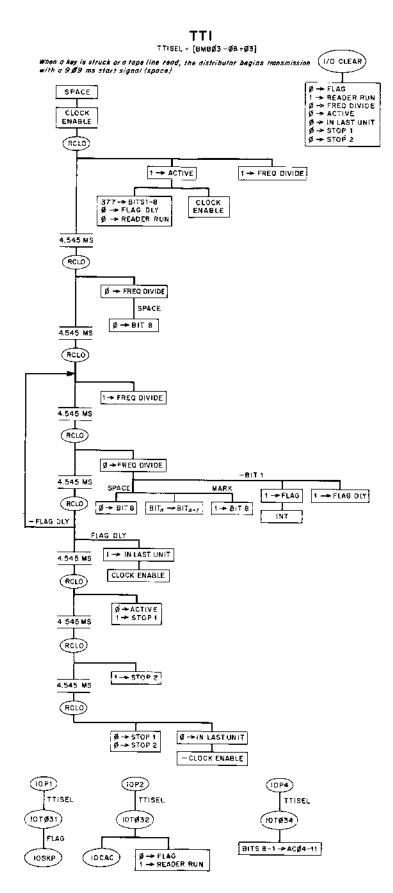

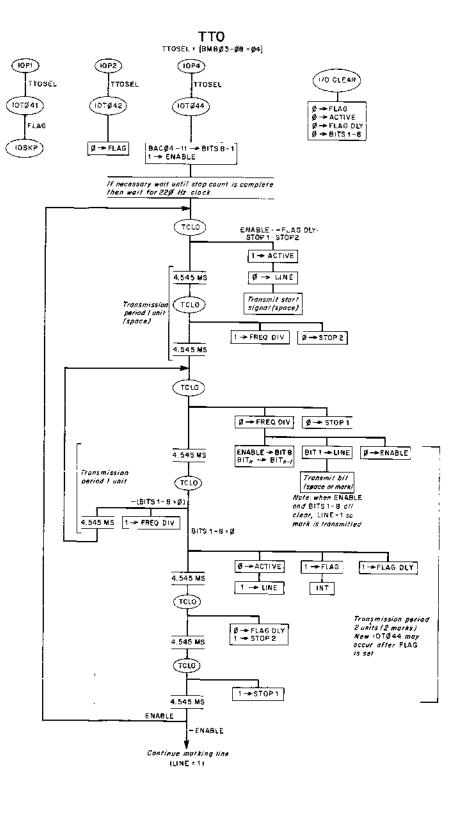

| 3.8   | Teletype                                             | 3-23 |

| 3.8.1 | Input                                                | 3-24 |

| 3.8.2 | Output                                               | 3-25 |

|       | CHAPTER 4 MAINTENANCE                                |      |

| 4.1   | Maintenance Programs                                 | 4-1  |

| 4.2   | Memory Alignment                                     | 4-2  |

| 4.3   | Memory Troubleshooting                               | 4-3  |

| 4.3.1 | X-Y Selection                                        | 4-3  |

| 4.3.2 | Inhibit Drivers                                      | 4-4  |

| 4.3.3 | Sense Amplifiers and Slicers                         | 4-5  |

| 4.4   | In-Out Bus Specifications                            | 4-6  |

|       | CHAPTER 5<br>MEMORY EXPANSION AND DATA BREAK OPTIONS |      |

| 5.1   | Introduction                                         | 5-1  |

| 5.1.1 | Physical Characteristics                             | 5-2  |

#### CONTENTS (cont)

| 5.1.2          | Electrical Characteristics                       | 5–3  |

|----------------|--------------------------------------------------|------|

| 5.2            | System Operation                                 | 5-3  |

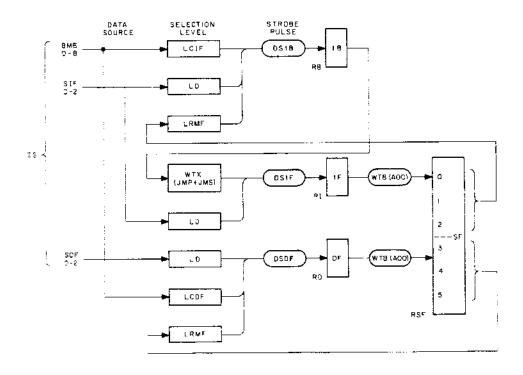

| 5.2.1          | Data Flow                                        | 5–3  |

| 5.2.2          | OMD8S Option                                     | 5-3  |

| 5.2.3          | MC8S Option                                      | 5-4  |

| 5.2.4          | DB8S Option                                      | 5-4  |

| 5.2.5          | ME8S Option                                      | 5-8  |

| 5.3            | Operation and Programming                        | 5-9  |

| 5.3.1          | Memory Field Selection                           | 5-9  |

| 5.3.2          | Initializing 3–Cycle Data Breaks                 | 5-9  |

| 5.3.3          | Indicators, Operating Keys, and Switches         | 5-9  |

| 5.4            | System Logic                                     | 5–10 |

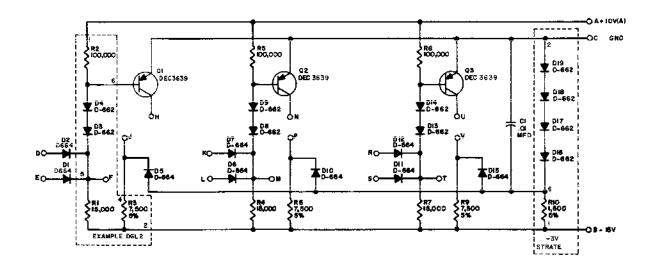

| 5.5            | OMD8\$ Logic                                     | 5-11 |

| 5.5.1          | Logic Elements                                   | 5-11 |

| 5.5.2          | OMD8S Sequential Operation                       | 5-13 |

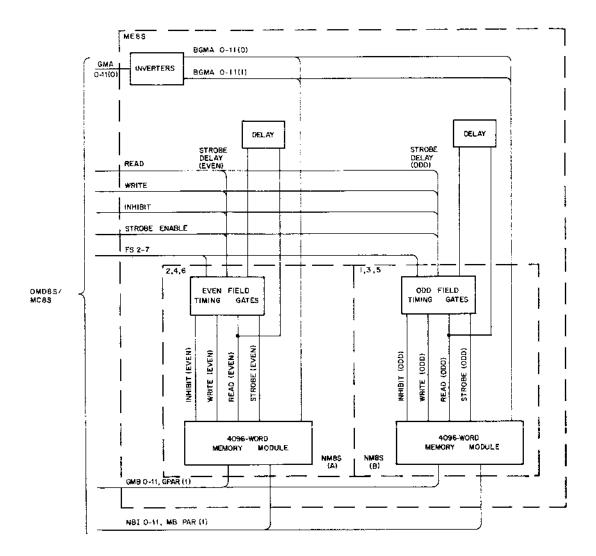

| 5.6            | MC8S Logic                                       | 5-14 |

| 5.6.1          | Logic Elements                                   | 5-14 |

| 5.6.2          | MC8S Sequential Operation                        | 5-16 |

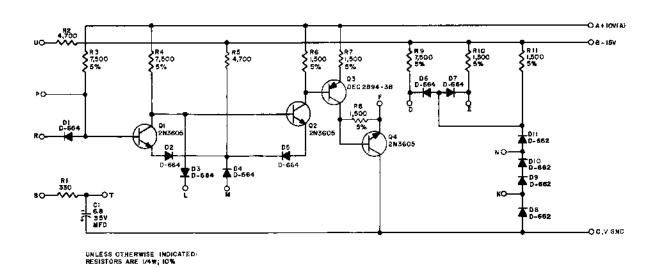

| 5.7            | DB8S Logic                                       | 5-20 |

| 5.7.1          | Logic Elements                                   | 5-20 |

| 5.7.2          | Standby Condition                                | 5-22 |

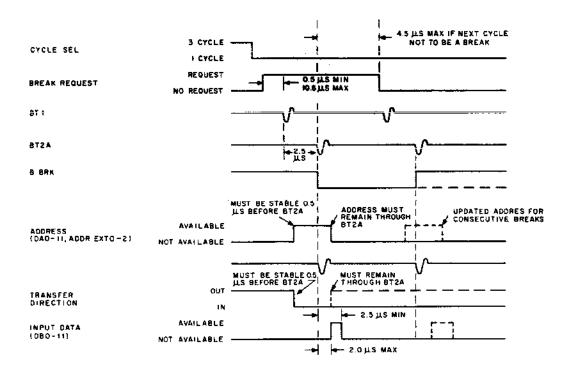

| 5 <b>.7.</b> 3 | Sequential Operation, 1-Cycle Breaks             | 5-22 |

| 5.7.4          | Sequential Operation, 3-Cycle Breaks             | 5-24 |

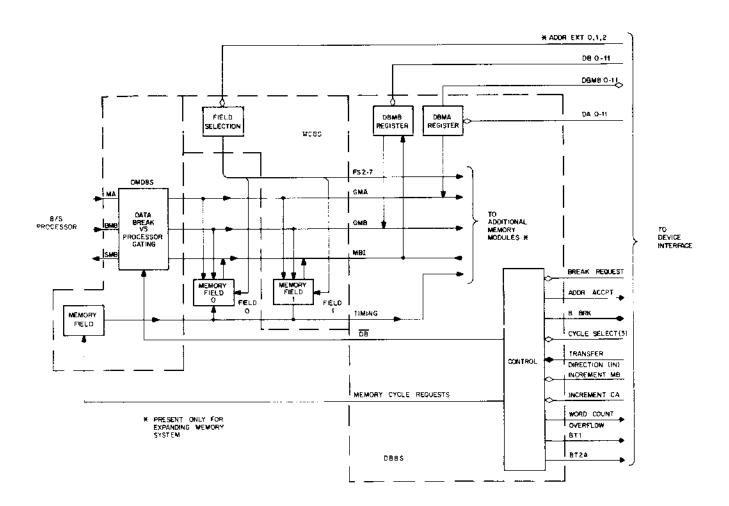

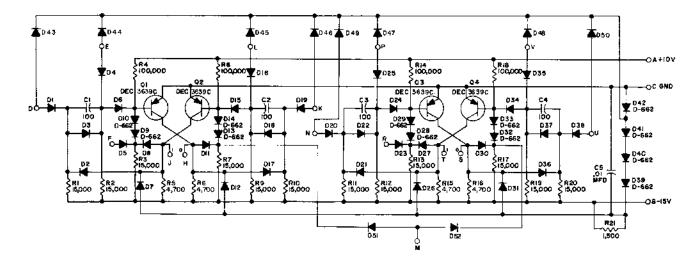

| 5,8            | Memory Extension Beyond 8K Words (ME85 and MM85) | 5-27 |

| 5.8.1          | ME8S Logic                                       | 5-27 |

| 5.8.2          | MM8S Logic                                       | 5-27 |

| 5.9            | Maintenance                                      | 5-28 |

| 5.9.1          | Spare Parts and Test Equipment                   | 5-28 |

| 5.9.2          | Maintenance Programs                             | 5-29 |

| 5.9.3          | Memory Alignment and Troubleshooting             | 5-29 |

| 5.9.4          | Interfacing External Equipment of DB8S Facility  | 5-29 |

|                |                                                  |      |

APPENDIX A ENGINEERING DRAWINGS

#### APPENDIX B GLOSSARY

# APPENDIX C ENGINEERING DRAWINGS AND GLOSSARY FOR OMD8S, MC8S, D88S, ME8S, AND MM8S OPTIONS

#### ILLUSTRATIONS

| Figure       |                                                                                 | Page         |

|--------------|---------------------------------------------------------------------------------|--------------|

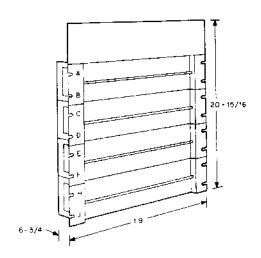

| 1-1          | Dimensions, Table Model (Front View)                                            | 1-4          |

| 1-2          | Dimensions, Table Model (Side View)                                             | ì -4         |

| 1-3          | Dimensions, PDP-8/S Mounted in Standard DEC Rack                                | 1-5          |

| 1-4          | Dimensions, PDP-8/S Mounted in Standard DEC Rack                                | 1-5          |

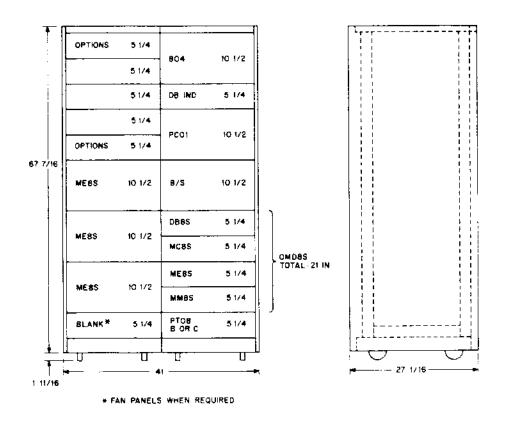

| 1-5          | Typical Rack Mounted PDP-8/S with Recommended Option Mounting                   | 1-6          |

| 2-1          | PDP-8/S Data Flow                                                               | 2-1          |

| 2-2          | Teletype Model ASR-33                                                           | 2-11         |

| 3-1          | Logic Symbols                                                                   | 3-3          |

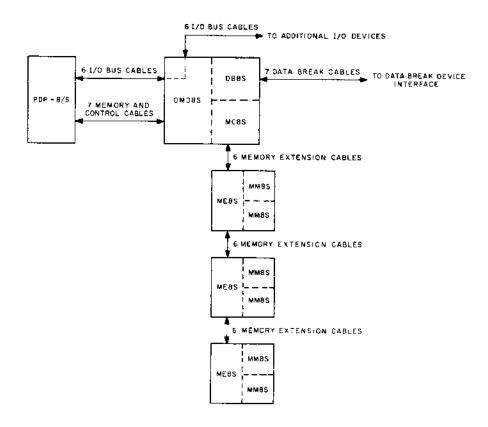

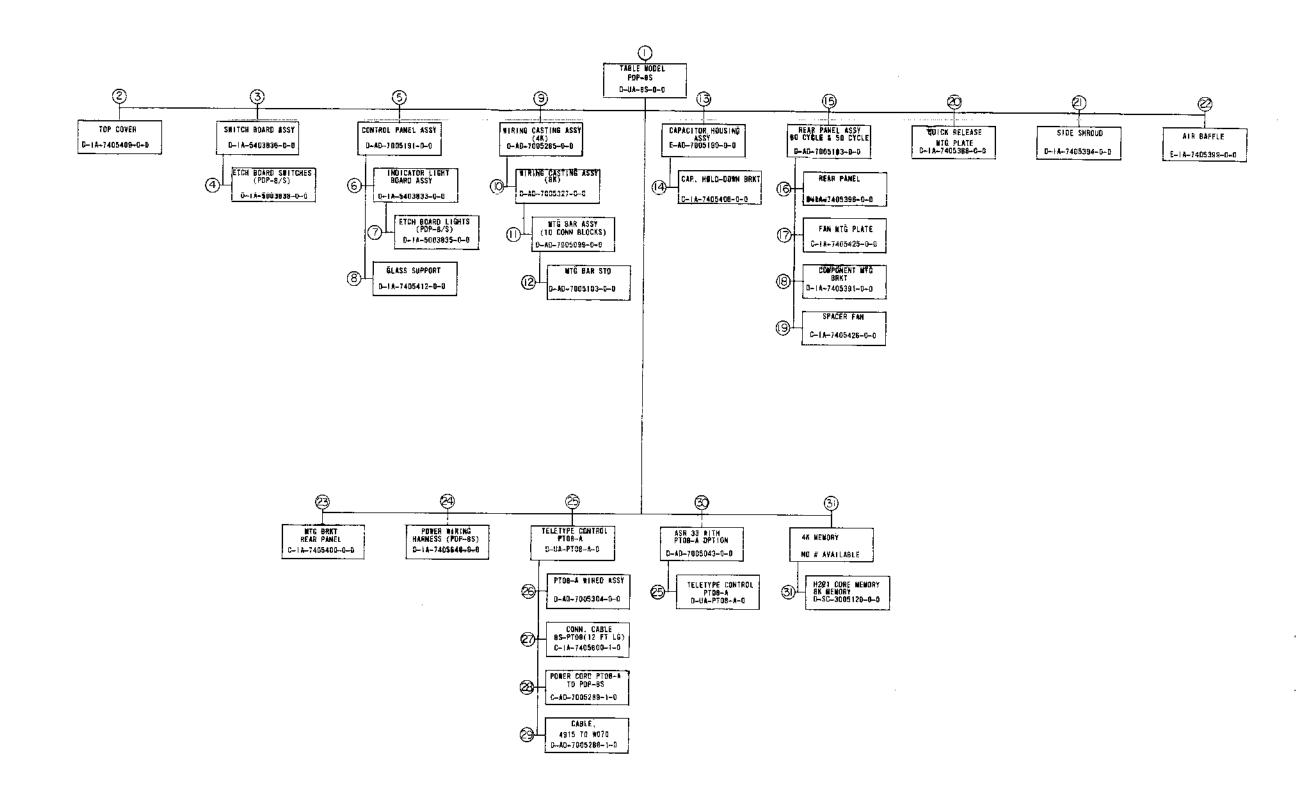

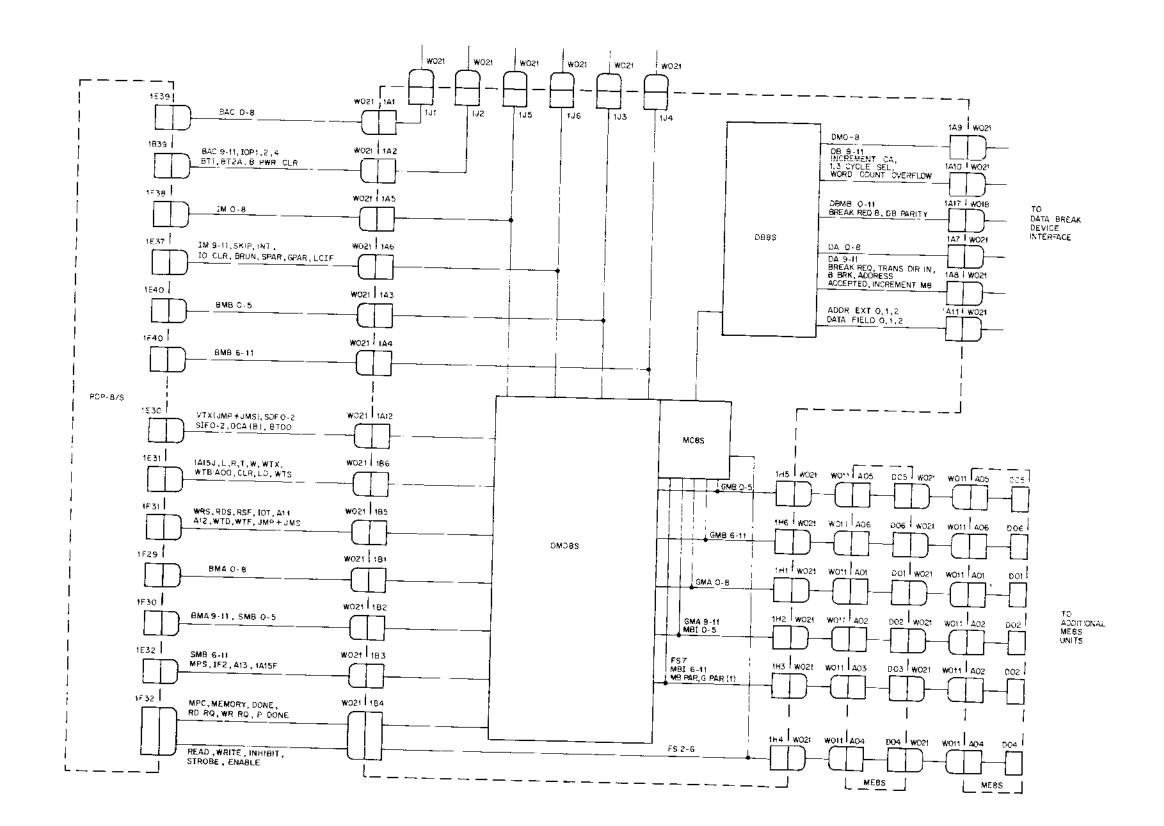

| 5-1          | Assembly and Cabling Configurations for Memory Expansion and Data Break Options | 5-2          |

| 5-2          | OMD8S Assembly Mounting Dimensions                                              | 5-3          |

| 5-3          | ME8S Assembly Mounting Dimensions                                               | 5-4          |

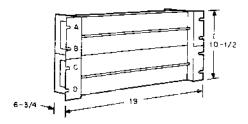

| 5-4          | OMD8S/MC8S/DB8S/ME8S Data Flow                                                  | 5-5          |

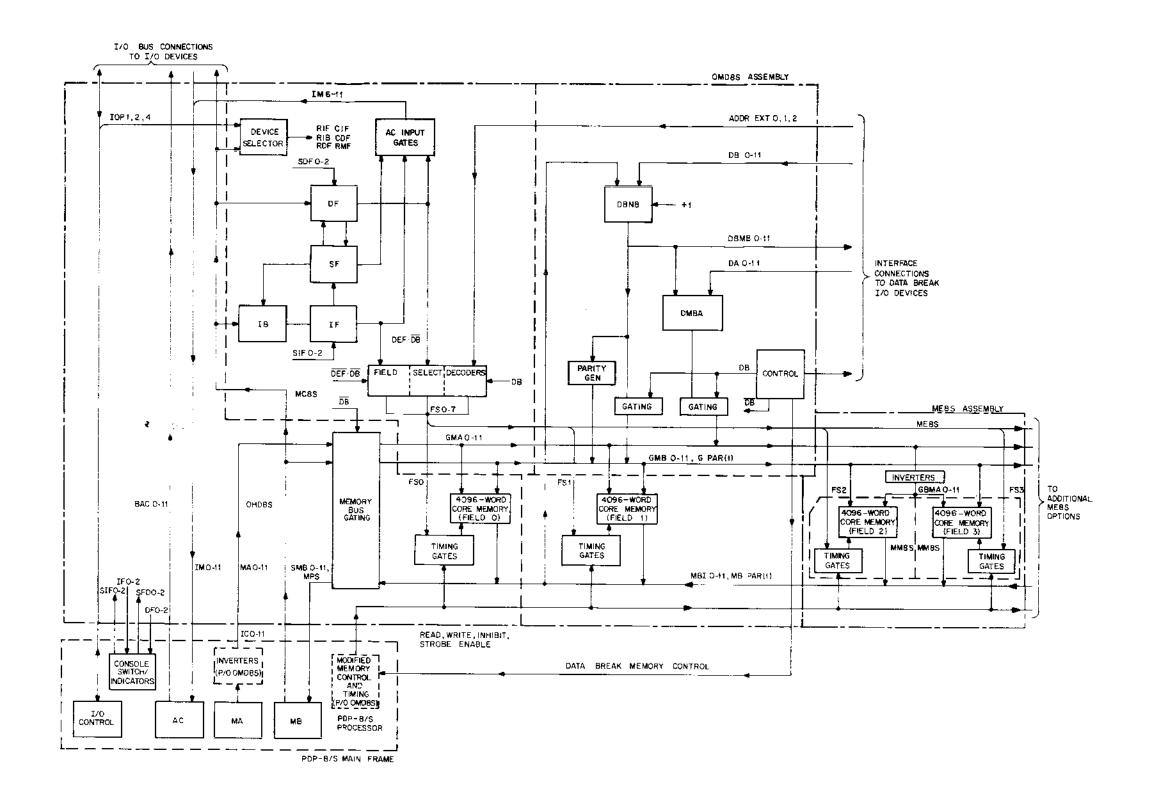

| 5-5          | OMD8S Memory Timing Diagram                                                     | 5-13         |

| 5-6          | MC8S Field Register Data Flow                                                   | 5-15         |

| 5 <b>-</b> 7 | ME8S/MM8S Memory Control and Data Distribution                                  | 5-28         |

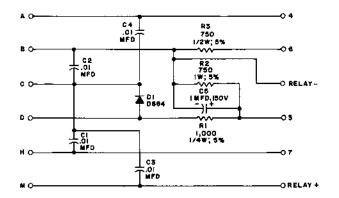

| 5-8          | DB8S Interface Connections                                                      | .5-30        |

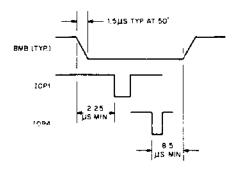

| 5-9          | Interface Timing, Single Cycle Breaks, Input                                    | 5-32         |

| 5-10         | Device Interface Logic for Single-Cycle Input Transfer                          | 5-33         |

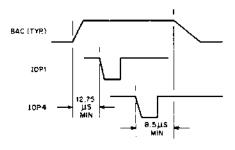

| 5-11         | Interface Timing, Single-Cycle Breaks, Output                                   | 5-34         |

| 5-12         | Device Interface Logic for Single-Cycle Output Transfer                         | <b>5</b> −35 |

| 5-13         | Device Interface for Strobing Output Data                                       | 5-36         |

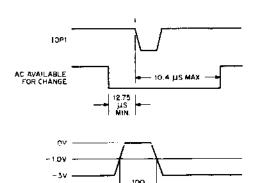

| 5-14         | Interface Timing, Memory Increment Data Breaks                                  | 5-38         |

| 5-15         | Device Interface Logic for Memory Increment Data Break                          | 5-39         |

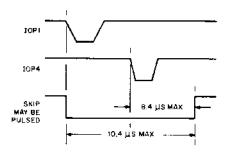

| 5-16         | Interface Timing, 3-Cycle Breaks                                                | 5-40         |

#### TABLES

|                   |                |                                 | Page          |

|-------------------|----------------|---------------------------------|---------------|

| 2-1               | Instru         | ction Index                     | 2-3           |

| 2-2               | PDP-8          | 8/S Instruction Execution Times | 2-7           |

| 2-3               | Telety         | ype Code                        | 2-12          |

| 3-1               | Mnem           | nonic Index                     | 3-6           |

|                   |                |                                 |               |

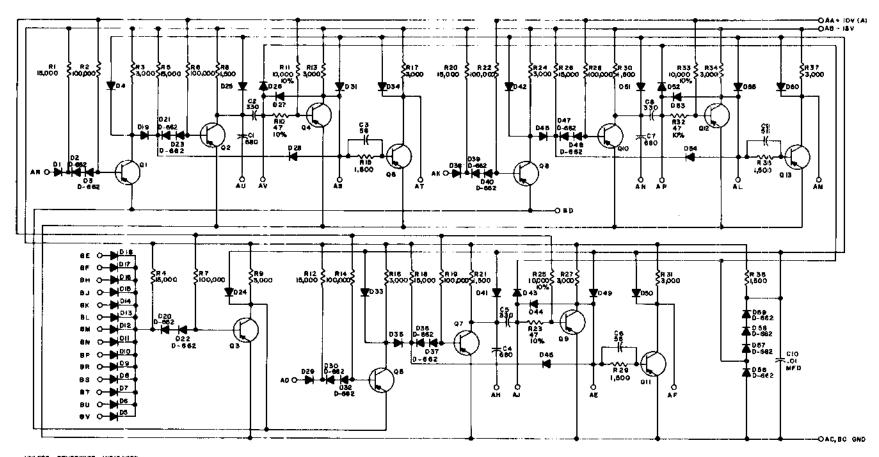

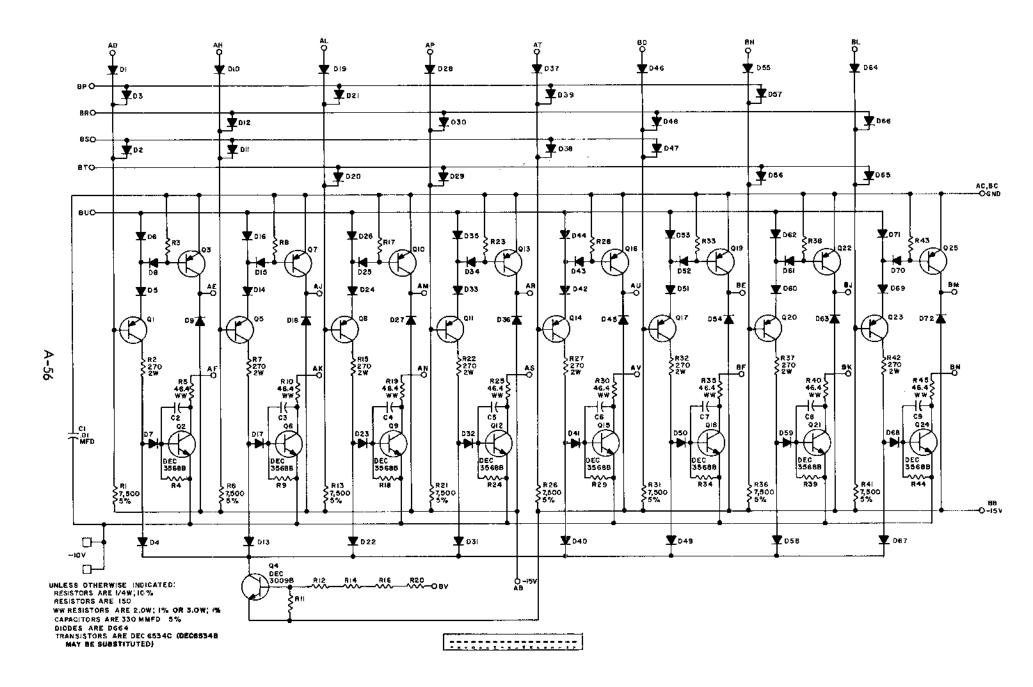

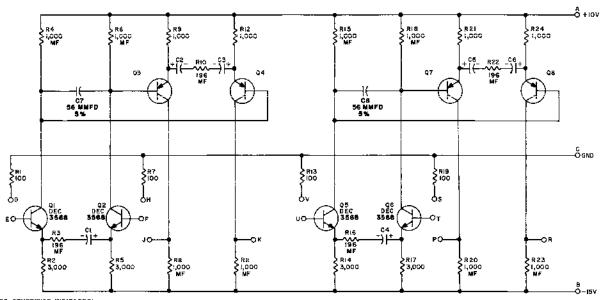

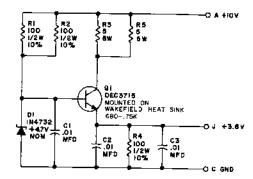

|                   |                | ENGINEERING DRAWINGS            |               |

|                   |                |                                 | Page          |

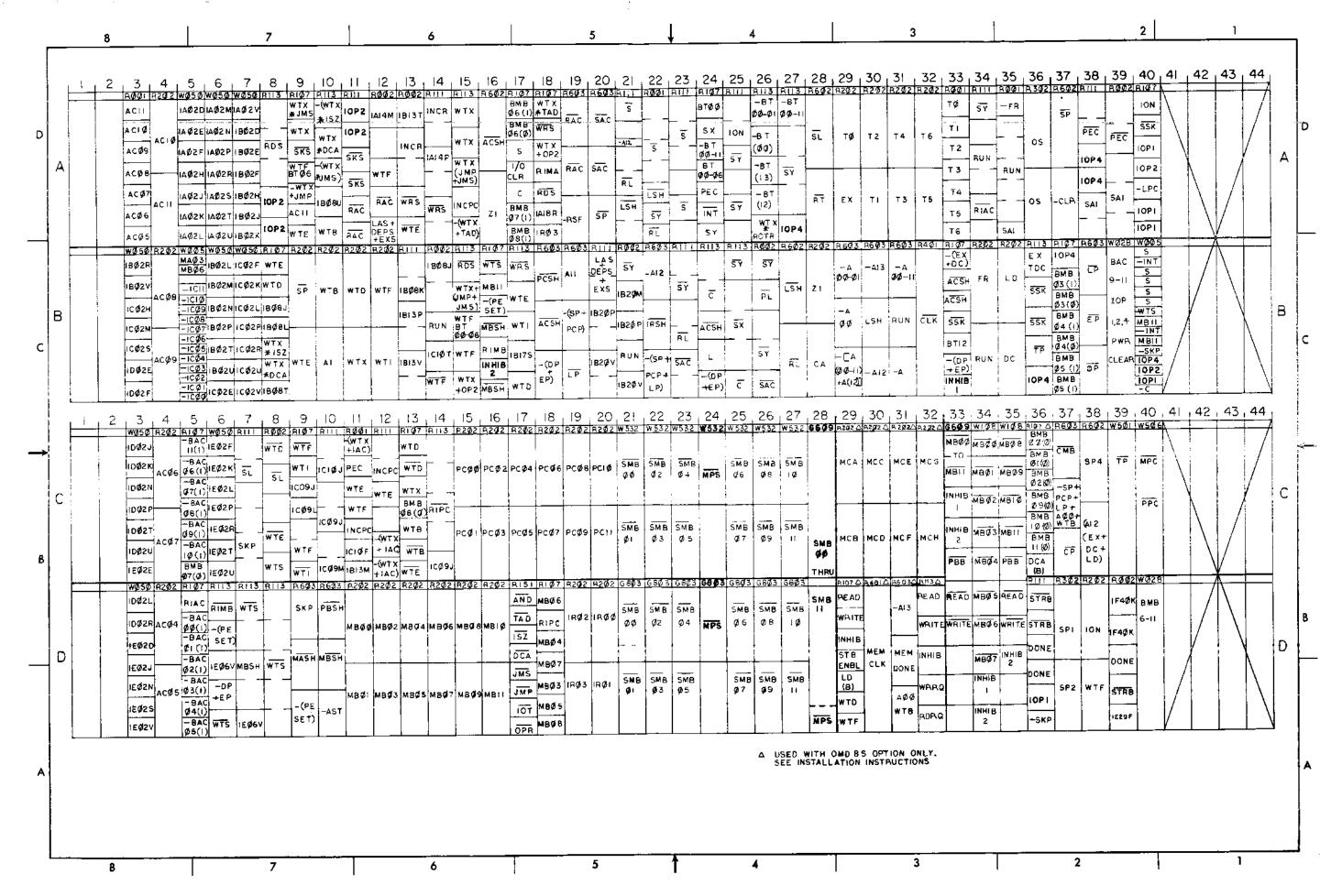

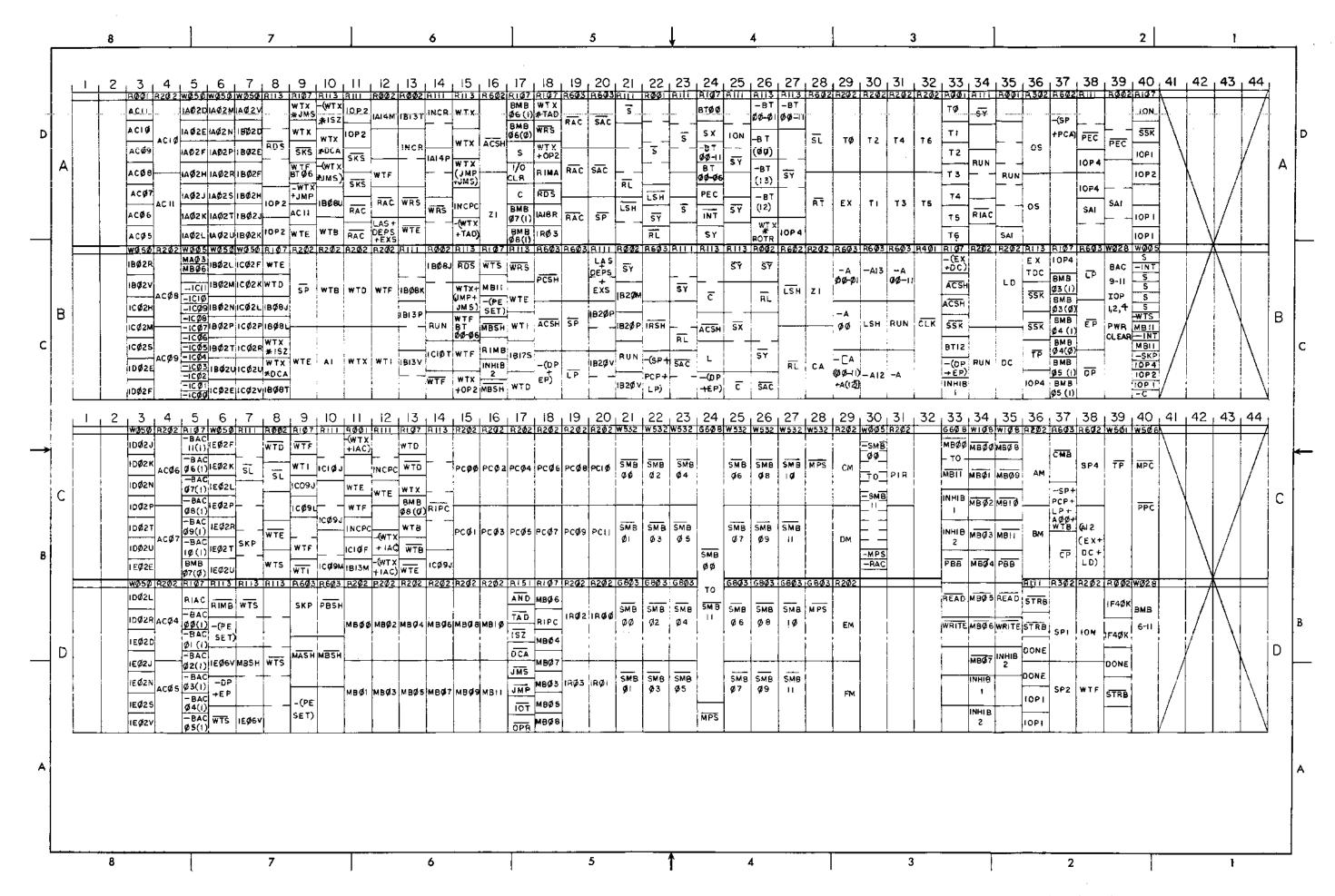

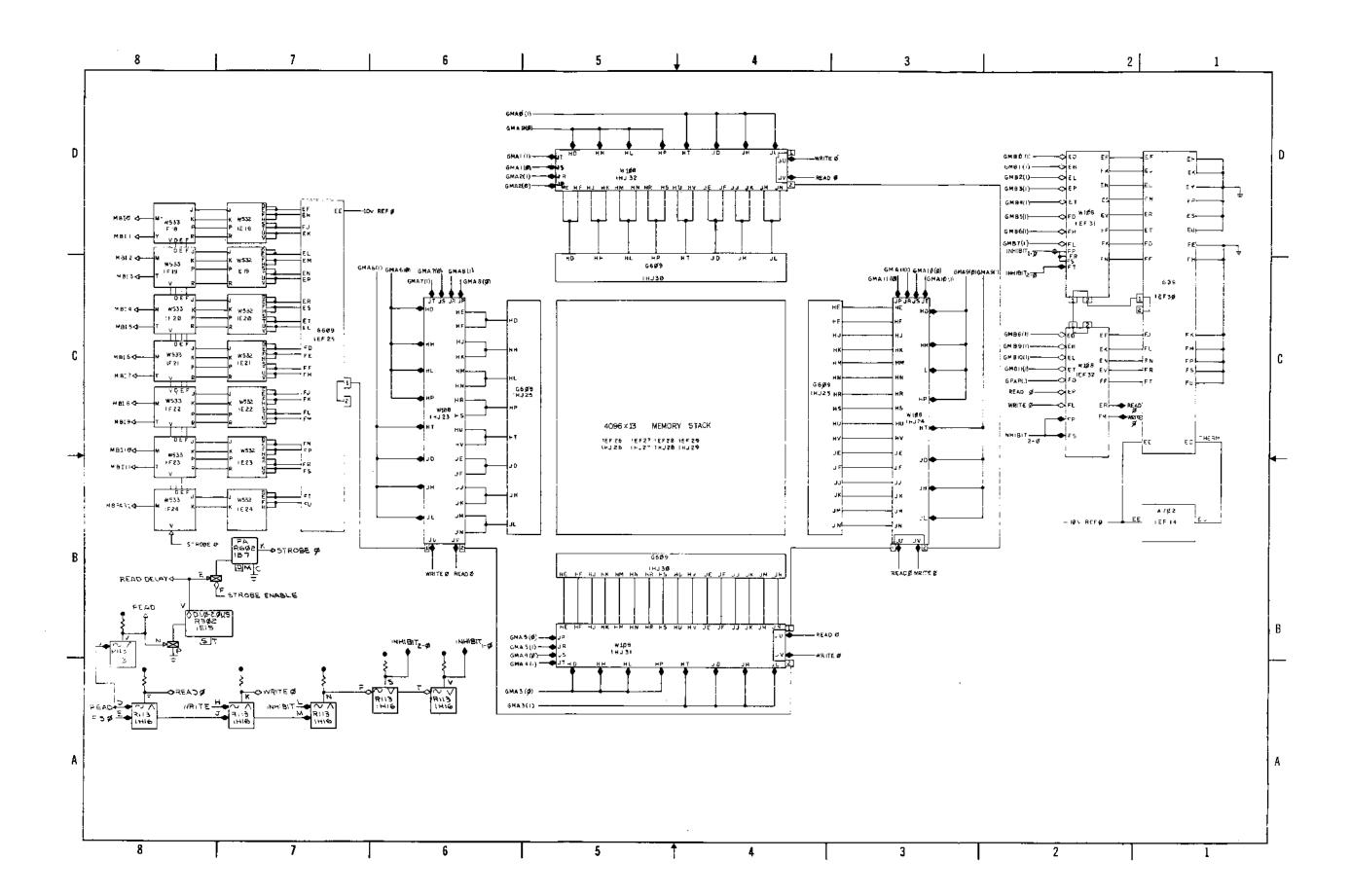

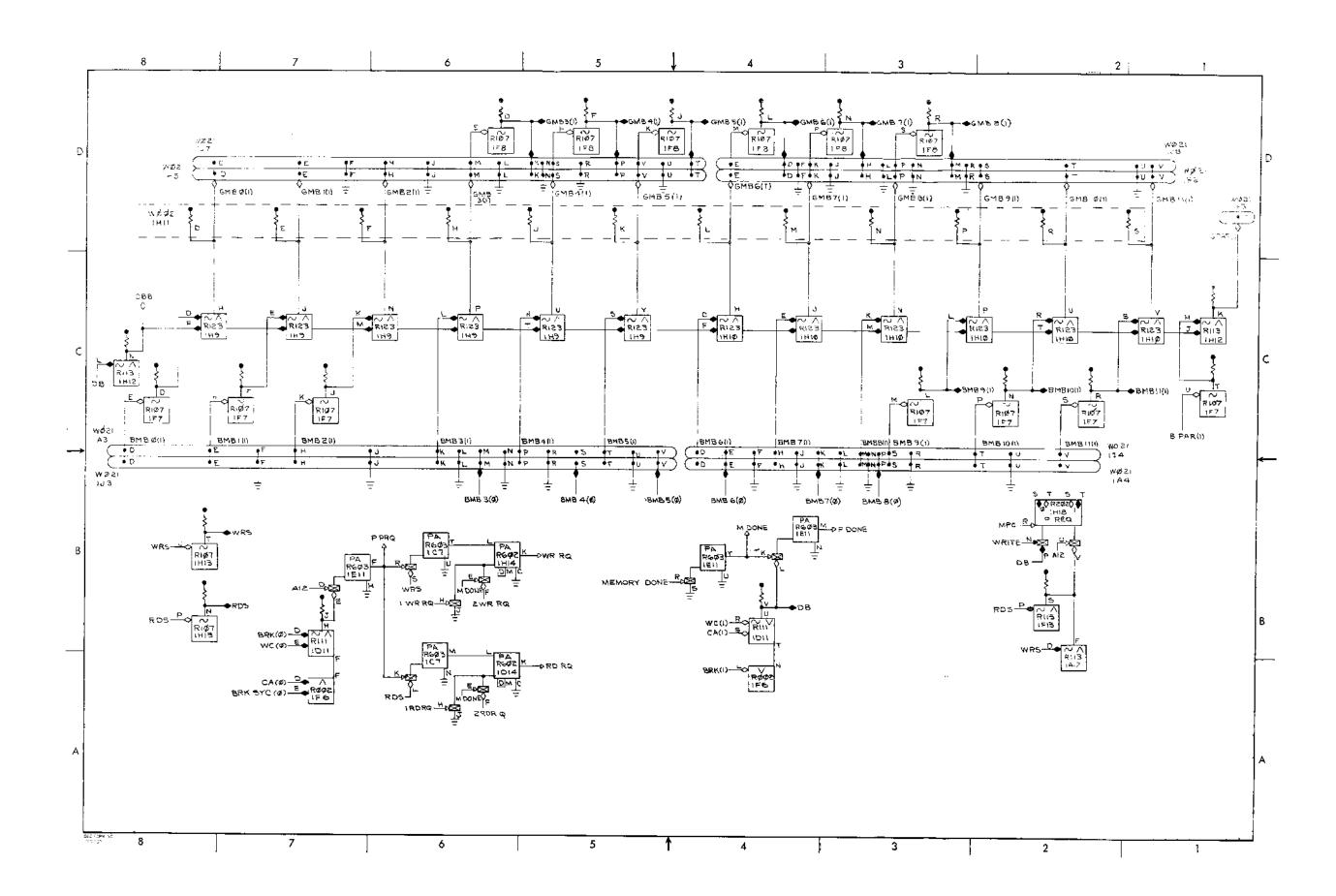

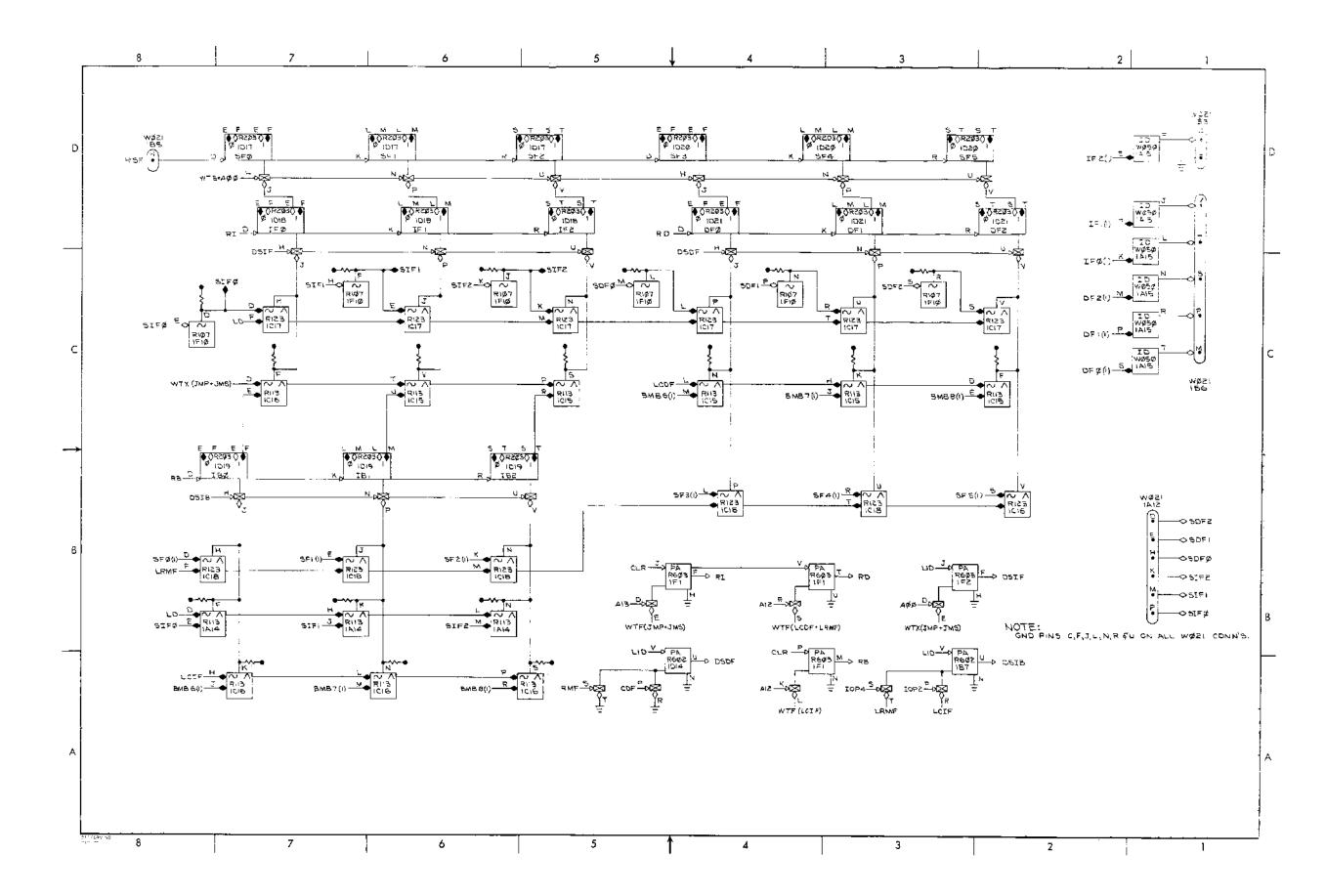

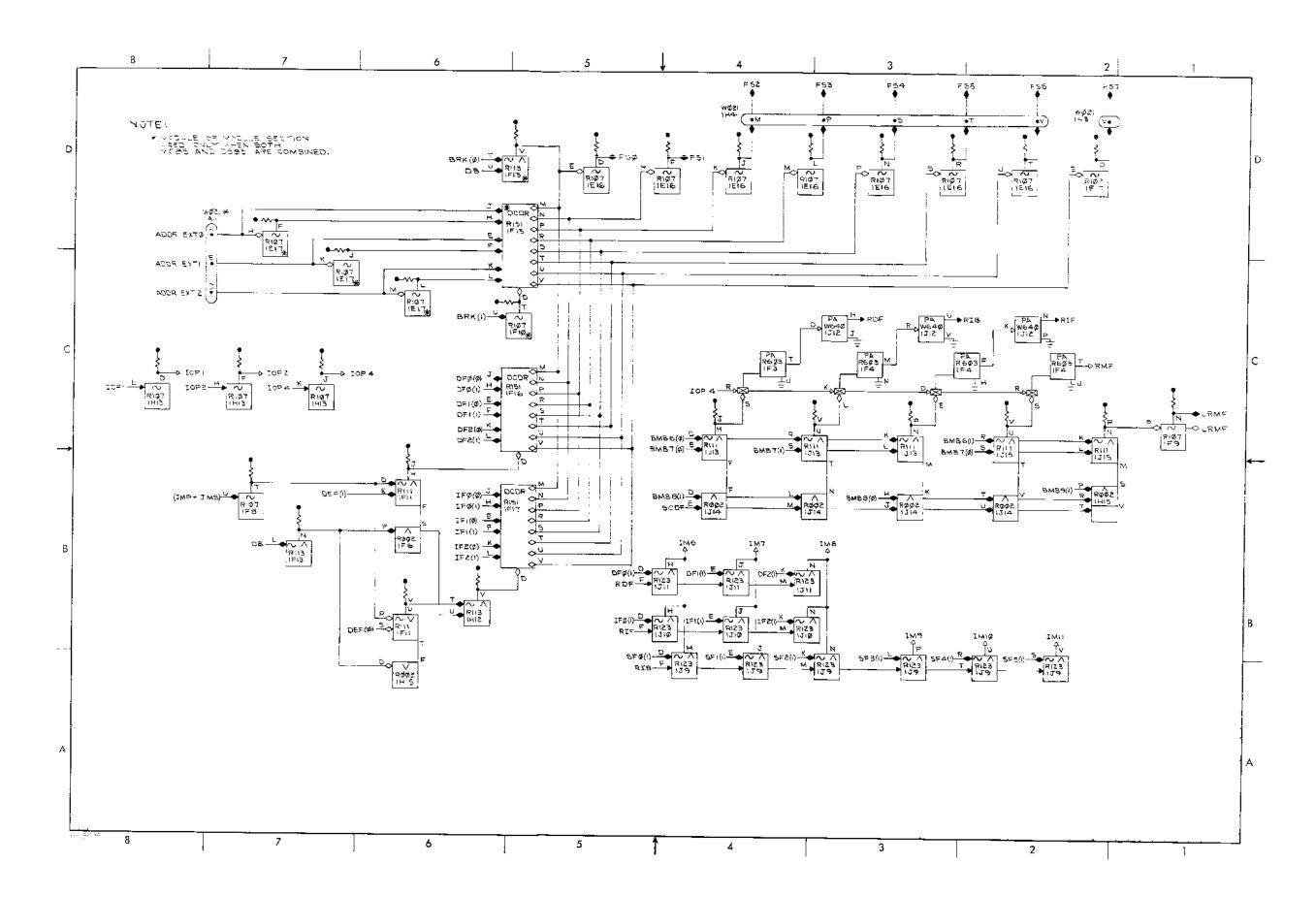

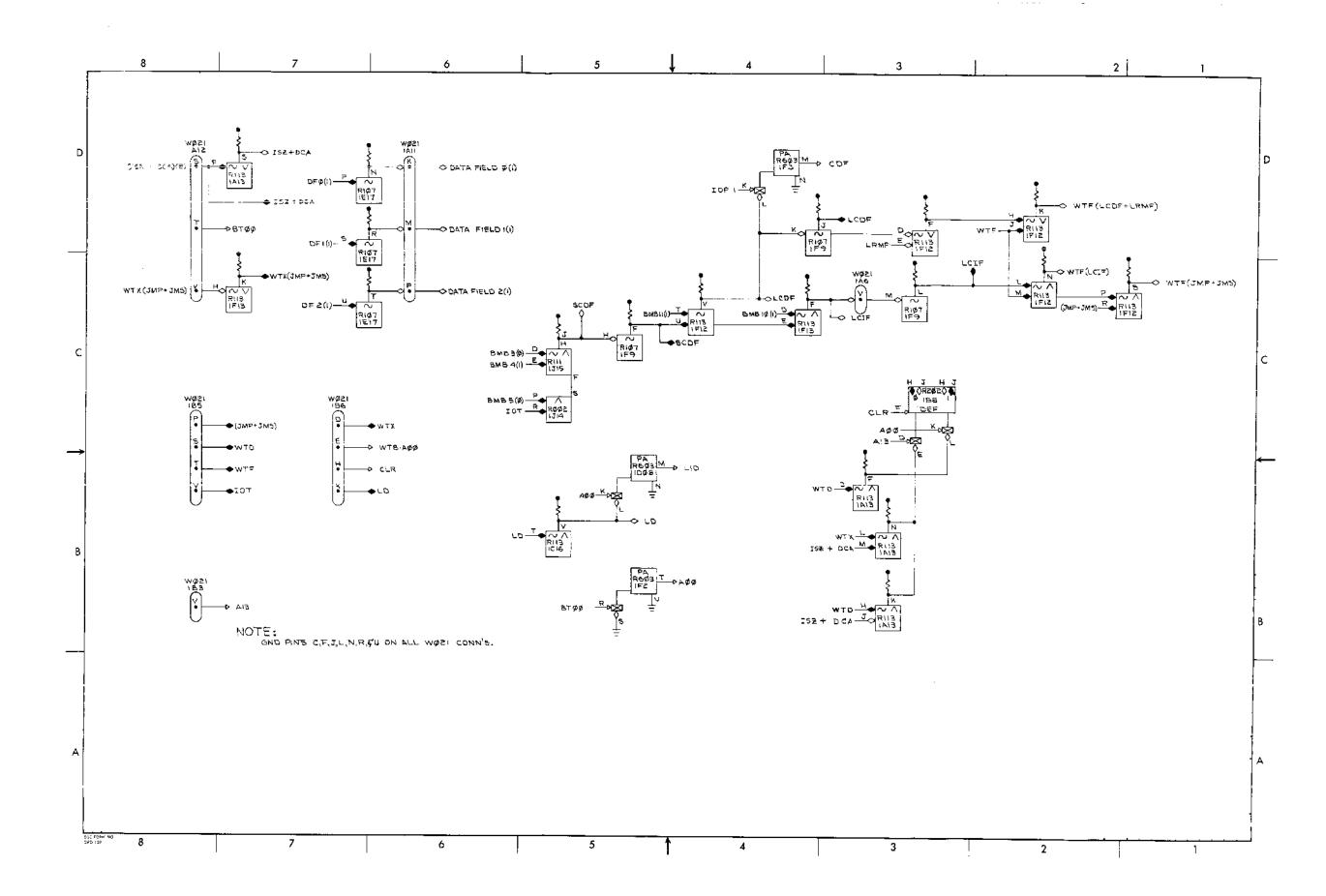

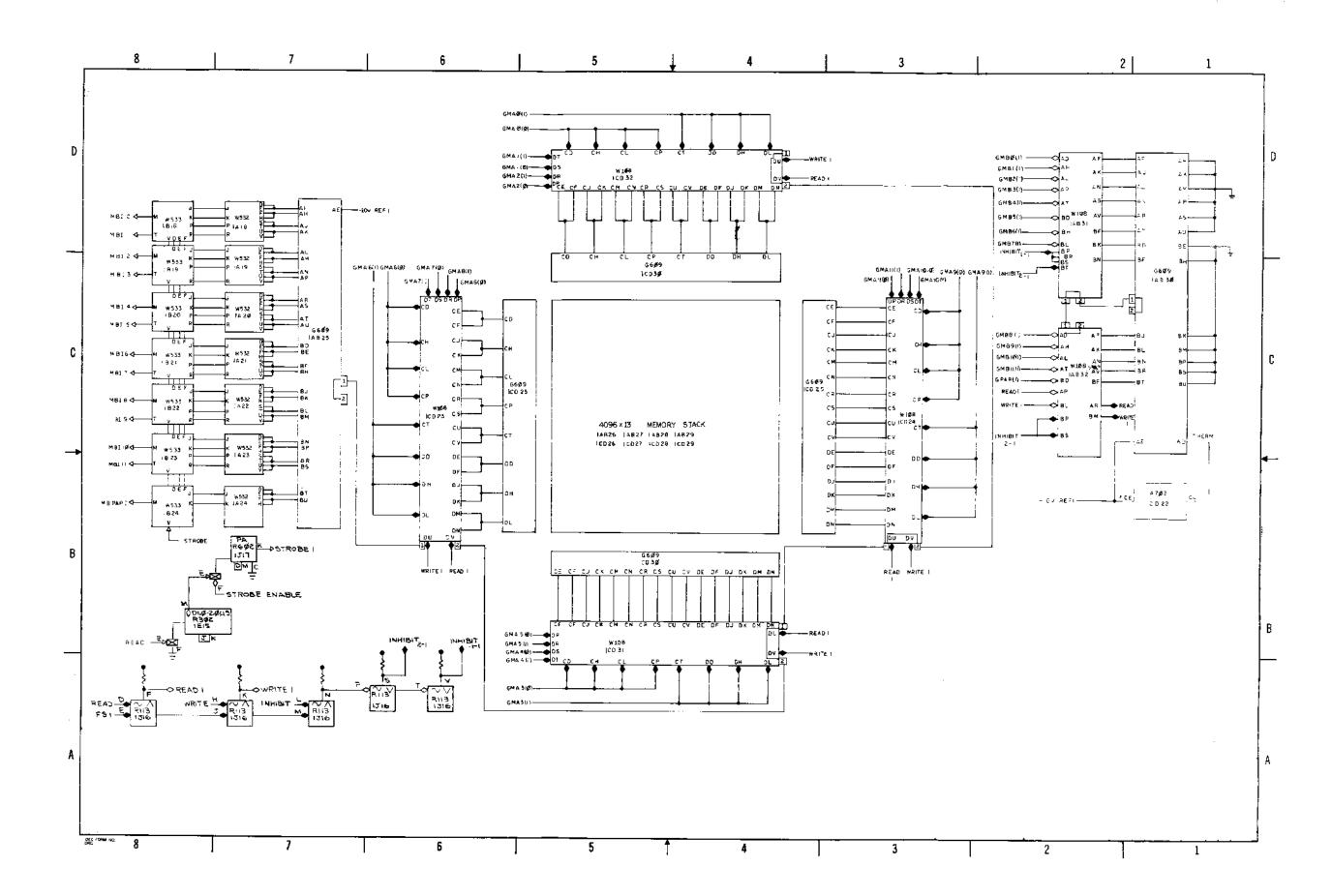

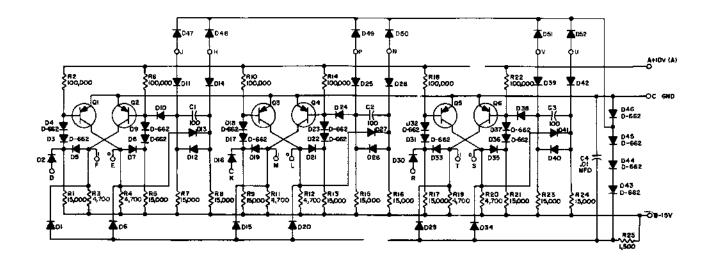

| D-BS-8S-          | 0-4            | Memory Block Diagram (4K)       | A-3           |

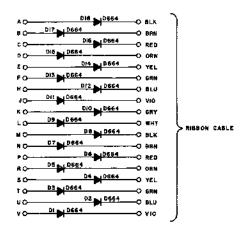

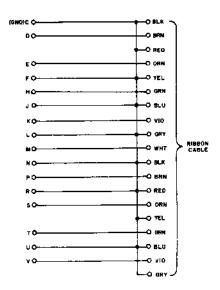

| D-CL-8S-          | -0~5           | 10 Cable Schedules              | A-5           |

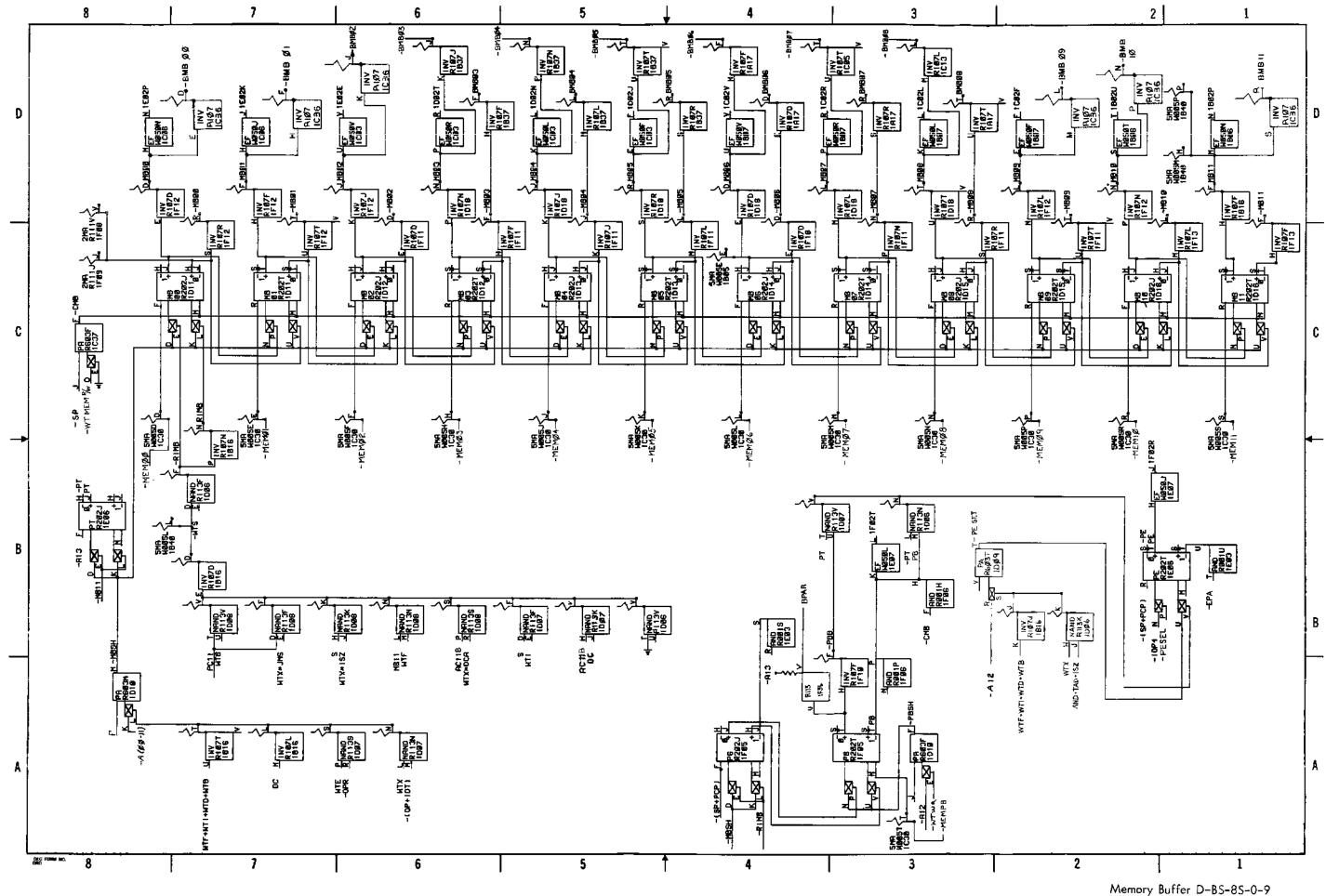

| D-BS-8S-          | 0-9            | Memory Buffer                   | A-7           |

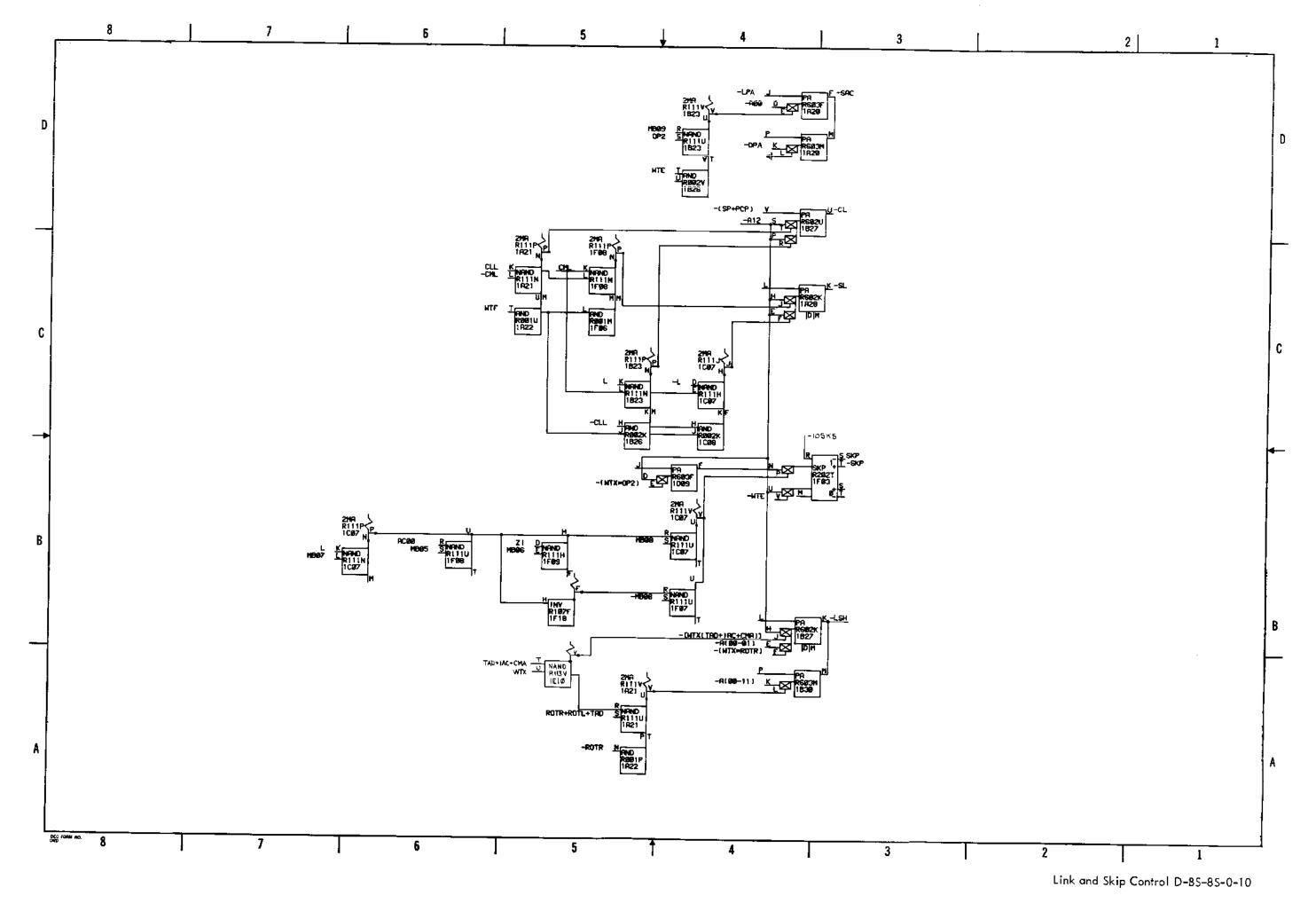

| D-BS-8S-          | 0-10           | Link and Skip Control           | A-9           |

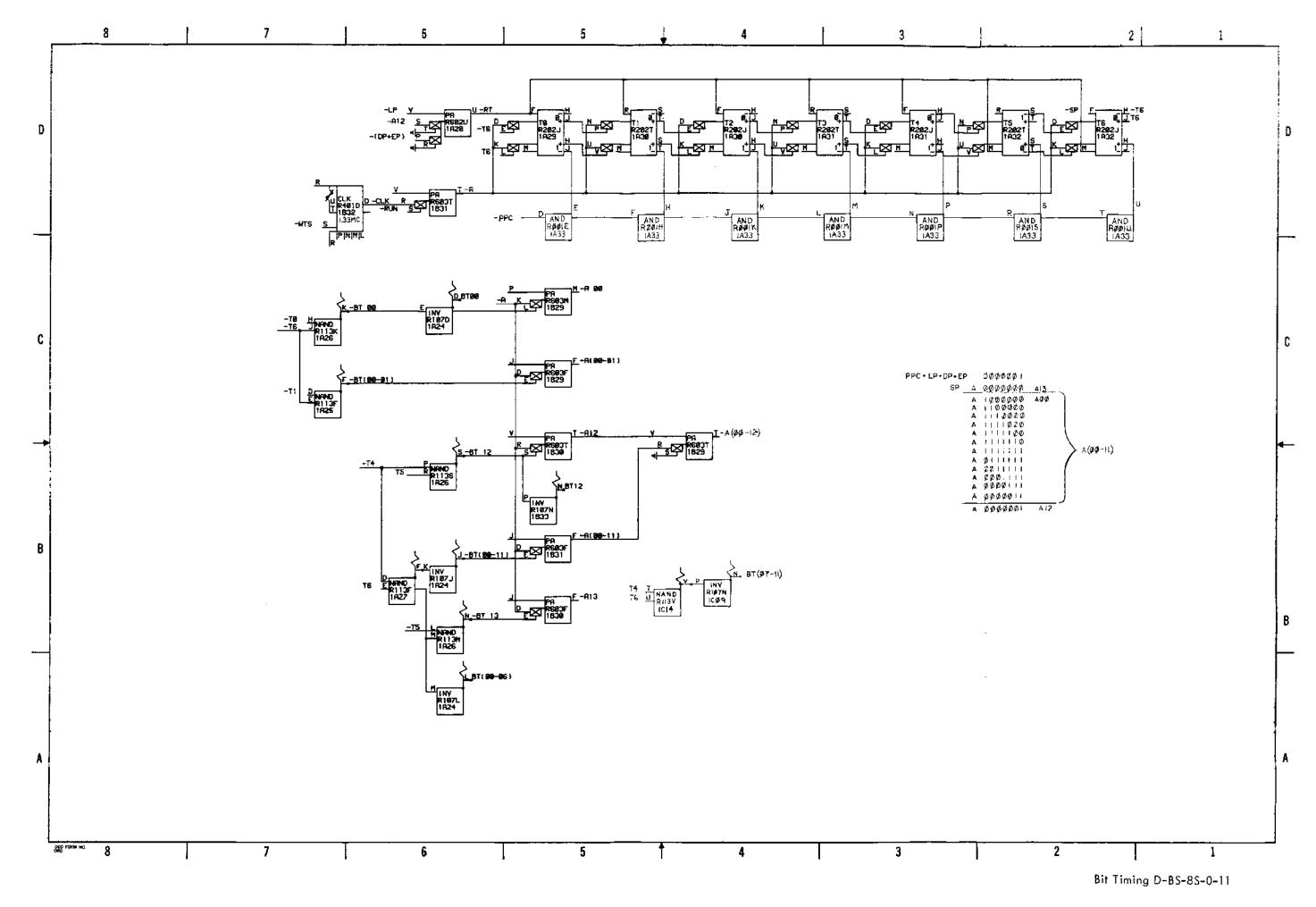

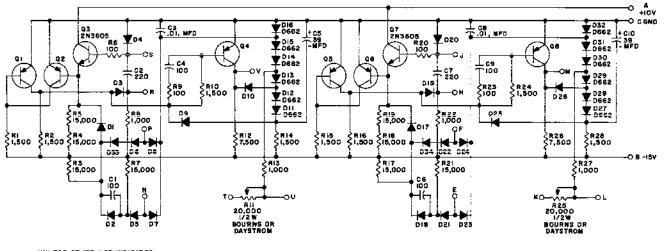

| D-BS-8S-          | 0-17           | Bit Timing                      | A-11          |

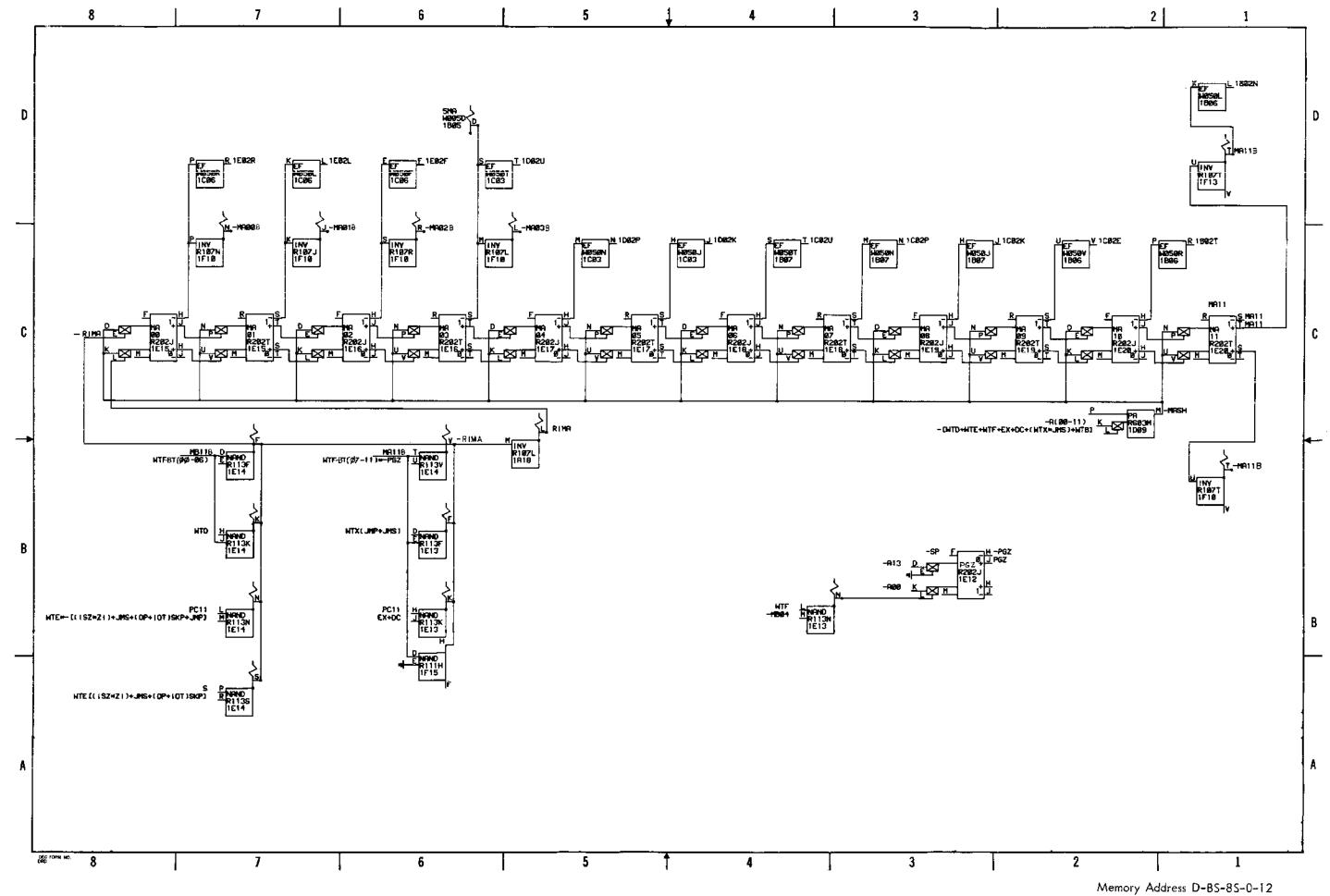

| D-8S-8S-          | 0-12           | Memory Address                  | A-13          |

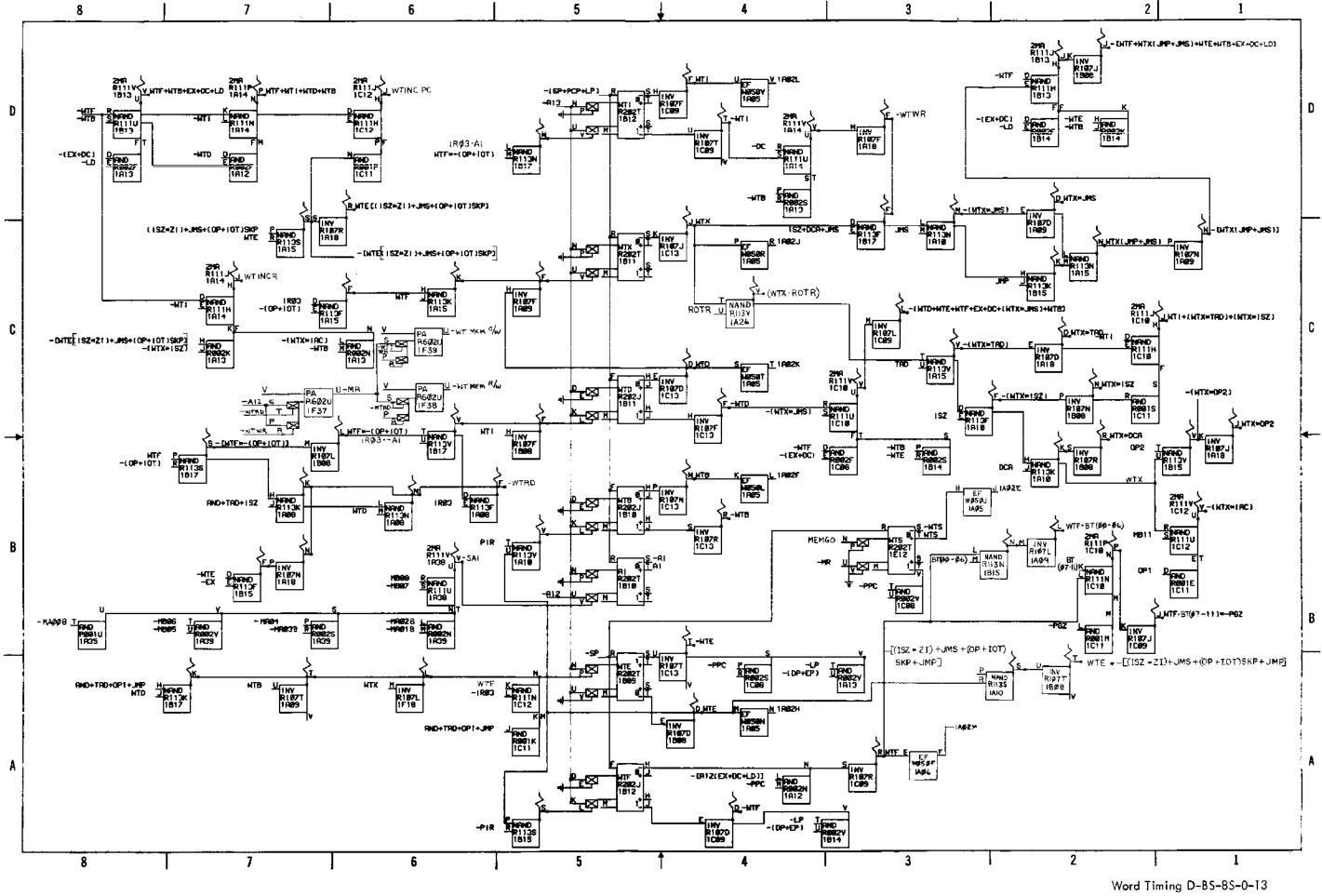

| D-BS-8S-          | 0-13           | Word Timing                     | A-15          |

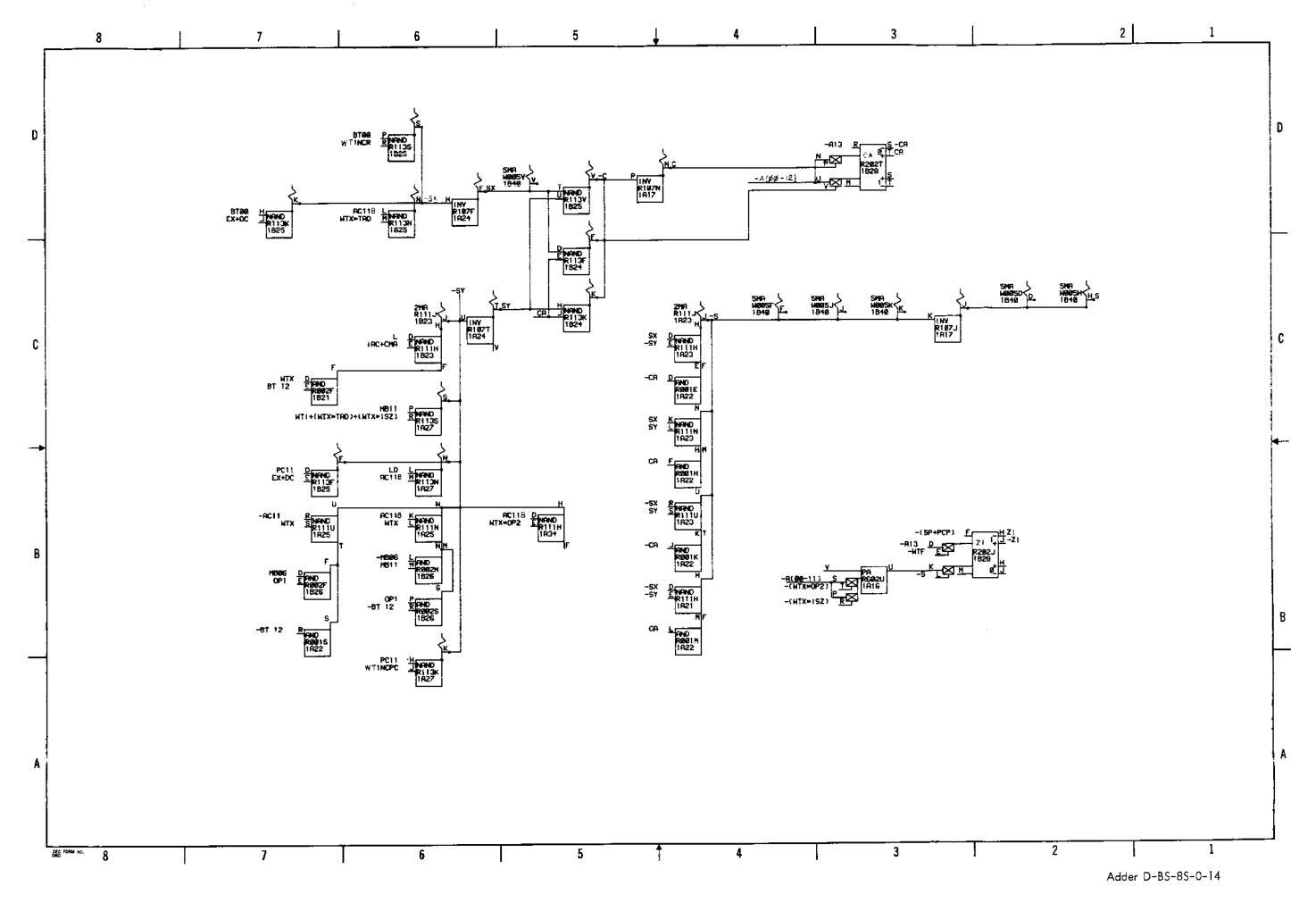

| D-BS-85-          | 0-14           | Adder                           | A-17          |

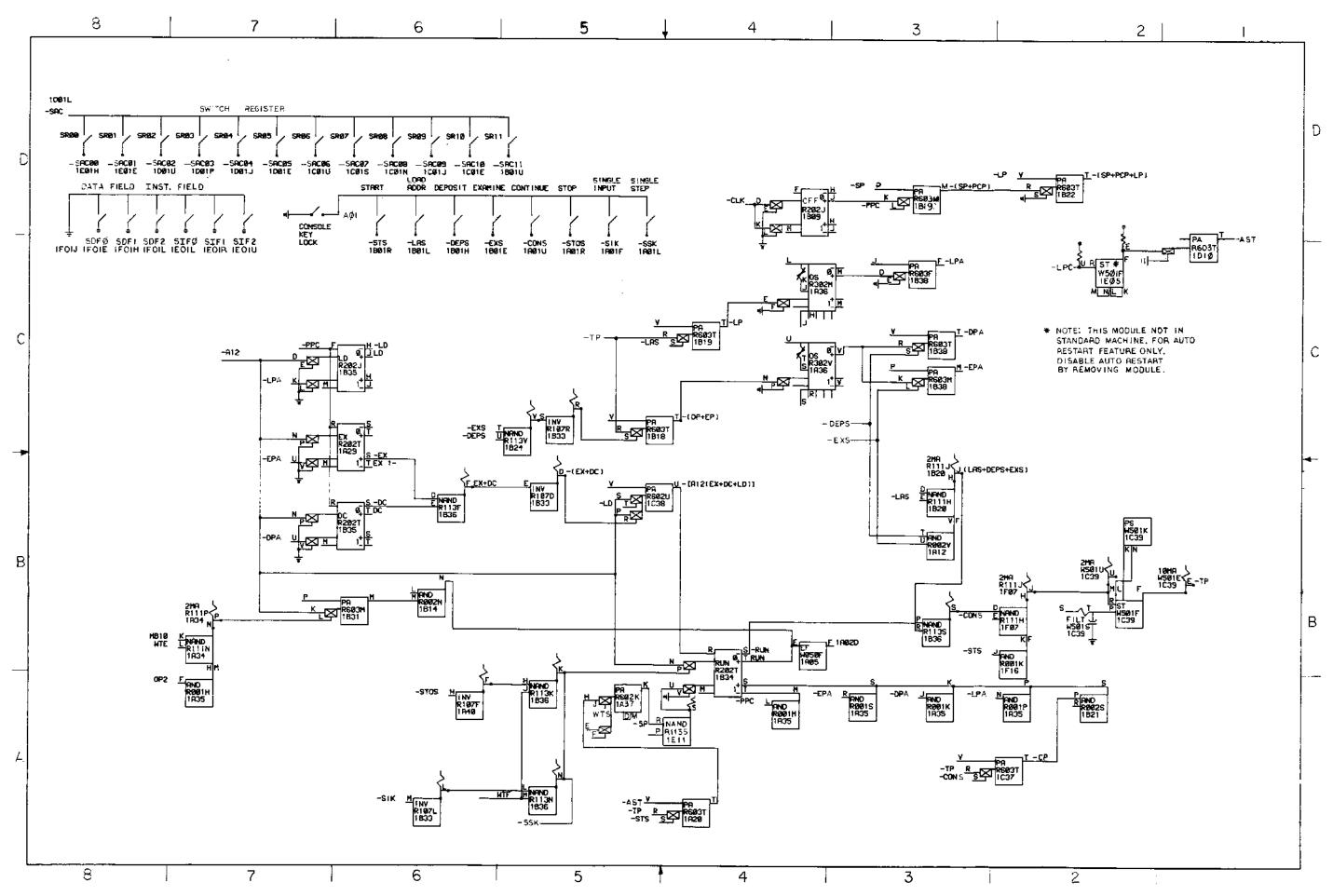

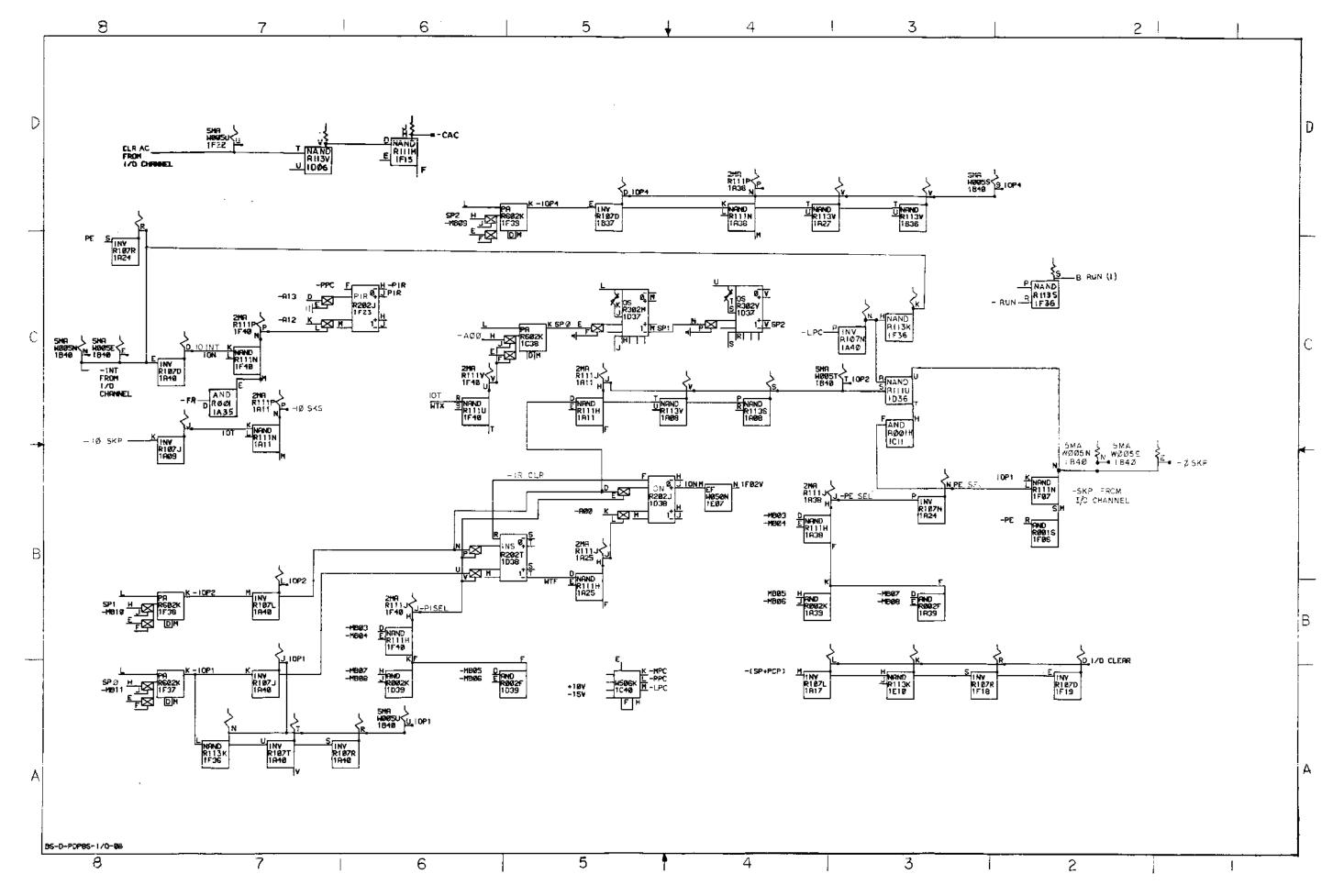

| D-BS-85-          | 0-15           | Control                         | A-19          |

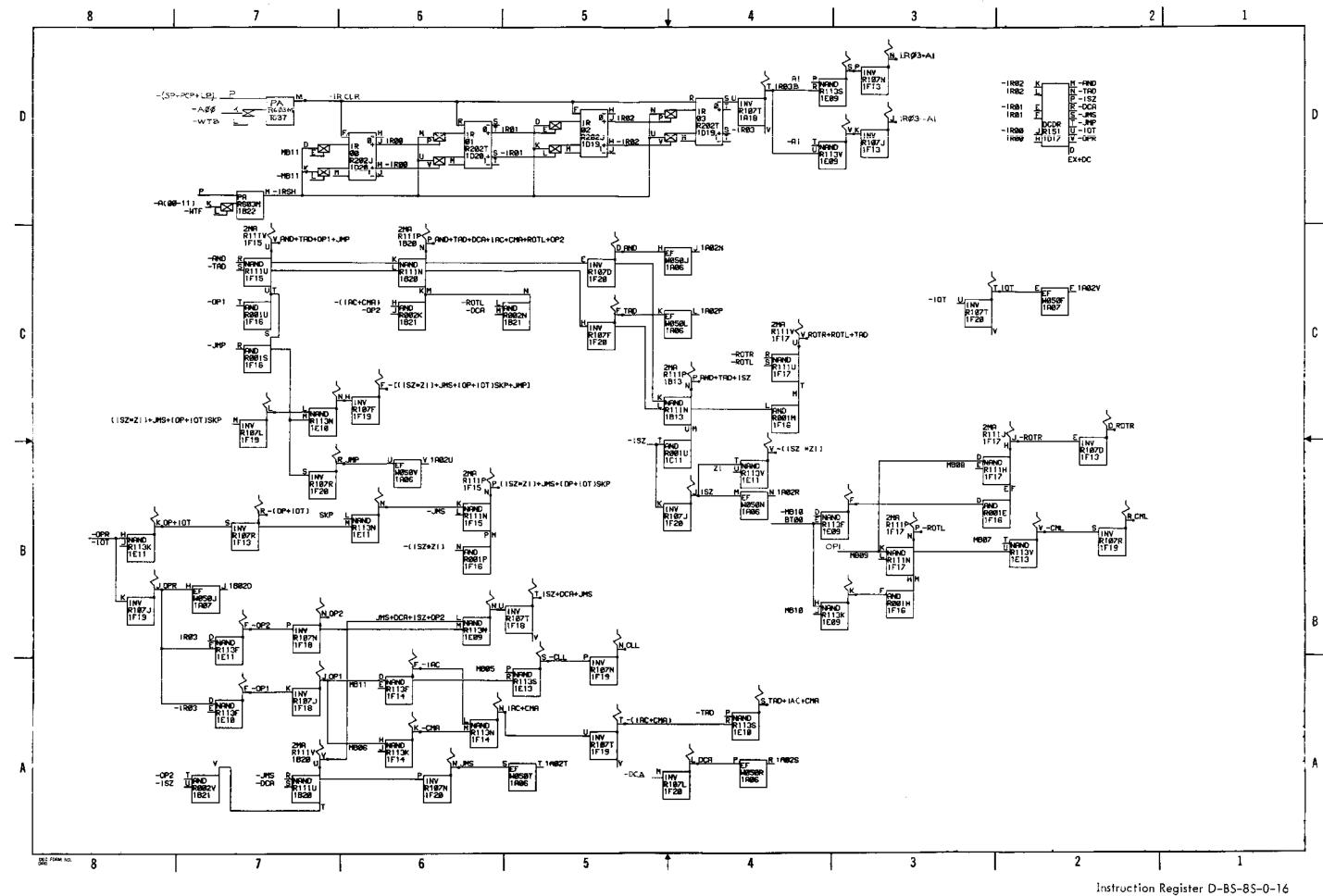

| D-BS-8S-          | 0-16           | Instruction Register            | A-21          |

| D-BS-85-          | 0-17           | In-Out                          | A-23          |

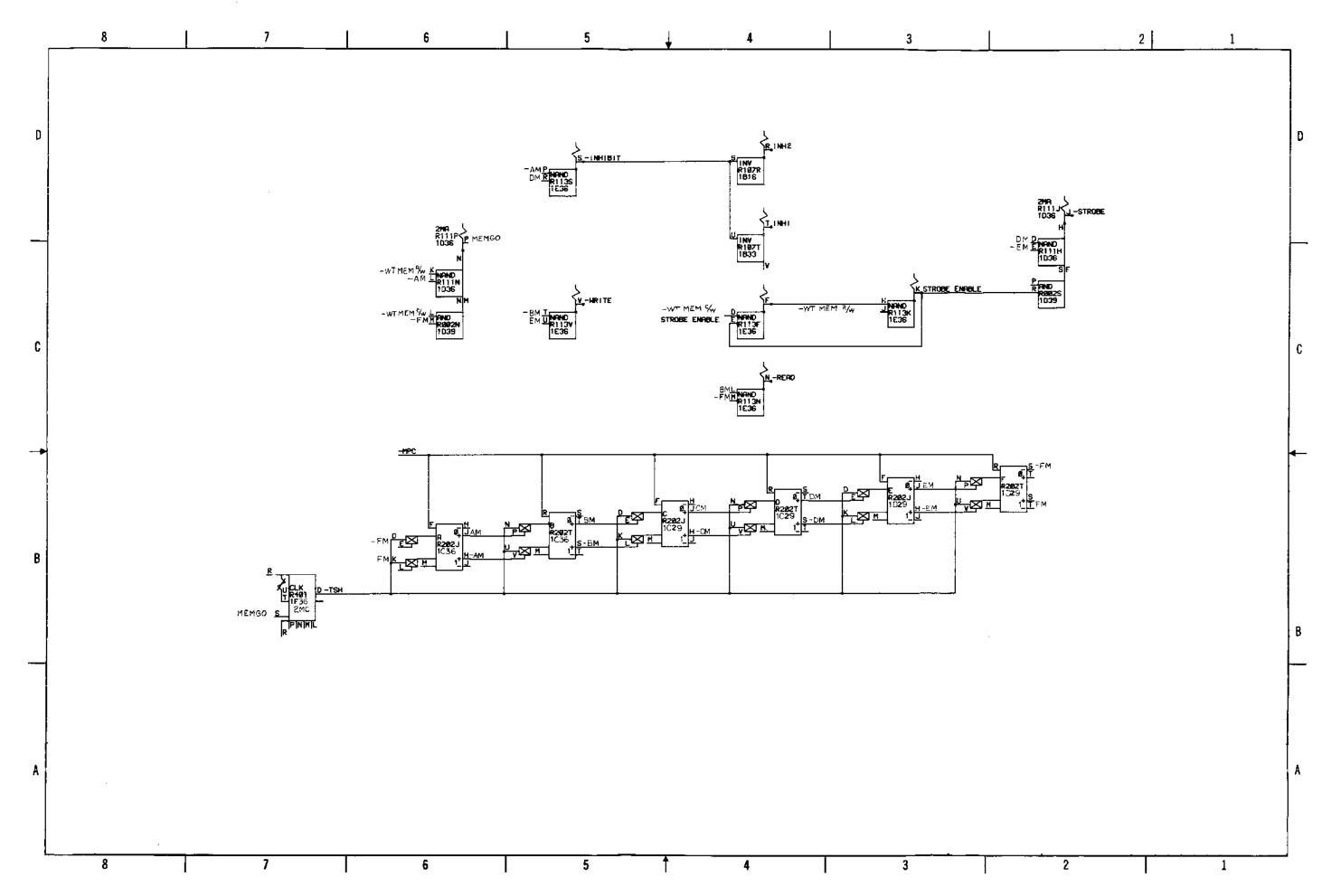

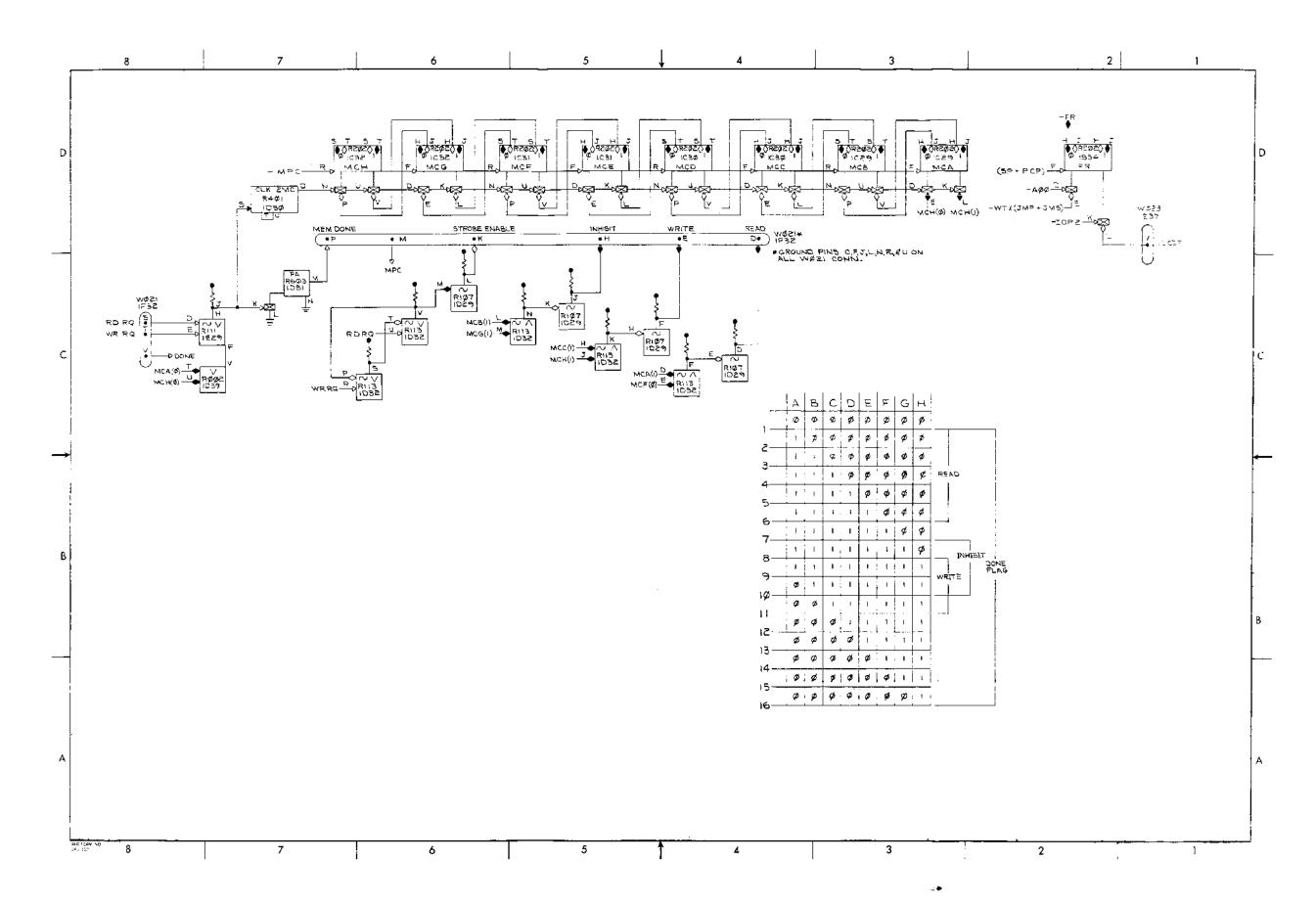

| D-BS-85-          | 0-18           | Memory Control (4K)             | A-25          |

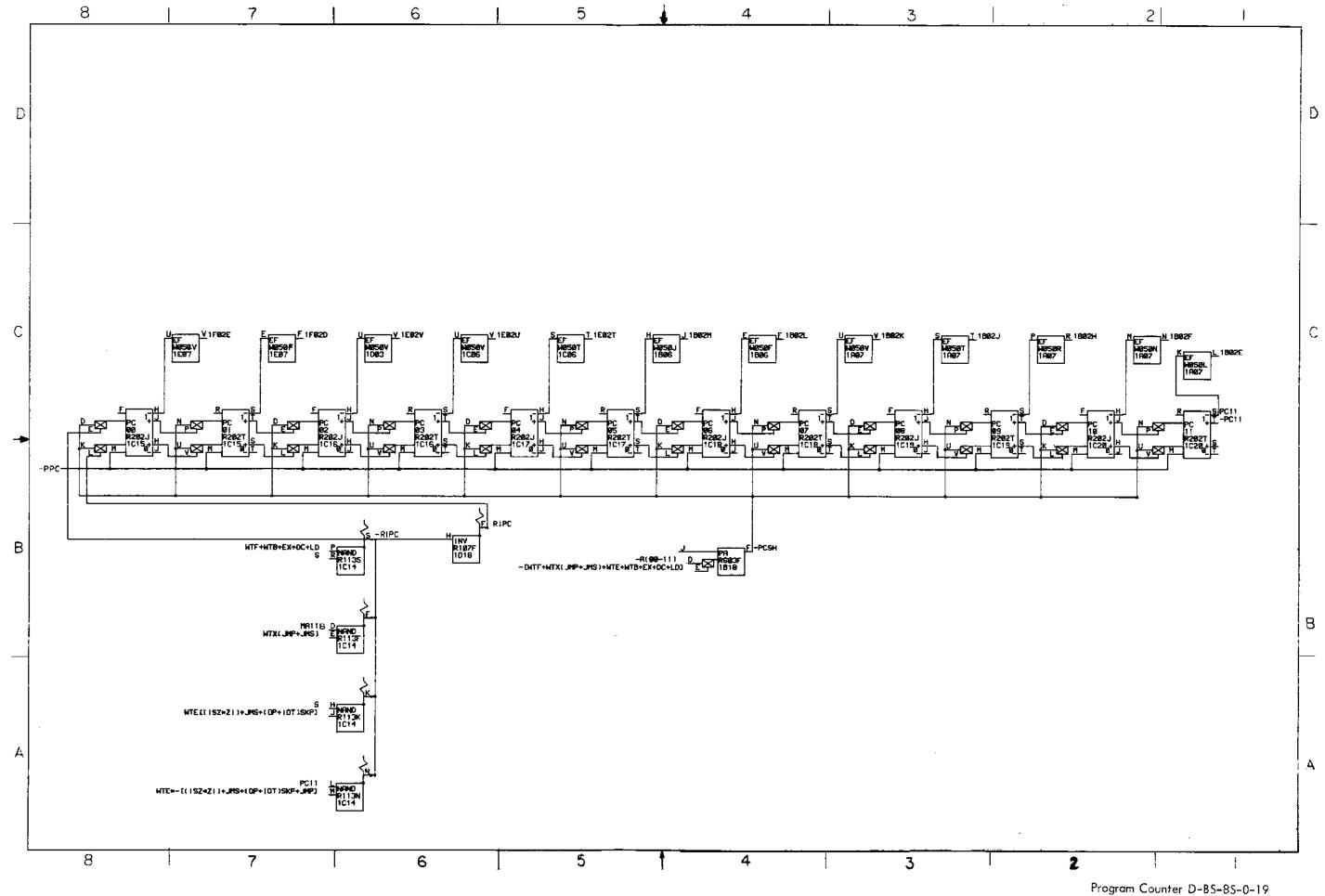

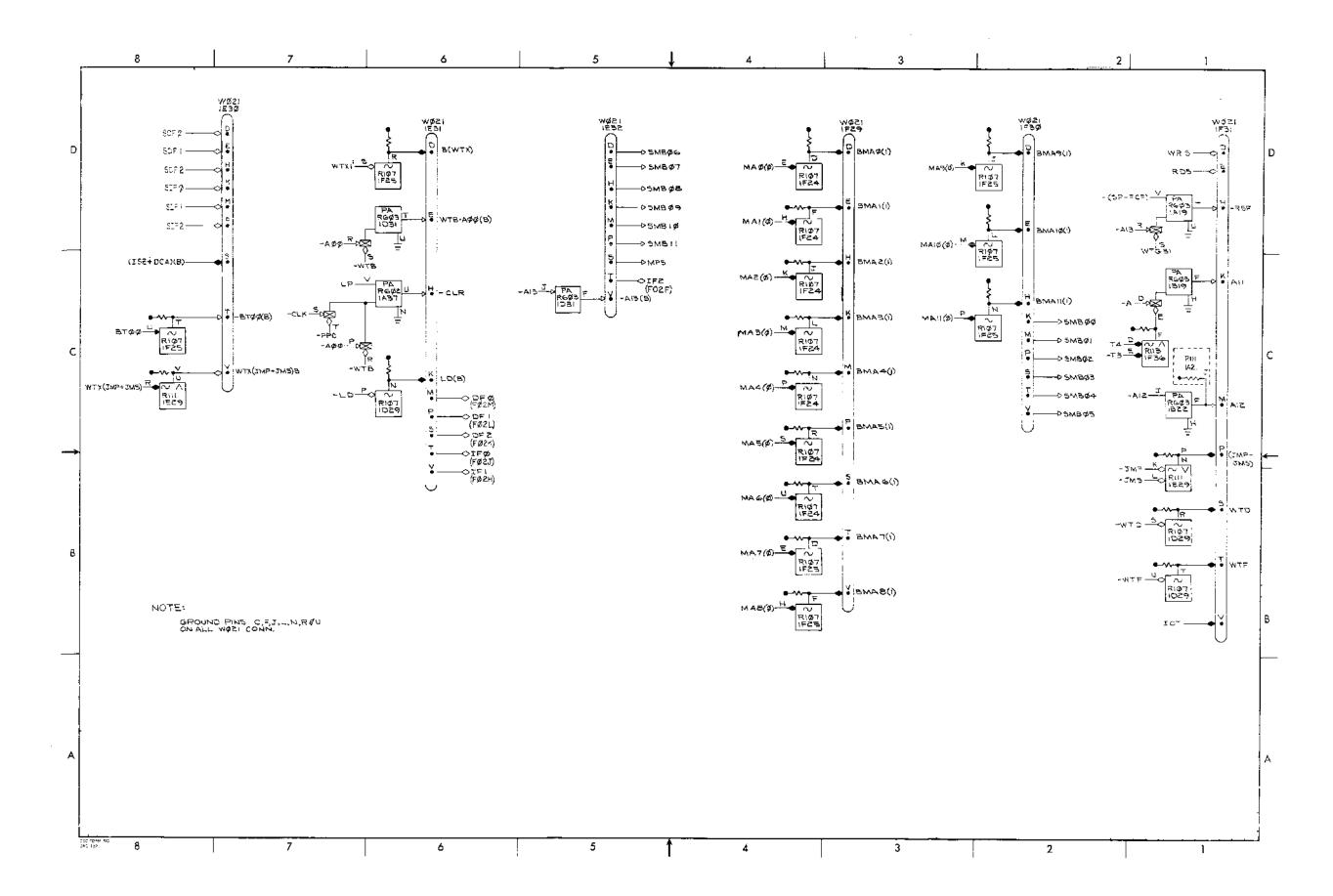

| D-BS-8S-0         | 0-19           | Program Counter                 | A-27          |

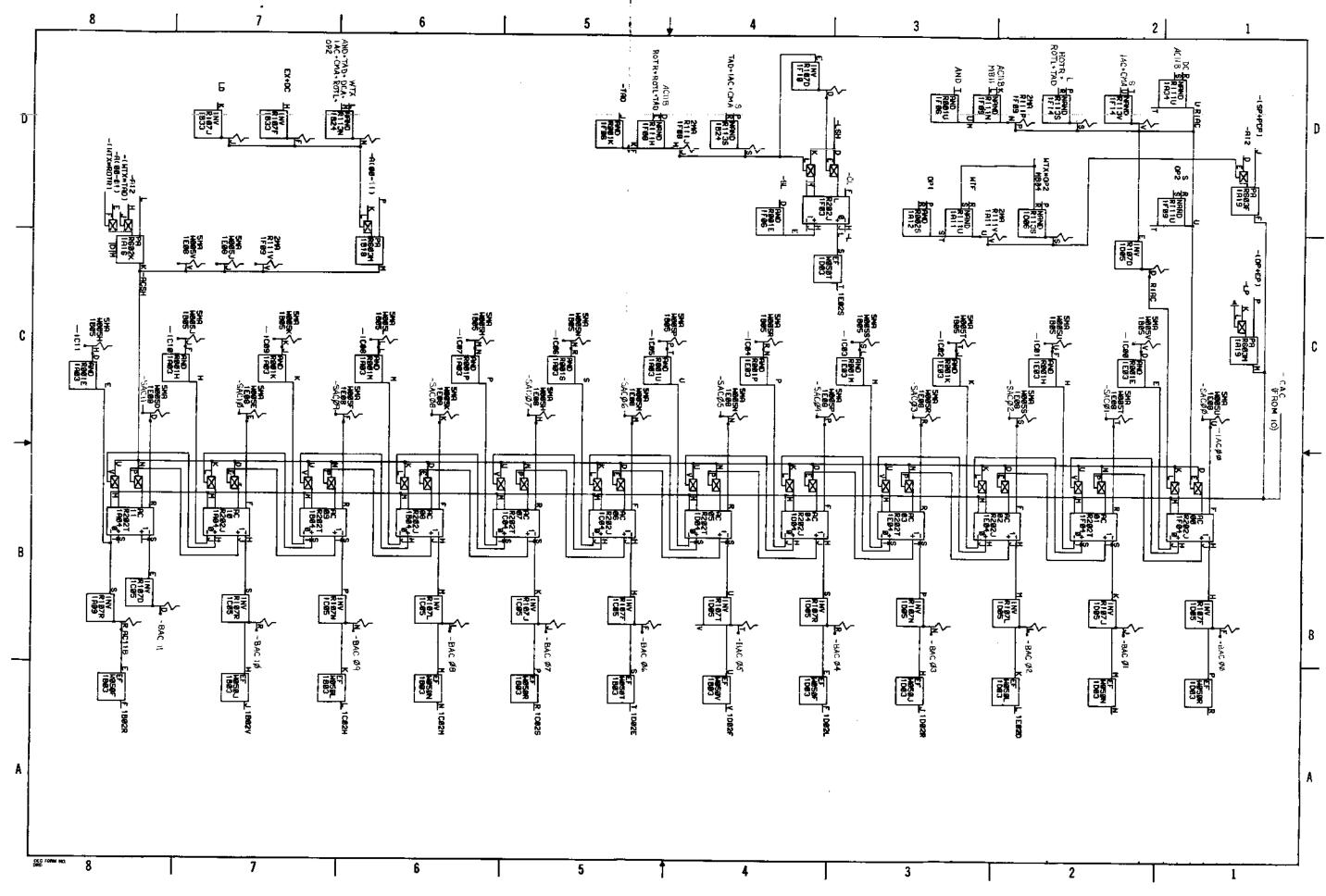

| D-BS-85-6         | 0-20           | Accumulator                     | A- <b>2</b> 9 |

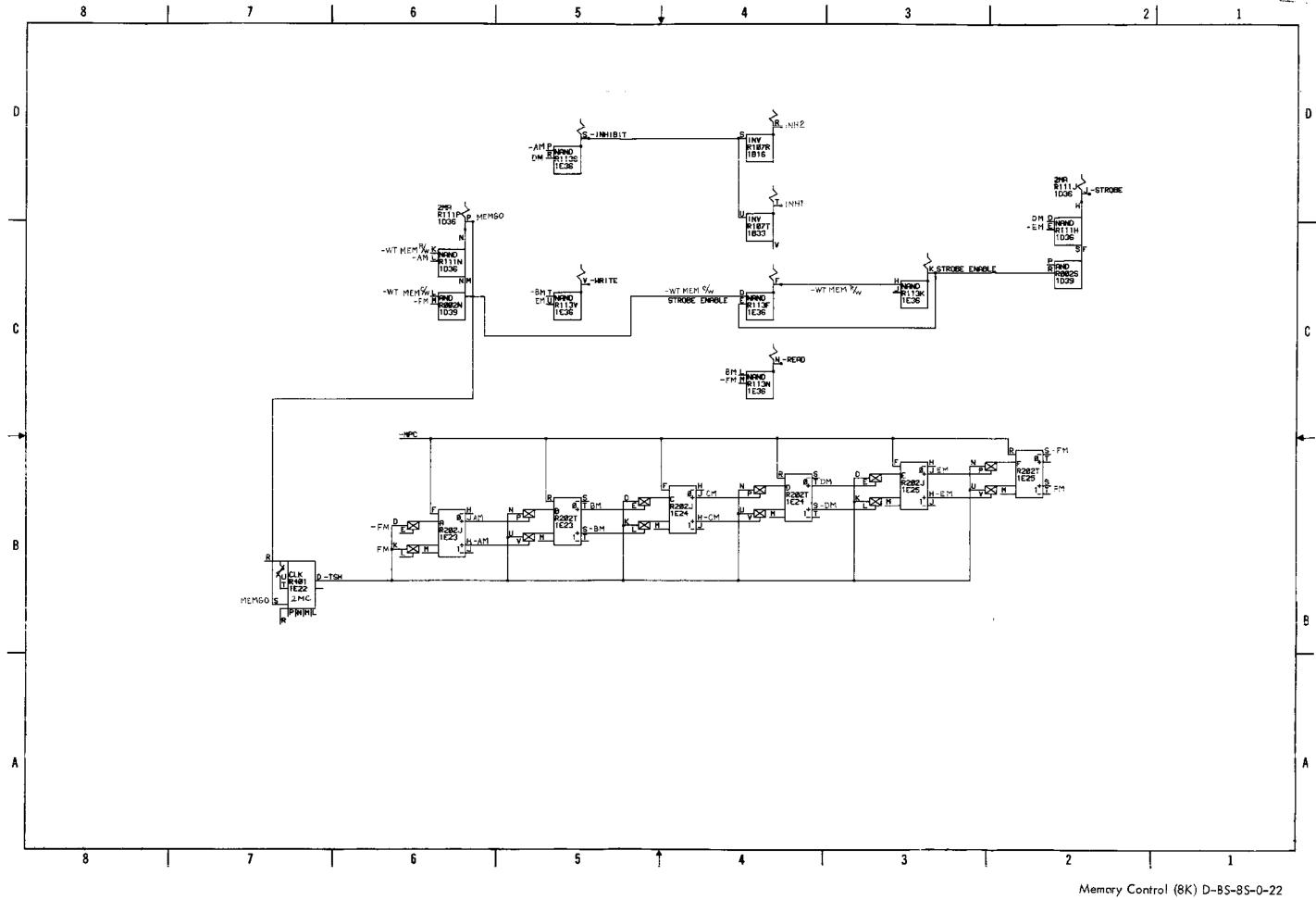

| D-BS-8S-0         | 0-22           | Memory Control (8K)             | A-31          |

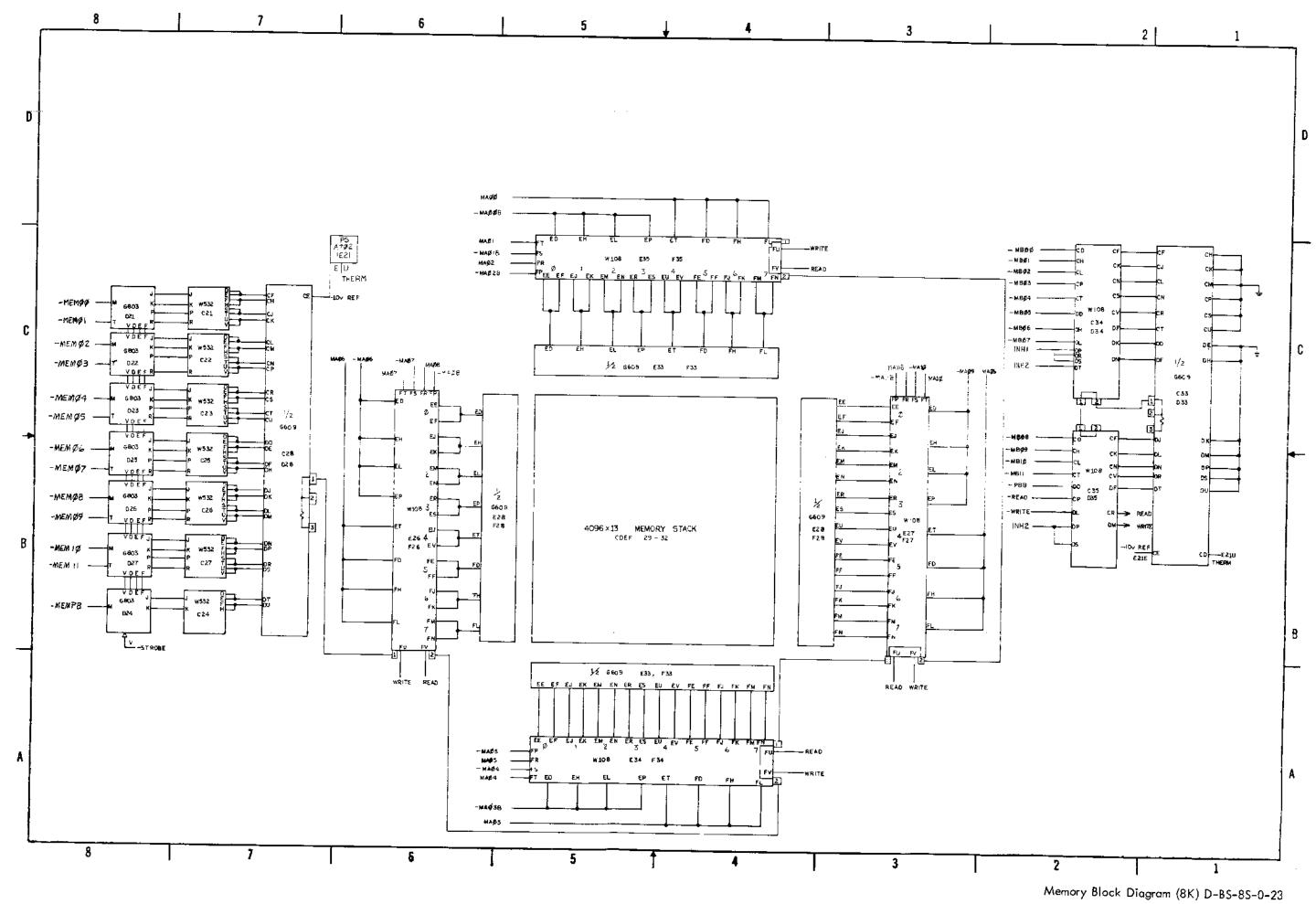

| D-BS-8S-0         | 0-23           | Memory Block Diagram (8K)       | A-33          |

| D-DI-8S-0         | 0-27           | Drawing Index List (Sheet 1)    | A-35          |

| D-DI-8S-0         | 0-27           | Drawing Index List (Sheet 2)    | A-37          |

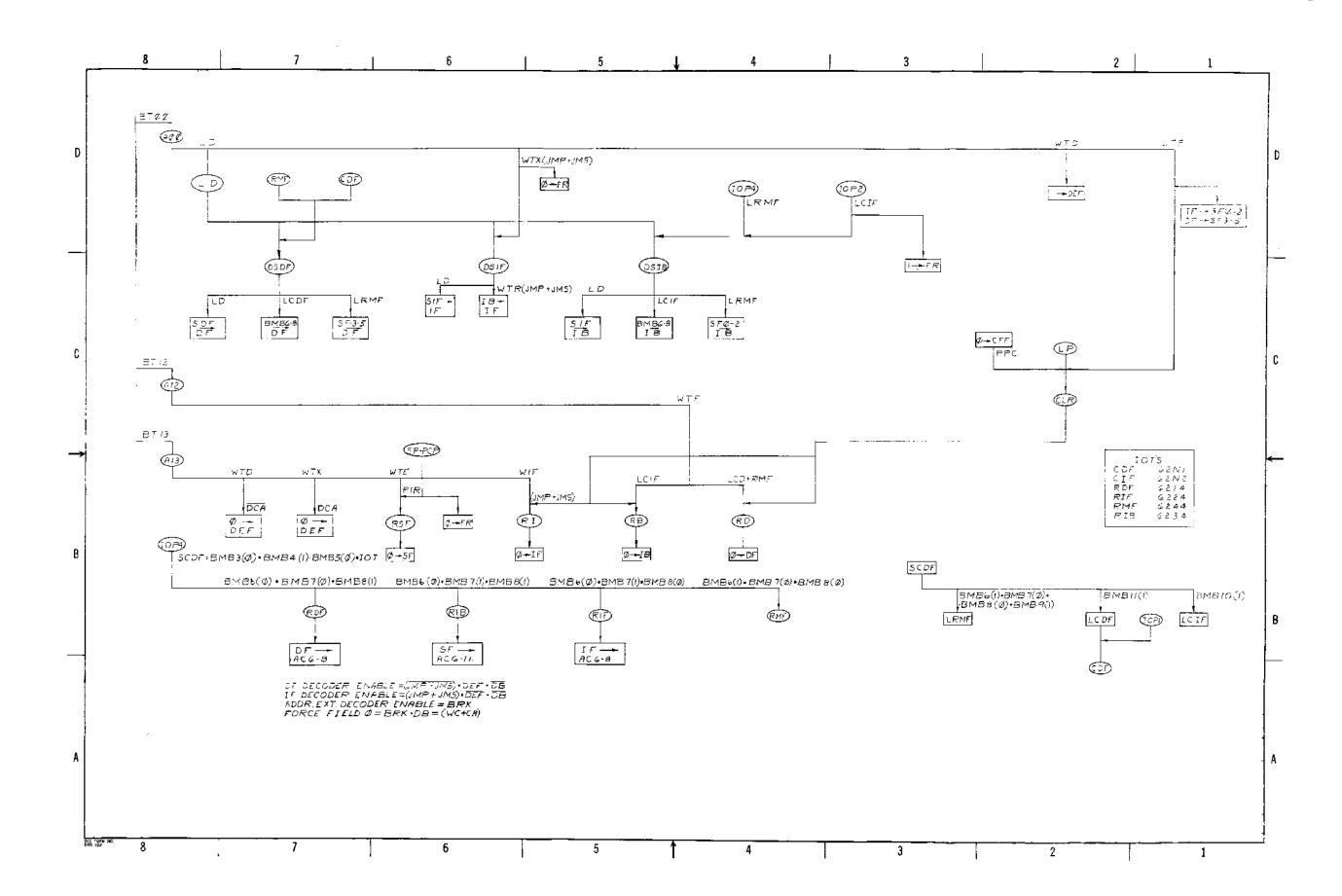

| D-FD <b>-</b> 8S- | 0-29           | Memory and In-out Flow          | A-39          |

| D-FD-8S-          | 0-30           | Main Flow                       | A-41          |

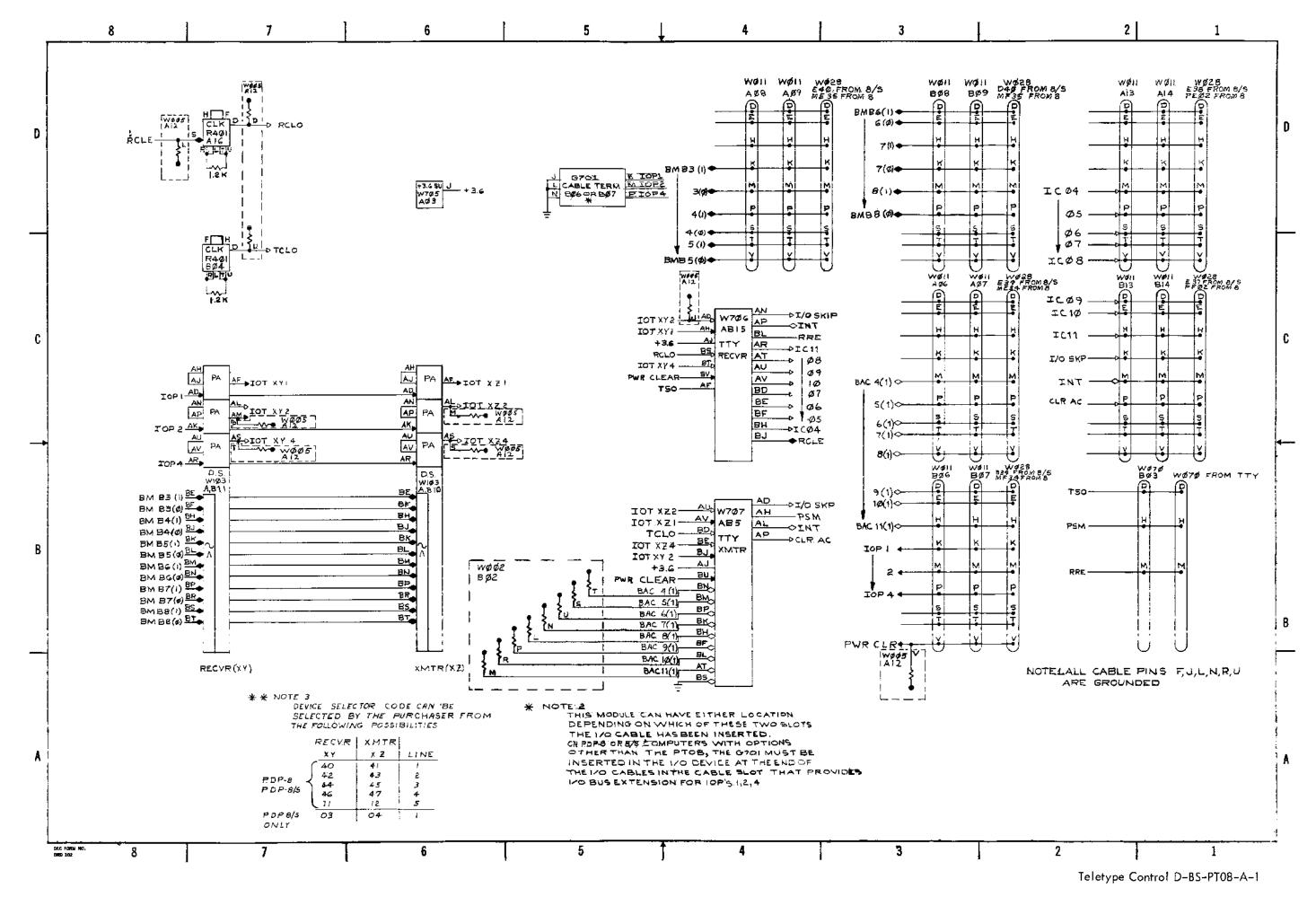

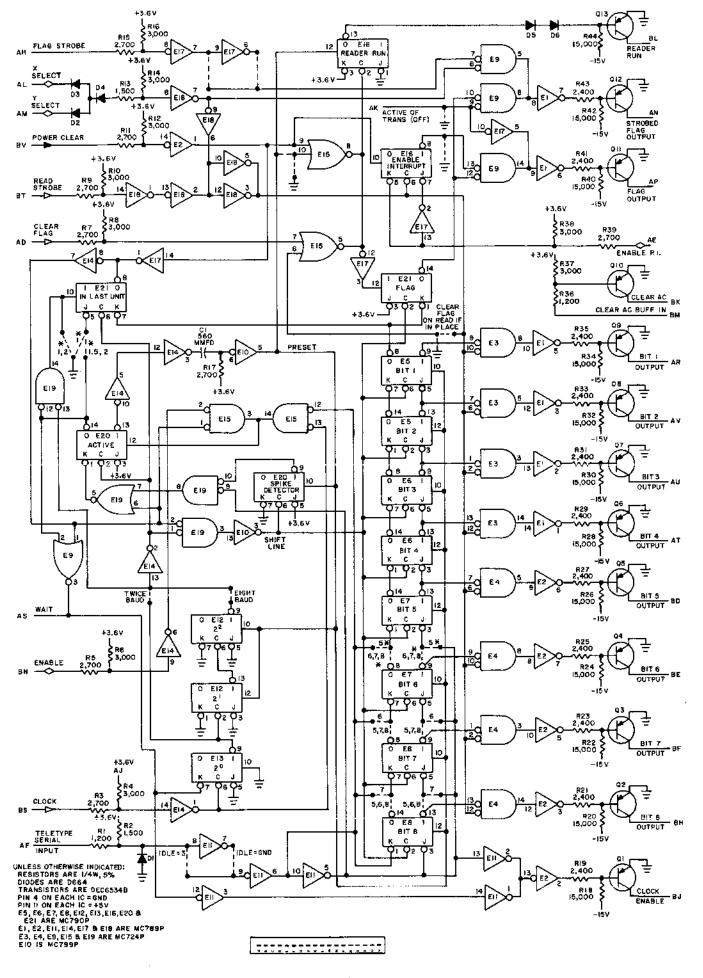

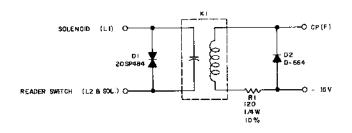

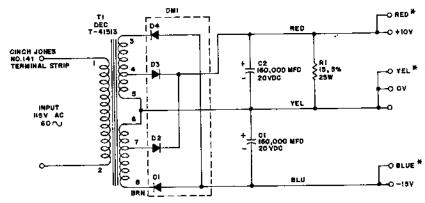

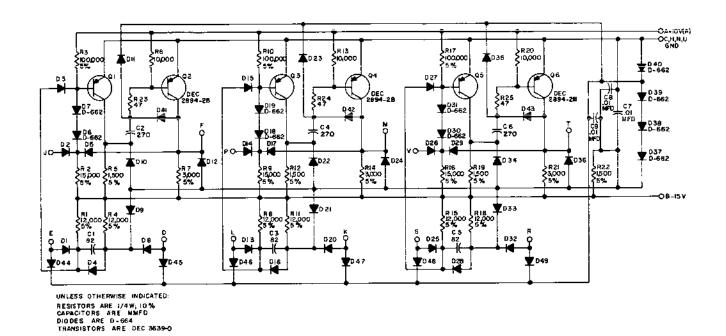

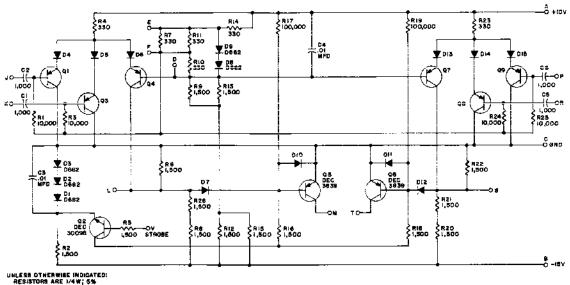

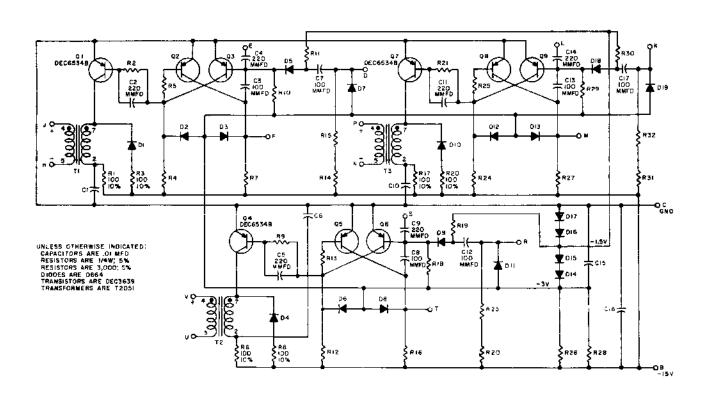

| D-BS-PTO          | 8 <b>-</b> A-1 | Teletype Control                | A-43          |

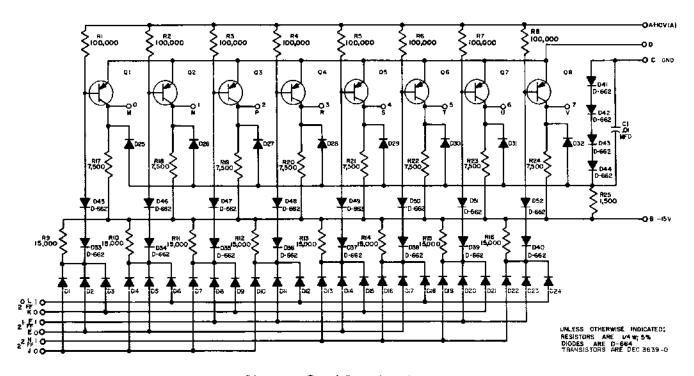

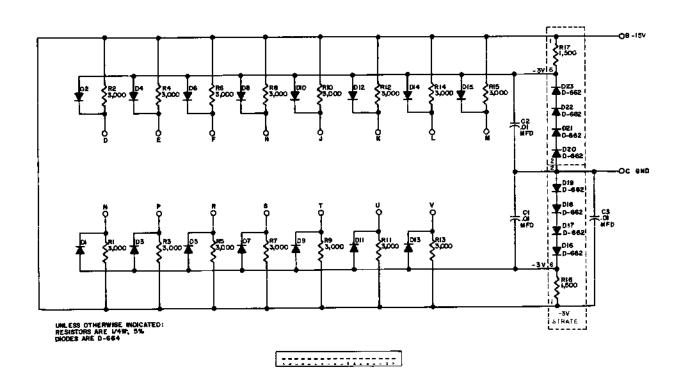

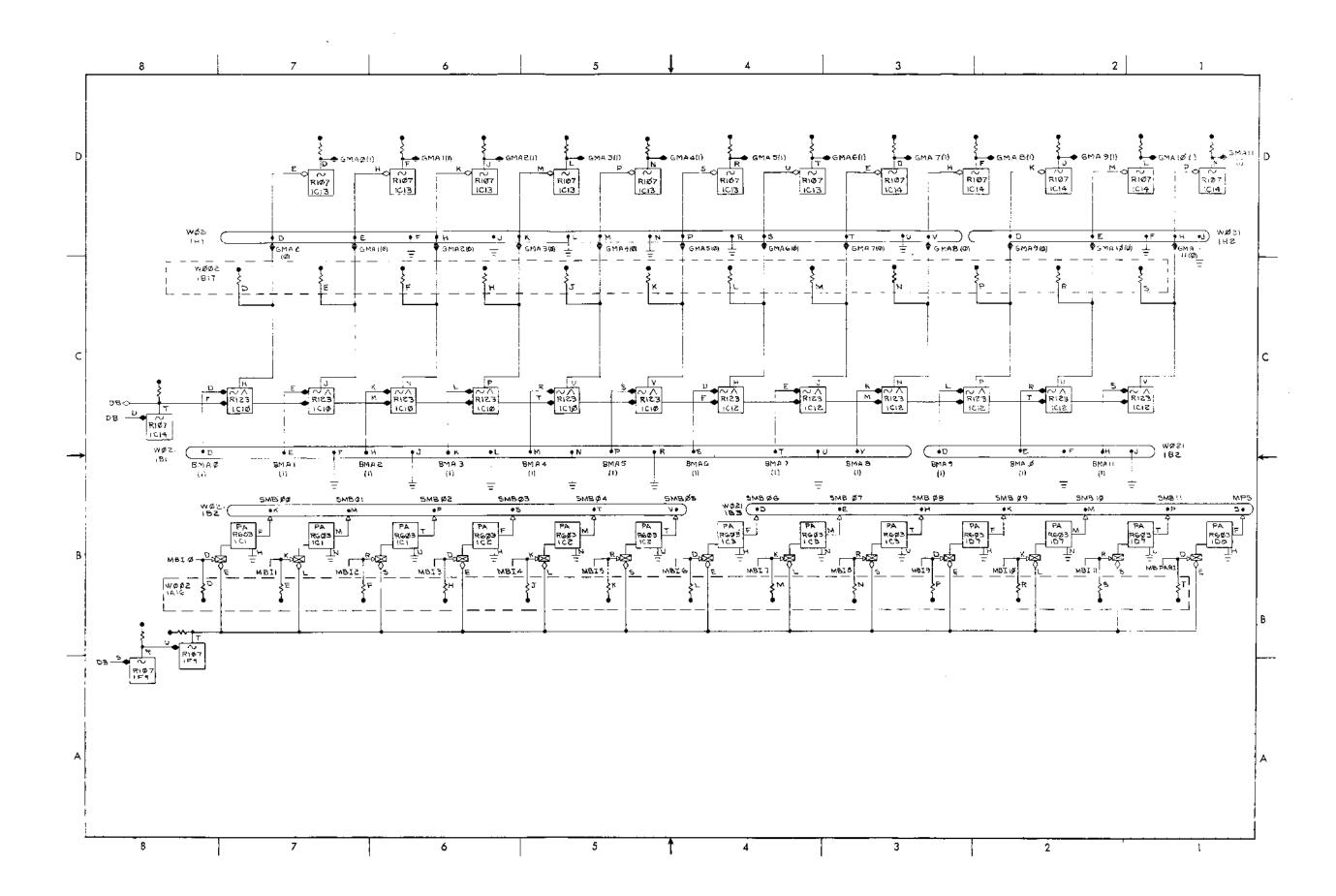

| D-MU-85           | -0-25          | Module Utilization (A-D) (8K)   | A-63          |

| D-MU-8S-          | -0 <b>-</b> 25 | Module Utilization (E+F) (8K)   | A-65          |

| D-MU <b>-</b> 8S- | -0-26          | Module Utilization (A-D) (4K)   | A-67          |

| D-MU-8S-0-26      |                | Module Utilization (E+F) (4K)   | A-69          |

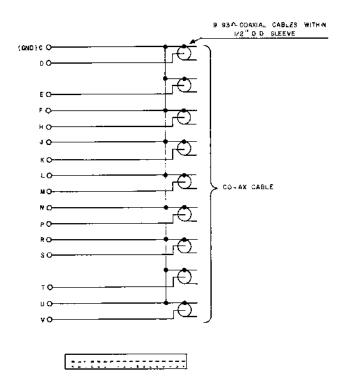

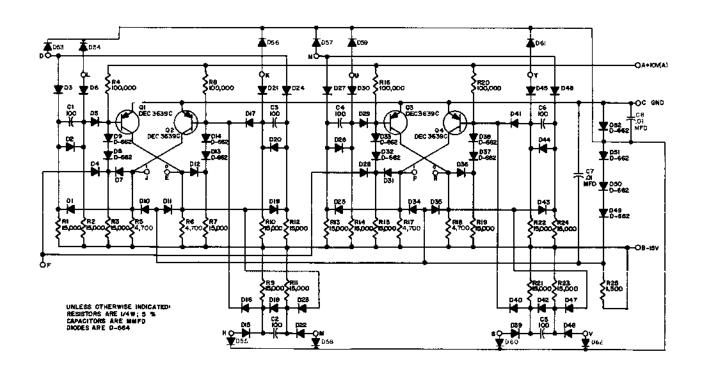

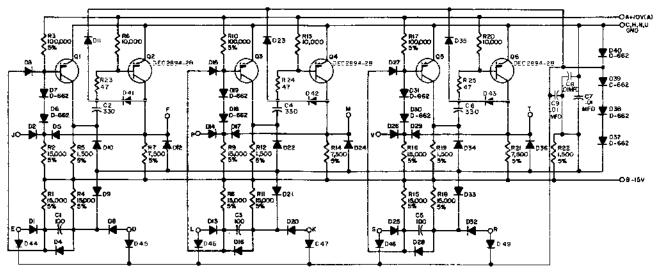

|                | Memory Expansion and Data Break Interconnecting Cables | C <b>-</b> 5 |

|----------------|--------------------------------------------------------|--------------|

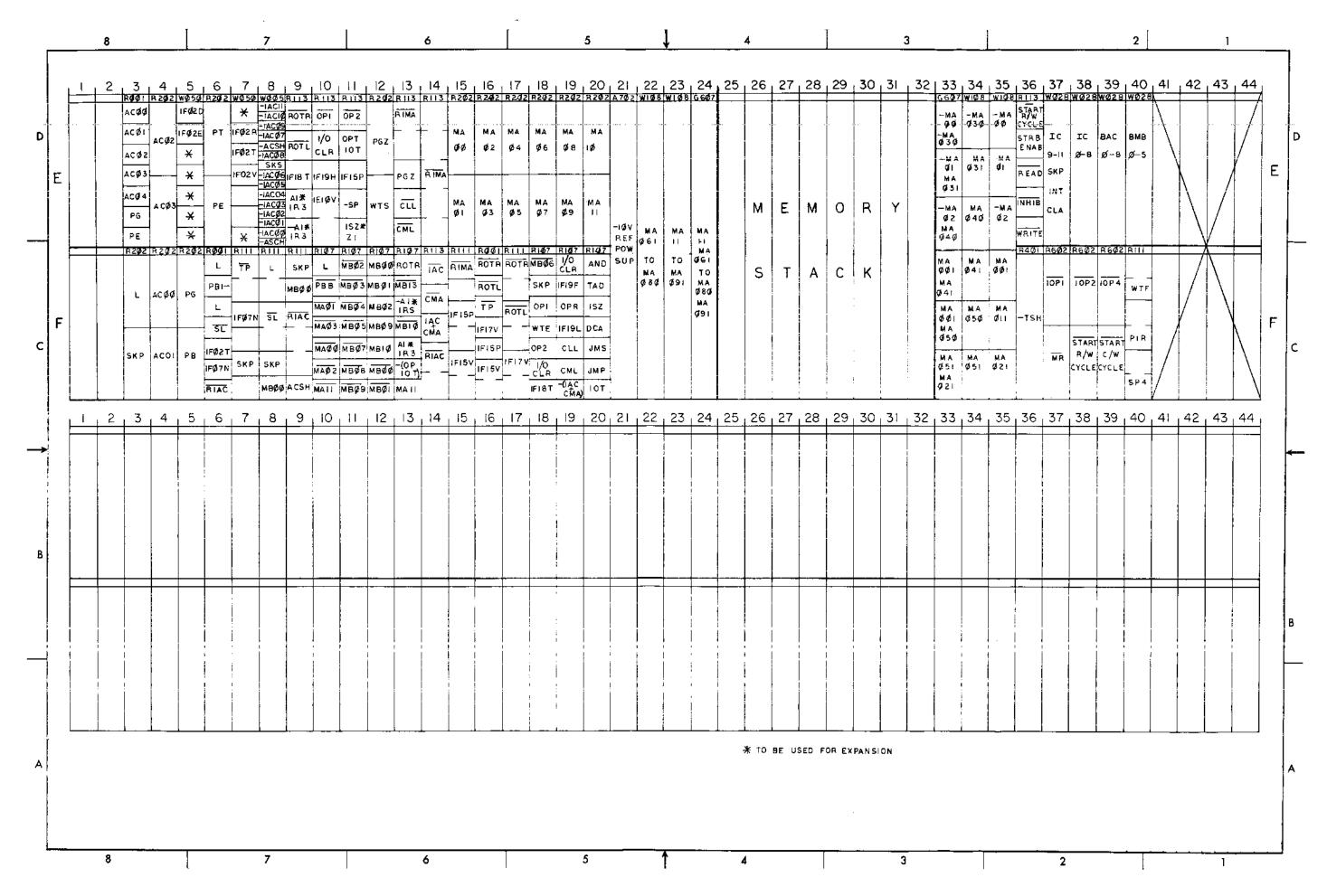

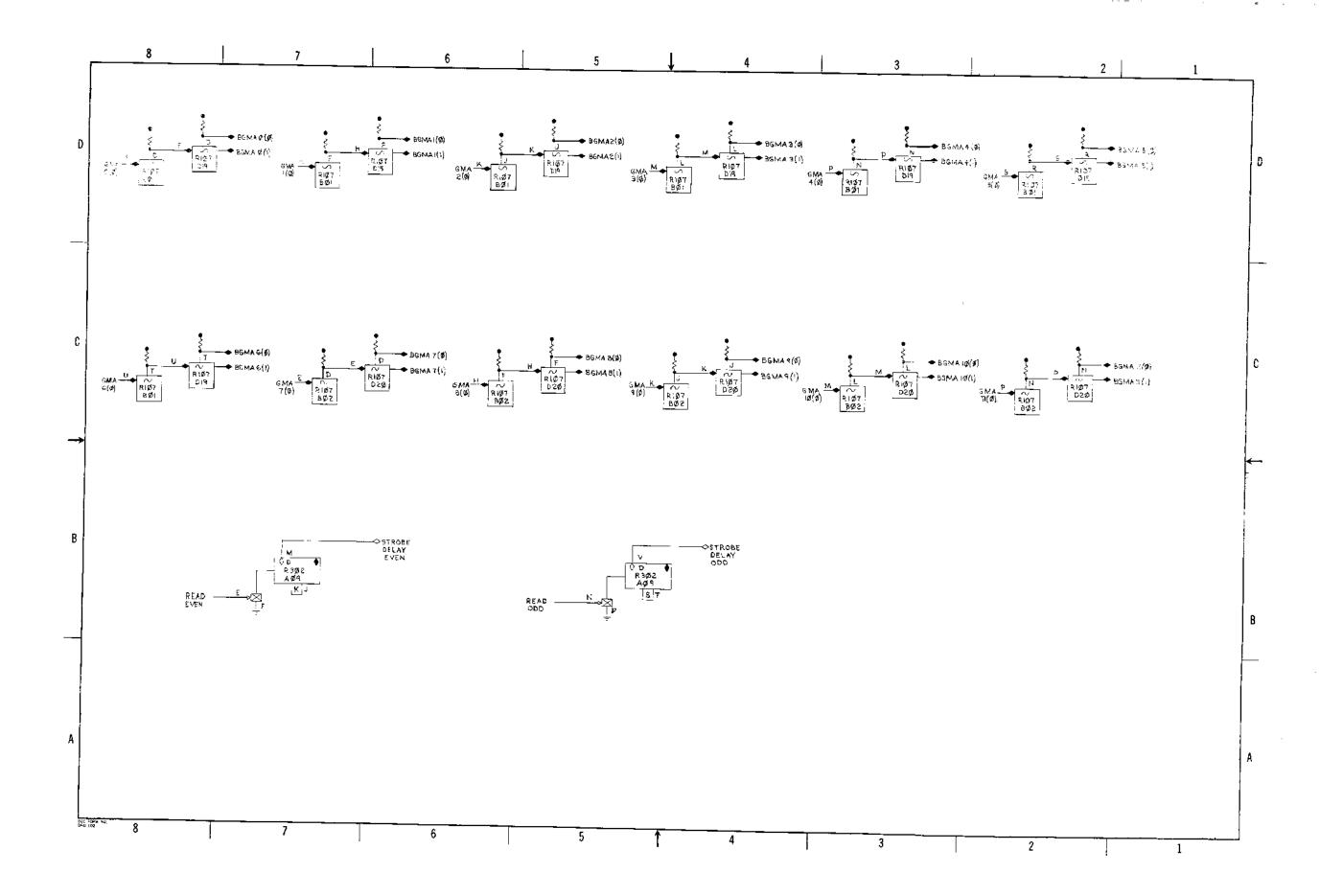

| D-MU-OMD8S-0-1 | Module Utilization (OMD8S) (2 Sheets)                  | C-7          |

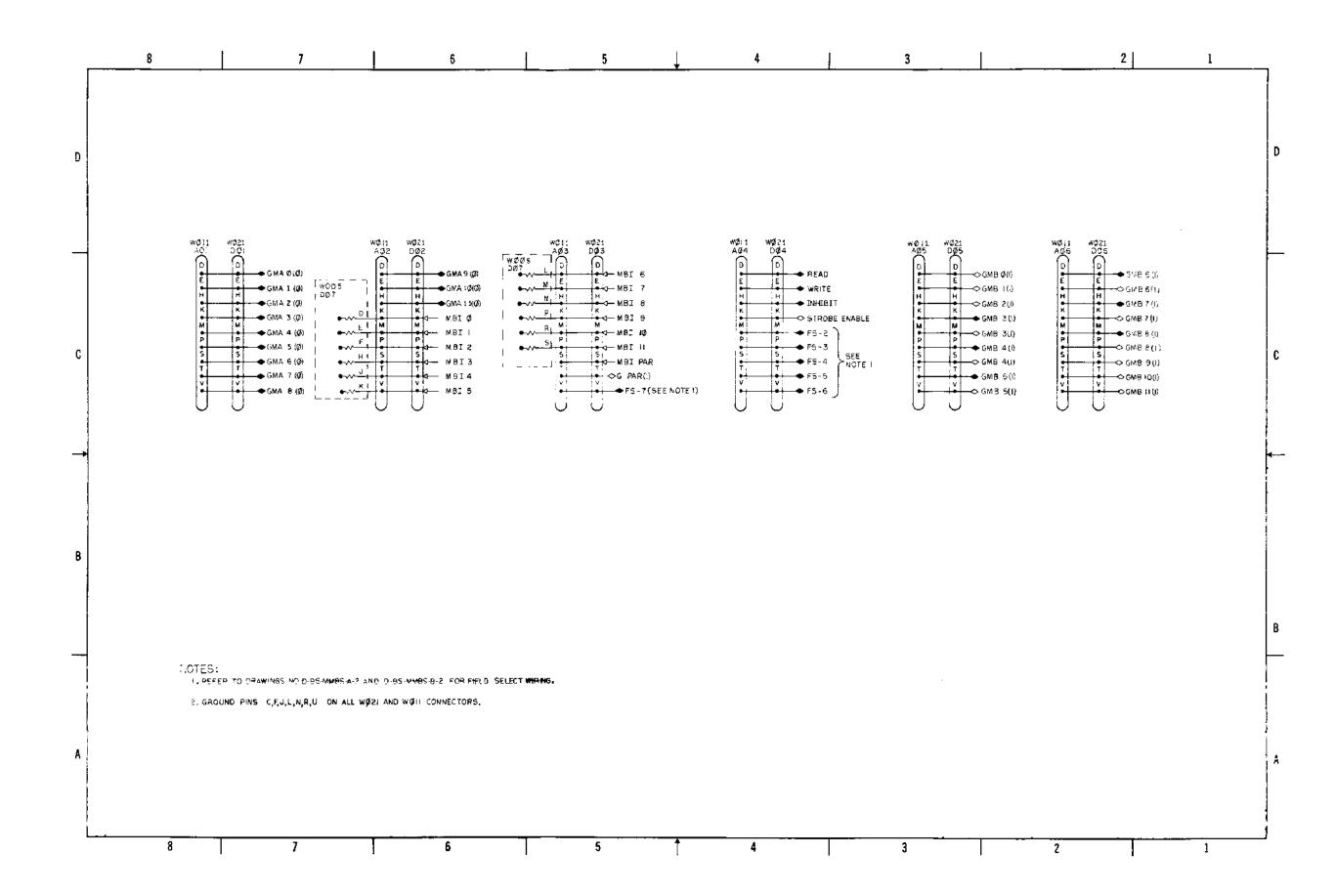

| D-IC-OMD8S-0-3 | DB8S, MC8S I/O Connectors                              | C-11         |

| D-BS-OMD8S-0-4 | OMD8S Conn and Logic in 8S (2 Sheets)                  | C-13         |

| D-BS-OMD8S-0-5 | Memory Field                                           | C-17         |

| D-BS-OMD8S-0-6 | OMD8S MA Gating                                        | C-19         |

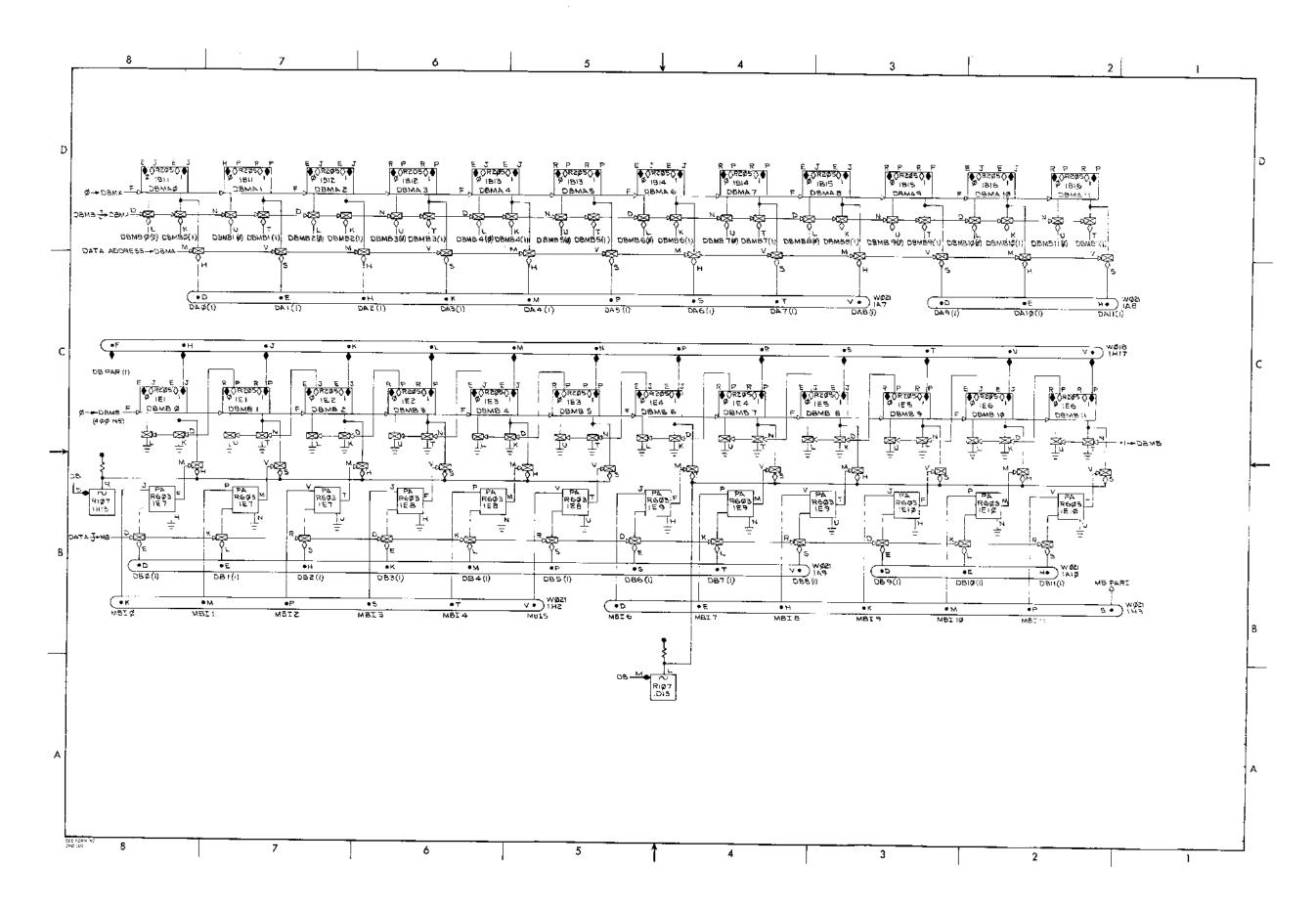

| D-BS-OMD8S-0-7 | OMD8S MB Gating                                        | C-21         |

| D-BS-OMD85-0-8 | Installation Procedure                                 | C-23         |

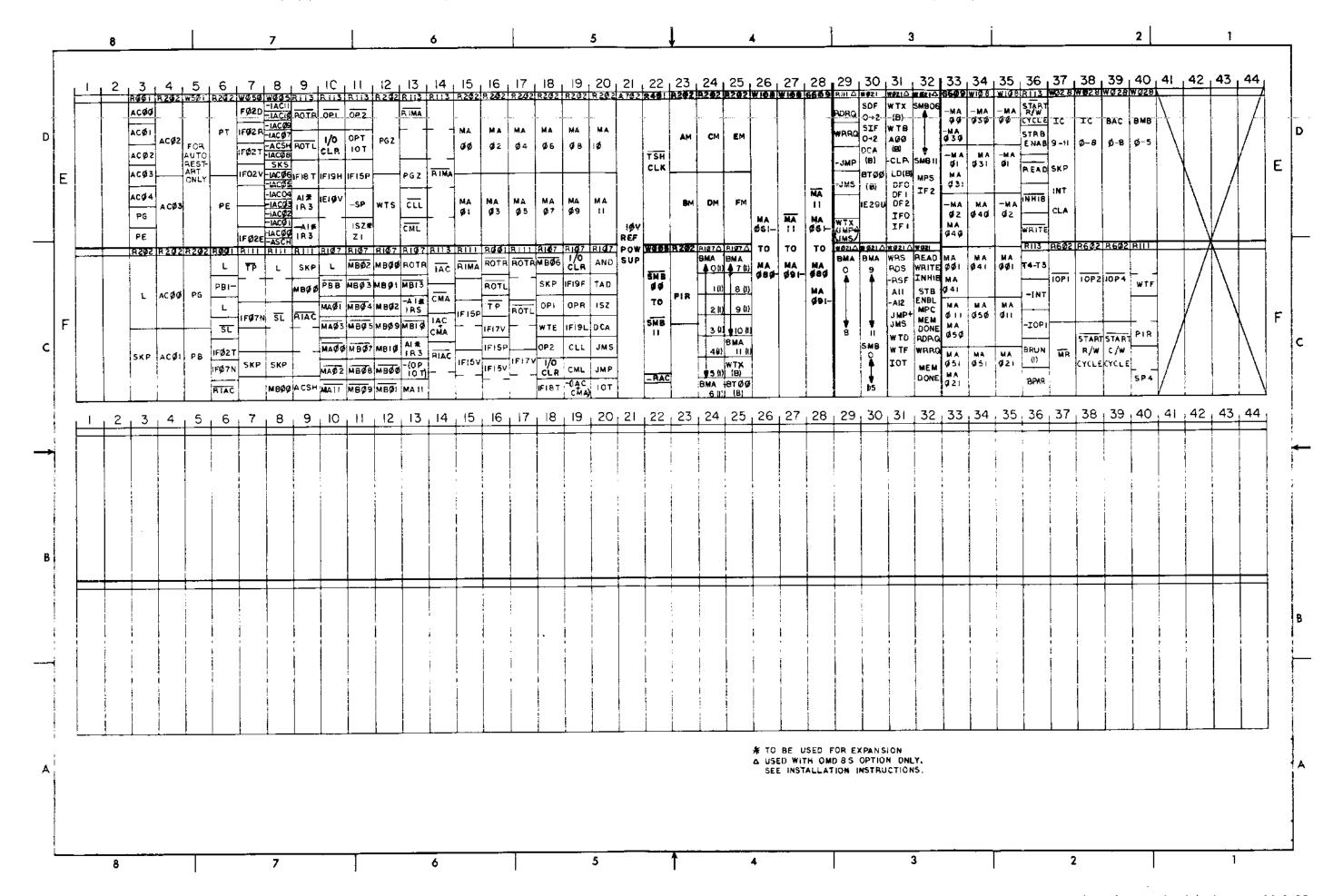

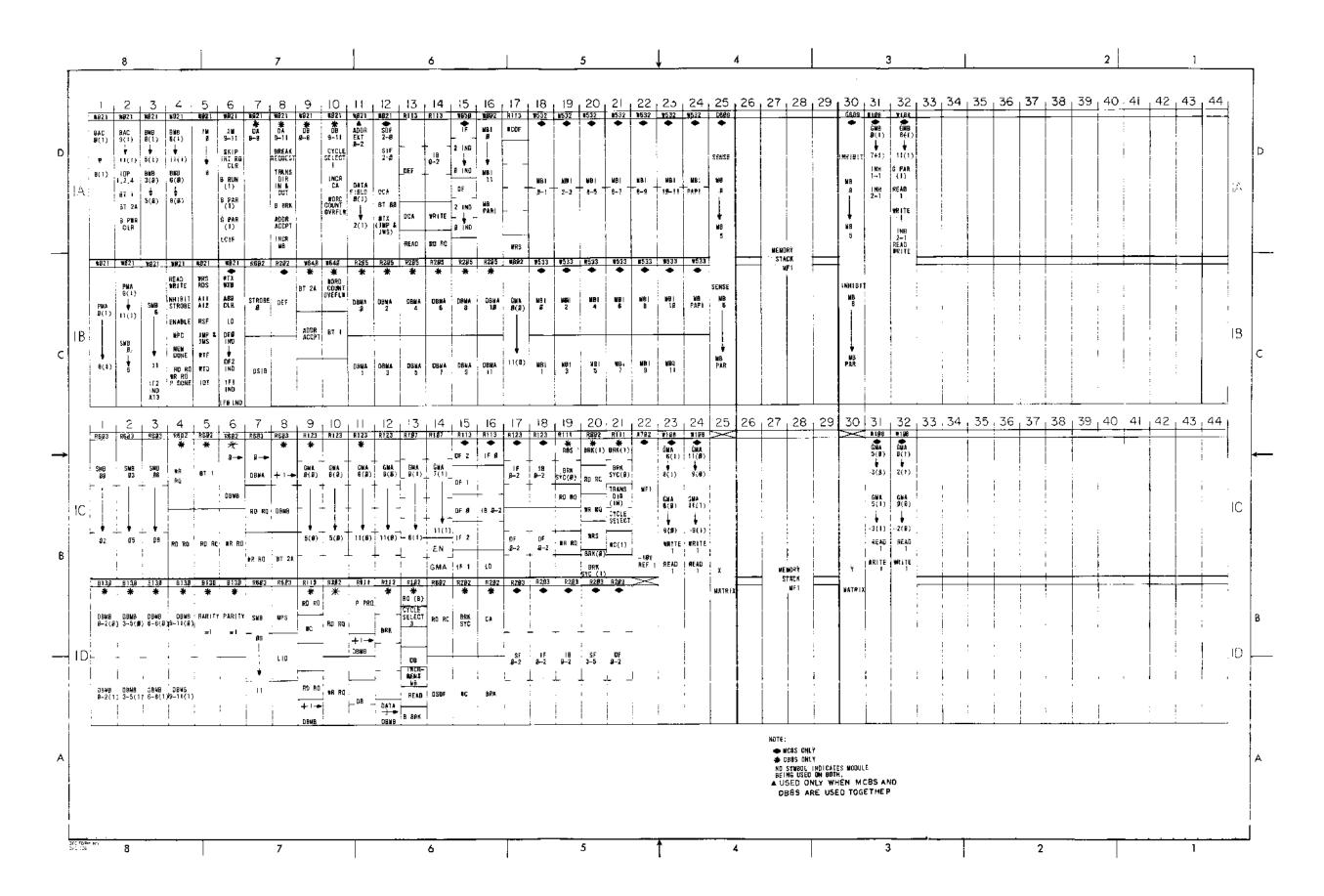

| D-BS-MC8S-0-1  | Extended Memory Control (MC8S) (3 Sheets)              | C-25         |

| D-BS-MC8S-0-2  | Memory Field 1 (MC8S)                                  | C-31         |

| D-BS-MC8S-0-4  | Flow Diagram (MC8S)                                    | C-33         |

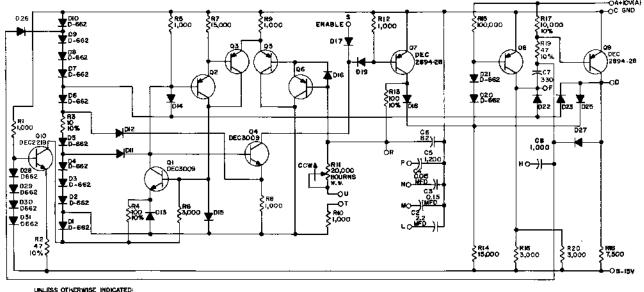

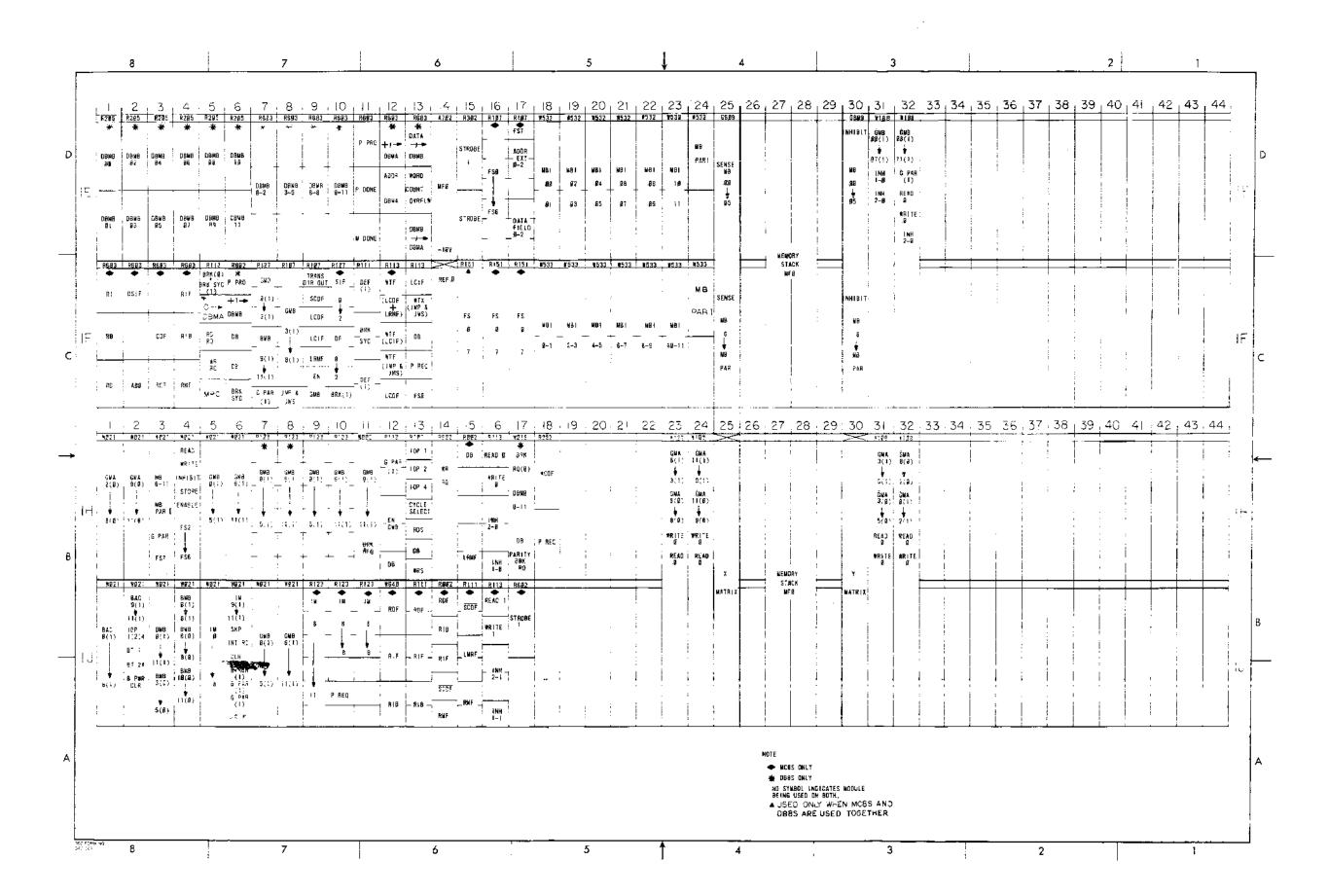

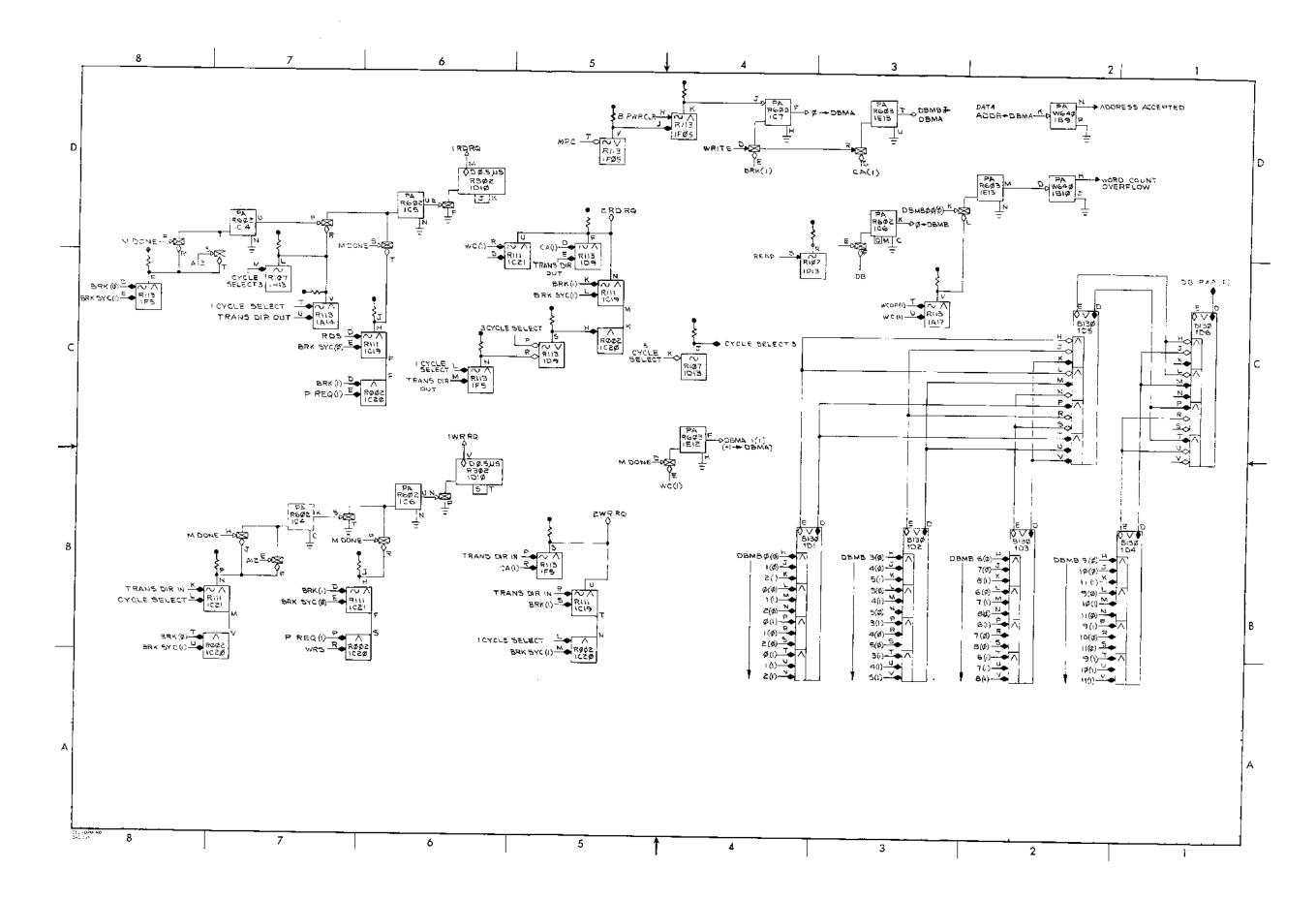

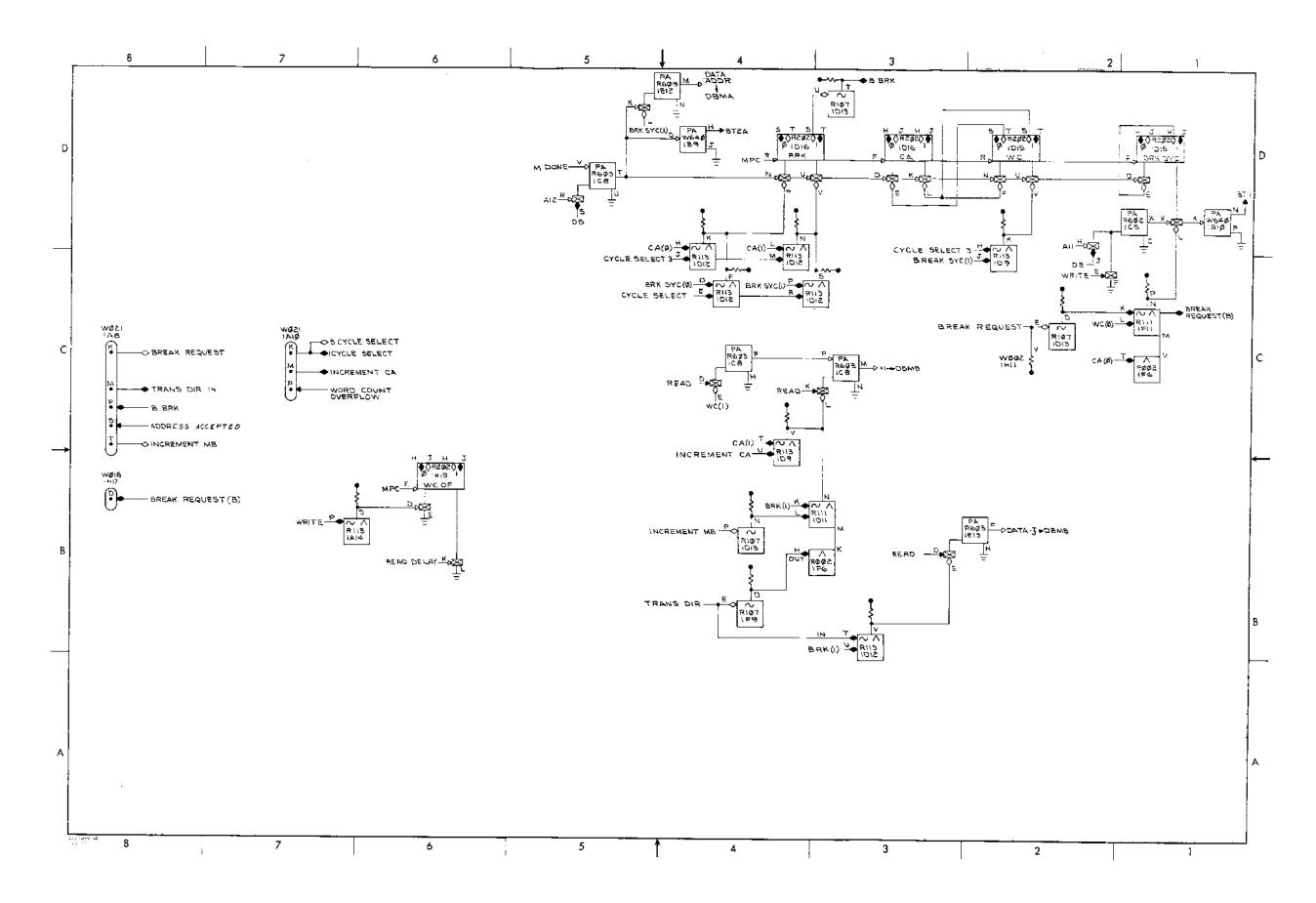

| D-BS-DB8S-0-1  | Control (DB85) (2 Sheets)                              | <b>C-</b> 35 |

| D-BS-DB8S-0-2  | MA and MB Register (DB8S)                              | C-39         |

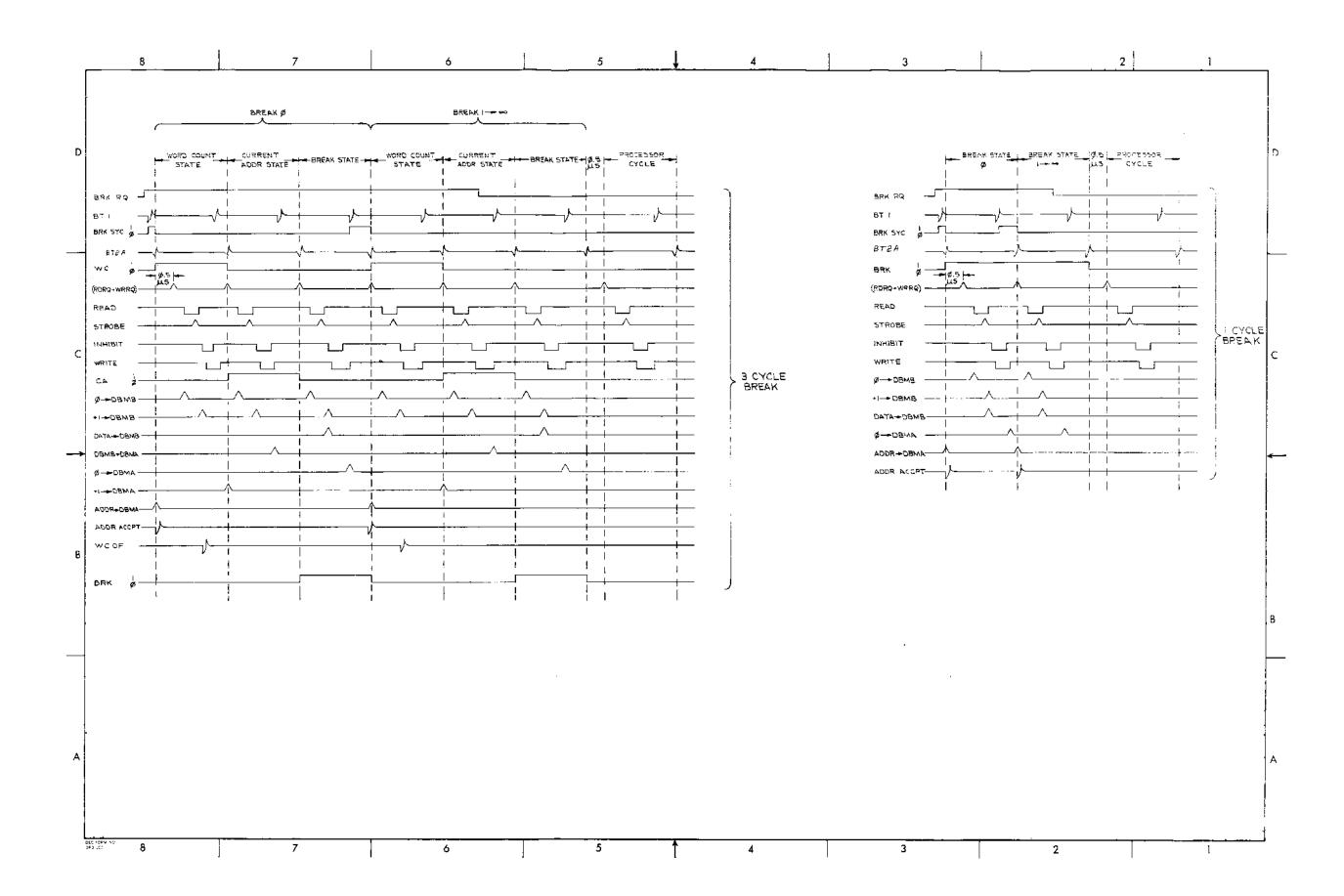

| D-TD-DB8\$-0-3 | DB8S Timing Diagram                                    | C-41         |

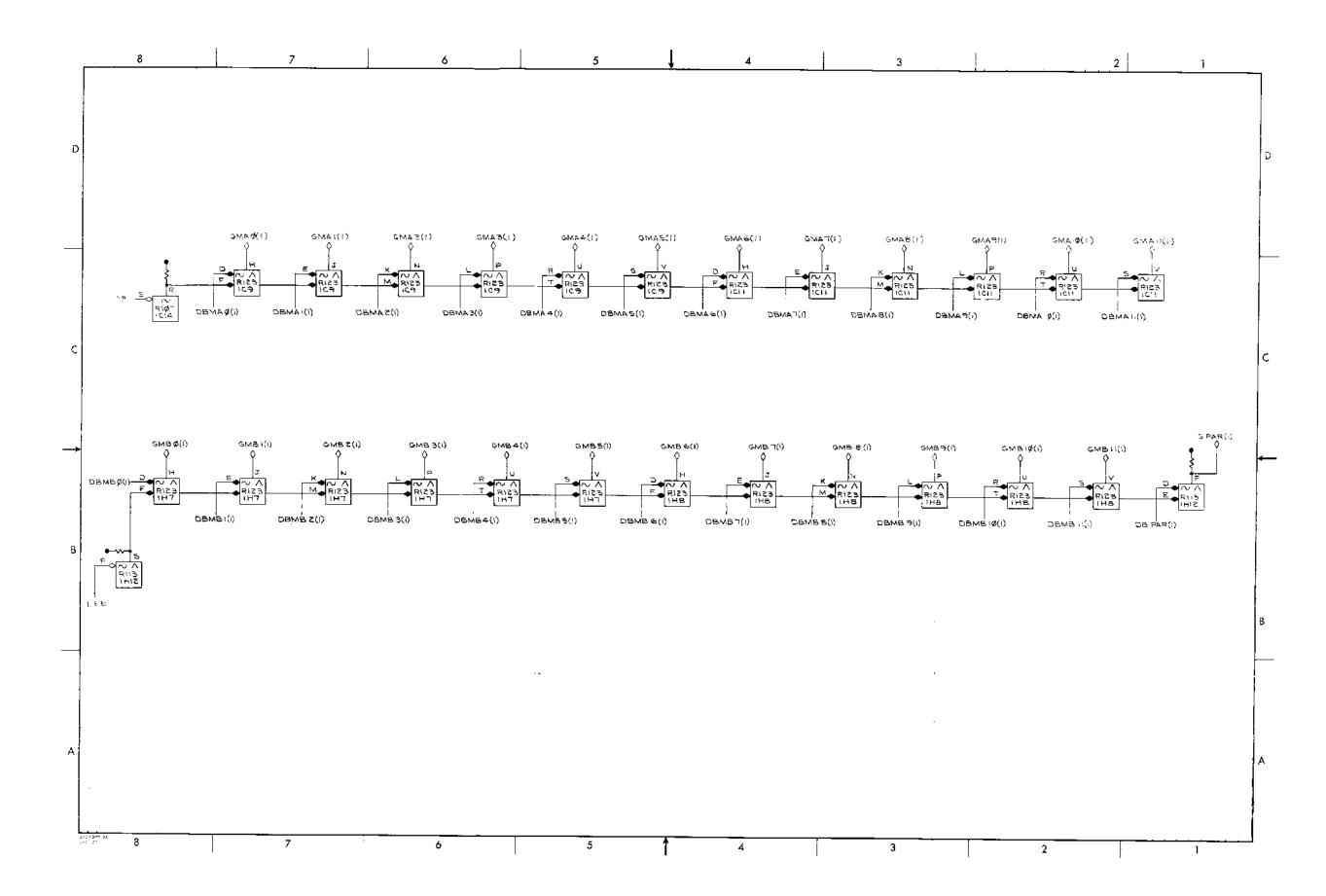

| D-BS-DB8S-0-5  | GMA and GMB Gating                                     | C-43         |

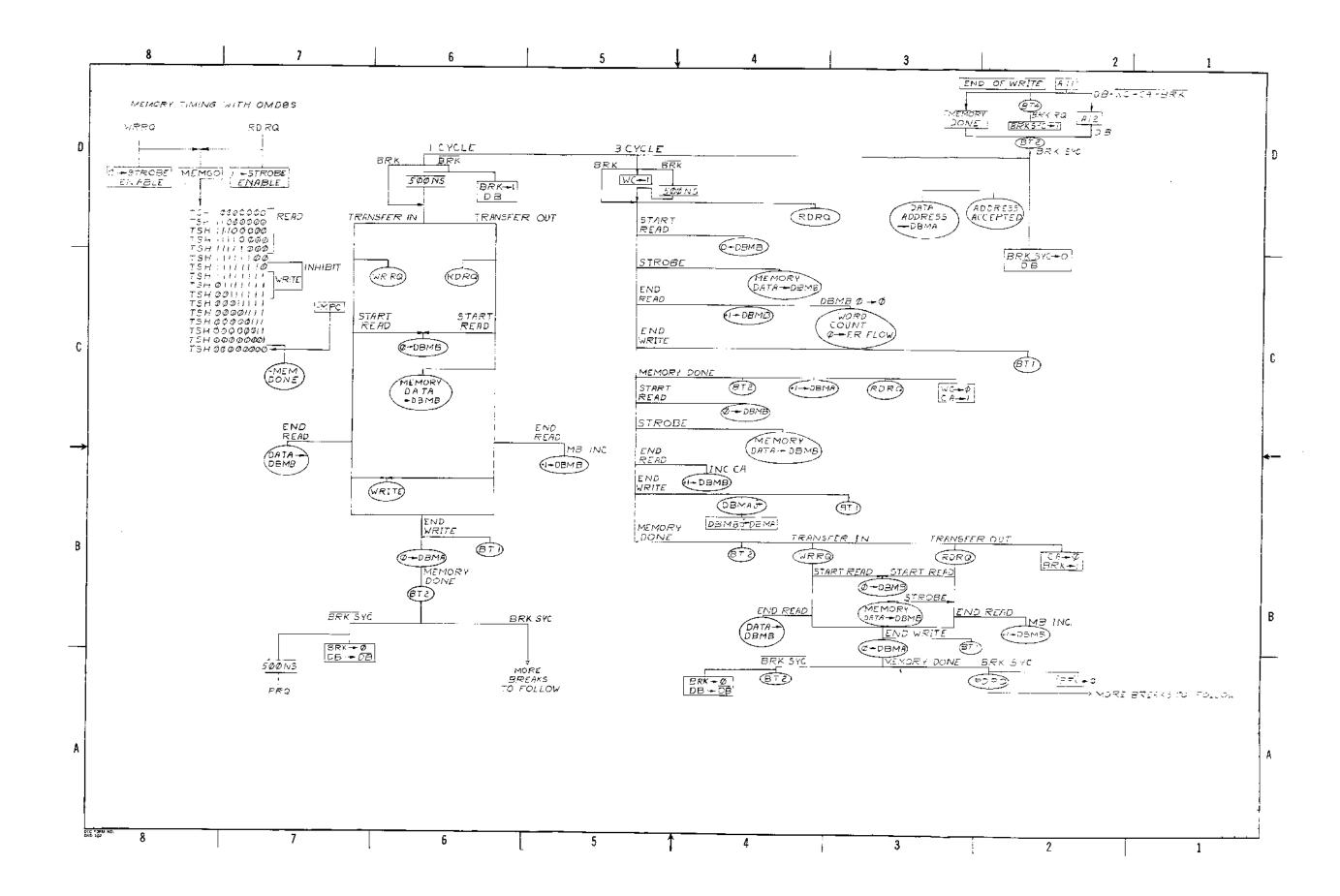

| D-FD-D88S-0-6  | Flow Diagram DB8S                                      | C-45         |

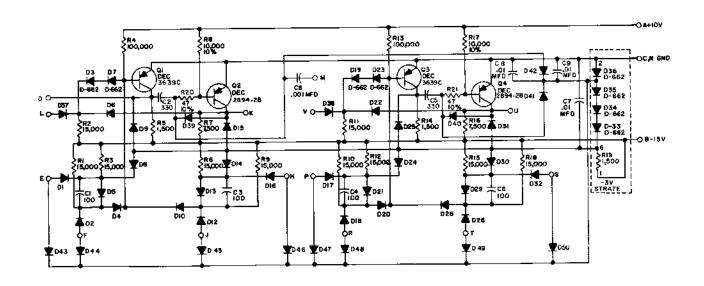

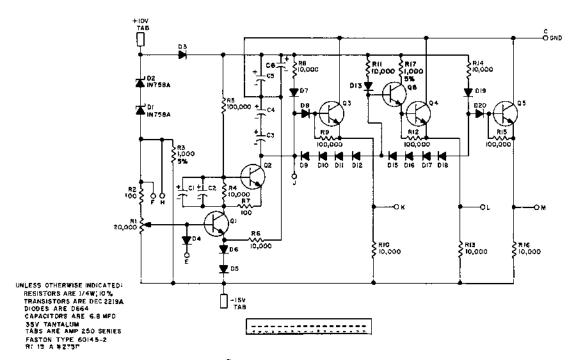

| D-BS-ME8S-0-1  | Control Logic (ME8S)                                   | C-47         |

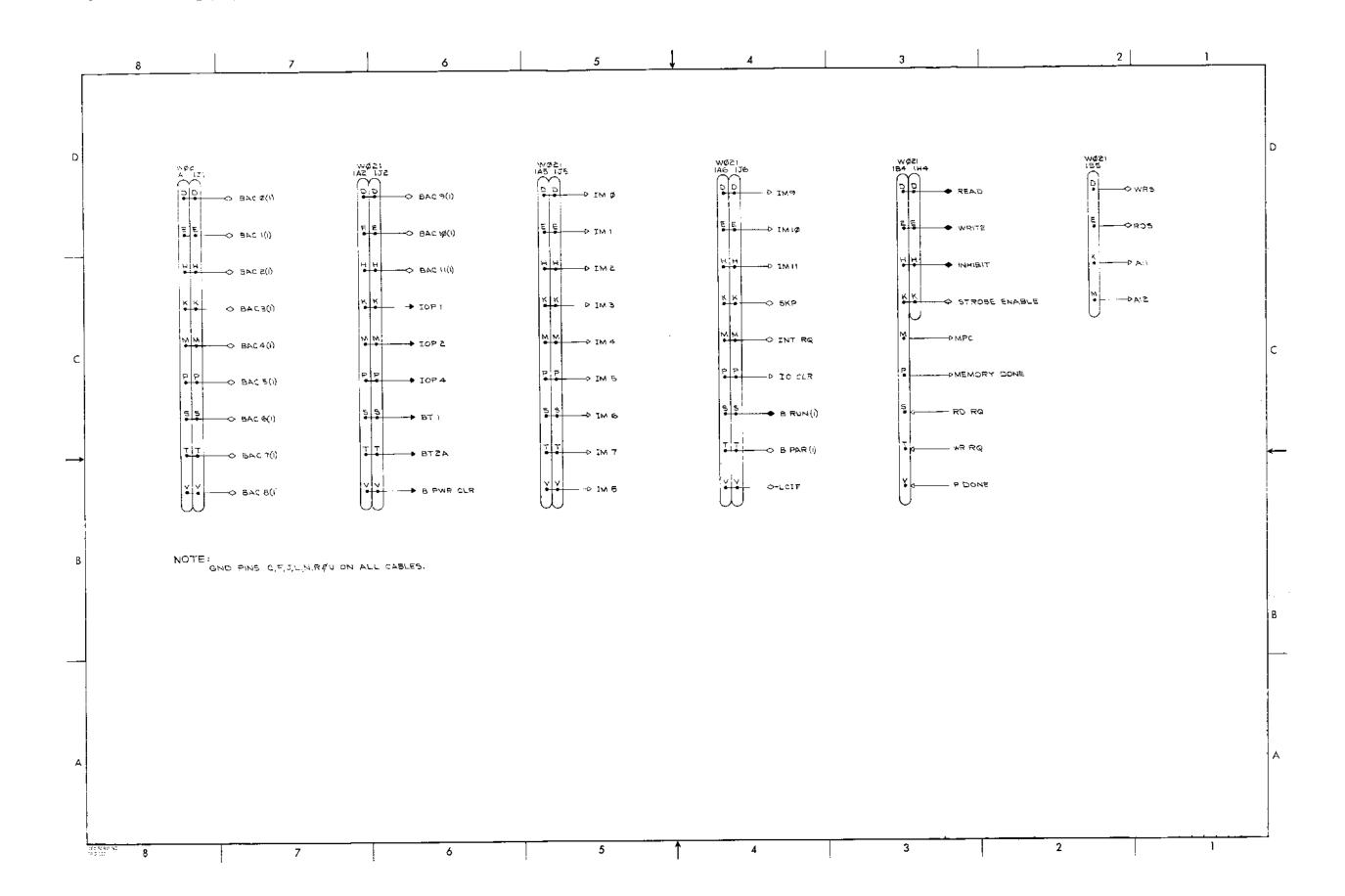

| D-IC-ME8S-0-2  | Interface Cables (ME8S)                                | C-49         |

| D-MU-ME8S-0-3  | Module Utilization                                     | C-51         |

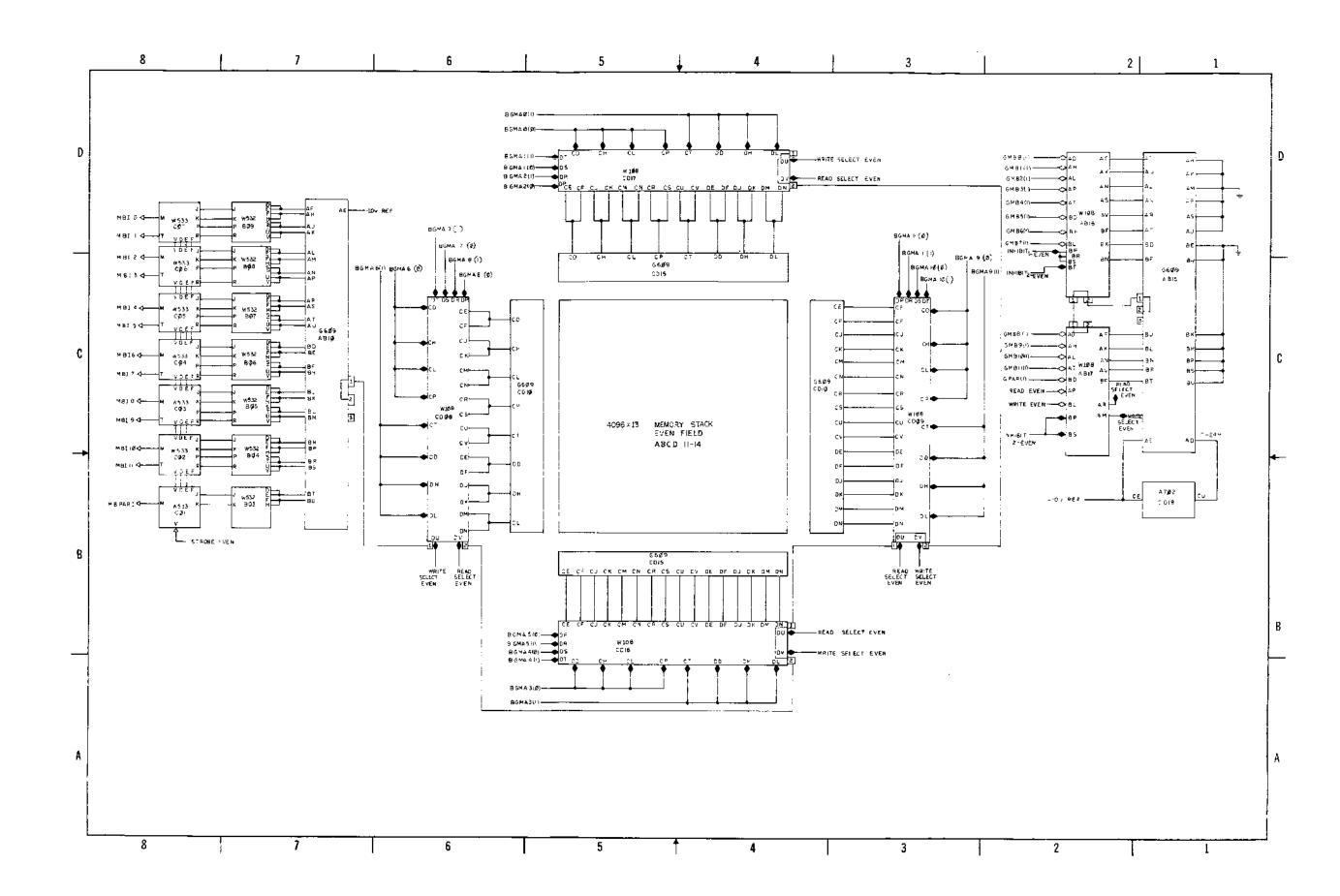

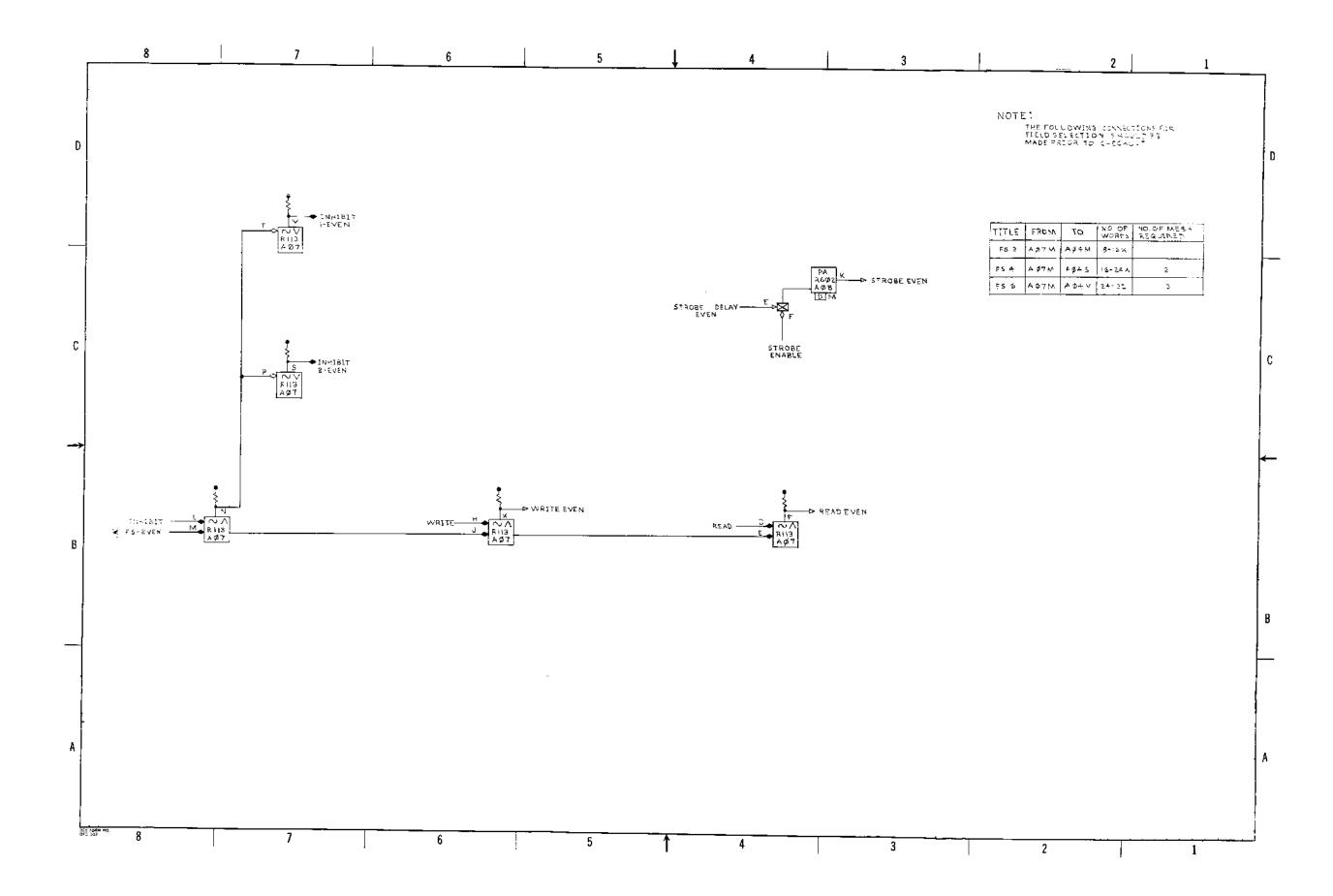

| D-BS-MM8S-A-1  | Memory Field Even (MM8S)                               | C-53         |

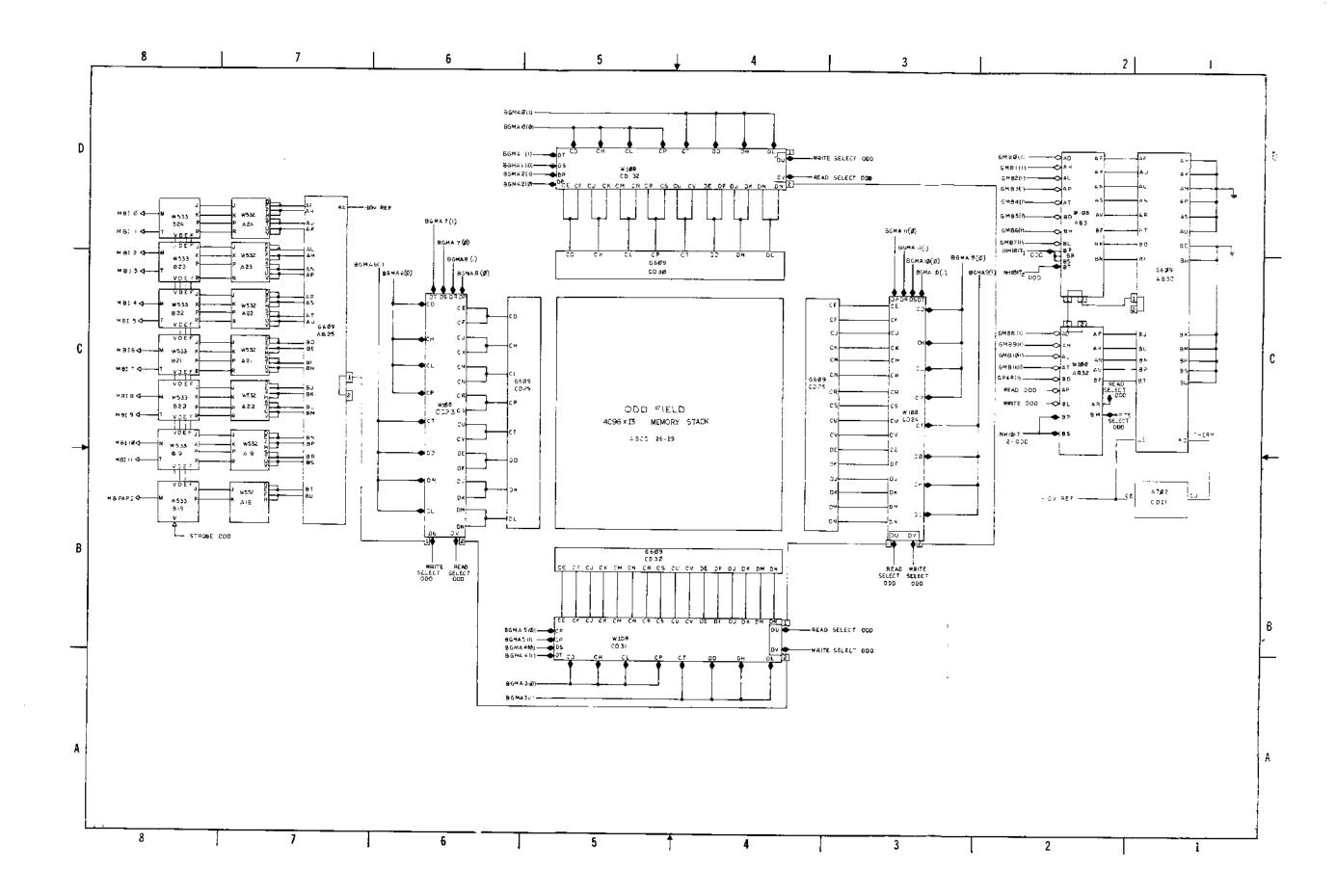

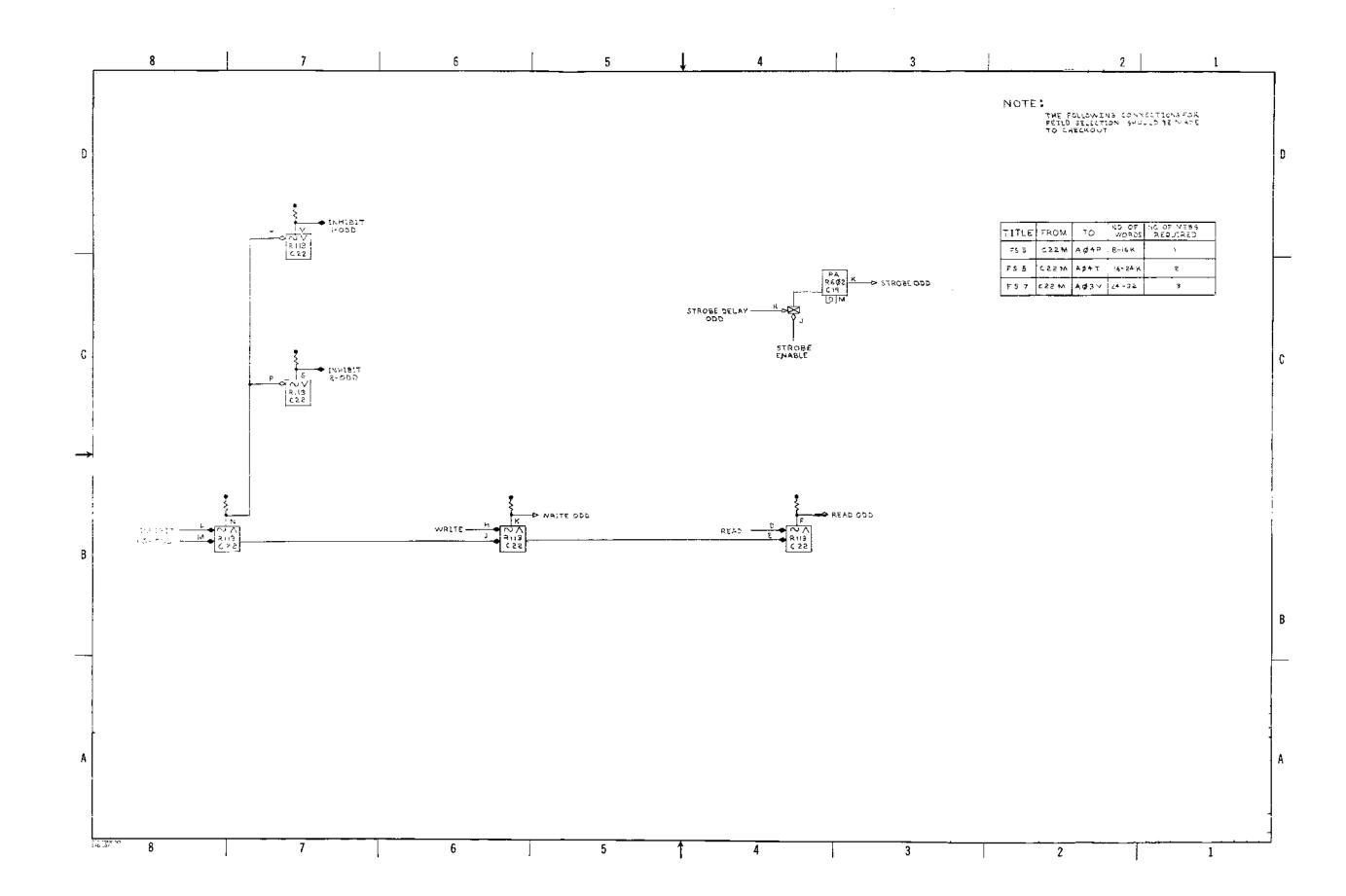

| D-BS-MM8S-B-1  | Memory Field Odd (MM8S)                                | C-55         |

| D-BS-MM8S-A-2  | Control Logic (MM8S)                                   | C-57         |

| D-BS-MM8S-B-2  | Control Logic (MM8S)                                   | C-59         |

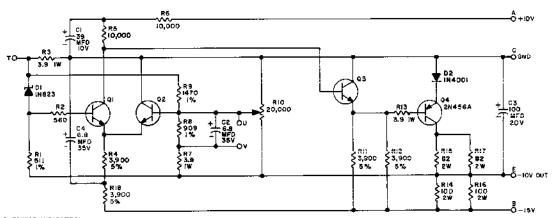

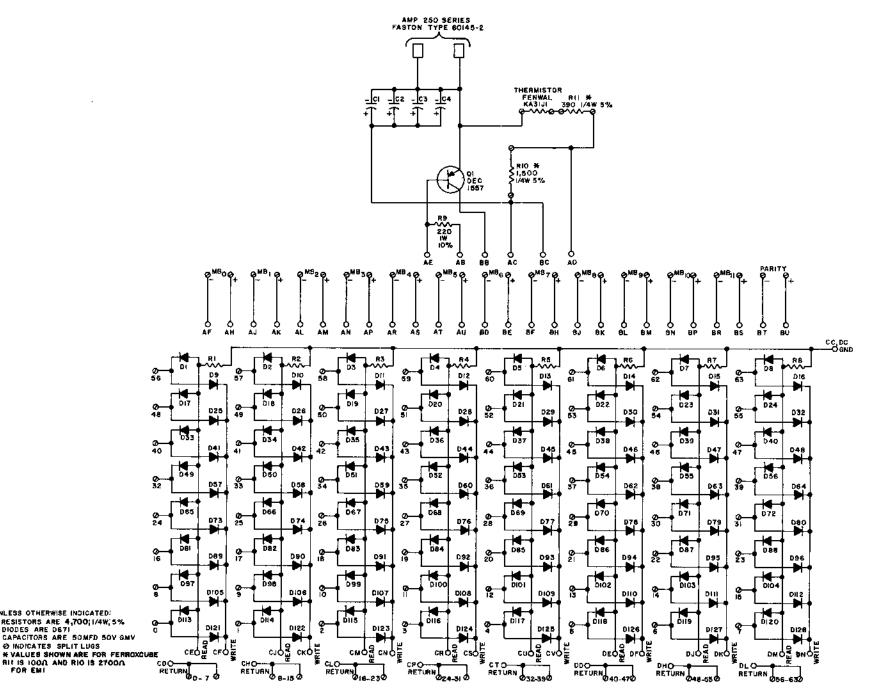

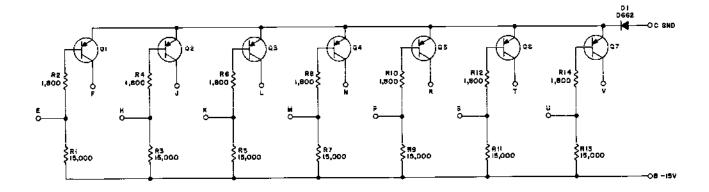

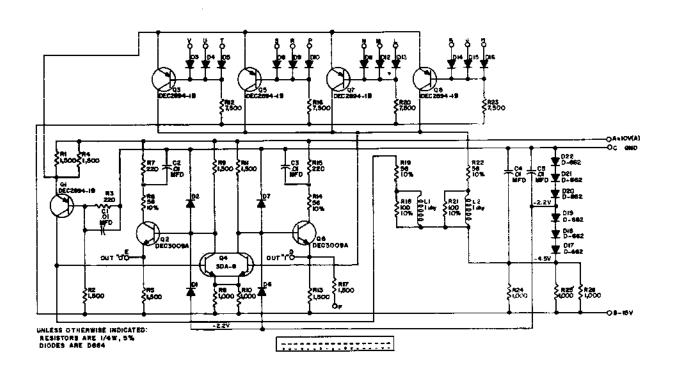

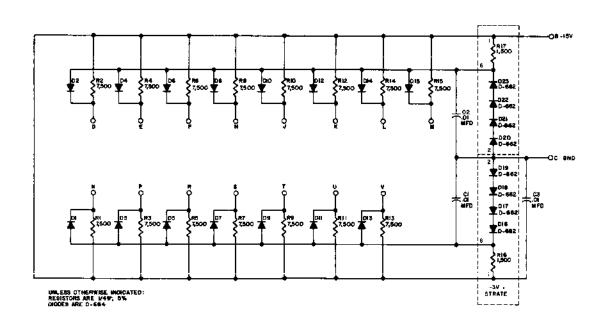

| B-CS-B130      | Three-Bit Parity Circuit                               | C-61         |

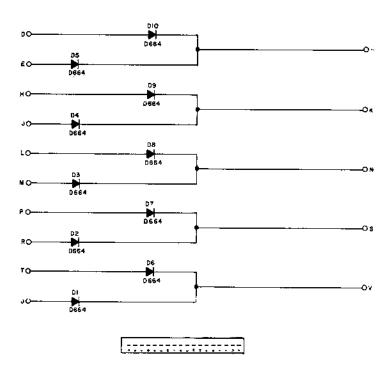

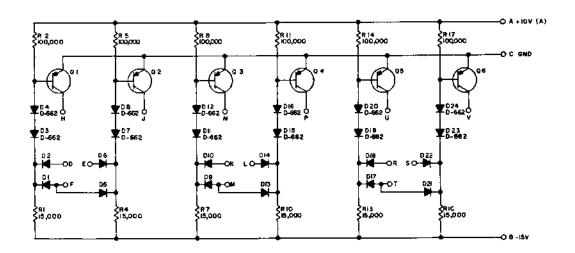

| B-CS-R123-0-1  | Diode Gate R123                                        | C-61         |

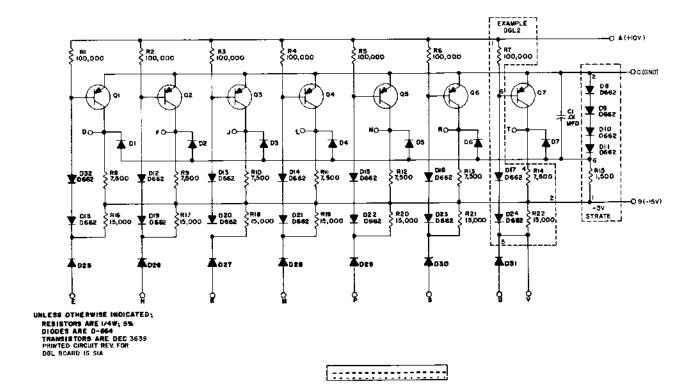

| B-CS-R203      | Triple Flip-Flop R203                                  | C-62         |

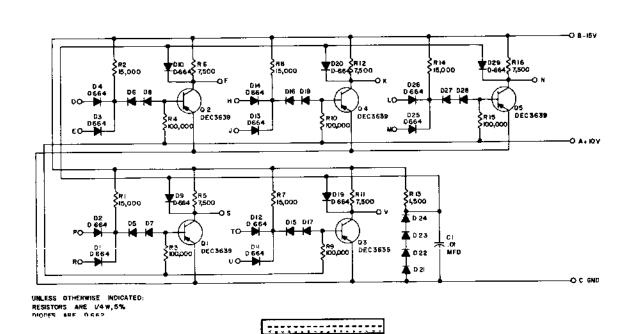

| B-CS-R205      | Dual Flip-Flop R205                                    | C-62         |

| B-CS-R603      | Pulse Amplifier R603                                   | C-63         |

| B-CS-W002-0-1  | Clamp Loads W002                                       | C-63         |

| B-CS-W018-0-1  | Indicator Connector                                    | C-64         |

| B-CS-W021      | Signal Cable Connector                                 | C-64         |

| B-CS-W533-0-1  | Rectifying Slicer                                      | C-65         |

| B-CS-W640      | Pulse Amplifier W640                                   | C-65         |

|                |                                                        |              |

#### PREFACE

This instruction manual is intended to aid personnel in the operation and maintenance of the PDP-8/S computer. The manual also discusses the operation of the Teletype ASR-33 and describes its control unit, which is of DEC manufacture, but a separate manual is furnished for the device itself.

Chapter 1 lists the operating specifications of the system and describes its physical and electrical characteristics. Chapter 2 describes the logical organization of the computer, discusses the number system and instruction formats used by it, explains the use of all controls and indicators on the operator panel, and explains the operation of the ASR-33. Chapter 3 presents a complete detailed description of the system logic, including a discussion of the symbols and notation used in the logic drawings and flow charts. Chapter 4 contains information useful in maintaining the system, including a discussion of maintenance programs, memory alignment and troubleshooting procedures, and in-out bus specifications.

Chapter 5 contains equivalent information on the Data Break (DB85) and Memory Expansion (MC85, ME85, MM85) options and the additional logic common to both (OMD85).

Appendix A contains engineering drawings, logic drawings, flow charts, and circuit schematics for the basic PDP-8S and ASR-33 control.

Appendix B contains engineering drawings, logic drawings, flow charts, circuit schematics, and a glossary for the Data Break and Memory Expansion Options.

### CHAPTER 1 INTRODUCTION

The PDP-8/S is a small-scale, general-purpose digital computer designed for use as an independent information-handling facility in a larger computer system, or as the control element in a complex processing system. The basic computer consists of a central processor and a memory, and has a Teletype Model 33 Automatic Send/Receive set for input-output. The processor performs all arithmetic, logical and system control functions. Memory operation is based on a read-write cycle, one cycle being executed each time access is requested by the processor.

Interface circuits for the in-out bus allows connection to a variety of peripheral equipment. Every device must detect its own selection code and provide any necessary input gating. In the standard computer all transfers over the in-out bus are under program control, but peripheral equipment can interrupt the program. Optional equipment allows direct data access to the memory for high speed devices such as disc memory.

In the processor all operations on words are serial; the computer uses parallel transfers only for communication between the processor and the memory, the console, or the in-out equipment over the in-out bus. Information handled by processor and memory has the following characteristics.

#### Word Length

Processor: 12 bits

Memory: 13 bits including parity bit

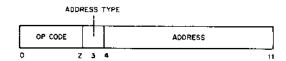

Instruction Format

Memory Reference: Instruction code, 3 bits

Indirect, 1 bit

Memory address, 8 bits

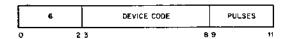

Operate Group: Instruction code, 12 bits

Input-Output: Instruction code, 12 bits including

6 bit device code

Internal Number System Binary

Negative Representation Two's complement

Number Format Sign, 1 bit; magnitude, 11 bits

All timing is synchronous, but processor and memory operate on separate clocks, which cannot run simultaneously. Thus every time that the processor requests memory access its clock stops; when the memory cycle is complete, the processor restarts. Each processor cycle of 10.5 µs is one word time, the time required to process one word serially. The PDP-8/S uses two types of random access magnetic

core memory having cycle times of 6.3 and 6.5  $\mu$ s. Instruction execution times differ depending upon the number of processor and memory cycle required, and upon whether a given instruction uses indirect addressing and autoindexing.

The processor must set up all transfers of data to and from the peripheral equipment; but since a device can signal the processor by means of a program interrupt when it requires services, no processor time need be lost in waiting, and processor and peripheral equipment can operate in parallel. The only I/O device supplied with the standard computer is the Teletype Model 33 ASR but it includes keyboard, printer, tape reader and punch. It handles data at the rate of ten 8-bit characters per second.

#### 1.1 PHYSICAL CHARACTERISTICS

The table model is housed in a cabinet but the computer is also available for mounting in a standard 19-in. rack. The computer contains six logic mounting panels, lettered A to F from right to left when viewing it from the front. Each mounting panel can hold forty DEC Flip-Chip plug-in modules numbered from front to back.

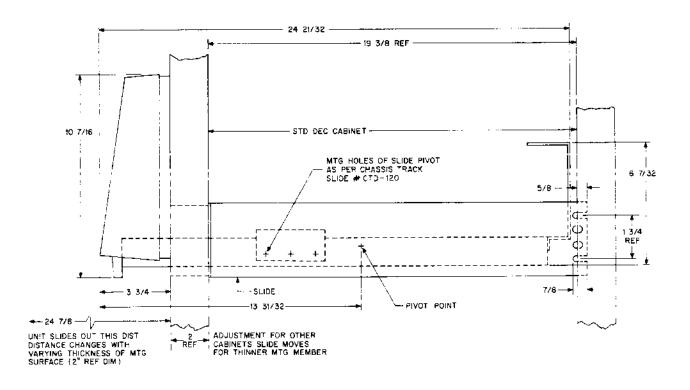

The rack-mountable model requires 10-1/2 in. of vertical space in a 19-in. rack. It protrudes 3-3/4 in. at the frant of the rack, and slides out 25 in. Physical dimensions of both models are shown in Figures 1-1 through 1-5. The table model weighs 84 lb, and the rack model weighs 200 lb including power equipment. The Teletype ASR 33 has the following dimensions.

Height:

45 in.

Width:

22 In.

Depth:

19 in.

Weight:

100 lb

Intake fans at the back of the table model cool the logic modules by blowing air between them. A PDP-8/S shipped mounted in a DEC rack has three muffin fans on the left side, but the user must supply adequate ventilation for a computer shipped unmounted.

It is recommended that the ambient temperature at the installation be maintained between  $70^{\circ}$  and  $85^{\circ}$ F, but it can vary between  $32^{\circ}$  and  $130^{\circ}$ F without adverse effect. Although all exposed surfaces are treated to prevent corrosion, exposure to extreme humidity for long periods of time should be avoided.

#### 1.2 ELECTRICAL CHARACTERISTICS

The computer uses standard line power at  $115\pm17$  Vac, 60 cycle ( $\pm2\%$ ), single phase. The rack model uses a standard 728 power supply and a control through which the power switch on the front panel switches as to a pair of receptacles on the computer backplate. These receptacles are for the power supply and the fans. To switch as to other supplies or devices from the computer front panel

requires the use of a repeater relay slaved to this switched ac. The power cable uses a Hubbell Twist-Lok connector; both cable and connector are rated at 20 or 30 amp depending upon total system requirements.

The table model has an equivalent power supply mounted on the inside rear of the cabinet, and both it and the fans receive ac through the front panel power switch and a pair of circuit breakers. The power cable uses a standard ac plug with ground and is rated at 15 amp. The teletype must be powered separately.

Current consumption is as follows.

|                | Processor | <u>Teletype</u>                 |

|----------------|-----------|---------------------------------|

| Line current   | 3 amp     | 2.6 amp<br>Turn on surge, 7 amp |

| Dissipation    | 100W      | 140W                            |

| Logic voltages |           |                                 |

| +10V           | 0.6 amp   | 1.2 amp                         |

| -1 <i>5</i> V  | 5.5 amp   | 0.5 amp                         |

The do voltages required by the logic are ±10V and -15V. All logic is solid state; transistors and diodes operate on static logic levels of 0 and -3Vdc (tolerances are 0V to -0.3V and -3.2V to -3.9V). Most logic modules include an internal supply to derive the negative logic level from the -15V input. PDP-8/S logic uses pulse timing almost exclusively. Pulse amplitude from a pulse generating source is ±3V from -3V with the same tolerances as levels. Pulses at inverter outputs may be from ground to -3V or vice versa. Pulse widths may be 100 ns or 400 ns depending upon application. Occasionally, an input may be triggered by a positive level transion of 60 ns or less instead of a pulse. Driving voltages for the core memory are nominally -10V to ground and -15V to ground. The statistics given here apply to all modules used in the equipment described in this manual except the transmitter and receiver modules for the teletype; the special voltage requirements for these modules are discussed with the teletype logic.

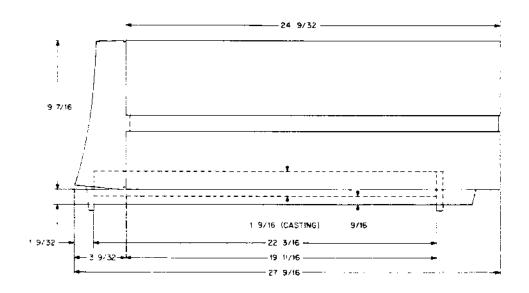

Figure 1-1 Dimensions, Table Model (Front View)

Figure 1-2 Dimensions, Table Model (Side View)

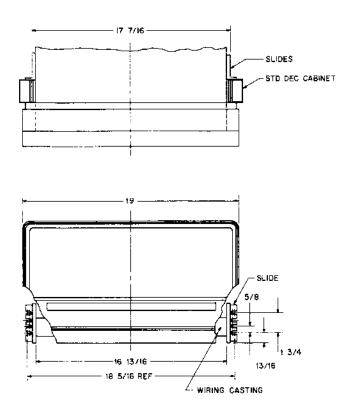

Figure 1-3 Dimensions, PDP-8/S Mounted in Standard DEC Rack

Figure 1-4 Dimensions, PDP-8/S Mounted in Standard DEC Rack

Figure 1-5 Typical Rack Mounted PDP-8/S with Recommended Option Mounting

#### CHAPTER 2 SYSTEM OPERATION

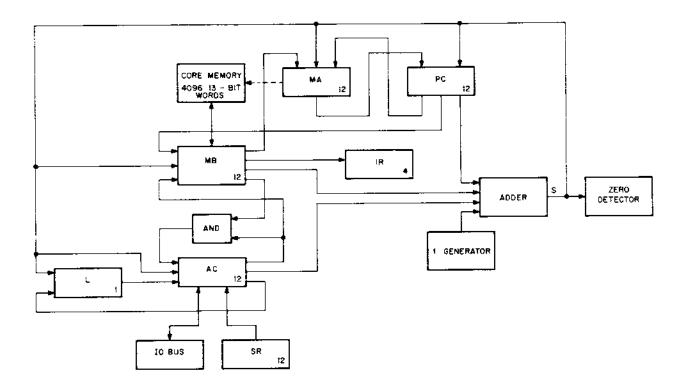

Figure 2-1 shows the registers and data flow in the PDP-8/S. The processor is the control unit for the entire system: it governs all peripheral in-out equipment, sequences the program, and performs all arithmetic and logical operations.

Figure 2-1 PDP-8/S Data Flow

The processor handles words of 12 bits, which are stored in a memory with a capacity of 4096 words. Storage in memory is actually in the form of 13-bit words, the extra bit being an even parity bit for the word. The bits of a word are numbered 0 through 11, left to right, as are the flip-flops in the registers that handle the words. Words are used either as computer instruction in the program, as addresses, or as operands, that is, data for the program.

The processor performs a program by executing instructions retrieved from consecutive memory locations, as counted by the program counter (PC), although the program may after its own sequence by changing the address in PC, either by indexing (incrementing it by one) an extra time in a test skip instruction or by replacing its contents with the value specified by a jump instruction. To gain access to memory for retrieval or storage, the processor requests a memory cycle and supplies an address from the memory address register (MA). All transfers of data between processor and memory are made through the memory buffer (MB). When a word is retrieved at MB, as an instruction, its left four bits pass to the instruction register (IR), which is decoded to govern the actual execution of the instruction. In a memory reference instruction, the rest of the word in MB supplies address information to MA; otherwise the rest of the word is decoded directly from MB to assist in instruction execution.

The heart of the processor is the memory buffer MB, the accumulator (AC), and a 1-bit serial adder. All transfers between processor and peripheral equipment are made via AC, which is connected to the in-out bus. The accumulator is also connected to the switch register (SR) through which the operator can send data and addresses into the computer from the console. The only parallel transfers that occur in the system are those between MB and memory, between AC and the I/O bus, and from SR to AC. All other operations in the processor are serial: all registers are shift registers, and information is transferred from one register to another by shifting both registers to the right, so that information leaves one register at the right (LSB) and enters the other from the left (MSB). Although not shown in Figure 2-1, the processor can recirculate any of the four main registers whenever its contents must be saved while being transferred.

To produce the logical AND function, the contents of MB and AC are shifted through a simple AND gate, with the result appearing in AC. All other operations on words are performed through the serial adder. The contents of MB and AC are added one bit at a time as the sum is shifted into AC. The adder is also used to increment AC, MB, or PC, to complement AC, and even to detect zero contents in MB or AC for a skip test.

Associated with AC is a 1-bit register, the link (L). The link serves as an overflow flag in addition and when AC is incremented. AC and L can be rotated together, to the left or right, as a single 13-bit register (left rotation is produced by a shortened right shift). The program can also use L to generate products and quotients one bit at a time.

Besides the registers that enter into the regular execution of the program and its instructions, the processor also contains a program interrupt system that allows peripheral devices, a memory parity error or a power failure to interrupt normal program flow. When such an interruption occurs and the interrupt is on (ION), the processor stores the current contents of PC (the address of the next instruction in the program) in location 0000, and executes the instruction in location 0001.

Timing for all operations in processor and memory is supplied by two clocks. Each serial processing of a word is performed in one word time under control of the processor clock. When memory access is required, the processor stops its own clock and triggers a memory cycle, which is executed under control of the memory clock. At the completion of the memory cycle the memory clock stops, and the processor clock restarts to execute another word time.

#### 2.1 PROGRAMMING

The program is a set of instructions used to perform some task and is stored in memory. Each word in memory is identified by an address, 0000-7777 octal. To execute a program, the computer normally retrieves instructions from sequentially increasing locations, but the instructions, themselves, can alter program flow and cause the computer to continue sequential operation from some other location. Table 2-1 is an instruction index.

Table 2-1.

Instruction Index

| Mnemonic | Meaning                              | Octal Code       |

|----------|--------------------------------------|------------------|

| AND      | Logical AND                          | 0xxx             |

| TAD      | Twos Add                             | lxxx             |

| ISZ      | Increment and Skip if Zero           | 2×××             |

| DCA      | Deposit and Clear Accumulator        | Зххх             |

| JMS      | Jump to Subroutine                   | 4xxx             |

| JMP      | Jump                                 | 5xxx             |

| IOT      | In-out Transfer                      | 6xxx             |

| OPR      | Operate                              | 7 <sub>xxx</sub> |

|          | Operate Group                        |                  |

| NOP      | No Operation                         | 7000             |

| IAC      | Increment Accumulator                | 7001             |

| RAL      | Rotate Accumulator Left              | 7004             |

| RTL      | Rotate Two Left                      | 7006             |

| RAR      | Rotate Accumulator Right             | 7010             |

| RTR      | Rotate Two Right                     | 7012             |

| CML      | Complement Link                      | 7020             |

| CMA      | Complement Accumulator               | 7040             |

| CIA      | Complement and Increment Accumulator | 7041             |

| CLL      | Clear Link                           | 7100             |

| STL      | Set Link                             | 7120             |

| CLA      | Clear Accumulator                    | 7200             |

| STA      | Set Accumulator                      | 7240             |

| HLT      | Halt                                 | 7402             |

| O SR     | OR Switch Register                   | 7404             |

| SKP      | Skip                                 | 7410             |

| SML      | Skip on Nonzero Link                 | 7420             |

| SZL      | Skip on Zero Link                    | 7430             |

| SZA      | Skip on Zero Accumulator             | 7440             |

| SNA      | Skip on Nonzero Accumulator          | 7450             |

| SMA      | Skip on Minus Accumulator            | 7500             |

| SPA      | Skip on Positive Accumulator         | <i>75</i> 10     |

Table 2-1. (continued) Instruction Index

| Mnemonic | Meaning                        | Octal Code |

|----------|--------------------------------|------------|

| CLA      | Clear Accumulator              | 7600       |

| LAS      | Load AC Switches               | 7604       |

|          | IOT Group                      |            |

| ION      | Interrupt On                   | 6001       |

| IOF      | Interrupt Off                  | 6002       |

| SMP      | Skip on No Memory Parity Error | 6101       |

| CMP      | Clear Memory Parity Error Flag | 6104       |

| KSF      | Keyboard, Skip on Flag         | 6031       |

| ксс      | Keyboard, Clear Flag           | 6032       |

| KRS      | Keyboard, Read Buffer Static   | 6034       |

| KRB      | Keyboard, Read Buffer          | 6036       |

| TSF      | Teleprinter, Skip on Flag      | 6041       |

| TCF      | Teleprinter, Clear Flag        | 6042       |

| TPC      | Teleprinter, Print Character   | 6044       |

| TLS      | Teleprinter, Load Sequence     | 6046       |

#### 2.1.1 Number System

The PDP-8/S uses two's complement, fixed-point conventions to do binary arithmetic. In a word used as a number, bit 0 (the left-most bit) represents the sign denoted by 0 for positive, 1 for negative. In a positive number, the remaining eleven bits are the magnitude in ordinary binary notation. The negative of a number is obtained by taking the two's complement. If x is an n-digit binary number, its two's complement is  $2^n - x$ , and its one's complement is  $(2^n - 1) - x$ , or equivalently  $(2^n - x) - 1$ . Subtracting a number from  $2^n - 1$  (from all 1s) is equivalent to performing the logical complement, changing all zeros to ones and all ones to zeros. Therefore, to form the two's complement, take the logical complement (usually referred to merely as the complement) of the entire word including the sign, and add 1 to the result. In a negative number, the sign bit is 1 and the remaining bits are the two's complement of the magnitude.

$$+153_{10} = +231_8 = 000 010 011 001$$

$0 11$

$-153_{10} = -231_8 = 111 101 100 111$

$0 11$

Zero is represented by a word containing all 0s; complementing this number produces all 1s, and adding 1 to that produces all 0s again. There is only one zero representation and its sign is positive. Since the numbers are symmetrical in magnitude about a single zero representation, all even numbers both positive and negative end in 0, all odd numbers in 1 (a number all 1s represents -1). Since there are the same number of positive and negative numbers, however, there is one more negative number than there are nonzero positive numbers. This is the most negative number and it cannot be produced by negating any positive number. (The magnitude of the most negative number is one greater than the largest positive number.)

If one's complements were used for negatives, a negative number could be read by attaching significance to the 0s instead of the 1s. In two's complement notation, each number is one greater than the complement of the positive number of the same magnitude, so one can read a negative number by attaching significance to the rightmost? and attaching significance to the 0s at the left of it. (The negative number of largest magnitude has a 1 in only the sign position.) In a negative integer, 1s may be discarded at the left, just as leading 0s may be dropped in a positive integer. In a negative fraction, 0s may be discarded at the right as long as only 0s are discarded, the number remains in two's complement form because it still has a 1 that possesses significance. If a portion including the rightmost 1 is discarded, the remaining part of the fraction is now a one's complement. The computer does not keep track of a binary point, so the programmer must adopt a point convention and shift the magnitude of the result to conform to the convention used.

#### 2.1.2 Instruction Format

A computer instruction performs some basic function, such as storing a word in memory or performing an arithmetic or logical operation. If an instruction requires a memory address, the three high-order bits (0 through 2) specify the operation, bit 3 specifies the type of addressing, and the remaining eight bits (4 through 11) specify the effective address or the location to be used in determining the effective address. The effective address is the actual address used to fetch the operand or alter program flow.

The operate and in-out instructions do not require memory addresses. In an operate instruction bits 0 through 2 contain 7, and the remaining bits specify individual operations, so an instruction can be microprogrammed to perform a combination of the various operations. In an in-out instruction,

bits 0 through 2 contain 6, bits 3 through 8 specify the in-out device, and bits 9 through 11 select the timing pulses sent out over the I/O bus. Pulses at the three event times, in order, are selected respectively by 1s in bits 11, 10, and 9.

#### 2.1.3 Addressing

Locations in memory are addressed by the 12-bit octal numbers 0000 to 7777 (0 to 4095 decimal). The instruction format allows only eight bits for an address, so for programming purposes the memory is divided into thirty-two pages, each containing 128 (200<sub>8</sub>) locations. The eight address bits in the instruction can select one location out of 256, or a single location from two pages. If bit 4 is 0, bits 5 through 11 are taken as an address in page 0, i.e., the address part of the instruction is taken to represent an address between 0000 and 0177. If bit 4 is 1, bits 5 through 11 are taken as an address in the same page from which the instruction was retrieved. The 12-bit address that is used is the combination of bits 5 through 11 of the instruction word and bits 0 through 4 of the address previously supplied by PC to MA for instruction retrieval.

Bit 3 of the instruction word specifies the type of address contained in bits 4 through 11. If bit 3 is 0, addressing is direct; the effective address is the 12-bit address determined by bits 4 through 11. If bit 3 is 1, addressing is indirect, and the address part of the instruction is taken to specify a location whose contents are to be used as the (12-bit) effective address.

#### 2.1.4 Autoindexing

The program can make use of an automatic indexing feature by indirectly addressing any memory location from 0010 to 0017. Whenever one of these locations is specified by an indirect address, the processor retrieves the contents of the addressed location, indexes the word contained therein, writes the altered word back into memory, and uses the indexed word as the effective address.

#### 2.1.5 Operating Speed

The table 2-2 gives the approximate execution times in microseconds of the various PDP-8/S instructions. Where they are applicable, the longer times that are required for indirect addressing and autoindexing are also given. With each time, the pair of numbers separated by a comma indicates the number of processor and memory cycles required for the instruction.

Table 2-2.

PDP-8/S Instruction Execution Times

|       |              |     | Indirect A | ddressing | Autoing | lexing |

|-------|--------------|-----|------------|-----------|---------|--------|

| AND   | 32.2         | 2,2 | 48.3       | 3,3       | 64.4    | 4,4    |

| TAD   | 32.2         | 2,2 | 48.3       | 3,3       | 64.4    | 4,4    |

| ISZ   | 48.3         | 3,3 | 64.4       | 4,4       | 80.5    | 5,5    |

| DCA   | 42.7         | 3,2 | 58.8       | 4,3       | 74.9    | 5,4    |

| JMS   | 42.7         | 3,2 | 58.8       | 4,3       | 74.9    | 5,4    |

| JMP   | 26.6         | 2,1 | 42.7       | 3,2       | 58.8    | 4,3    |

| IOT   | 37.1         | 3,1 |            |           |         |        |

| OPR 1 | 26.6         | 2,1 |            |           |         |        |

| OPR 2 | <b>37.</b> 1 | 3,1 |            |           |         |        |

A processor cycle (one word time) requires  $10.5\,\mu s$  if there is no memory request, about 9.8  $\mu s$  otherwise. The above times are based on a memory cycle of 6.3  $\mu s$ . The nominal times for the two memory types are  $6.3\,\mu s$  and  $6.5\,\mu s$ , but either type can differ by as much as 100 ns from its nominal value. Moreover, if the optional data channel equipment or expanded memory is added to the computer, the memory cycle time is fixed at 8  $\mu s$  regardless of stack type. The programmer is advised not to use internal computer timing in place of a real-time clock.

A program interrupt takes 32.2  $\mu s$  (2,2) in addition to instruction execution time. The first IOT pulse occurs 10.5  $\mu s$  after the IOT instruction is fetched, and the other two pulses occur at 1- $\mu s$  intervals thereafter.

#### 2.2 Word Times

Each word time is made up of 14-bit times (numbered 00 through 13) during which the clack generates a string of fourteen bit pulses 750 ns apart. The first 12 pulses perform whatever serial operations are required on one or more 12-bit words. The thirteenth pulse performs most of the individual operations that are required for any instruction (such as an OPR), checks parity, and requests a memory cycle if one is required. When a memory cycle is requested, the processor clock stops, and the memory goes through its cycle controlled by its own clock. Upon completion of the cycle, the processor clock restarts at the fourteenth pulse, which determines the transition to the next word-time. When the computer is stopped by the program or the operator, it does so between the thirteenth and fourteenth bit times, i.e., at time 13 but following completion of the memory cycle if one is requested.

The word-time in which a word is processed depends upon what type of information it represents (an instruction, an address, an operand) and what functions must be performed on it. There are six word-times: fetch, index, defer, execute, end, break. Although the execution of an instruction

begins in fetch time, the program must start in end time, which determines the location of the first instruction and requests a memory cycle to retrieve it. In other words, fetch time does not fetch the instruction. Fetch time processes the instruction just retrieved from memory. It transfers the instruction code to IR for decoding, transfers the address part to MA, and indexes PC so that it will point to the next location.

At the end of fetch time, the processor requests memory access if the instruction is indirectly addressed or requires the retrieval of an operand. If an autoindexing location is indirectly addressed, the processor then enters index time; for any other indirect addressing it enters defer time; in any other situation it goes directly to execute time. In index time the address that has been retrieved is incremented by one and written back in memory. The processor then enters defer time to move the new address to MA and request a memory cycle, if an operand must be retrieved. The actual logical, arithmetic or program control operation specified by the instruction is then performed in execute time, which requests access if an operand must be deposited in memory. In end time the processor determines the location of the next instruction and fetches it. In some cases the execute and end times are simultaneous; if they are not, the processor automatically goes from execute to end time.

After retrieving an instruction, the processor returns to fetch time unless a program interrupt has been requested. In this case the processor enters break time in which it deposits the current contents of PC in location 0000, and then returns to end time to retrieve the instruction in location 0001. There are also three special word times for operations associated with the console: these are used for loading a starting address into PC, depositing a word in memory, or examining the contents of a memory location.

To control the special operations required for in-out, including parallel transfer over the bus, the first bit pulse in execute time of an IOT triggers a string of three special pulses 1 µs apart. Of these, the only pulses actually sent over the bus for use in IOT operations are those specified by the programmer in bits 9 through 11 of the IOT instruction.

#### 2.3 PROCESSOR OPERATION

In the table model of the PDP-8/S, the circuit breakers are mounted on the rear panel with the power supply; the rack mounted model has a power control that includes circuit breakers and usually a power light. All other controls and indicators for the processor and memory are located on the computer front panel. The indicators are on the vertical upper part of the panel; below this is a raw of two-position keys and switches with a key-operated rotary switch at each end (switches are alternate action, keys are momentary contact).

The six switches at the left end of the row and the corresponding lights at the top of the panel are for the optional memory expansion. The next 12 switches make up a switch register through which the operator can supply data and addresses to the processor (the up position of a switch represents a 1).

The register can be used in conjunction with some of the operating keys, and its contents can be read into AC by the program. The next six levers are the operating keys. They are off when in the up position, except for DEP (third one from the left) which is off when in the down position. The last two levers are the operating mode switches, which are off when in the down position. Power is applied to the computer by turning clockwise the key-operated POWER switch at the right-hand end of the panel. The similar PANEL LOCK switch at the left-hand end disables the operating keys and switches when turned clockwise (the last eight levers at the right-hand end become inoperative and the switch register is not affected).

When any indicator is lit, the associated flip-flop is in the 1 state or the associated function is true. A few indicators display useful information while the processor is running, but most change too frequently and are therefore discussed in terms of the information they display when the processor has stopped.

#### 2.3.1 Indicators, Operating Keys, and Switches

In the center of the panel there are four rows of indicators that display (from top to bottom) the contents of PC, MA, MB and AC. The extra light at the left-hand end of the bottom row displays the contents of the link. When the computer stops, PC usually holds the address of the next instruction, MA indicates the address of the last memory access, and MB holds the word read from or written into memory.

| Indicator                                    | <u>Function</u>                                                                                                                                                                                                                                                                    |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FETCH, INDEX,<br>DEFER, EXEC,<br>END, BREAK  | EXEC and END can be on together, but otherwise only one of these lights can be on at a time. The on light indicates the word time the processor has stopped in.                                                                                                                    |

| PAUSE                                        | A memory cycle is in progress. This light can stay on long enough to be noticed only if optional data break equipment is occupying the memory most or all of the time, and thus the processor is running little if at all.                                                         |

| RUM                                          | The processor is in normal operation with one instruction following another. When the light goes off, the computer stops.                                                                                                                                                          |

| AND, TAD, ISZ,<br>DCA, JMS, JMP,<br>IOT, OPR | Only one of these can be on at a time. It indicates the instruction being executed or just executed. If the processor stops with BREAK on, or the operator has just loaded an address from the console, the AND light will be on regardless of what instruction was last executed. |

| ION                                          | The program interrupt system is on, so a parity error or an interrupt request over the in-out bus will cause a program break.                                                                                                                                                      |

| PARITY                                       | Displays the parity bit of the last word read from or written into memory.                                                                                                                                                                                                         |

| PARITY ERROR                                 | Indicates that a word read from memory had incorrect parity.                                                                                                                                                                                                                       |

When the computer executes a HLT, it stops with RUN and PAUSE off, and END and OPR on. The MB lights display the next instruction, the PC and MA lights indicate the address of the next instruction to be executed, i.e., the instruction just retrieved from memory in end time.

| Operating Key    | <u>Function</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START            | Pressing this key clears AC, L, MB and the in-out equipment. It turns off ION, PARITY, and PARITY ERROR. It sets the END state, and lights RUN, causing the computer to begin normal operation by retrieving an instruction from the location currently addressed by PC.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LOAD ADD         | If RUN is off, pressing this key clears AC. It turns off ION and loads the contents of the switch register into PC, and lights FETCH and AND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DEP              | If RUN is off, <u>lifting</u> this key deposits the contents of the switch register into the memory location currently addressed by PC, increments PC by one, and lights FETCH. At the completion of the operation, the AC and MB lights display the word deposited, PARITY indicates its parity, MA addresses the location into which the word was deposited, and PC contains the next consecutive address.                                                                                                                                                                                                                                                                                        |

| EXAM             | If RUN is off, pressing this key turns off PARITY ERROR, clears AC, displays the contents of the memory location addressed by PC in the MB and PARITY lights. It increments PC by one, and lights FETCH. At the end of the operation MB and PARITY display the word, MA addresses the location that was examined, and PC addresses the next consecutive location.                                                                                                                                                                                                                                                                                                                                   |

| CONT             | Pressing this key lights RUN, causing the computer to begin normal operation in its current state. If RUN is already lit the key has no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| STOP             | Pressing this key while RUN is lit causes the computer to stop with FETCH lit. At this time the instruction lights indicate which instruction is about to be executed, MB contains the instruction word or operand (or an address if an indirect bit was used) depending on the type of instruction, and PC points to the location one beyond that from which the instruction was retrieved. The MA lights indicate the address from which the last memory word was fetched. They represent either the address of the instruction or the operand (or an address if an indirect bit was used) depending on the type of instruction. The instruction indicators will display the type of instruction. |

| Operating Switch | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SING INST        | While this switch is in the up position, the processor stops in fetch time of every instruction that it executes. Hence the operator can run a program one instruction at a time, by turning on this switch, fetching the first instruction by pressing START, and executing each succeeding instruction by pressing CONT. Each time the computer stops, the lights display the same information as when the STOP key is pressed.                                                                                                                                                                                                                                                                   |

| SING STEP        | While this switch is in the up position, the processor stops at the end of every word-time that it executes. This switch is for maintenance purposes and allows the operator to run a diagnostic routine or other program, one                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

SING STEP (continued) step at a time. Operations are begun by pressing START, and each succeeding word-time is initiated by pressing CONT. The reader can determine the information that should be displayed on the panel by consulting the flow charts.

#### 2.4 TELETYPE OPERATION

The teletype provides two-way communication between operator and computer. It is actually four devices: keyboard, printer, reader and punch, which may be operated in various combinations. The equipment operates at speeds up to ten characters per second, with 8-bit characters plus start and stop control signals transmitted serially.

Figure 2-2 Teletype Model ASR 33

Located at the right front right-hand side of the unit is a 3-position rotary switch LINE/OFF/LOCAL. When this switch is set to LOCAL, the entire unit is independent of the computer and the key-board and printer function together as a normal typewriter. Moreover, turning on the punch allows the operator to punch a tape from the keyboard, and running the reader allows a tape to control the printer (if the punch is also on, it duplicates the tape).

Turning the switch to LINE connects the unit to the computer and separates its input and output functions. Any information transmitted to the computer from the keyboard affects the printer only insofar as the computer sends it back. Turning on the reader places it under program control, and turning on the punch causes it to punch whatever is sent to the printer by the computer.

The only control on the reader is a 3-position switch. When the switch is in the FREE position, the tape can be moved by hand freely through the reader mechanism. The STOP position engages the reader clutch so the tape is stationary but the reader is still off. Turning the switch to START causes the reader to read the tape if the unit is in local, but places it under program control if on line.

The operator controls the punch by means of four pushbuttons. The two on the right turn the punch on and off. Pressing the REL button releases the tape so that it can be moved by hand through the punch mechanism. Pressing B. SP. moves the tape backward one frame so that the operator can delete a frame that is incorrect by using the RUB OUT key (rubout characters are ignored when the tape is read).

The keyboard resembles that of a standard typewriter with four rows of keys and a space bar. The line feed moves the carriage only vertically with a spacing of six lines per inch. The return moves the carriage to the left margin but does not feed a line. To start a new line, the operator must strike both return and line feed. Codes for the characters on the lower parts of the key tops can be transmitted merely by striking the keys. Codes for printable characters on the upper parts (punctuation, ampersand, percent sign) are transmitted by holding down the shift key when striking the character key. Control codes are transmitted by holding down the control key CTRL, while striking the appropriate character key. Codes for all characters listed on the keyboard and some that are not can be transmitted to the computer, but codes for some of the control functions have no effect on the printer when sent back. Table 2–3 lists all codes, their ASCII assignments, and the key combinations required to transmit them. The 8-bit codes are listed below. An asterisk indicates a code that has no effect on the Model 33. The characters actually contain only seven information bits; the eighth bit may be used for parity, but currently all machines are set up so that the eighth bit is a mark, and thus the codes generated from the keyboard are 200g greater than the corresponding ASCII codes.

Table 2-3. Teletype Code

| Octal<br>Code | ASCII<br>Character | Key<br>Combination | <u>Remarks</u>                                       |

|---------------|--------------------|--------------------|------------------------------------------------------|

| 200           | NULL               | SHIFT CTRL P       | Noll                                                 |

| 201*          | SOM                | CTRL A             | Start of message                                     |

| 202*          | EOA                | CTRL B             | End of address                                       |

| 203*          | EOM                | CTRL C             | End of message                                       |

| 204           | EOT                | CTRL EOT           | End of transmission; shuts off TWX machines          |

| 205           | WRU                | CTRL WRU           | "Who are you?" Triggers "Here is," at remote station |

| 206*          | RU                 | CTRL RU            | "Are you…?"                                          |

Table 2-3. (continued) Teletype Code

| Octal<br>Code | ASCII<br>Character | Key<br>Combination | Remarks                                      |

|---------------|--------------------|--------------------|----------------------------------------------|

| 207           | BELL               | CTRL BELL          | Rings the bell                               |

| 210*          | FE                 | CTRL H             | Format effector                              |

| 211           | HT                 | CTRL TAB           | Horizontal tab                               |

| 212           | LF                 | LINE FEED          | Line feed                                    |

| 213           | VTAB               | CTRL VT            | Vertical tab                                 |

| 214           | FF                 | CTRL FORM          | Form feed                                    |

| 215           | CR                 | RETURN             | Carríage return                              |

| 216*          | SO                 | CTRL N             | Shift out                                    |

| 217*          | SI                 | CTRL O             | Shift in                                     |

| 220*          | DC0                | CTRL P             | Device control reserved for data line escape |

| 221           | DC1                | CTRL Q             | Turns reader on                              |

| 222*          | DC2                | CTRL TAPE          | Turns punch on                               |

| 223           | DC3                | CTRL XOFF          | Turns reader off                             |

| 224*          | DC4                | CTRL               | Turns punch off                              |

| 225*          | ERR                | CTRL U             | Error                                        |

| 226*          | SYNC               | CTRL V             | Synchronous idle                             |

| 227*          | LEM                | CTRL W             | Logical end of media                         |

| 230*          | <b>S</b> 0         | CTRL X             | Separator, information                       |

| 231*          | 53                 | CTRL Y             | Separator, data delimiter                    |

| 232*          | <b>S</b> 2         | CTRL Z             | Separator, words                             |

| 233*          | \$3                | SHIFT CTRL K       | Separator, groups                            |

| 234*          | \$4                | SHIFT CTRL L       | Separator, records                           |

| 235*          | \$5                | SHIFT CTRL M       | Separator, files                             |

| 236*          | S6                 | SHIFT CTRL N       | Separator, miscellaneous                     |

| 237*          | 57                 | SHIFT CTRL O       | Separator, miscellaneous                     |

| 240           | Space              | Space bar          |                                              |

| 241           | ļ.                 | SHIFT!             |                                              |

| 242           | 41                 | SHIFT "            |                                              |

| 243           | #                  | SHIFT #            |                                              |

| 244           | \$                 | SHIFT \$           |                                              |

| 245           | %                  | SHIFT %            |                                              |

Table 2-3. (continued) Teletype Code

| Octal<br>Code | ASCII<br>Character | Key<br>Combination | Remarks                   |

|---------------|--------------------|--------------------|---------------------------|

| 246           | &                  | SHIFT &            |                           |

| 247           | ī                  | SHIFT '            |                           |

| 250           | (                  | SHIFT (            |                           |

| 251           | )                  | SHIFT)             |                           |

| 252           | *                  | SHIFT *            |                           |

| 253           | +                  | SHIFT +            |                           |

| 254           | ,                  | ,                  |                           |

| 255           | -                  | -                  |                           |

| 256           | •                  | •                  |                           |

| 257           | /                  | /                  |                           |

| <b>26</b> 0   | ø                  | 0                  | Zero, prints with a slash |

| 261           | 1                  | 1                  |                           |

| 262           | Ž                  | 2                  |                           |

| <b>26</b> 3   | 3                  | 3                  |                           |

| 264           | 4                  | 4                  |                           |

| 265           | 5                  | 5                  |                           |

| 266           | 6                  | 6                  |                           |

| 267           | 7                  | 7                  |                           |

| 270           | 8                  | 8                  |                           |

| 271           | 9                  | 9                  |                           |

| 272           | :                  | :                  |                           |

| 273           | ;                  | ;                  |                           |

| 274           | <                  | SHIFT <            |                           |

| 275           | =                  | SHIFT =            |                           |

| 276           | >                  | SHIFT >            |                           |

| 277           | ?                  | SHIFT ?            |                           |

| 300           | @                  | SHIFT @            |                           |

| 301           | Α                  | Α                  |                           |

| 302           | В                  | В                  |                           |

| 303           | С                  | С                  |                           |

| 304           | D                  | D                  |                           |

Table 2–3. (continued)

Teletype Code

| Octal<br>Code | ASC11<br>Character | Key<br>Combination | Remarks                                                                                                                             |

|---------------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 305           | E                  | E                  |                                                                                                                                     |

| 306           | F                  | F                  |                                                                                                                                     |

| 307           | G                  | G                  |                                                                                                                                     |

| 310           | н                  | Н                  |                                                                                                                                     |

| 311           | 1                  | 1                  |                                                                                                                                     |

| 312           | J                  | J                  |                                                                                                                                     |

| 313           | K                  | K                  |                                                                                                                                     |

| 314           | L                  | L                  |                                                                                                                                     |

| 315           | W                  | M                  |                                                                                                                                     |

| 316           | Ν                  | N                  |                                                                                                                                     |

| 317           | 0                  | 0                  |                                                                                                                                     |

| 320           | P                  | Р                  |                                                                                                                                     |

| 321           | Q                  | Q                  |                                                                                                                                     |

| 322           | R                  | R                  |                                                                                                                                     |

| 323           | S                  | S                  |                                                                                                                                     |

| 324           | T                  | τ                  |                                                                                                                                     |

| 325           | U                  | U                  |                                                                                                                                     |

| 326           | ٧                  | ٧                  |                                                                                                                                     |

| 327           | W                  | W                  |                                                                                                                                     |

| 330           | ×                  | X                  |                                                                                                                                     |

| 331           | Υ                  | Υ                  |                                                                                                                                     |

| 332           | Z                  | Z                  |                                                                                                                                     |

| 333           | [                  | SHIFT K            |                                                                                                                                     |

| 334           | \                  | SHIFT L            |                                                                                                                                     |

| 335           | ]                  | SHIFT M            |                                                                                                                                     |

| 336           | <b>?</b>           | SHIFT 1            |                                                                                                                                     |

| 337           | <b>-</b>           | SHIFT ←            |                                                                                                                                     |

| 340-<br>373*  |                    |                    | Lower case letters; codes cannot be gen-<br>erated from keyboard and should not be<br>used in programs for reasons of compatibility |

| 374           | ACK                |                    | Acknowledge; code cannot be generated from keyboard and should not be used in programs for reasons of compatibility                 |

Table 2-3. (continued) Teletype Code

| Octal<br>Code | ASC II<br>Character | Key<br>Combination | Remarks                                                                                                                |

|---------------|---------------------|--------------------|------------------------------------------------------------------------------------------------------------------------|

| 375*          | 1                   | ALT MODE           | May be used for any desired control purpose                                                                            |

| 376*          | ESC                 |                    | Escape; code cannot be generated from key-<br>board and should not be used in programs<br>for reasons of compatibility |

| 377*          | DEL                 | RUB OUT            | Delete                                                                                                                 |

|               |                     | REPT               | Causes any other key that is struck to repeat continuously until REPT is released                                      |

|               |                     | HERE IS            | In local, punches 20 lines of tape feed                                                                                |

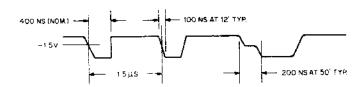

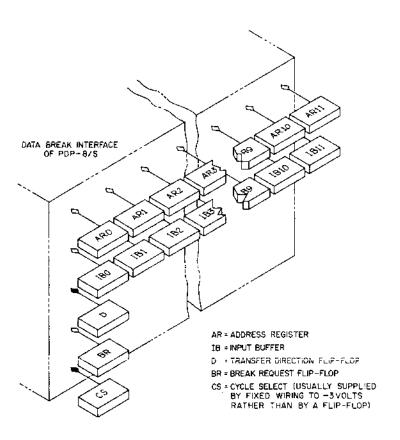

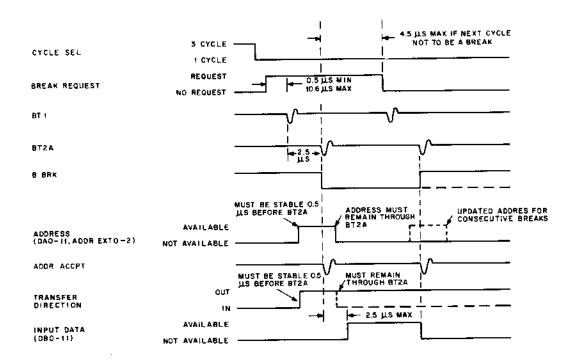

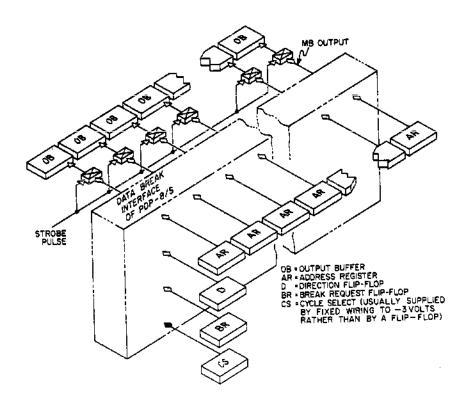

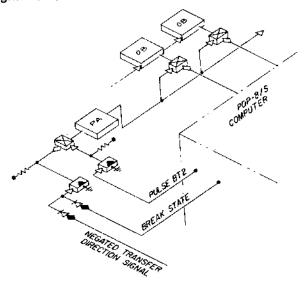

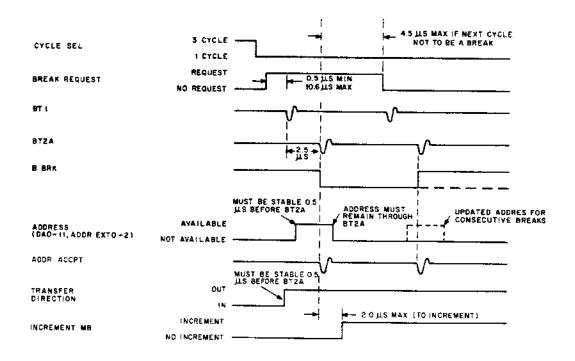

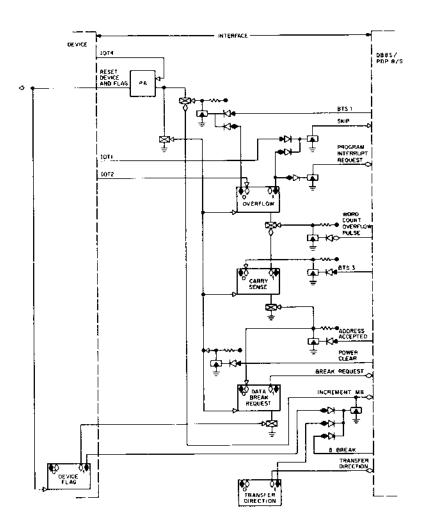

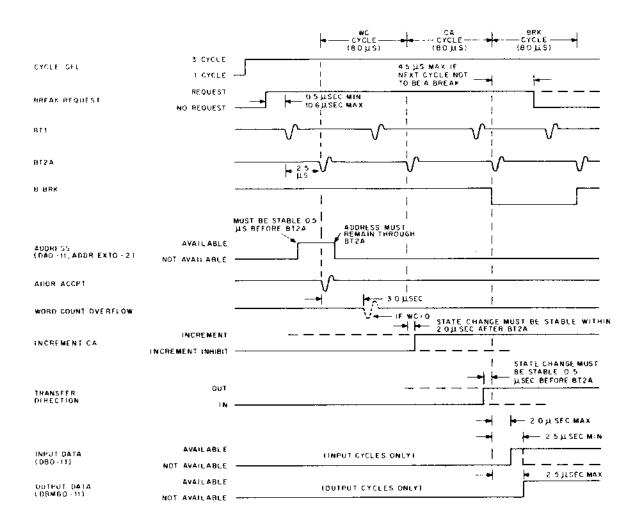

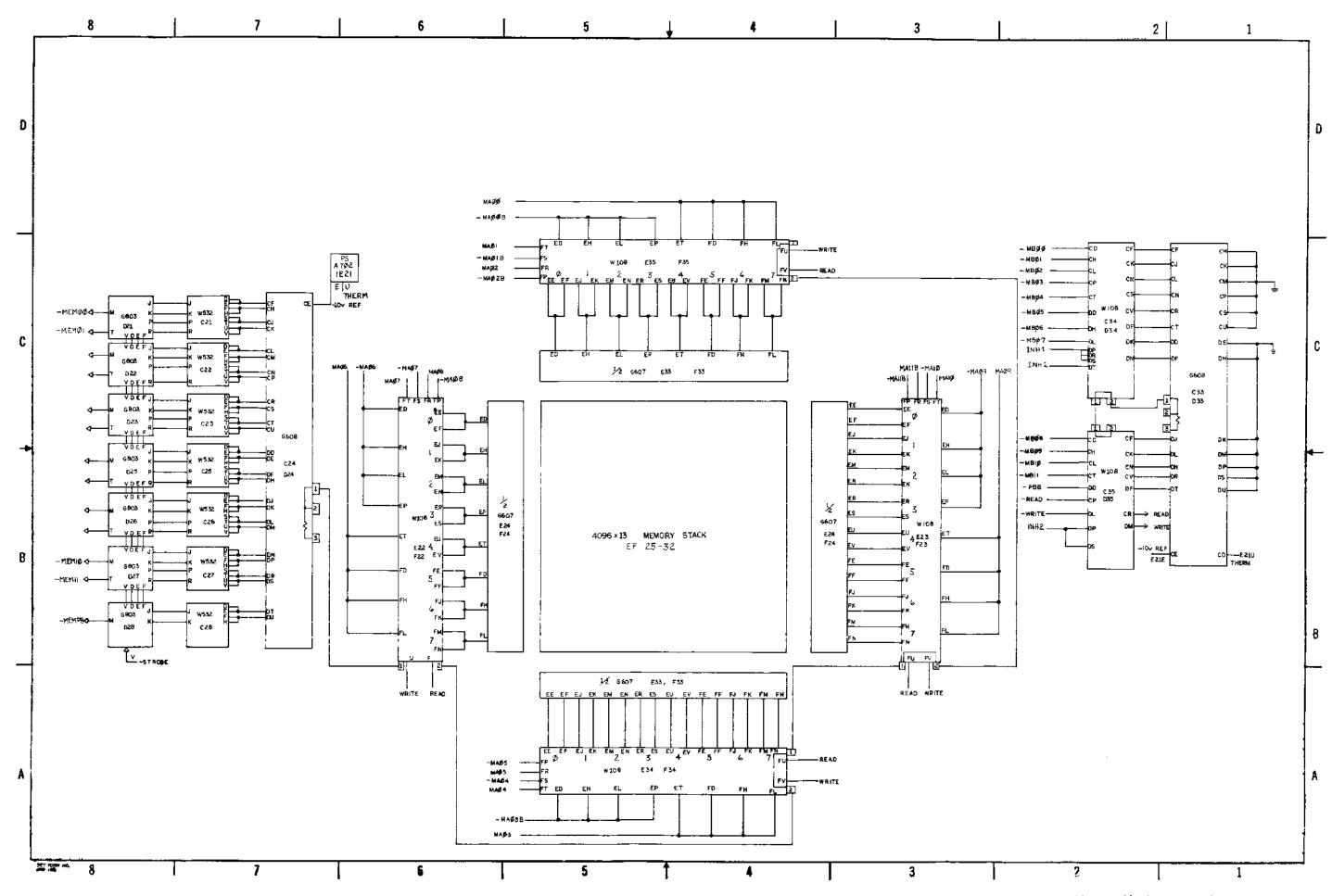

|               |                     | BRK RLS            | Not connected                                                                                                          |