## RX02 FLOPPY DISK SYSTEM TECHNICAL MANUAL

# RX02 Floppy Disk System Technical Manual

#### Copyright • 1978 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS |

|---------|--------------|---------|

| DEC     | DECSYSTEM-20 | OMNIBUS |

| PDP     | DIBOL        | OS/8    |

| DECUS   | EDUSYSTEM    | RSTS    |

| UNIBUS  | VAX          | RSX     |

|         | VMS          | IAS     |

## **CONTENTS**

| PREFACE   |                                                                 | Page         |

|-----------|-----------------------------------------------------------------|--------------|

| TREFACE   |                                                                 |              |

| CHAPTER 1 | GENERAL INFORMATION                                             |              |

| 1.1       | INTRODUCTION                                                    |              |

| 1.2       | GENERAL DESCRIPTION                                             | 1-2          |

| 1.2.1     | Interface Modules                                               | 1-2          |

| 1.2,2     | Microprogrammed Controller                                      | 1 -2         |

| 1.2.3     | Read/Write Electronics                                          | 1-2          |

| 1.2.4     | Electromechanical Drive                                         | 1-2          |

| 1.2.5     | Power Supply                                                    | 1-4          |

| 1.3       | OPTION DESCRIPTION                                              |              |

| 1.3.1     | Operation For Single Density Recording Only (RX8E, RX11, RXV11) | 1-€          |

| 1.3.1.1   | PDP-8 Operation                                                 | 1-6          |

| 1 3 1,2   | PDP-11 Operation                                                | 1 6          |

| 1.3.1.3   | LSI-11 Operation                                                | 1-7          |

| 1.3.2     | Operation For Single or Double Density Recording RX28, RX211,   |              |

|           | RXV211)                                                         |              |

| 1.3.2.1   | PDP-8 Operation                                                 | 1-7          |

| 1.3,2,2   | PDP-11 Operation                                                | 1-7          |

| 1.3.2.3   | LSI-11 Operation                                                | 1-7          |

| 1.4       | SPECIFICATIONS                                                  | 1-8          |

| 1.5       | SYSTEMS COMPATIBILITY                                           | 1-9          |

| 1.5.1     | Media                                                           | 1-9          |

| 1.5.2     | Recording Scheme                                                | 1-10         |

| 1.5,2.1   | Double Frequency (FM)                                           | 1-10         |

| 1.5.2.2   | Miller Code (MFM)                                               | 1-10         |

| 1.5.3     | Logical Format                                                  | 1-12         |

| 1.5.3.1   | Header Field Description                                        | <b>1-</b> 13 |

| 1.5,3,2   | Data Field Description                                          |              |

| 1.5.3,3   | Track Usage                                                     | 1-14         |

| 1.5.3.4   | CRC Capability                                                  |              |

| CHAPTER 2 | INSTALLATION                                                    |              |

| 2.1       | SITE PREPARATION                                                | 2-           |

| 2.1.1     | Space                                                           |              |

| 2.1.2     | Cabling                                                         | 2-2          |

| 2.1.3     | AC Power                                                        |              |

| 2.1.3.1   | Power Requirements                                              |              |

| 2.1.3.2   | Input Power Modification Requirements                           |              |

|           |                                                         | Page |

|-----------|---------------------------------------------------------|------|

| 2.1.4     | Fire and Safety Precautions                             | 2-4  |

| 2.2       | CONFIGURATION GUIDELINES                                |      |

| 2.3       | ENVIRONMENTAL CONSIDERATIONS                            | 2-4  |

| 2.3.1     | General                                                 | 2-4  |

| 2.3.2     | Temperature, Relative Humidity                          |      |

| 2.3.3     | Heat Dissipation                                        |      |

| 2.3.4     | Radiated Emissions                                      |      |

| 2.3.5     | Cleanliness                                             | 2-6  |

| 2.4       | UNPACKING AND INSPECTION                                | 2-6  |

| 2.4.1     | General                                                 | 2-6  |

| 2.4.2     | Tools                                                   |      |

| 2.4.3     | Unpacking                                               |      |

| 2.4.3.1   | Cabinet-Mounted                                         |      |

| 2.4.3.2   | Separate Container                                      | 2-7  |

| 2.4.3.3   | Inspection                                              |      |

| 2.5       | INSTALLATION                                            |      |

| 2.6       | TESTING                                                 |      |

|           |                                                         |      |

| CHAPTER 3 | USER INFORMATION                                        |      |

| 3.1       | CUSTOMER RESPONSIBILITY                                 | 3-1  |

| 3.2       | CARE OF MEDIA                                           |      |

| 3.2.1     | Handling Practices and Precautions                      | 3-1  |

| 3.2,2     | Diskette Storage                                        | 3-2  |

| 3.2.2.1   | Short Term (Available for Immediate Use)                | 3-2  |

| 3.2.2.2   | Long Term                                               | 3-2  |

| 3.2.3     | Shipping Diskettes                                      | 3-2  |

| 3.3       | OPERATING INSTRUCTIONS                                  | 3-3  |

| 3.4       | OPERATOR TROUBLESHOOTING                                | 3-3  |

| CHAPTER 4 | PROGRAMMING                                             |      |

| 4.1       | RX8E and RX28 PROGRAMMING INFORMATION                   | 4-1  |

| 4.1.1     | Device Codes.                                           |      |

| 4.1.2     | Instruction Set                                         |      |

| 4.1.2.1   | RX8E Load Command (LCD) - 67x1                          |      |

| 4.1.2.2   | RX28 Load Command - (First byte 67x1, Second byte 67x2) |      |

| 4.1,2.3   | Transfer Data Register (XDR) - 67x2                     |      |

| 4.1.2.4   | STR - 67x3                                              |      |

| 4.1.2.5   | SER – 67x4                                              | 4-4  |

| 4.1.2.6   | SDN - 67x5                                              |      |

| 4.1.2.7   | INTR - 67x6                                             |      |

| 4.1.2.8   | INIT – 67x7                                             |      |

| 4.1.3     | Register Description                                    |      |

|          |                                             | Page |

|----------|---------------------------------------------|------|

| 4.1,3.1  | Command Register                            | 4-4  |

| 4.1.3.2  | Error Code Register                         | 4-5  |

| 4.1.3.3  | RX2TA - RX Track Address                    |      |

| 4.1.3.4  | RX2SA - RX Sector Address                   |      |

| 4.1.3.5  | RX2DB - RX Data Buffer                      |      |

| 4.1.3.6  | RX8E - RX Error and Status                  |      |

| 4.1.3.7  | RX28 - RX Error and Status                  |      |

| 4.1.4    | Function Code Description                   |      |

| 4.1.4.1  | Fill Buffer (000)                           |      |

| 4.1.4.2  | Empty Buffer (001)                          |      |

| 4.1.4.3  | Write Sector (010)                          |      |

| 4.1.4.4  | Read Sector (011)                           |      |

| 4.1.4.5  | Set Media Density (100) for RX28 Only       | 4-11 |

| 4.1.4.6  | Maintenance Read Status (101) for RX28 Only |      |

| 4.1.4.7  | Read Status (101) for RX8E Only             | 4-12 |

| 4.1.4.8  | Write Deleted Data Sector (110)             | 4-12 |

| 4.1.4.9  | Read Error Code Function (111)              |      |

| 4.1.4.10 | Power Fail                                  |      |

| 4.1.5    | Error Recovery                              |      |

| 4.1.5.1  | RX8E                                        |      |

| 4.1.5.2  | RX28                                        |      |

| 4.1.6    | RX8E Programming Examples                   | 4-14 |

| 4.1.6.1  | Write/Write Deleted Data/Read Functions     | 4-14 |

| 4.1.6.2  | Empty Buffer Function                       |      |

| 4.1.6.3  | Fill Buffer Function.                       |      |

| 4.1.7    | RX28 Programming Examples                   |      |

| 4.1.8    | Restrictions and Programming Pitfalls       |      |

| 4.2      | RXII and RXVII PROGRAMMING INFORMATION      | 4-24 |

| 4.2.1    | Register and Vector Addresses               |      |

| 4.2.2    | Register Description                        |      |

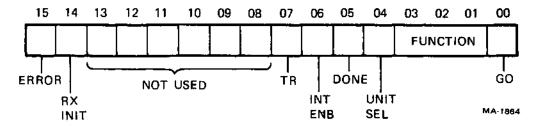

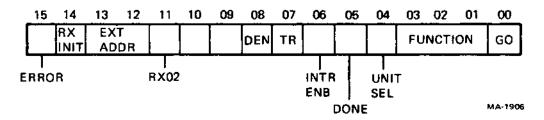

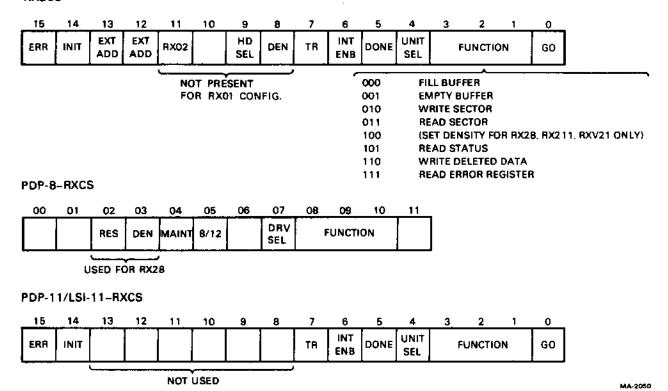

| 4.2.2.1  | RXCS - Command and Status (177170)          |      |

| 4.2.2.2  | RXDB - Data Buffer Register (177172)        |      |

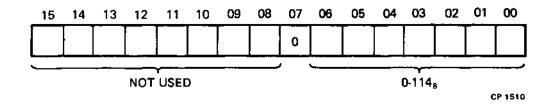

| 4.2.2.3  | RXTA - RX Track Address                     | 4-26 |

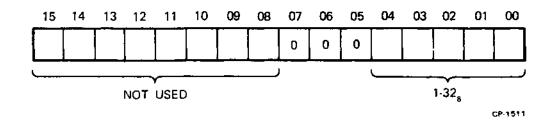

| 4.2,2,4  | RXSA - RX Sector Address                    | 4-26 |

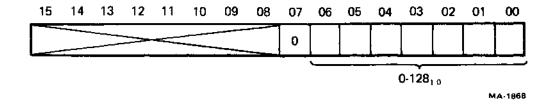

| 4.2.2.5  | RXDB - RX Data Buffer                       |      |

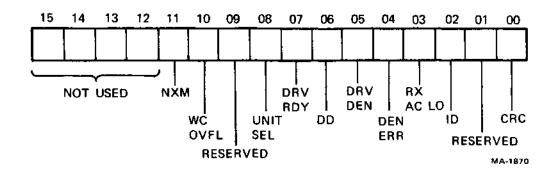

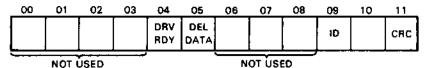

| 4.2.2.6  | RXES - RX Error and Status                  |      |

| 4.2.3    | Function Codes                              |      |

| 4.2.3.1  | Fill Buffer (000)                           | 4-29 |

| 4.2.3.2  | Empty Buffer (001)                          |      |

| 4.2.3.3  | Write Sector (010)                          |      |

| 4.2.3.4  | Read Sector (011)                           |      |

| 4.2.3.5  | Read Status (101)                           |      |

| 4.2.3.6  | Write Sector with Deleted Data (110)        |      |

| 4.2.3.7  | Read Error Code Function (111)              |      |

|           |                                                       | Page |

|-----------|-------------------------------------------------------|------|

| 4.2.3.8   | Power Fail                                            | 4-31 |

| 4.2.4     | Programming Examples                                  | 4-31 |

| 4.2.4.1   | Read Data/Write Data                                  |      |

| 4.2.4.2   | Empty Buffer Function                                 |      |

| 4.2.4.3   | Fill Buffer Function                                  | 4-33 |

| 4.2.5     | Restrictions and Programming Pitfalls                 | 4-33 |

| 4.2.6     | Error Recovery                                        |      |

| 4.3       | RX211 and RXV21 PROGRAMMING INFORMATION               |      |

| 4.3.1     | Register and Vector Addresses                         | 4-37 |

| 4.3.2     | Register Description                                  |      |

| 4.3.2.1   | RX2CS - Command and Status (177170)                   |      |

| 4.3.2.2   | RX2DB - Data Buffer Register (177172)                 |      |

| 4.3.2.3   | RX2TA - RX Track Address                              |      |

| 4.3,2.4   | RX2SA - RX Sector Address                             |      |

| 4.3.2.5   | RX2WC - RX Word Count Register                        |      |

| 4.3.2.6   | RX2BA – RX Bus Address Register                       |      |

| 4.3.2.7   | RX2DB - RX Data Buffer                                |      |

| 4.3.2.8   | RX2ES – RX Error and Status                           |      |

| 4.3.3     | Function Codes                                        |      |

| 4.3.3.1   | Fill Buffer (000)                                     |      |

| 4.3.3.2   | Empty Buffer (001)                                    |      |

| 4.3.3.3   | Write Sector (010)                                    |      |

| 4.3.3.4   | Read Sector (011)                                     |      |

| 4.3.3.5   | Set Media Density (100)                               |      |

| 4.3.3.6   | Maintenance Read Status (101)                         |      |

| 4.3.3.7   | Write Sector with Deleted Data (110)                  |      |

| 4,3.3.8   | Read Error Code (111)                                 |      |

| 4.3.3.9   | RX02 Power Fail                                       |      |

| 4.3.4     | Error Recovery                                        |      |

| 4.3.5     | RX211/RXV21 Programming Examples                      |      |

| 4.3.5.1   | ,                                                     |      |

| 4.3.5.2   | Write/Fill Buffer                                     |      |

| 4.3.3.2   | Read/Empty Buller                                     | 440  |

| CHAPTER 5 | THEORY OF OPERATION                                   |      |

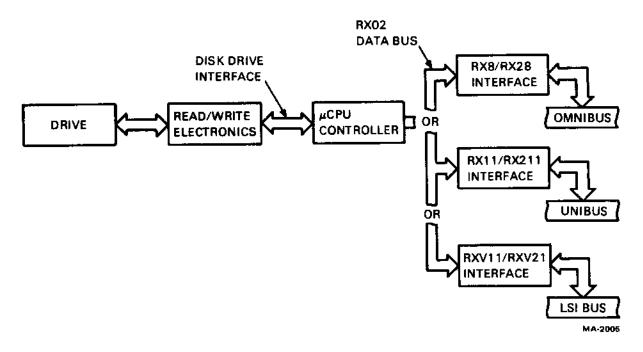

| 5.1       | OVERALL SYSTEM BLOCK DIAGRAM                          | 5-1  |

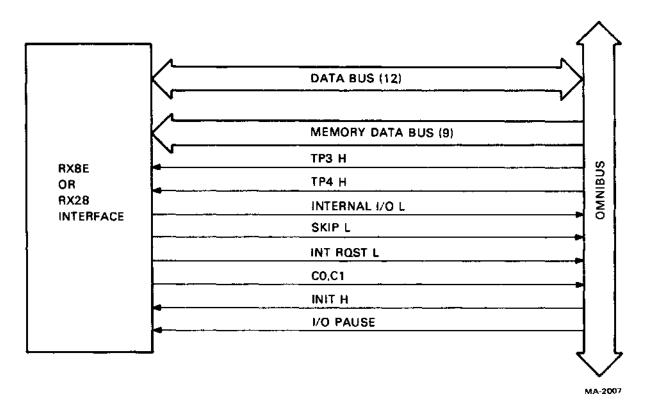

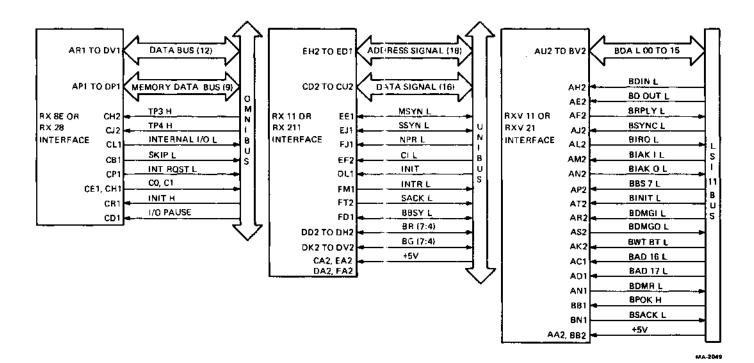

| 5.1.1     | Omnibus to RX8E/RX28 Interface Signals                | 5-1  |

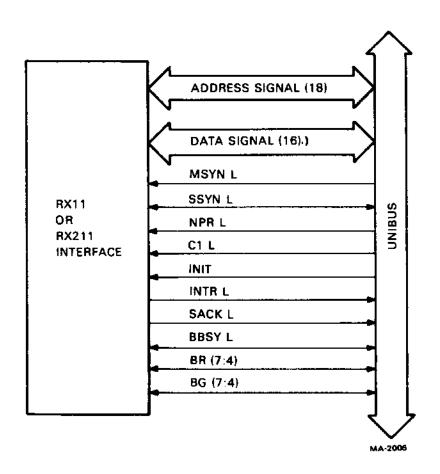

| 5.1.2     | Unibus to RX11/RX211 Interface Signals                | 5-3  |

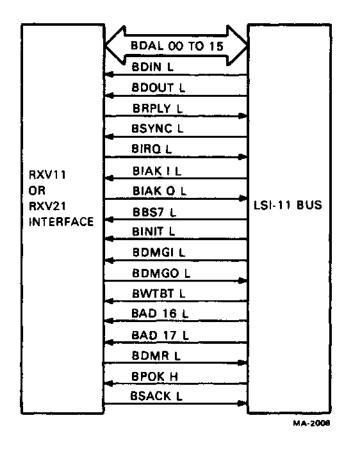

| 5.1.3     | LSI-11 Bus to RXV11/RXV21 Interface Signals           | 5-4  |

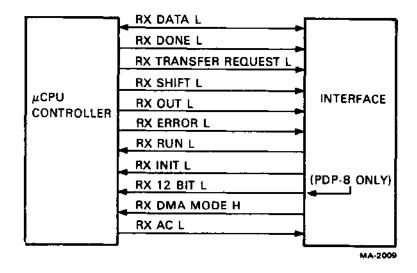

| 5.1.4     | Interface Module to µCPU Controller Signals           |      |

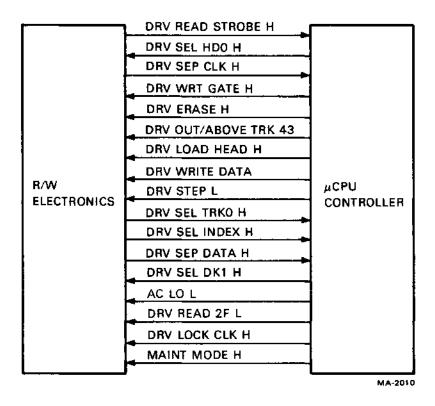

| 5.1.5     | μCPU Controller to Read/Write Electronics Signals     |      |

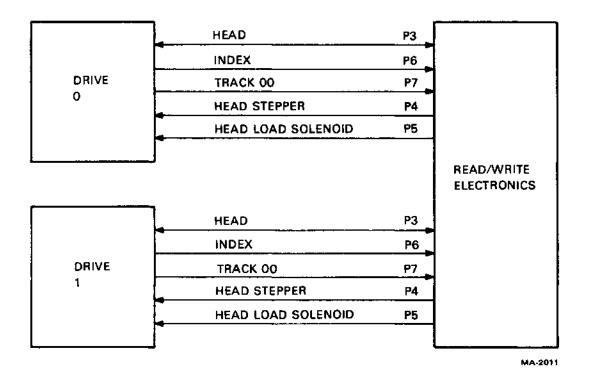

| 5.1.6     | Read/Write Electronics to Drive Signals               |      |

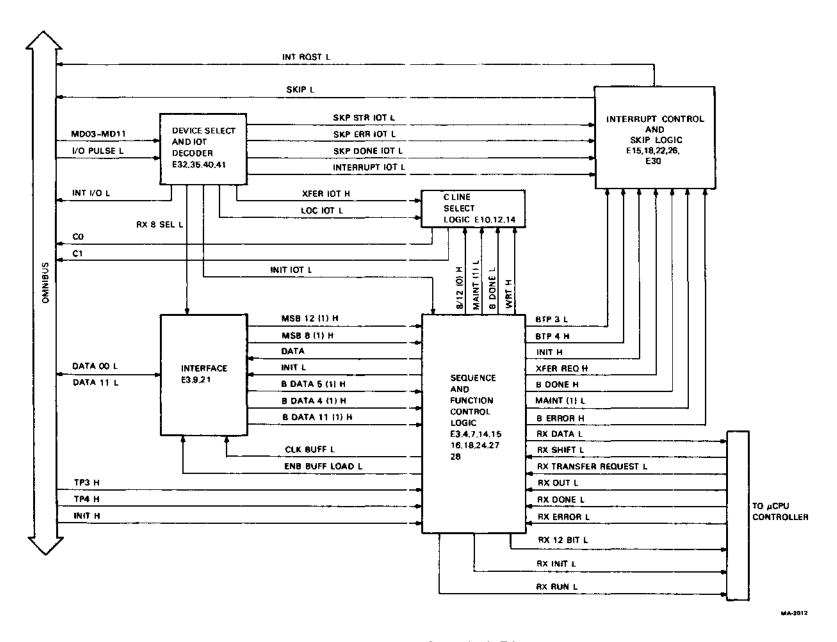

| 5.2       | INTERFACE MODULES BLOCK DIAGRAM DESCRIPTION           | 5-10 |

| 5.2.1     | RX8E/RX28 Interface (M8357) Block Diagram Description |      |

|         |                                                            | Page |

|---------|------------------------------------------------------------|------|

| 5.2.1.1 | Device Select and IOT Decoder                              | 5-10 |

| 5.2.1.2 | Interrupt Control and Skip Logic                           | 5-12 |

| 5.2.1.3 | C Line Select Logic                                        |      |

| 5.2.1.4 | Interface Register                                         |      |

| 5.2.1.5 | Sequence and Function Control Logic                        |      |

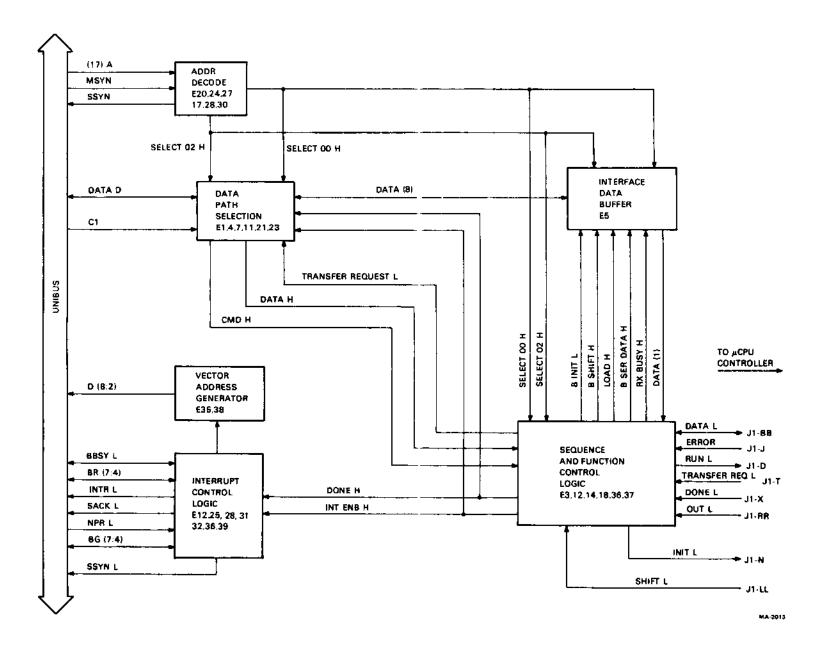

| 5.2.2   | RX11 Interface (M7846) Block Diagram Description           |      |

| 5.2.2.1 | Address Decoder                                            |      |

| 5.2.2.2 | Data Path Selection                                        |      |

| 5.2.2,3 | Interface Data Buffer Register                             |      |

| 5.2.2.4 | Sequence and Function Control Logic                        |      |

| 5.2.2.5 | Interrupt Control Logic                                    |      |

| 5.2,2.6 | Vector Address Generator                                   |      |

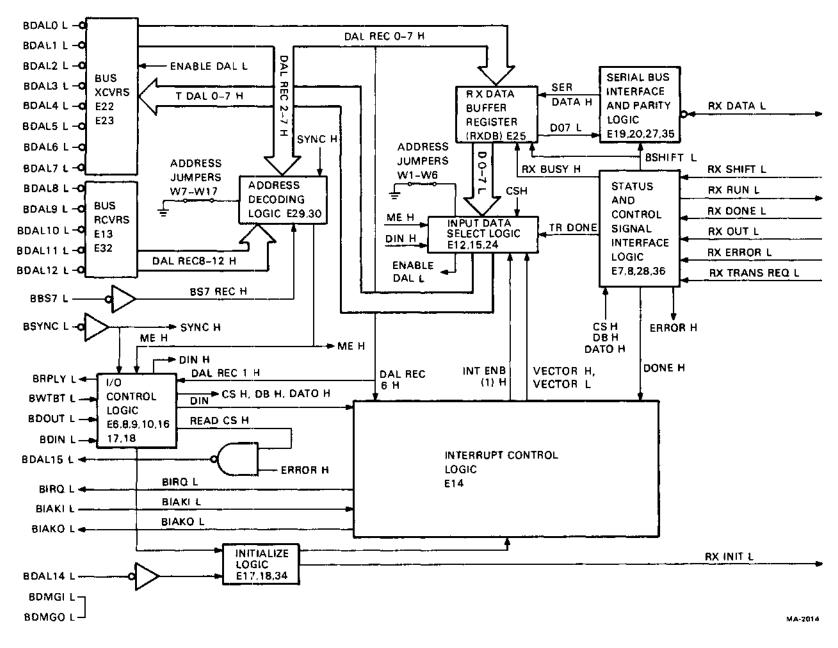

| 5.2.3   | RXV11 Interface (M7946) Block Diagram Description          |      |

| 5.2.3.1 | Address Decoding Logic                                     |      |

| 5,2,3,2 | 1/O Control Logic                                          |      |

| 5.2.3.3 | RX Data Buffer (RXDB) Register                             |      |

| 5.2.3.4 | RX Command/Status (RXCS) Register                          |      |

| 5.2.3.5 | Status and Control Signal Interface Logic                  |      |

| 5.2.3.6 | Interrupt Control Logic                                    |      |

| 5.2.3.7 | Initialize Logic                                           |      |

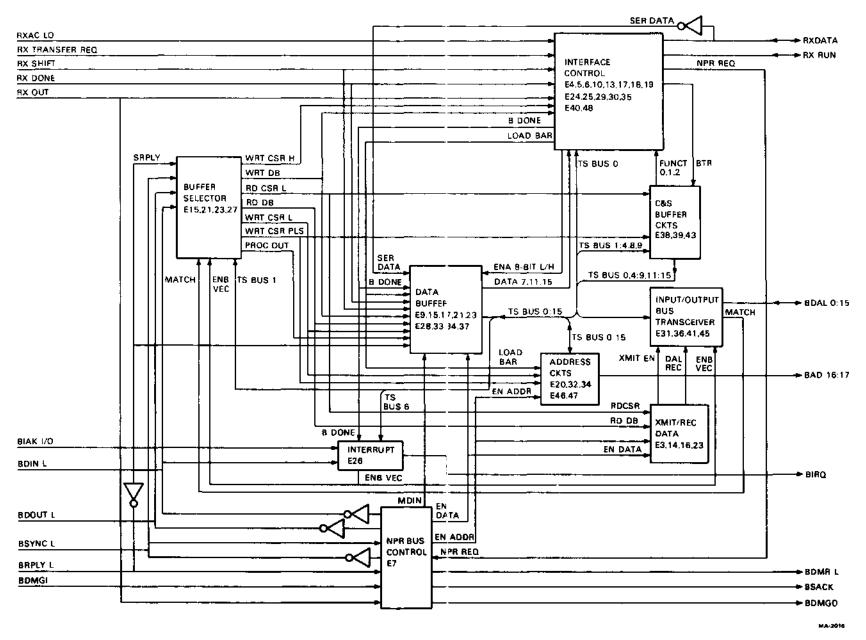

| 5.2.4   | RX211 Interface (M8256) Block Diagram Description          |      |

| 5.2.4.1 | Address Decoder, Buffer Selector, SSYN Register            |      |

| 5.2.4.2 | Command and Status Buffer                                  |      |

| 5.2.4.3 | Data Buffer                                                |      |

| 5.2.4.4 | Data Input/Output and TRANSMIT DATA CIRCUIT                |      |

| 5.2.4.5 | Address Circuits                                           |      |

| 5.2.4.6 | Interface Control Circuits                                 |      |

| 5.2.4.7 | Bus Control Circuits                                       |      |

| 5.2.4.8 | Interrupt Circuits                                         |      |

| 5.2.5   | RXV21 Interface (M8029) Block Diagram Description          |      |

| 5.2.5.1 | Input/Output Transceiver, Buffer Selector                  |      |

| 5.2.5.2 | Command and Status Buffer                                  |      |

| 5.2.5.3 | Data Buffer                                                |      |

| 5.2.5.4 | Input/Output Transceiver and Transmit/Receive Data Circuit |      |

| 5.2.5.5 | Address Circuits                                           |      |

| 5.2.5.6 | Interface Control Circuits                                 |      |

| 5.2.5.7 | Bus Control Circuits                                       |      |

| 5,2.5.8 | Interrupt Circuits                                         |      |

| 5.3     | UNIT LEVEL DESCRIPTION                                     |      |

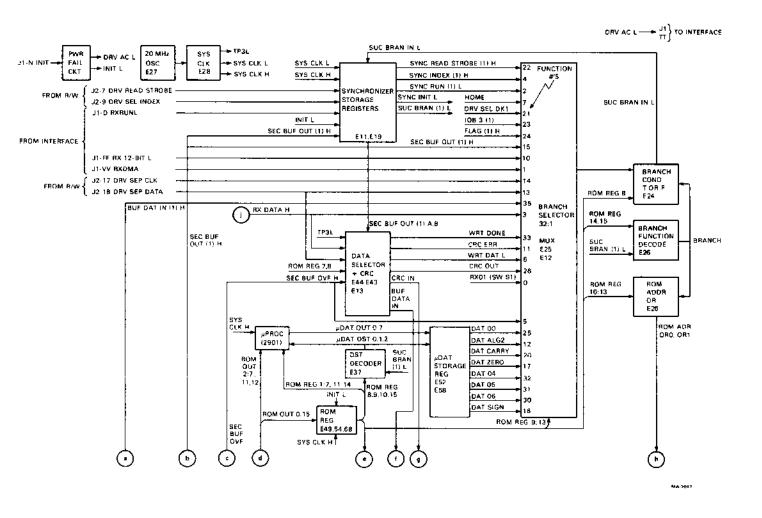

| 5.3.1   | Microprogrammed Controller (M7744) Hardware Description    |      |

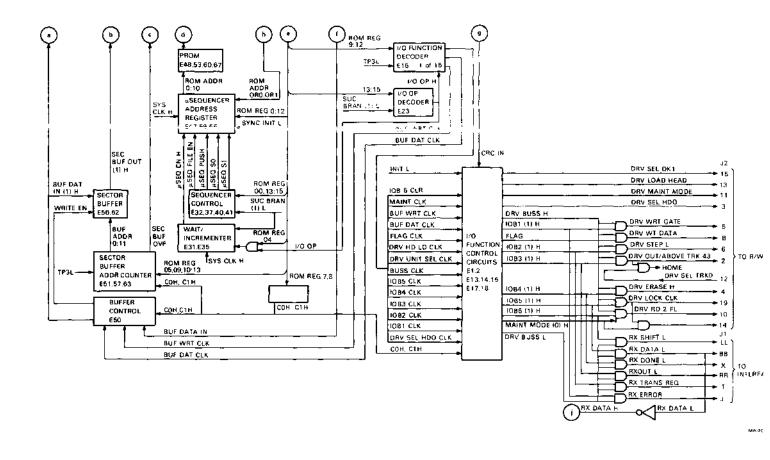

| 5.3.1.1 | PROM, ROM Register, Processor and Sequencer Circuits       |      |

| 5.3.1.2 | Branch Control Circuits                                    |      |

| 5.3.1.3 | I/O Control Circuits                                       |      |

| 5.3.1.4 | Sector Buffer and Control Circuits                         |      |

|                |                                                                      | Page |

|----------------|----------------------------------------------------------------------|------|

| 5.3.1.5        | Data Selection and CRC Circuits                                      | 5-31 |

| 5.3.1.6        | Timing and Synchronizing Circuits                                    | 5-32 |

| 5.3.1.7        | Power Fail Circuit                                                   |      |

| 5.3.2          | Microprogrammed Controller Software Description                      |      |

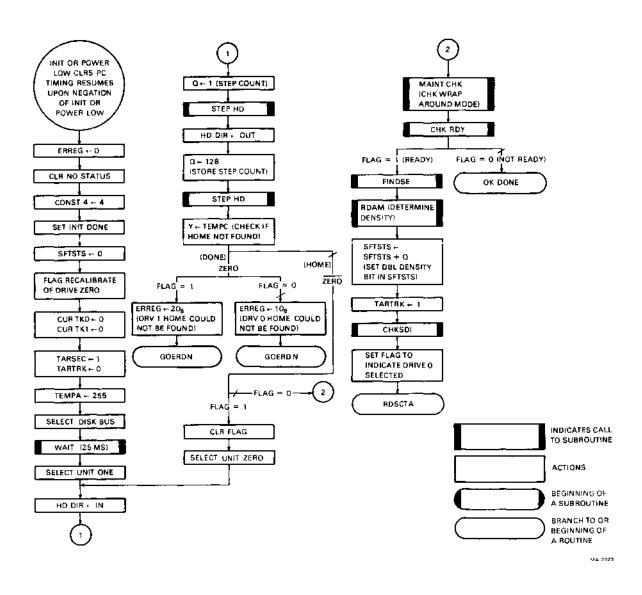

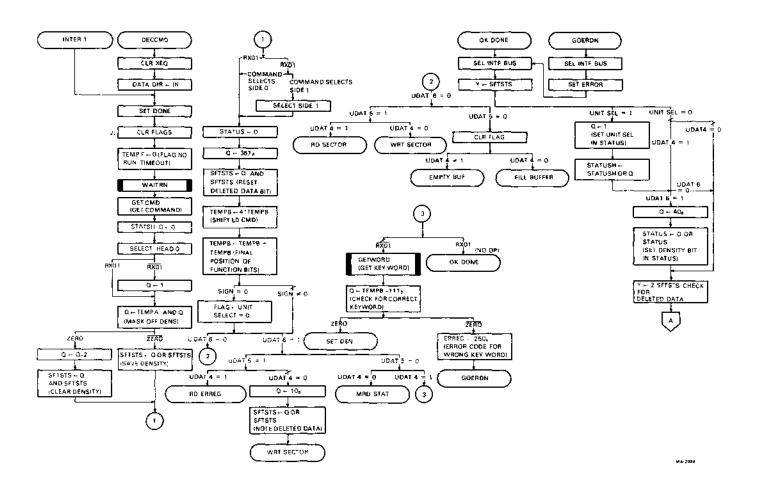

| 5,3,2,1        | Initialize Routine                                                   |      |

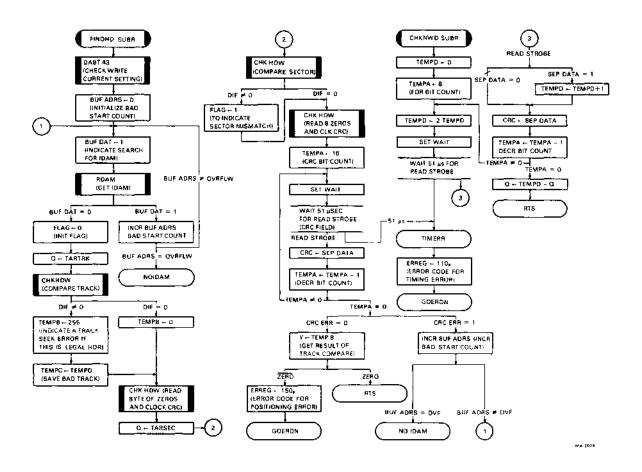

| 5.3.2,2        | Find Header (FIND HD) Subroutine                                     |      |

| 5,3,2,3        | Read Address Mark (RDAM) Subroutine                                  |      |

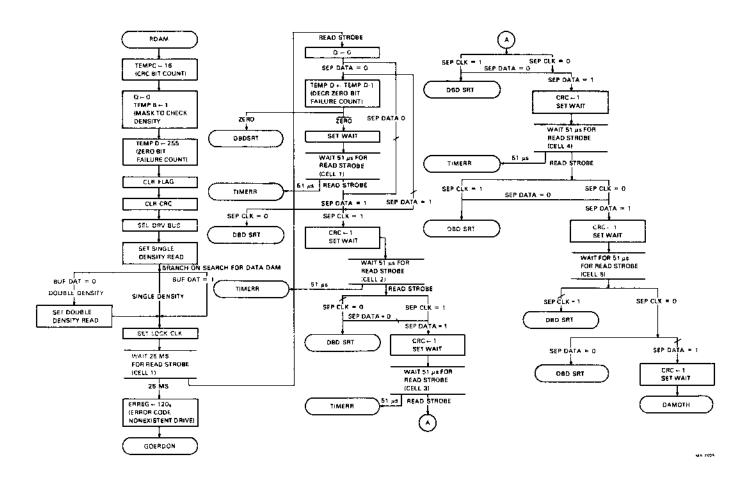

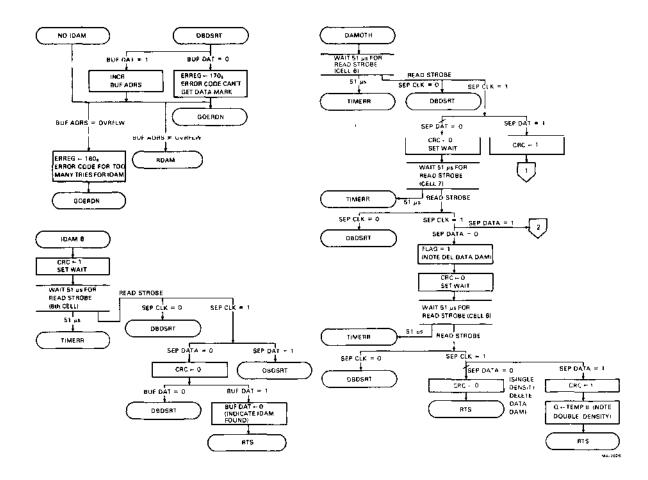

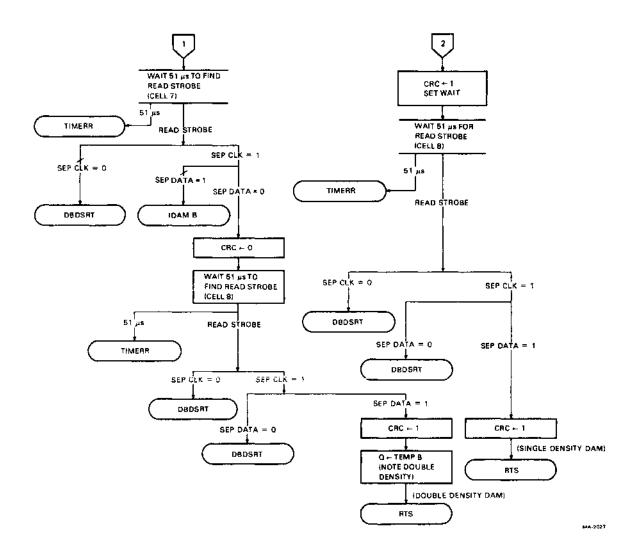

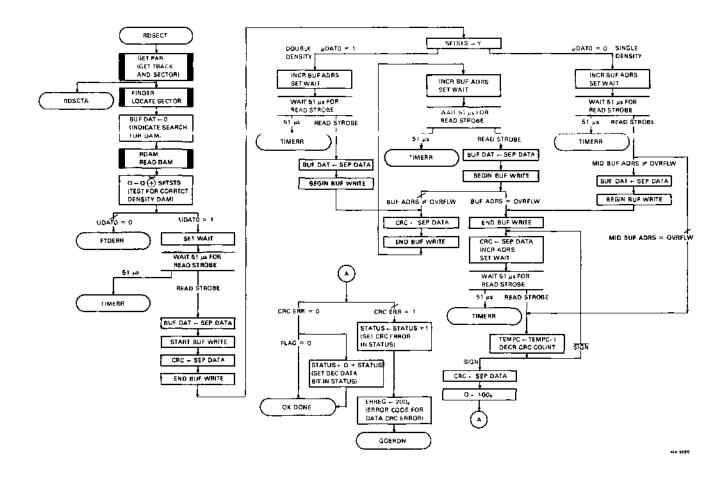

| 5.3.2.4        | Read (RD) Sector Subroutine                                          |      |

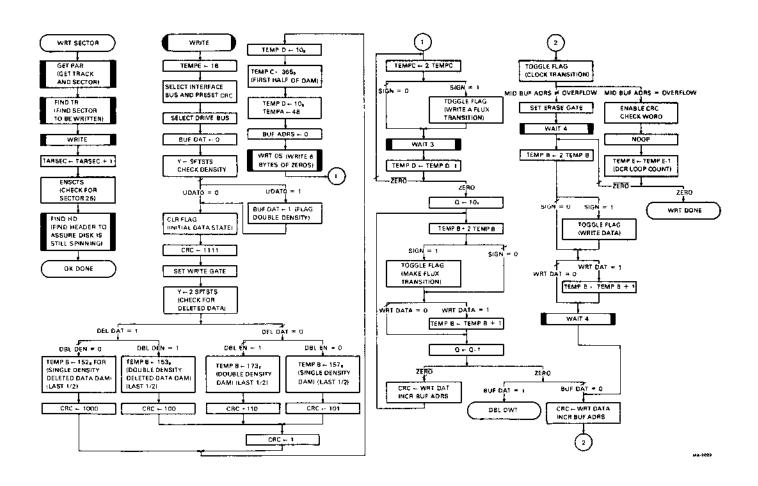

| 5.3.2.5        | Write/Write Sector Subroutine                                        |      |

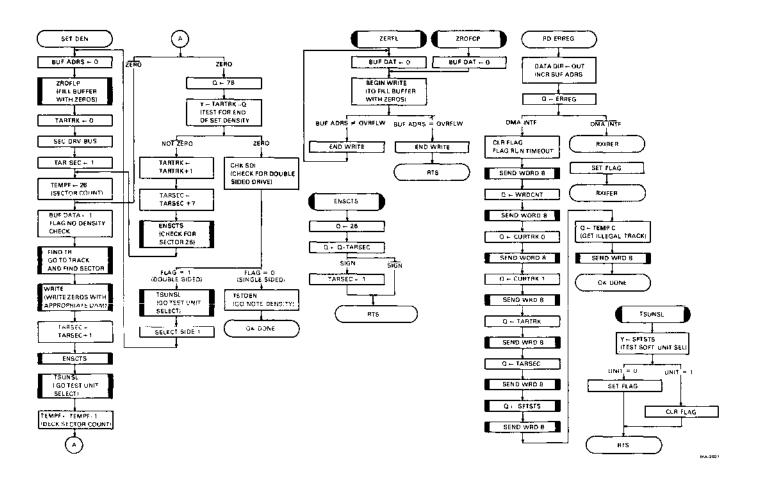

| 5.3.2.6        | Read Error Register (RDERRG) and Set Density (SET DEN)               |      |

| 5 3 <b>3 7</b> | Subroutines                                                          |      |

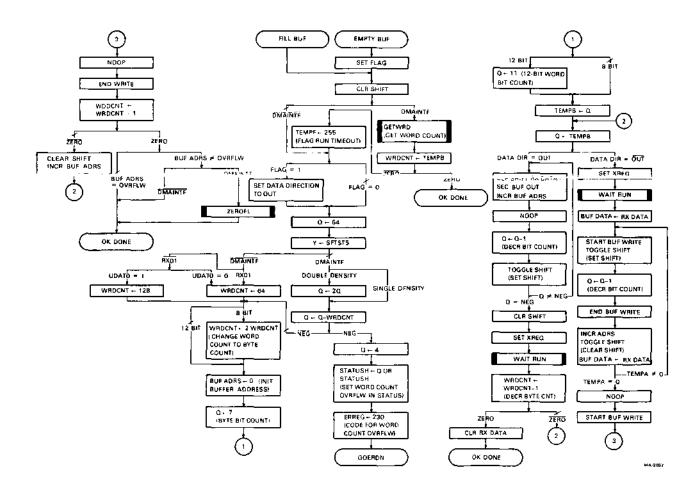

| 5.3.2.7        | Fill/Empty Buffer Routine                                            |      |

| 5.3.2.8        | Find Track Subroutine                                                |      |

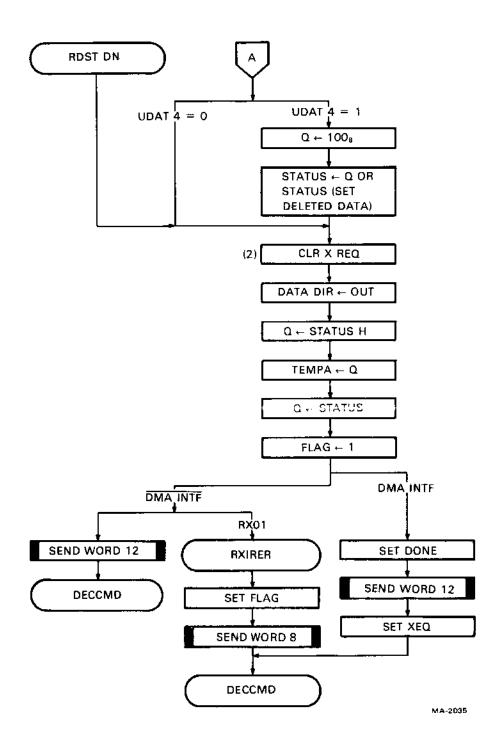

| 5.3.2.9        | Decode Command (DECCMD) Routine                                      | 5-45 |

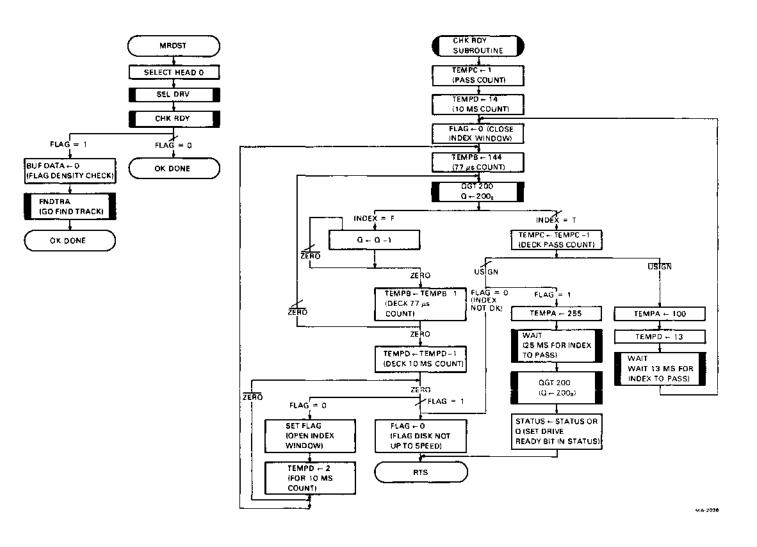

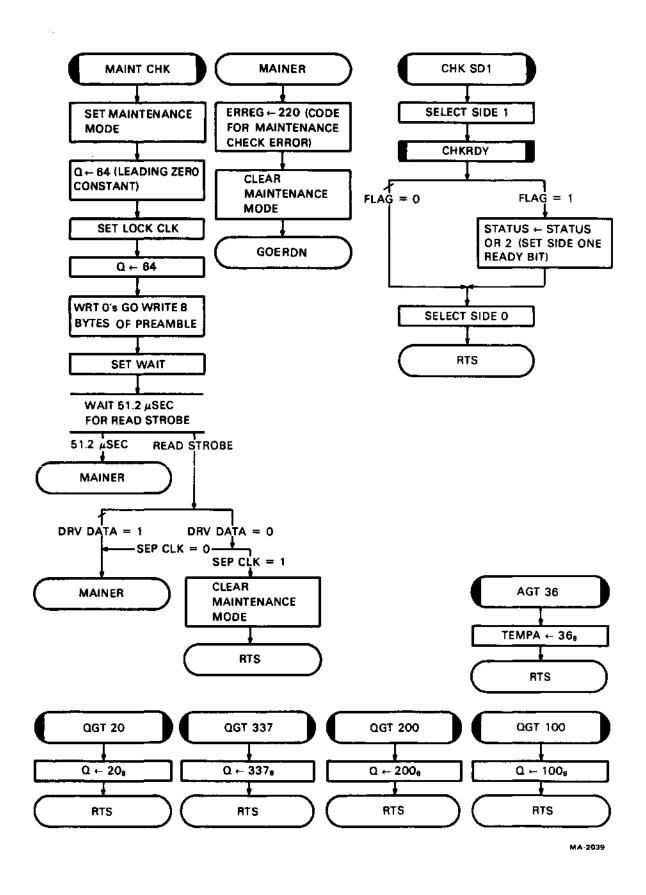

| 5.3.2.10       | Maintenance Read Status (MRDST) and Check Ready (CHKRDY) Subroutines | 5-45 |

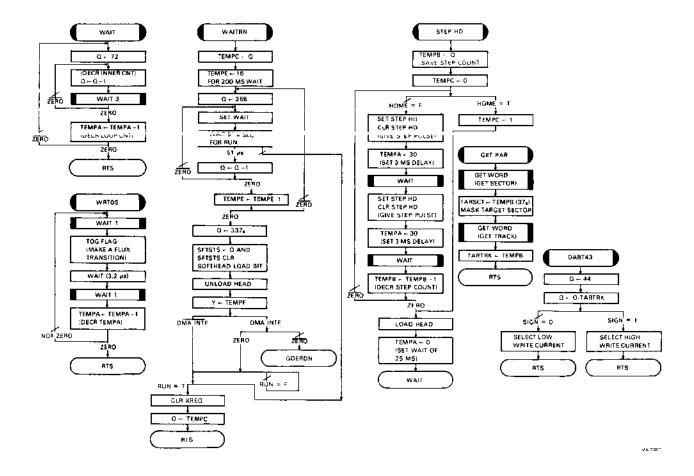

| 5.3.2.11       | Get Parameter (GET PAR), Step Head (STEPHD), Wait,                   |      |

| J.B.2.11       | Wait Run, and Write Zeros (WRTS) Subroutines                         | 5-45 |

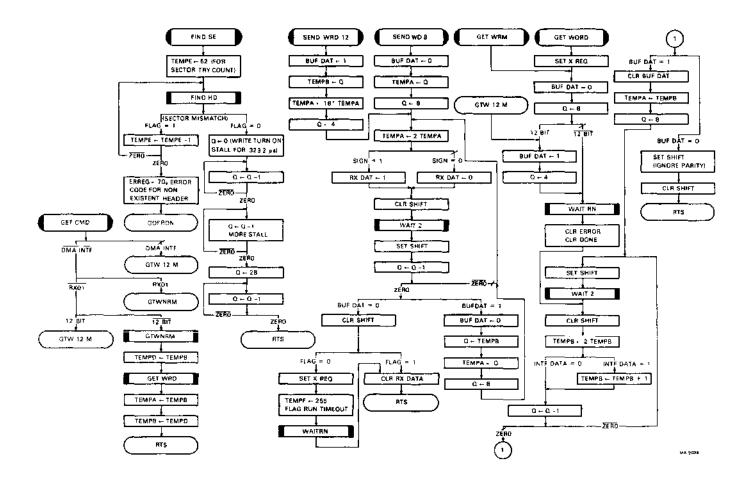

| 5.3.2.12       | Find Sector (FINDSE), Send Word 12 (SNDW12),                         |      |

| 5.5.2.12       | Send Word 8 (SNDW8), Get Command (GET CMD), and                      |      |

|                | Get Word (GET WRD) Subroutines                                       | 5-45 |

| 5.3.2.13       | Maintenance Check Ready (MAINT CHK) Subroutine                       |      |

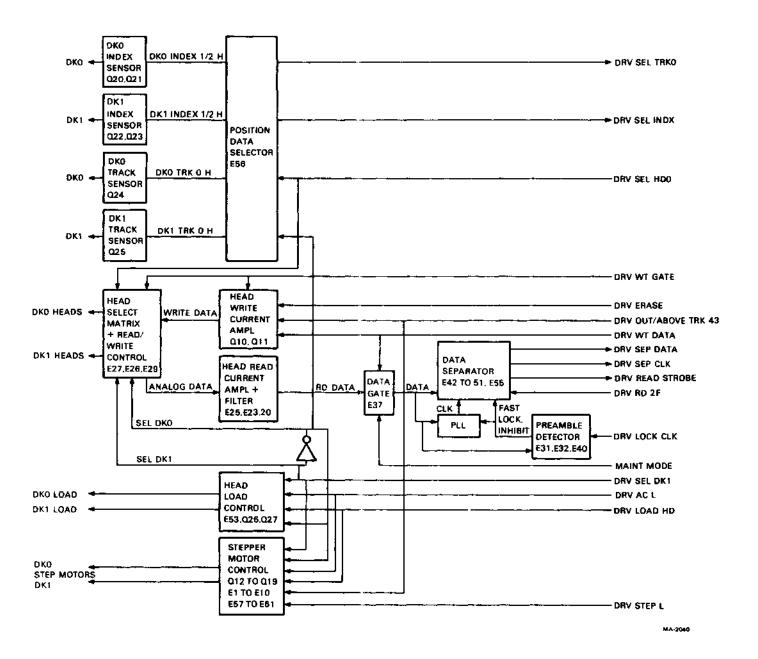

| 5.3.3          | Read/Write Block Diagram Description                                 |      |

| 5.3.3.1        | Drive and Head Control                                               |      |

| 5.3.3.2        | Position Data Selection                                              |      |

| 5,3.3,3        | Read/Write Circuit                                                   |      |

| 5.3.4          | Mechanial Drive Description                                          |      |

| 5.3.4.1        | Drive Mechanism                                                      |      |

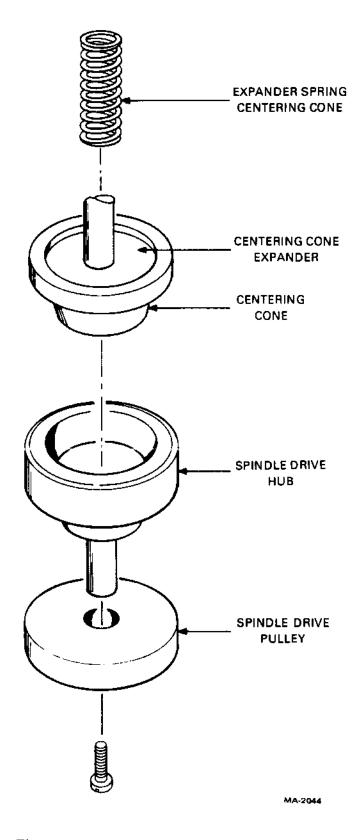

| 5.3.4.2        | Spindle Mechanism                                                    |      |

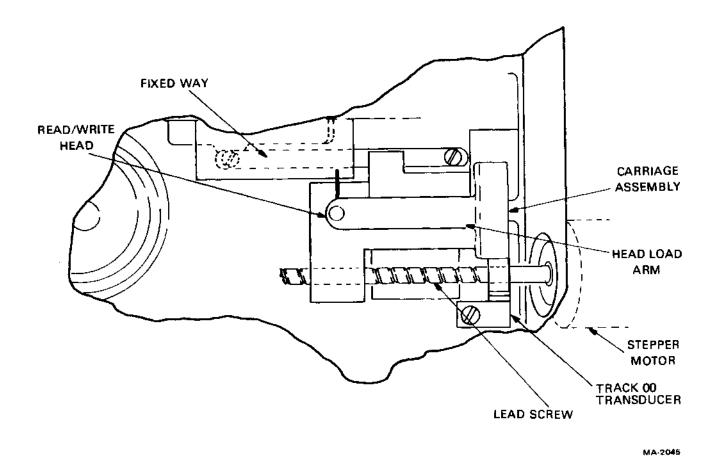

| 5.3.4.3        | Positioning Mechanism                                                |      |

| 5.3.4.4        | Head Load Mechanism                                                  |      |

|                |                                                                      | ەر-ر |

| CHAPTER 6      | MAINTENANCE                                                          |      |

| 6.1            | EQUIPMENT CARE                                                       |      |

| 6.2            | TROUBLESHOOTING THE RX02                                             |      |

| 6.2.1          | M7744, M7745 Failures                                                |      |

| 6.2.2          | Drive Failures                                                       |      |

| 6.3            | TROUBLESHOOTING WITH DIAGNOSTICS                                     |      |

| 6.4            | TROUBLESHOOTING WITHOUT A DIAGNOSTIC                                 |      |

| 6.4.1          | RX211 and RXV21 Systems                                              | 6-2  |

| 6.4.2          | PDP-8 and CM05-8 Based Systems                                       |      |

| 6.5            | REMOVAL AND REPLACEMENT                                              | 6-5  |

| 6.5.1          | Module Replacement Procedures                                        | 6-5  |

6.5.2 6.5.3

6.5.4

6.5.5

Drive Replacement Procedure ......6-8

Front Handle Replacement Procedure......6-8

Drive Motor Replacement Procedures......6-9

Drive Belt Replacement Procedures ......6-10

Page

| 6.5.6      | Quick Check For Belt on Pulleys            | 6-10         |

|------------|--------------------------------------------|--------------|

| APPENDIX A | RX02 SUMMARY                               |              |

|            | FIGURES                                    |              |

| Figure No. | Title                                      | Page         |

| 1-1        | Floppy Disk Configuration                  | 1-3          |

| 1-2        | Front View of the Floppy Disk System       |              |

| 1-3        | Interface Modules                          |              |

| 1-4        | Top View of R X02                          | 1-6          |

| 1-5        | Underside View of Drive                    |              |

| 1-6        | Diskette Media                             | 1-10         |

| 1-7        | Flux Reversal Patterns for FM              | 1-11         |

| 1-8        | FM Versus MFM Encoding                     | 1-12         |

| 1-9        | Track Format (Each Track)                  | 1-12         |

| 1-10       | Sector Format (Each Sector)                | 1-13         |

| 2-1        | RX02 Outline Dimensions                    | 2-1          |

| 2-2        | Cabinet Layout Dimensions                  |              |

| 2-3        | RX02 Rear View                             |              |

| 2-4        | RX02 Unpacking                             | 2-8          |

| 2-5        | RX02 Cabinet Mounting Information          |              |

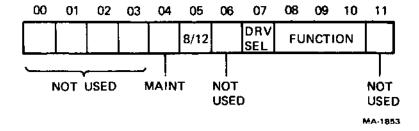

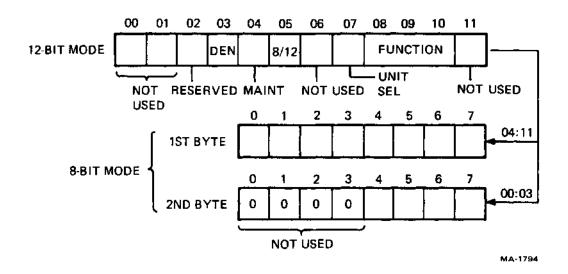

| 4-1        | LCD Word Format (RX8E)                     | <b>.4-</b> 2 |

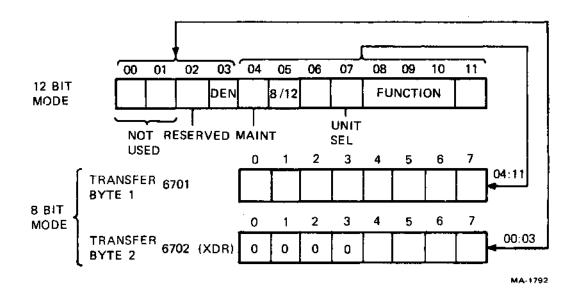

| 4-2        | Command Word Format (RX28)                 |              |

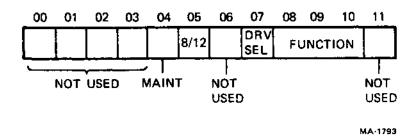

| 4-3        | Command Register Format (RX8E)             | 4-4          |

| 4-4        | Command Register Format (RX28F)            |              |

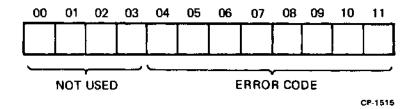

| 4-5        | Error Code Register Format (RX8E/RX28A)    |              |

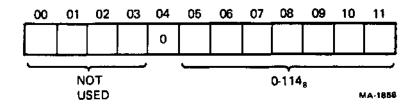

| 4-6        | RX2TA Format (RX8E/RX28)                   | 4-7          |

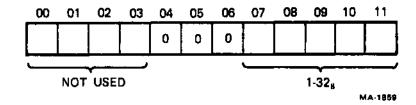

| 4-7        | RX2SA Format (RX8E/RX28)                   | 4-7          |

| 4-8        | RX2DB Format (RX8E/RX28)                   | 4-7          |

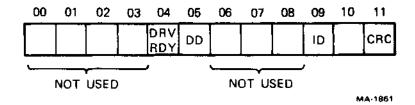

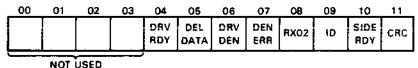

| 4-9        | RXES Format (RX8E)                         |              |

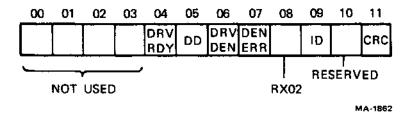

| 4-10       | RX2ES Format (RX28)                        |              |

| 4-11       | RX8E Write/Write Deleted Data/Read Example |              |

| 4-12       | RX8E Empty Buffer Example                  |              |

| 4-13       | RX8E Fill Buffer Example                   |              |

## FIGURES (Cont)

| Figure No. | Title                                             | Page |

|------------|---------------------------------------------------|------|

| 4-14       | RX28 Write/Write Deleted Data/Read Example        | 4-19 |

| 4-15       | RX28 Fill Buffer Example                          | 4-21 |

| 4-16       | RX28 Empty Buffer Example                         | 4-22 |

| 4-17       | RXCS Format (RXI1/RXVI1)                          | 4-25 |

| 4-18       | RXTA Format (RX11/RXV11)                          | 4-26 |

| 4-19       | RXSA Format (RX11/RXV11)                          |      |

| 4-20       | RXDB Format (RX11/RXV11)                          |      |

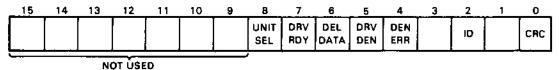

| 4-21       | RXES Format (RX11/RXV11)                          |      |

| 4-22       | RX11/RXV11 Write/Write Deleted Data/Read Example  | 4-32 |

| 4-23       | RX11/RXV11 Empty Buffer Example                   |      |

| 4-24       | RX11/RXV11 Fill Buffer Example                    |      |

| 4-25       | RX2CS Format (RX211/RXV21)                        |      |

| 4-26       | RX2TA Format (RX211/RXV21)                        |      |

| 4-27       | R X2SA Format (R X211/RXV21)                      |      |

| 4-28       | RX2WC Format (RX211/RXV21)                        |      |

| 4-29       | RX2BA and RX2DB Format (RX211/RXV21)              |      |

| 4-30       | RX2ES Format (RX211/RXV21)                        |      |

| 4-31       | RX211/RXV21 Write/Fill Buffer Example             |      |

| 4-32       | RX211/RXV21 Read/Empty Buffer Example             |      |

| 5-1        | RX02 System Block Diagram                         |      |

| 5-2        | Omnibus to RX8E/RX28 Interface Signals            |      |

| 5-3        | Unibus to RX11/RX211 Interface Signals            |      |

| 5-4        | LSI-11 Bus to RXV11/RXV21 Interface Signals       |      |

| 5-5        | Interface to µCPU Controller Signals              |      |

| 5-6        | μCPU Controller to Read/Write Electronics Signals |      |

| 5-7        | Read/Write Electronics to Drive Signals           |      |

| 5-8        | RX8E/RX28 Interface Block Diagram                 |      |

| 5-9        | RX11 Interface Block Diagram                      |      |

| 5-10       | RXVII Interface Block Diagram                     |      |

| 5-11       | RX211 Interface Module Block Diagram              |      |

| 5-12       | RXV21 Interface Module Block Diagram              |      |

| 5-13       | μCPU Controller Block Diagram                     |      |

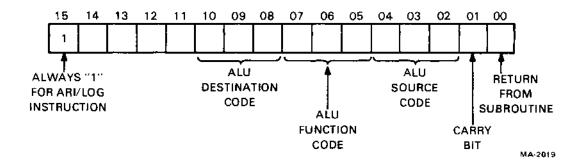

| 5-14       | Arithmetic and Logical Instruction Format         |      |

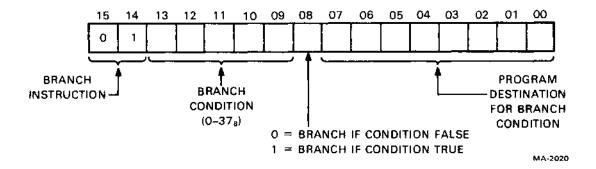

| 5-15       | Branch Instruction Format                         |      |

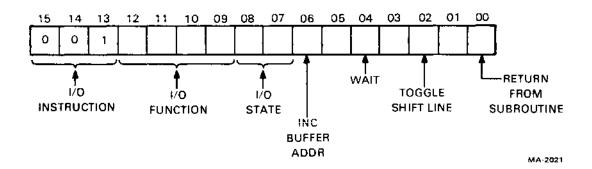

| 5-16       | I/O Instruction Format                            |      |

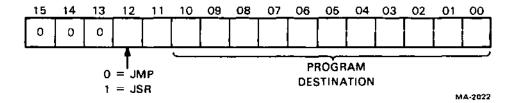

| 5-17       | JMP/JSR Instruction Format                        |      |

| 5-18       | Initialize Routine Flowchart                      |      |

| 5-19       | Find Header Subroutine Flowchart                  |      |

| 5-20       | Read Address Mask Subroutine Flowchart            |      |

| 5-21       | Read Sector Subroutine Flowchart                  |      |

## FIGURES (Cont)

| Figure No. | Title                                                            | Page  |

|------------|------------------------------------------------------------------|-------|

| 5-22       | Write/Write Sector Subroutine Flowchart                          | 5-40  |

| 5-23       | Read Error Register and Set Density Subroutines Flowchart        |       |

| 5-24       | Fill/Empty Buffer Routine Flowchart                              |       |

| 5-25       | Select Drive and Find Track Subroutines Flowchart                |       |

| 5-26       | Decode Command Routine Flowchart                                 | 5-46  |

| 5-27       | Maintenance Read Status and Check Ready Subroutines Flowchart    |       |

| 5-28       | Get Parameter, Step Head, Wait, Wait Run, and Write Zeros        | -     |

|            | Subroutines Flowchart                                            | 5-49  |

| 5-29       | Find Sector, Send Word 12, Send Word 8, Get Command and Get Word | ***** |

|            | Flowchart Subroutines                                            | 5-50  |

| 5-30       | Maintenance Check Ready Subroutine Flowchart                     |       |

| 5-31       | Read/Write Electronics Block Diagram                             |       |

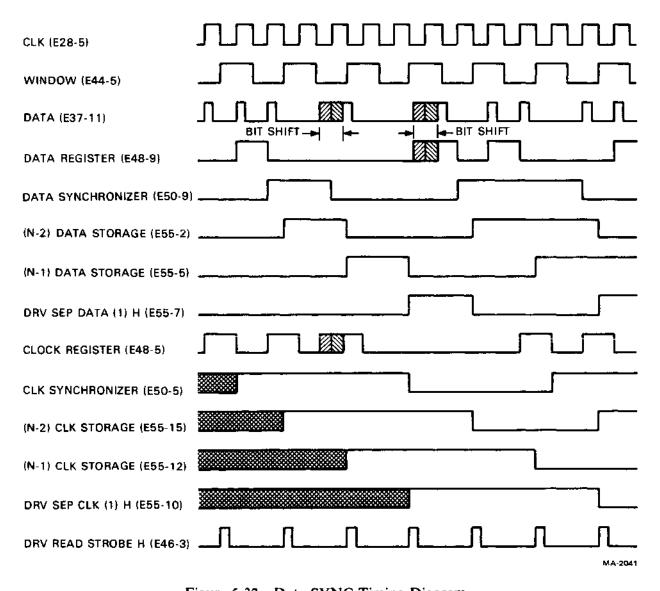

| 5-32       | Data SYNC Timing Diagram                                         |       |

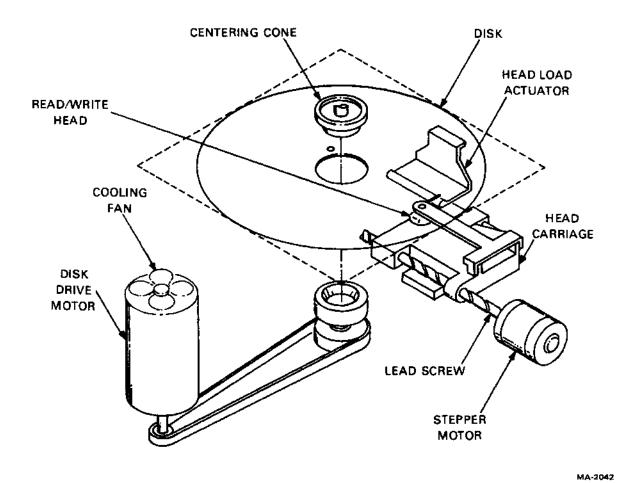

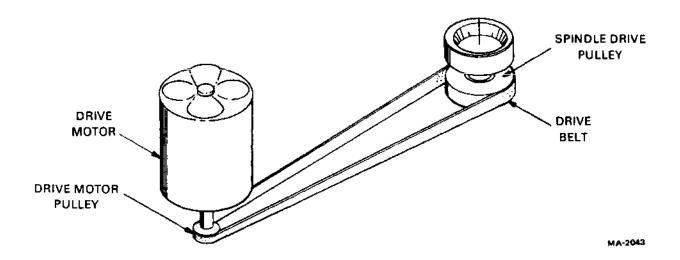

| 5-33       | Disk Drive Mechanical System                                     |       |

| 5-34       | Drive Mechanism                                                  |       |

| 5-35       | Centering Cone and Drive Hub                                     |       |

| 5-36       | Positioning Mechanism                                            |       |

| 6-1        | RX02 Component Location Diagram.                                 |       |

| 6-2        | Drive Motor Positioning Diagram                                  |       |

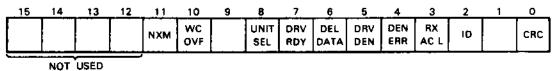

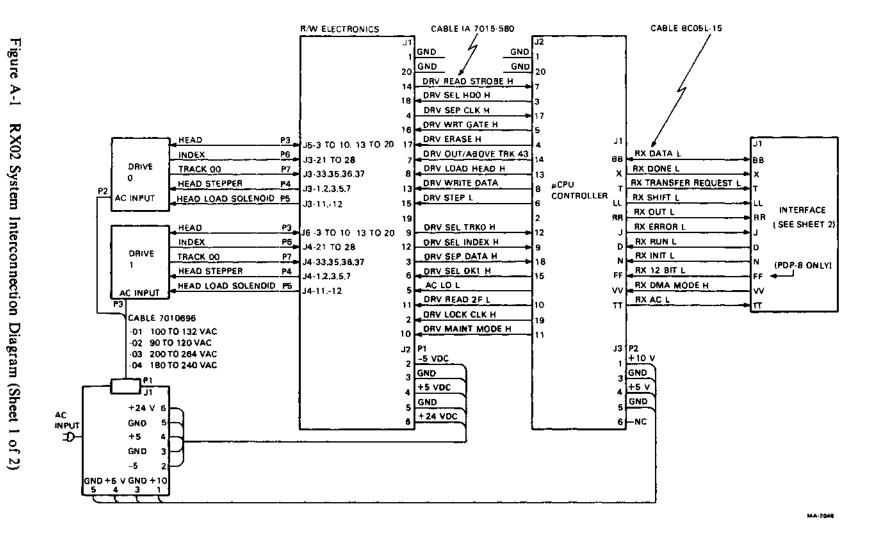

| A-1        | RX02 System Interconnection Diagram                              |       |

| A-I        | K XU2 System Interconnection Diagram                             | A     |

### **TABLES**

| Table No. | Title                                     | Page |

|-----------|-------------------------------------------|------|

| 1-1       | Data Address Mark Code                    | 1-14 |

| 2-1       | RX02 Configurations                       | 2-5  |

| 2-2       | Controller Configuration Switch Positions |      |

| 2-3       | Interface Code/Jumper Configuration       |      |

| 3-1       | Operator Troubleshooting Guide            | 3-3  |

| 4-1       | Device Code Switch Selection              | 4-2  |

| 5-1       | C Line Transfer Control Signals           | 5-13 |

| 6-1       | Troubleshooting Chart                     |      |

| 6-2       | Error Code Probable Causes                |      |

| 6-3       | M7745 Connectors                          |      |

#### **PREFACE**

The manual is intended to provide the user with sufficient information to correctly set up and operate the RX02 Floppy Disk System in any of the various configurations that are available for use with the PDP-8, PDP-11, or LSI-11 computers. The manual presents general, installation, user, programming and maintenance information for the RX02 Floppy Disk System and the interface options associated with the PDP-8, PDP-11, and LSI-11 computer systems.

## CHAPTER 1 GENERAL INFORMATION

#### 1.1 INTRODUCTION

The RX02 is a low cost, random access mass memory device that stores data in fixed length blocks on flexible diskettes with preformatted industry standard headers. The RX02 interfaces with either a PDP-8, a PDP-11, or an LSI-11 system. Various interface modules are selected according to the computer being used and either single or double density recording. The various configurations are:

| Designation | Computer | Interface<br>Module | Recording<br>Density |

|-------------|----------|---------------------|----------------------|

| RX8E        | PDP-8    | M8357               | Single               |

| RX28        | PDP-8    | M8357               | Single or Double     |

| RXII        | PDP-11   | M7846               | Single               |

| RX211       | PDP-11   | M8256               | Single or Double     |

| RXVI1       | LSI-11   | M7946               | Single               |

| RXV21       | LSI-11   | M8029               | Single or Double     |

#### NOTE

The single density recording configurations RX8E, RX11, and RXV11 are compatible with the RX01 Floppy Disk System when the M7744 controller module has been switched to be compatible with these configurations. (See Table 2-2.)

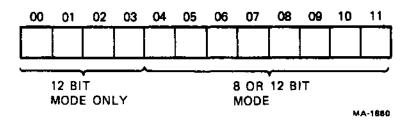

The RX02 consists of one or two flexible disk drives, a single read/write electronics module, a microprogrammed controller module, and a power supply, enclosed in a rack-mountable, 10-1/2 inch, self-cooled chassis. A cable is included for connection to either a PDP-8 interface module, a PDP-11 interface module, or an LSI-11 interface module. The amount of data that can be stored on the RX02 varies according to the configuration. For each drive system using double density recording, up to 512K 8-bit bytes of data (PDP-8, PDP-11, LSI-11) or 256K 12-bit words (PDP-8) can be stored and retrieved. For each drive system using single density recording, up to 256K 8-bit bytes of data or 128 12-bit words (PDP-8) can be stored and retrieved. The RX02 interfaces with IBM-compatible devices when single density data recording is used. If two drives are used, the recording density can be different for each drive.

For single or double density recording, the RX02 is used with either an M8357 interface module (PDP-8), an M8256 interface module (PDP-11), or an M8029 interface module (LSI-11). The interface modules convert the RX02 I/O bus to the bus structure of the computer being used. Each module controls the interrupts to the CPU initiated by the RX02 and handles the data interchange between the RX02 and the host computer. Each interface module is powered by the host processor.

In addition, the RX02 is used for single density recording when it is configured to be compatible with the RX01. The interface module used is either an M8357 (PDP-8), an M7846 (PDP-11), or an M7946 (LSI-11).

To record or retrieve data the RX02 performs implied seeks. Given an absolute sector address, the RX02 locates the desired sector and performs the indicated function, including automatic head position verification and hardware calculation and verification of the cyclic redundancy check (CRC) character. The CRC character that is read and generated is compatible with IBM 3740 equipment.

#### 1.2 GENERAL DESCRIPTION

An RX02 Floppy Disk System consists of the following components:

M7744 Controller Module

M7745 Read/Write Electronics Module

H771-A, -C, or -D Power Supply

RX02-CA Floppy Disk Drive (60 Hz max of 2)

RX02-CC Floppy Disk Drive (50 Hz max of 2)

One interface module is used:

M8357 (PDP-8, Programmed I/O)

M7846 (PDP-11, Programmed I/O)

M7946 (LSI-11, Programmed I/O)

M8029 (LSI-11 with DMA)

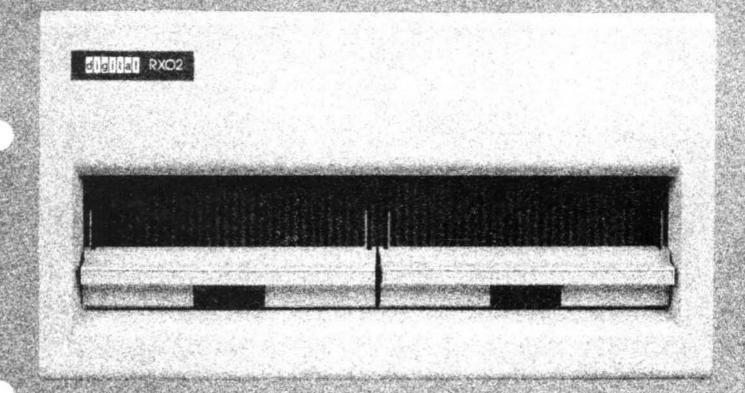

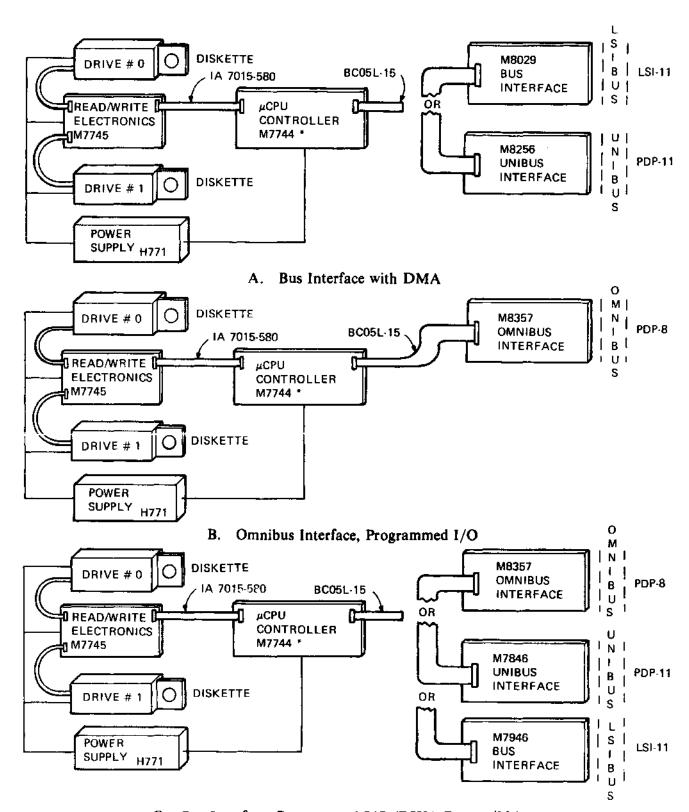

All components except the interface modules are housed in a 10-1/2 inch rack-mountable box. The power supply, M7744 module, and M7745 module are mounted above the drives. Interconnection from the RX02 to the interface is with a 40-conductor BC05L-15 cable of standard length (15 ft). Figure 1-1 is a configuration drawing of the system: part A shows the configuration for a bus interface with DMA; part B shows the configuration for all Omnibus interfaces (programmed I/O); part C shows the configuration for a bus interface (programmed I/O) that is RX01 compatible. Figure 1-2 is a front view of a dual drive system.

#### 1.2.1 Interface Modules

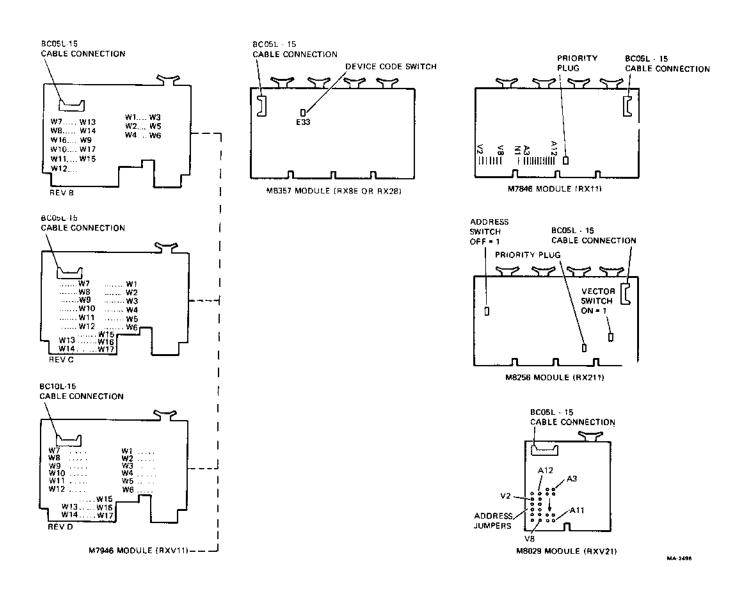

The interface modules plug into a slot on the bus for PDP-8, PDP-11, and LSI-11 computers. Figure 1-3 shows the outline of the various modules and areas of interest on each module.

#### 1.2.2 Microprogrammed Controller

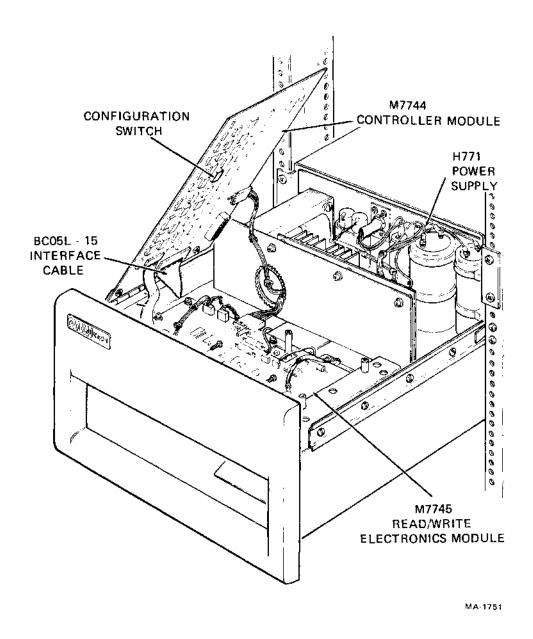

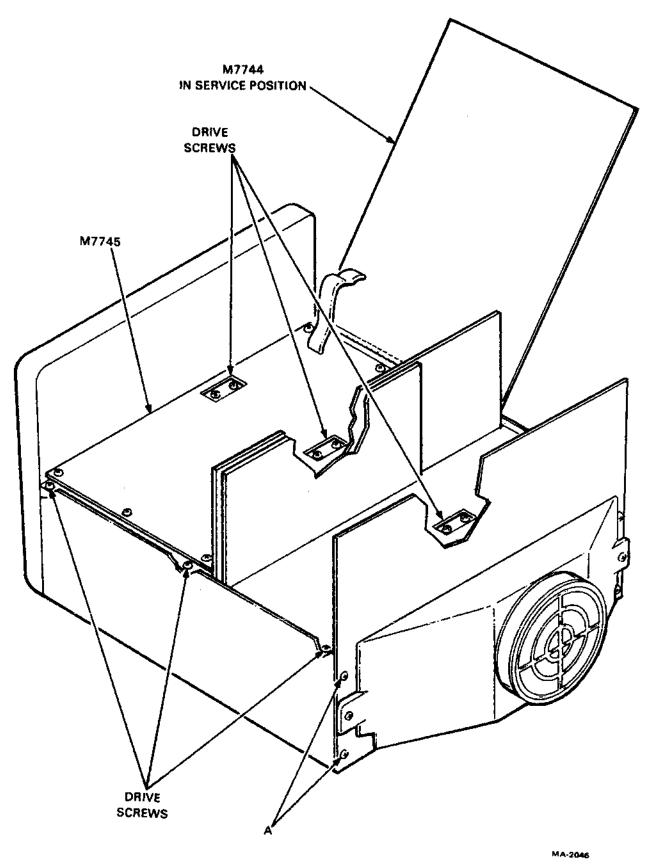

The M7744 microprogrammed controller module is located in the RX02 cabinet as shown in Figure 1-4. The M7744 is hinged on the left side and lifts up for access to the M7745 read/write electronics module.

#### 1.2.3 Read/Write Electronics

The M7745 read/write electronics module is located in the RX02 cabinet as shown in Figure 1-4.

#### 1.2.4 Electromechanical Drive

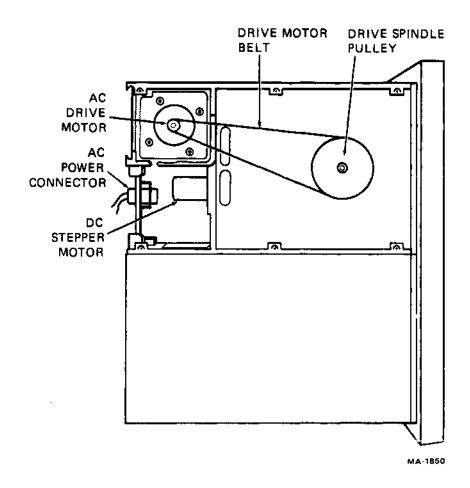

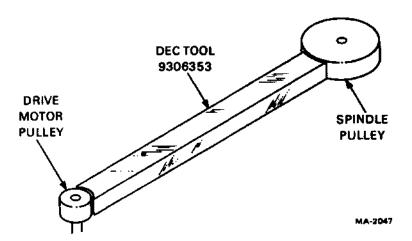

A maximum of two drives can be attached to the read/write electronics. The electromechanical drives are mounted side by side under the read/write electronics board (M7745). Figure 1-5 is an underside view of the drive showing the drive motor connected to the spindle by a belt. (This belt and the drive pulley are different on the 50 Hz and 60 Hz units; see Paragraph 2.1.3.2 for complete input power modification requirements.)

C. Bus Interface, Programmed I/O (RX01 Compatible)

Figure 1-1 Floppy Disk Configuration

MA-1824

Figure 1-2 Front View of the Floppy Disk System

#### 1.2.5 Power Supply

The H771 power supply is mounted at the rear of the RX02 cabinet as shown in Figure 1-4. The H771-A is rated at 60 Hz  $\pm 1/2$  Hz over a voltage range of 90-128 Vac. The H771-C and -D are rated at 50 Hz + 1/2 Hz over four voltage ranges:

```

90-120 Vac

100-128 Vac } 3.5 A circuit breaker; H771-C

184-240 Vac } 1.75 A circuit breaker; H771-D

```

Two configuration plugs are provided to adapt the H771-C or -D to each voltage range. This is not applicable to the H771-A.

#### 1.3 OPTION DESCRIPTION

The optional interface modules that are used to interface the RX02 with a PDP-8, PDP-11, and LSI-11 are listed in Paragraphs 1.1 and 1.2. (Each module is powered by the host processor.) The module selected is determined by the computer being used and whether the data interchange is between either IBM system 3740 compatible devices or DIGITAL system double density devices. Also, when an M7744 controller module's configuration switch is set to be compatible, the RX02 can operate as an RX01. The RX02 interfaces with IBM compatible devices when single density data recording is used. The RX02 interfaces with DIGITAL system double density recording devices when the controller module configuration switch is positioned to be compatible with RX28, RX211, and RXV21 configurations.

Figure 1-3 Interface Modules

Figure 1-4 Top View of RX02

#### 1.3.1 Operation For Single Density Recording Only (RX8E, RX11, RXV11)

- 1.3.1.1 PDP-8 Operation The RX02 connects to the M8357 Omnibus interface module. This module converts the RX02 I/O bus to PDP-8 family Omnibus structure. It controls interrupts to the CPU initiated by the RX02, controls data interchange between the RX02 and the host CPU by programmed I/O, and handles input/output transfers used for maintenance status conditions.

- 1.3.1.2 PDP-11 Operation The RX02 connects to the M7846 Unibus interface module. This module converts the RX02 I/O bus to PDP-11 Unibus structure. It controls interrupts to the CPU initiated by the RX02, decodes Unibus addresses for register selection, and handles data interchange between the RX02 and the host CPU main memory by programmed I/O.

1-6

Figure 1-5 Underside View of Drive

1.3.1.3 LSI-11 Operation – The RX02 connects to the M7946 LSI-11 bus interface module. This module converts the RX02 I/O bus to the LSI-11 bus structure. It controls interrupts to the CPU initiated by the RX02, decodes LSI-11 bus addresses for register selection, and transfers data between the RX02 and the host CPU main memory by programmed I/O.

#### 1.3.2 Operation For Single or Double Density Recording (RX28, RX211, RXV21)

- 1.3.2.1 PDP-8 Operation The RX02 connects to the M8357 Omnibus interface module. This module converts the RX02 I/O bus to PDP-8 family Omnibus structure. It controls interrupts to the CPU initiated by the RX02, controls transfer of data between the RX02 and host CPU by programmed I/O, and handles input/output transfer used to test status conditions.

- 1.3.2.2 PDP-11 Operation The RX02 connects to the M8256 Unibus interface module. This module converts the RX02 I/O bus to PDP-11 Unibus structure. It controls interrupts to the CPU initiated by the RX02, decodes Unibus addresses for register selection, and initiates NPR requests to transfer data between the RX02 and the host CPU main memory.

- 1.3.2.3 LSI-11 Operation The RX02 connects to the M8029 LSI-11 bus interface module. This module converts the RX02 I/O bus to the LSI-11 bus structure. It controls interrupts to the CPU initiated by the RX02, decodes LSI-11 bus addresses for register selection, and initiates NPR requests to transfer data between the RX02 and the host CPU main memory.

#### 1.4 SPECIFICATIONS

System Reliability

Minimum number of revo-

lutions per track

Seek error rate

Soft data error rate Hard data error rate 3 million/media (head loaded)

1 in 106 seeks

1 in 109 bits read or written

1 in 1012 bits read or written

#### NOTE

The above error rates only apply to DEC approved media that is properly cared for. Seek error and soft data errors are usually attributable to random effects in the head/media interface, such as electrical noise, dirt, or dust. Both are called "soft" errors if the error is recoverable in 10 additional tries or less. "Hard" errors cannot be recovered. Seek error retries should be preceded by a recalibrate.

#### Drive Performance

| Capacity     | Recording | 8-bit bytes | 12-bit words |

|--------------|-----------|-------------|--------------|

| Per diskette | FM        | 256,256     | 128,128      |

|              | MFM       | 512,512     | 256,256      |

| Per track    | FM        | 3,328       | 1,664        |

|              | MFM       | 6,656       | 3,328        |

| Per sector   | FM        | 128         | 64           |

|              | MFM       | 256         | 128          |

Data transfer rate

Diskette to controller buffer

4 μs/data bit (FM) 2 μs/data bit (MFM)

Buffer to CPU interface

$1.2 \,\mu s/bit$

#### NOTE

#### PDP-8 interface can operate in 8- or 12-bit modes under software control.

Track-to-track move 6 ms/track maximum Head settle time 25 ms maximum Rotational speed 360 rpm  $\pm$  2.5%; 166 ms/rev nominal

Recording surfaces per disk

Tracks per disk Sectors per track Recording technique

Bit density maximum on

inner track

Track density

Average access

77 (0-76) or (0-114<sub>8</sub>)

26 (1-26) or (0-32<sub>8</sub>)

Double frequency (FM) or modified MFM

3200 bpi (FM) or modified (MFM)

48 tracks/inch

262 ms, computed as follows:

Seek Settle Rotate 77 tks/3 ×6 ms + + 166 ms/2 = 262 ms25 ms

#### **Environmental Characteristics**

#### Temperature

RX02, operating 15° to 32° C (59° to 90° F) ambient:

maximum temperature gradient = 11° C/hr (20° F/hr)

RX02, nonoperating  $-35^{\circ}$  to  $+60^{\circ}$  C ( $-30^{\circ}$  to  $+140^{\circ}$  F)  $-35^{\circ}$  to  $+52^{\circ}$  C ( $-30^{\circ}$  to  $+125^{\circ}$  F) Media, nonoperating

#### NOTE

#### Media temperature must be within operating temperature range before use.

Heat Dissipation (RX02 System)

Less than 225 Btu/hr

Relative humidity

RX02, operating 25° C (77° F) maximum wet bulb

2° C (36° F) minimum dew point 20% to 80% relative humidity

RX02, nonoperating

5% to 98% relative humidity (no condensation)

Media, nonoperating

10% to 80% relative humidity

Magnetic field

Media exposed to a magnetic field strength of 50 oersteds or

greater may lose data.

Interface modules

Operating temperature

5° to 50° C (41° to 122° F)

Relative humidity Maximum wet bulb

10% to 90% 32° C (90° F)

Minimum dew point

2° C (36° F)

#### Electrical

Power consumption

RX02 5 A at +5 Vdc, 25 W; 0.14 A at -5 Vdc, 0.7 W; 1.3 A t +24 Vdc,

31 W

PDP-11 interface (M7846,

1.8 A at 5 Vdc

M8256)

PDP-8 interface (M8357)

1.5 A at 5 Vdc

LSI-11 interface (M7946,

1.8 A at 5 Vdc

M8029)

4 A at 115 Vac AC power

2 A at 230 Vac

#### 1.5 SYSTEMS COMPATIBILITY

This section describes the physical, electrical, and logical aspects of compatibility for data interchange with IBM system 3740 devices and for data interchange with double density devices.

#### 1.5.1 Media

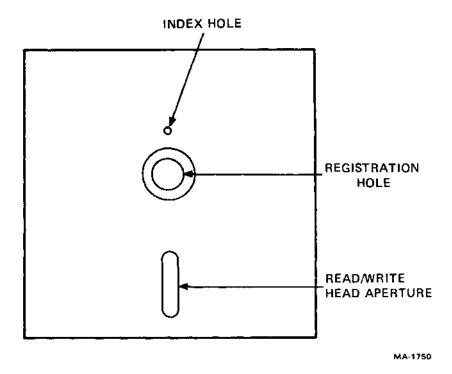

The media used on the RX02 Floppy Disk system is compatible with the IBM 3740 family of equipment and is shown in Figure 1-6. The "diskette" media was designed by applying tape technology to disk architecture, resulting in a flexible oxide-on-mylar surface. The diskette is encased in a plastic envelope with a hole for the read/write head, a hole for the drive spindle hub, and a hole for the hard index mark. The envelope is lined with a fiber material that cleans the diskette surface. The media is supplied to the customer preformatted and pretested.

Figure 1-6 Diskette Media

#### 1.5.2 Recording Scheme

There are two recording schemes used in the RX02: double frequency (FM) and modified Miller code (MFM). The FM scheme is used for single density data recording which is compatible with IBM system 3740 devices. (When this recording scheme is used and the RX02 is configured as shown in Figure 1-1 part C, the RX02 is compatible with the RX01.) The MFM scheme is used for double density data recording which is compatible with DIGITAL double density devices but is not compatible with other manufacturers.

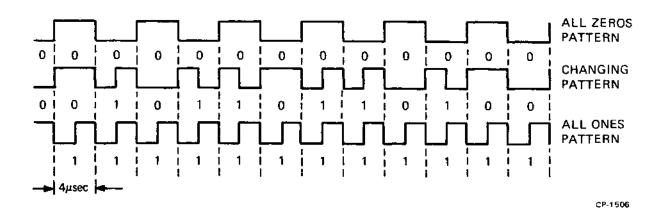

1.5.2.1 Double Frequency (FM) – For the double frequency recording scheme data is recorded between bits of a constant clock stream. The clock stream consists of a continuous pattern of one flux reversal every four  $\mu$ s (Figure 1-7). A data "one" is indicated by an additional reversal between clocks (i.e., doubling the bit stream frequency; hence the name). A data "zero" is indicated by no flux reversal between clocks.

A continuous stream of ones, shown in the bottom waveform in Figure 1-7, would appear as a "2F" bit stream, and a continuous stream of zeros, shown in the top waveform in Figure 1-7, would appear as a "IF" or fundamental frequency bit stream.

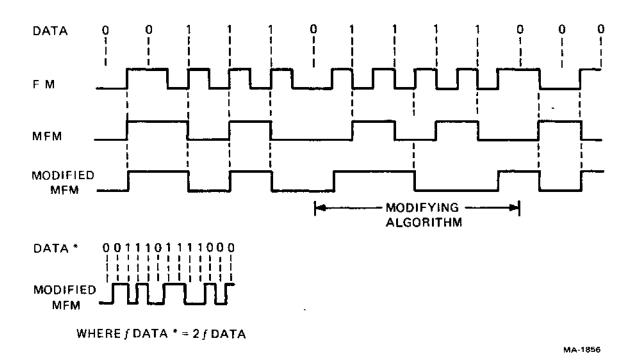

1.5.2.2 Miller Code (MFM) - MFM or Miller code encodes clocks between data bits of a continuous data stream. The data stream consists of flux reversals for a data "one" and no flux reversal for a data "zero." A clock is recorded only between data "zeros." Because it is possible to have double density data fields map into a preamble and ID mark, the MFM encoding is modified slightly to prevent a false header from being detected within a double density data field.

#### NOTE

The modified MFM encoding is not compatible with other manufacturers.

Figure 1-7 Flux Reversal Patterns for FM

The encoding algorithms for implementing modified MFM are:

Encoding Algorithm #1 (MFM or Miller Code Algorithm)

|    | Data   | Encoded |    |        |

|----|--------|---------|----|--------|

| Dn | Dn + 1 | Dn      | Cn | Dn + 1 |

| 0  | 0      | 0       | 1  | 0      |

| ì  | 0      | ] 1     | Ū  | j o    |

| 0  | 1      | 0       | 0  | 1      |

| 1  | 1      | 1       | 0  | 1      |

Encoding Algorithm #2 (MFM Modified Algorithm)

| Data |        |        |        |        |        |  |  |

|------|--------|--------|--------|--------|--------|--|--|

| Dn   | Dn + 1 | Dn + 2 | Dn + 3 | Dn + 4 | Dn + 5 |  |  |

| 0    | 1      | 1      | 1      | 1      | 0      |  |  |

|    | Encoded Data |        |        |        |        |        |        |        |        |        |

|----|--------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Dn | Cn           | Dn + 1 | Cn + 1 | Dn + 2 | Cn + 2 | Dn + 3 | Cn + 3 | Dn + 4 | Cn + 4 | Dn + 5 |

| 0  | 1            | 0      | 0      | 0      | 1      | 0      | 0      | 0      | 1      | 0      |

The decoding algorithm used in data separation is:

|    | Encoded | Decoded |     |        |

|----|---------|---------|-----|--------|

| Dn | Cn      | Dn + 1  | Dn  | Dn + 1 |

| 0  | 0       | 0       | 1   | 1      |

| 0  | i       | 0       | 0   | 0      |

| !  | 0       | 0       | 1   | 0      |

| 0  | 0       | ł       | 0   | j      |

| 1  | 0       | 1       | ] 1 | ì      |

Figure 1-8 shows the waveforms that are generated for a data stream of zeros and ones when FM code, MFM code, and modified MFM code are used.

#### 1.5.3 Logical Format

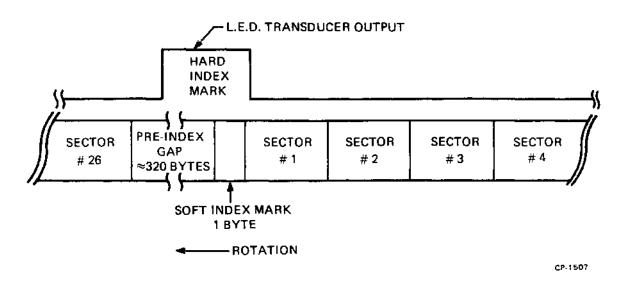

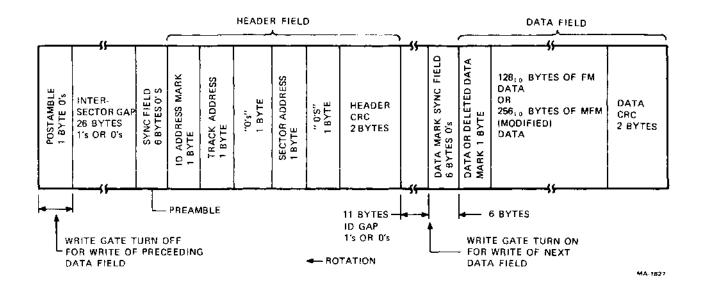

Data is recorded on only one side of the diskette. This surface is divided into 77 concentric circles or "tracks" numbered 0-76. Each track is divided into 26 sectors numbered 1-26 (Figure 1-9). Each sector contains two major fields: the header field and the data field (Figure 1-10).

Figure 1-8 FM Versus MFM Encoding

Figure 1-9 Track Format (Each Track)

Figure 1-10 Sector Format (Each Sector)

- 1.5.3.1 Header Field Description The header field is broken into seven bytes (eight bits/byte) of information and is preceded by a field of at least six bytes of zeros for synchronization. The header and its preamble are always recorded in FM.

- 1. Byte No. 1: ID Address Mark This is a unique stream of flux reversals (not a string of data bits) that is decoded by the controller to identify the beginning of the header field. (Data = FE hex, clock = C7 hex.)

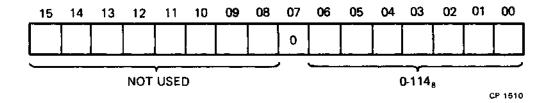

- 2. Byte No. 2: Track Address This is the absolute (0-1148) binary track address. Each sector contains track address information to identify its location on 1 of the 77 tracks.

- 3. Byte No. 3: Zeros

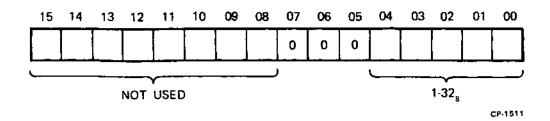

- 4. Byte No. 4: Sector Address This is the absolute binary sector address (1-32<sub>8</sub>). Each sector contains sector address information to identify its circumferential position on a track. There is no sector 0.

- 5. Byte No. 5: Zeros

- 6,7. Bytes No. 6 and 7: CRC This is the cyclic redundancy check character that is calculated for each sector from the first five header bytes using the IBM 3740 polynomial.

- 1.5.3.2 Data Field Description The data field contains either 131<sub>10</sub> or 259<sub>10</sub> bytes of information depending on the recording scheme. This field is preceded by a field of zeros for synchronization and the header field (Figure 1-10).

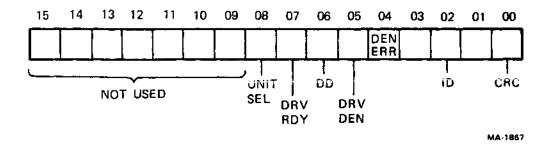

- 1. Byte No. 1: Data or Deleted Data Address mark This byte is always recorded in FM and is unique because it contains missing clocks. It is decoded by the controller to identify the beginning of a data field. The deleted data mark is not used during normal operation but the R X02 can identify and write deleted data marks under program control as required. There is a unique address mark for each density as shown in the following table. One of these marks is the first byte of each data field.

Table 1-1 Data Address Mark Code

|         |          | Hex Byte |            |

|---------|----------|----------|------------|

| Mark    | Density  | Data     | Clock      |

|         | FM       | FB       | C7         |

| Data    | MFM mod. | FD       | <b>C</b> 7 |

| DELETED | FM       | F8       | C7         |

| DATA    | MFM mod. | F9       | C7         |

2. Bytes No. 2: -129 (FM) or -257 (MFM modified) – This is the data field and it can be recorded in either FM or MFM (modified). It is used to store 128<sub>10</sub> or 256<sub>10</sub> (depending upon encoding) 8-bit bytes of information.

## NOTE Partial data fields are not recorded.

- 3. Bytes No. 130 and 131 or 258 and 259 These bytes comprise the CRC character that is calculated for each sector from the first 129 or 257 data field bytes using the industry standard polynomial division algorithm designed to detect the types of failures most likely to occur in recording on the floppy media. These bytes will be recorded with the same encoding scheme as the data field.

- 1.5.3.3 Track Usage In the IBM 3740 system, some tracks are commonly designated for special purposes such as error information, directories, spares, or unused tracks. The RX02 is capable of recreating any system structure through the use of special systems programs, but normal operation will make use of all the available tracks as data tracks. Any special file structures must be accomplished through user software.

- 1.5.3.4 CRC Capability Each sector has a two-byte header CRC character and a two-byte data CRC character to ensure data integrity. The CRC characters are generated by the hardware during a write operation and checked to ensure all bits were read correctly during a read operation. The CRC character is the same as that used in IBM 3740 series equipment.

#### CHAPTER 2 INSTALLATION

#### 2.1 SITE PREPARATION

This chapter contains information that is required for site preparation, unpacking, installation, and testing of the RX02 Floppy Disk System. Information is also provided to identify the various system configurations that are available.

#### 2.1.1 Space

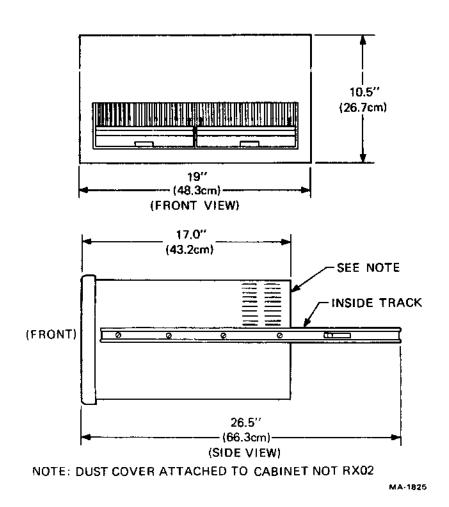

The RX02 is a cabinet-mountable unit that may be installed in a standard Digital Equipment Corporation cabinet. This rack-mountable version is approximately 28 cm high, (10-1/2 inches), 48 cm wide, (19 inches) and 42 cm deep (16-1/2 inches) as shown in Figure 2-1.

Figure 2-1 RX02 Outline Dimensions

2-1

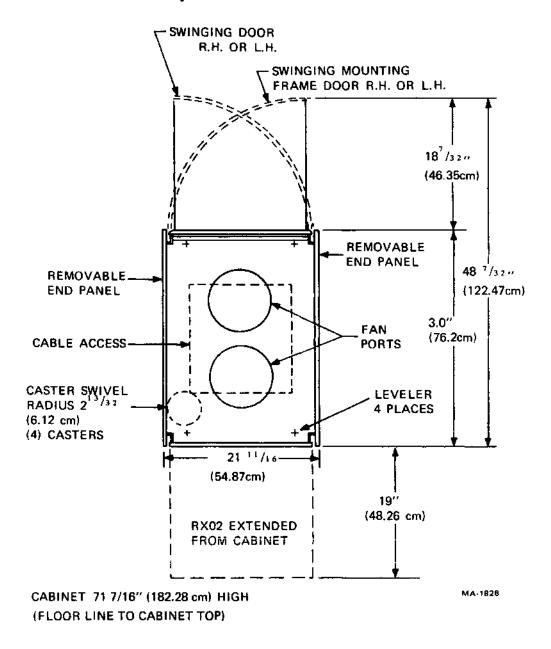

When the RX02 is mounted in a cabinet (Figure 2-2), provision should be made for service clearances of approximately 56 cm (22 inches) at the front and rear of the cabinet so that the RX02 can be extended or the cabinet rear door opened.

Figure 2-2 Cabinet Layout Dimensions

#### 2.1.2 Cabling

The standard interface cable provided with an RX02 (BC05L-15) is 4.6 m (15 ft) in length; the positioning of the RX02 in relation to the central processor should be planned to take this into consideration. The RX02 should be placed near the control console or keyboard so that the operator will have easy access to load or unload disks. The position immediately above the CPU is preferred. The ac power cord is about 2.7 m (9 ft) long.

#### 2.1.3 AC Power

2.1.3.1 Power Requirements – The RX02 is designed to use either a 60 Hz or a 50 Hz power source. The 60 Hz version will operate from 90–128 Vac, without modifications, and will use less than 4 A operating. The 50 Hz version will operate within four voltage ratings and will require field verification/modification to ensure that the correct voltage option is selected. The voltage ranges of 90–120 Vac and 184–240 Vac will use less than 4 A operating. The voltage ranges of 100–128 Vac and 200–256 Vac will use less than 2 A. Both versions of the RX02 will be required to receive the input power from an ac source (e.g., 861 power control) that is controlled by the system's power switch.

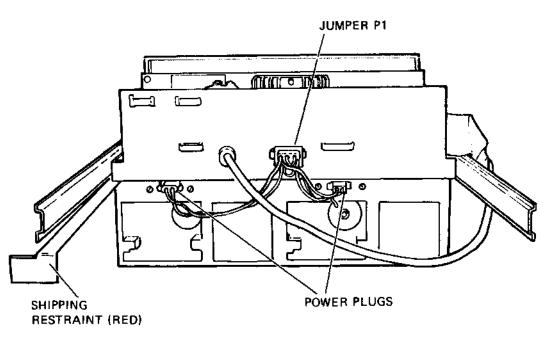

2.1.3.2 Input Power Modification Requirements – The 60 Hz version of the RX02 uses the H771-A power supply and will operate on 90–128 Vac, without modification. To convert to operate on a 50 Hz power source in the field, the H771-A supply must be replaced with an H771-C or -D (Figure 1-4) and the drive motor belt and drive motor pulley must be replaced (Figure 1-5). The H771-C operates on a 90–120 Vac or 100–128 Vac power source. The H771-D operates on a 184–240 Vac or 200–256 Vac power source. To convert the H771-C to the higher voltage ranges or the H771-D to the lower voltage ranges, the power harness and circuit breaker must be changed. See Figure 2-3 for the appropriate jumper and circuit breaker.

| VOLTAGE (VAC) | JUMPER      | CIRCUIT BREAKER     |

|---------------|-------------|---------------------|

| 90-120        | 70-10696-02 | 3.5 A, 12-12301-01  |

| 100-128       | 70-10696-01 | 3.5 A, 12-12301-01  |

| 184-240       | 70-10696-04 | 1.75 A, 12-12301-00 |

| 200-256       | 70-10696-03 | 1.75 A, 12-12301-00 |

MA-1855

Figure 2-3 RX02 Rear View

#### 2.1.4 Fire and Safety Precautions

The RX02 Floppy Disk System presents no additional fire or safety hazards to an existing computer system. Wiring should be carefully checked, however, to ensure that the capacity is adequate for the added load and for any contemplated expansion.

#### 2.2 CONFIGURATION GUIDELINES

The most common RX02 Floppy Disk System configurations available are listed in Table 2-1. Each interface module listed in the table plugs into a computer bus; it is compatible with the applicable computer so that there is adequate power to operate each module. The interconnections between each interface module and the RX02 controller for each of the configurations in Table 2-1 is by a BC05L-15 cable which is 4.6 m (15 ft) maximum. (See Table 2-2 for the controller module configuration switch positions.)

#### NOTE

For single drive configurations, the drive will be identified as drive 0 and will be mounted as the left drive. For dual drive configurations, the left drive will be identified as drive 0 and the right drive will be identified as drive 1.

#### 2.3 ENVIRONMENTAL CONSIDERATIONS

#### 2.3.1 General

The RX02 is capable of efficient operation in computer environments; however, the parameters of the operating environment must be determined by the most restrictive facets of the system, which in this case are the diskettes.

#### 2.3.2 Temperature, Relative Humidity

The operating ambient temperature range of the diskette is 15° to 32° C (59° to 90° F) with a maximum temperature gradient of 11° C/hr (20° F/hr). The media nonoperating temperature range (storage) is increased to -34.4° to 51.6° C (-30° to 125° F), but care must be taken to ensure that the media has stabilized within the operating temperature range before use. This range will ensure that the media will not be operated above its absolute temperature limit of 51.6° C (125° F).

Humidity control is important in any system because static electricity can cause errors in any CPU with memory. The RX02 is designed to operate efficiently within a relative humidity range of 20 to 80 percent, with a maximum wet bulb temperature of 25° C (77° F) and a minimum dew point of 2° C (36° F).

#### 2.3.3 Heat Dissipation

The heat dissipation factor for the RX02 Floppy Disk System is less than 225 Btu/hr. By adding this figure to the total heat dissipation for the other system components and then adjusting the result to compensate for such factors as the number of personnel, the heat radiation from adjoining areas, and sun exposure through windows, the approximate cooling requirements for the system can be determined. It is advisable to allow a safety margin of at least 25 percent above the maximum estimated requirements.

#### 2.3.4 Radiated Emissions

Sources of radiation, such as FM radio broadcasts, vehicle ignitions, and radar transmitters located close to the computer system, may affect the performance of the RX02 Floppy Disk System because of the possible adverse effects magnetic fields can have on diskettes. A magnetic field with an intensity of 50 oersteds or greater might destroy all or some of the information recorded on the diskette.

Table 2-1 RX02 Configurations

| Computer | System<br>Designation | μCPU<br>Controller | Interface<br>Module | RX02<br>Model No.             | Drive                                                             |

|----------|-----------------------|--------------------|---------------------|-------------------------------|-------------------------------------------------------------------|

|          | RX8E                  | M7744              | M8357               | RX02-AA<br>RX02-AC<br>RX02-AD | Single/115 V, 60 Hz<br>Single/115 V, 50 Hz<br>Single/230 V, 50 Hz |

|          |                       |                    |                     | RX02-BA<br>RX02-BC<br>RX02-BD | Dual/115 V, 60 Hz<br>Dual/115 V, 50 Hz<br>Dual/230 V, 50 Hz       |

| PDP-8    | RX28E                 | M7744              | M8357               | RX02-AA<br>RX02-AC<br>RX02-AD | Single/115 V, 60 Hz<br>Single/115 V, 50 Hz<br>Single/230 V, 50 Hz |

|          |                       |                    |                     | RX02-BA<br>RX02-BC<br>RX02-BD | Dual/115 V, 60 Hz<br>Dual/115 V, 50 Hz<br>Dual/230 V, 50 Hz       |

|          | RX11                  | M7744              | M7846               | RX02-AA<br>RX02-AC<br>RX02-AD | Single/115 V, 60 Hz<br>Single/115 V, 50 Hz<br>Single/230 V, 50 Hz |

|          |                       |                    |                     | RX02-BA<br>RX02-BD            | Dual/115 V, 60 Hz<br>Dual/230 V, 50 Hz                            |

| PDP-11   | RX211                 | M7744              | M8256               | RX02-AA<br>RX02-AC<br>RX02-AD | Single/115 V, 60 Hz<br>Single/115 V, 50 Hz<br>Single/230 V, 50 Hz |

|          |                       |                    |                     | RX02-BA<br>RX02-BC<br>RX02-BD | Dual/115 V, 60 Hz<br>Dual/115 V, 50 Hz<br>Dual/230 V, 50 Hz       |

|          | RXVII                 | M7744              | M7946               | RX02-AA<br>RX02-AC<br>RX02-AD | Single/115 V, 60 Hz<br>Single/115 V, 50 Hz<br>Single/230 V, 50 Hz |

|          |                       |                    |                     | RX02-BA<br>RX02-BC<br>RX02-BD | Dual/115 V, 60 Hz<br>Dual/115 V, 50 Hz<br>Dual/230 V, 50 Hz       |

| LSI-11   | RXV21                 | M7744              | M8029               | RX02-AA<br>RX02-AC<br>RX02-AD | Single/115 V, 60 Hz<br>Single/115 V, 50 Hz<br>Single/230 V, 50 Hz |

|          |                       |                    |                     | RX02-BA<br>RX02-BC<br>RX02-BD | Dual/115 V, 60 Hz<br>Dual/115 V, 50 Hz<br>Dual/230 V, 50 Hz       |

Table 2-2 Controller Configuration Switch Positions

| Interface                                   | S1-1             | S1-2             | 2<br>1 | S1       |

|---------------------------------------------|------------------|------------------|--------|----------|

| RX211, RXV21,<br>RX8E, RX11, RXV11,<br>RX28 | OFF<br>ON<br>OFF | ON<br>OFF<br>OFF | ON     | Top View |

#### 2.3.5 Cleanliness

Although cleanliness is important in all facets of a computer system, it is particularly important in the case of moving magnetic media, such as the RX02. Diskettes are not sealed units and are vulnerable to dirt. Such minute obstructions as dust specks or fingerprint smudges may cause data errors. Therefore, the RX02 should not be subjected to unusually contaminated atmospheres, especially one with abrasive airborne particles.

#### NOTE

Removable media involve use, handling, and maintenance which are beyond DIGITAL's direct control. DIGITAL disclaims responsibility for performance of the equipment when operated with media not meeting DIGITAL specifications or with media not maintained in accordance with procedures approved by DIGITAL. DIGITAL shall not be liable for damages to the equipment or to media resulting from such operation.

#### 2.4 UNPACKING AND INSPECTION

#### 2.4.1 General

The RX02 Floppy Disk System can be shipped in a cabinet as an integral part of a system or in a separate container. If the RX02 is shipped in a cabinet, the cabinet should be positioned in the final installation location before proceeding with the installation.

#### 2.4.2 Tools

Installation of an RX02 Floppy Disk System requires no special tools or equipment. Normal hand tools are all that are necessary. However, a forklift truck or pallet handling equipment may be needed for receiving and installing a cabinet-mounted system.

#### 2.4.3 Unpacking

#### 2.4.3.1 Cabinet-Mounted

- 1. Remove the protective covering over the cabinet.

- 2. Remove the restraint on the rear door latch and open the door.

- 3. Carefully roll the cabinet off the pallet; if a forklift is available, it should be used to lift and move the cabinet.

- 4. Remove the shipping restraint from the RX02 and save it for possible reuse.

- 5. Slide the RX02 out on the chassis slides and visually inspect for any damage as indicated in Paragraph 2.4.3.3.

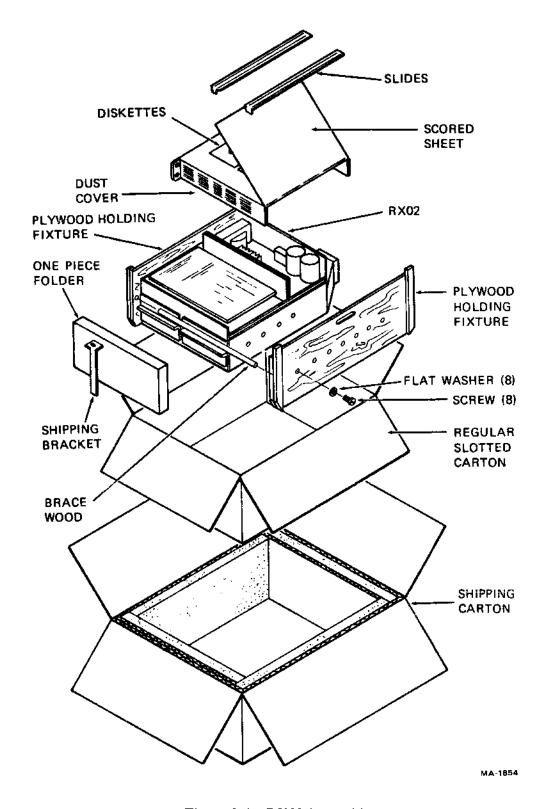

#### 2.4.3.2 Separate Container

- 1. Open the carton (Figure 2-4) and remove the packing pieces.

- Lift the RX02 out of the carton.

- 3. Remove the shipping fixtures from both sides of the RX02 and inspect for shipping damage as indicated in Paragraph 2.4.3.3.

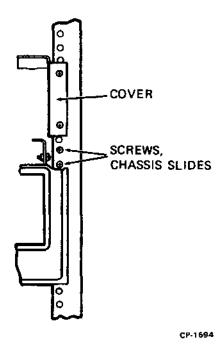

- 4. Attach the inside tracks of the chassis slides provided in the carton to the RX02 (Figure 2-1).

- 5. Locate the proper holes in the cabinet rails (Figure 2-5) and attach the outside tracks to the cabinet.

- 6. Place the tracks attached to the RX02 inside the extended cabinet tracks and slide the unit in until the tracks lock in the extended position.

- 7. Attach the front bezel with the screws supplied.

- 8. Locate the RX02 cover in the cabinet above the unit and secure it to the cabinet rails (Figure 2-5).

#### 2.4.3.3 Inspection

- 1. Inspect the front cover(s) of the RX02 to be sure it operates freely. Compress the latch which allows the spring-loaded front cover to open.

- 2. Inspect the rear of the RX02 chassis to be sure there are no broken or bent plugs. Also, be sure the fuse is not damaged.

- 3. Visually inspect the interior of the unit for damaged wires or loose hardware.

- 4. Loosen the screws securing the hinged upper module (M7744) and raise the module so that modules M7744 and M7745 can be inspected for damaged components or wires.

- 5. Verify that the items listed on the shipping order are included in the shipment. Be sure the interface cable (BC05L-15) and the appropriate interface module are included.

#### **NOTE**

If any shipping damage is found, the customer should be notified at this time so he can contact the carrier and record the information on the acceptance form.

#### 2.5 INSTALLATION

- 1. Ensure that power for the system is off.

- 2. Loosen the screws securing the upper module (M7744) and swing it up on the hinge.

- Inspect the wiring and connectors for proper routing and ensure that they are seated correctly.

- 4. This step is for 50 Hz versions only. Check the power configuration to ensure that the proper jumpers and the correct circuit breaker are installed (Figure 2-3).

Figure 2-4 RX02 Unpacking

Figure 2-5 RX02 Cabinet Mounting Information

5. Connect the BC05L-15 cable to the M7744 module and route it along the near side of the chassis through the back of the RX02 to the CPU; then connect it to the interface module for the PDP-8, PDP-11, or LSI-11.

The cable is connected to the M7744 module with the red stripe on the left, looking from the component side of board; the cable is connected to the interface module with the red stripe toward the center of the module.

- 6. Refer to Table 2-2 for the correct controller configuration switch positions.

- 7. Refer to Table 2-3 for correct device code or addressing jumpers on the interface module.

- 8. Insert the interface module into the Omnibus (PDP-8), available SPC slot (PDP-11), or LSI bus (LSI-11). The PDP-11 and LSI-11 interface modules must be inserted in the lowest numbered available option location. Modules that use DMA processing should have a higher priority than programmed I/O devices. For modules using DMA processing in the PDP-11 SPC slot, ensure that the NPG (NPG IN, NPG OUT) line (CA1-CB1) is cut on the backplane.

- 9. Connect the RX02 ac power cord into a switched power source.

- 10. Turn the power on, watching for head movement on the drive(s) during the power up, initialize phase. The head(s) should move one track toward the center and back to track zero.

Table 2-3 Interface Code/Jumper Configuration

| PDP-8  | (M8357) |

|--------|---------|

| Davice | e Codes |

|                                           | SW1                                 | SW2                                       | SW3                                 | SW4                                 | SW5                                        | SW6                                        |

|-------------------------------------------|-------------------------------------|-------------------------------------------|-------------------------------------|-------------------------------------|--------------------------------------------|--------------------------------------------|

| 670X* 671X 672X 673X 674X 675X 676X 6777X | ON<br>ON<br>ON<br>OFF<br>OFF<br>OFF | ON<br>ON<br>OFF<br>OFF<br>ON<br>ON<br>OFF | ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF | OFF<br>OFF<br>OFF<br>ON<br>ON<br>ON | OFF<br>OFF<br>ON<br>ON<br>OFF<br>OFF<br>ON | OFF<br>ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF |

|                                                                       |                                                                                                                                                                     | PDP-11 (M7846)                                                                                            | (M8256)                                                                                                              |                                                                       |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| BR Priority                                                           | Unibus Address 17                                                                                                                                                   | 717X*                                                                                                     | Vector Address (2                                                                                                    | 64 <sub>s</sub> )*                                                    |

| BR7 - 54-08782<br>BR6 - 54-08780<br>BR5 - 54-08778*<br>BR4 - 57-08776 | A12 - Removed<br>A11 - Removed<br>A10 - Removed<br>A9 - Removed<br>A8 - Installed<br>A7 - Installed<br>A6 - Removed<br>A5 - Removed<br>A4 - Removed<br>A3 - Removed | SW10 OFF<br>SW9 OFF<br>SW8 OFF<br>SW7 OFF<br>SW6 ON<br>SW5 ON<br>SW4 OFF<br>SW3 OFF<br>SW2 OFF<br>SW1 OFF | V2 – Installed<br>V3 – Removed<br>V4 – Installed<br>V5 – Installed<br>V6 – Removed<br>V7 – Installed<br>V8 – Removed | SW1 ON<br>SW2 OFF<br>SW3 ON<br>SW4 ON<br>SW5 OFF<br>SW6 ON<br>SW7 OFF |

### LSI-11 (M8029)

| Register Address* (17717X)                                                                                                                                          | Vector Address (264 <sub>8</sub> )                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| A12 - Installed A11 - Installed A10 - Installed A9 - Installed A8 - Removed A7 - Removed A6 - Installed A5 - Installed A4 - Installed A3 - Installed A3 - Installed | V2 - Installed V3 - Removed V4 - Installed V5 - Installed V6 - Removed V7 - Installed V8 - Removed |

Table 2-3 Interface Code/Jumper Configuration (Cont)

|                                                                                                  | LS                                                                                               | I-11 (M7946)                                                                                                                   |                                                                                                                                  |

|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Vector                                                                                           | Address                                                                                          | Registe                                                                                                                        | er Address                                                                                                                       |

| 2648                                                                                             | 2708                                                                                             | 177170                                                                                                                         | 177150                                                                                                                           |

| V6 - Removed<br>V5 - Installed<br>V4 - Removed<br>V3 - Removed<br>V2 - Installed<br>V1 - Removed | W6 - Removed<br>W5 - Installed<br>W4 - Removed<br>W3 - Removed<br>W2 - Removed<br>W1 - Installed | W17 - Removed W16 - Removed W14 - Removed W13 - Installed W11 - Removed W10 - Removed W9 - Removed W8 - Removed W7 - Installed | W17 - Removed W16 - Removed W14 - Removed W13 - Installed W11 - Removed W10 - Removed W9 - Installed W8 - Removed W7 - Installed |

#### 2.6 TESTING

To test the operation of RX02, run the DEC diagnostics supplied. Perform the diagnostics in the sequence listed for the number of passes (time) indicated.

RX8 or RX11 Diagnostic - 2 passes Data Reliability/Exerciser - 3 passes DECX-8 or DECX-11 - 10 minutes

If any errors occur contact Field Service.

### CHAPTER 3 USER INFORMATION

#### 3.1 CUSTOMER RESPONSIBILITY

It is the user's responsibility to ensure that the RX02 is located and operated in an area that is free from excessive dust and dirt, and meets or exceeds the environmental conditions listed in Paragraph 1.4. The exterior of the RX02 should be kept clean. Also, it is the user's responsibility to ensure that the diskettes are handled and stored properly in order to prevent errors or data loss which might occur when recording or reading data; diskette handling procedures are described in Paragraph 3.2.

#### 3.2 CARE OF MEDIA

#### 3.2.1 Handling Practices and Precautions

To prolong the diskette life and prevent errors when recording or reading, reasonable care should be taken when handling the media. The following handling recommendations should be followed to prevent unnecessary loss of data or interruptions of system operation.

- 1. Do not write on the envelope containing the diskette. Write any information on a label prior to affixing it to the diskette.

- 2. Paper clips should not be used on the diskette.

- 3. Do not use writing instruments that leave flakes (such as lead or grease pencils) on the jacket of the media.

- 4. Do not touch the disk surface exposed in the diskette slot or index hole.

- 5. Do not clean the disk in any manner.

- 6. Keep the diskette away from magnets or tools that may have become magnetized. Any disk exposed to a magnetic field may lose information.

- 7. Do not expose the diskette to a heat source or sunlight.

- 8. Always return the diskette to the envelope supplied with it to protect the disk from dust and dirt. Diskettes not being used should be stored in a file box if possible.

- 9. When the diskette is in use, protect the empty envelope from liquids, dust, and metallic materials.

- 10. Do not place heavy items on the diskette.

- 11. Do not store diskettes on top of computer cabinets or in places where dirt can be blown by fans into the diskette interior.