# peripherals and interfacing handbook

1972 edition

digital

# peripherals and interfacing handbook

digital equipment corporation

# CONTENTS

| PART I                                         |       |

|------------------------------------------------|-------|

| Chapter 1- Programming Peripherals             | 1     |

| Chapter 2- Basic 1/O Terminals                 | 5     |

| Chapter 3- Magnetic Tape Options               | 33    |

| Chapter 4 Display Terminals                    | 55    |

| Chapter 5- Disk Storage Devices                | 63    |

| Chapter 6- Clocks                              | 91    |

| Chapter 7- Bus Extension Options               | 97    |

| Chapter 8- Communications Options              | 109   |

| Chapter 9- Data Aquisition and Control Options | 153   |

| PART II                                        |       |

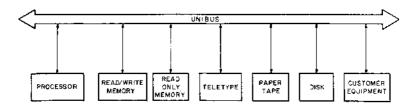

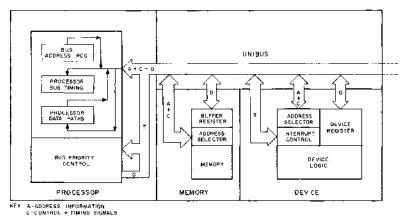

| Chapter 1- Unibus Theory and Operation         | 179   |

| Chapter 2- Interface Circuits                  | .,201 |

| Chapter 3: Interface Examples                  | 245   |

| APPENDICES                                     |       |

| Appendix A- Device Registers                   | 281   |

| Appendix B- UNIBUS Pin Assignments             | 289   |

÷

# INTRODUCTION

This Handbook is intended for users of any PDP-11 family system. It describes standard PDP-11 peripherals and options and provides detailed information on interfacing to the PDP-11 UNIBUS.

This Handbook supplements information contained each of the PDP-11 family processor handbooks.

Part I describes each PDP-11 peripheral device and includes programming information. Part II covers the operation of the PDP-11 UNIBUS and describes interfacing techniques.

# PART I

| Chapter 1 - PROGRAMMING PERIPPERALS             |      |

|-------------------------------------------------|------|

| Chapter 2 · BASIC INPUT/OUTPUT DEVICES          | 5    |

| TELETYPEHIGH SPEED READER/PUNCH, PC11           |      |

| HIGH SPEED LINE PRINTER, LP11                   |      |

| CARD READERS, CM11, CR11                        |      |

| DECWRITER, LA30                                 |      |

| Chapter 3 - MAGNETIC TAPE OPTIONS               | 33   |

| DECTAPE, TC11/TU56                              | 35   |

| MAGTAPE, TM11/TU10                              |      |

| Chapter 4 - DISPLAY TERMINALS                   | 55   |

| STORAGE DISPLAY, VT01A                          | 56   |

| OSCILLOSCOPE, VR01A                             |      |

| POINT PLOT DISPLAY, VR14                        | 57   |

| ALPHANUMERIC TERMINAL, VT05                     | 58   |

| DECLINK TERMINAL, RT01                          | 60   |

| Chapter 5 - DISK STORAGE DEVICES                | 63   |

| DECDISK MEMORY, RC11/RS64                       |      |

| DISK AND CONTROL, RF11/RS11                     |      |

| DECPACK DISK CARTRIDGE SYSTEM, RK11-C/RK02, RK0 | )381 |

| Chapter 6 - CLOCKS                              | 91   |

| PROGRAMMABLE REAL TIME CLOCK, KW11-P            | 91   |

| LINE TIME CLOCK, KW11-L                         | 93   |

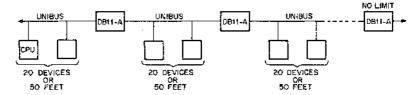

| Chapter 7 - BUS EXTENSION OPTIONS               | .,97 |

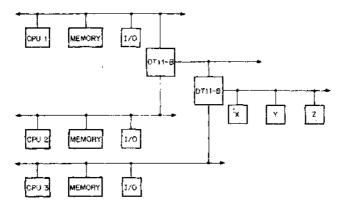

| BUS REPEATER, DB11                              |      |

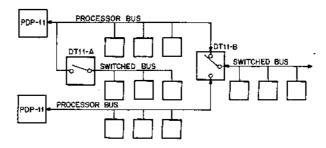

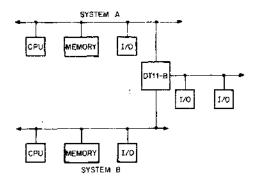

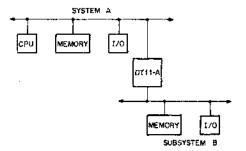

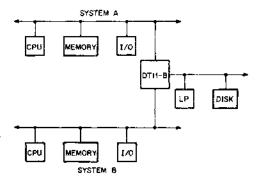

| BUS SWITCHES, DT11-A, DT11-B                    | 100  |

| Chapter 8 - COMMUNICATIONS OPTIONS              | 109 |

|-------------------------------------------------|-----|

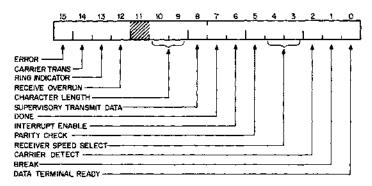

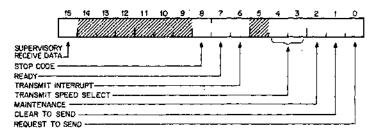

| ASYNCHRONOUS LINE INTERFACE, DC11               | 109 |

| AUTOMATIC CALLING UNIT INTERFACE, DN11          | 116 |

| SYNCHRONOUS INTERFACE, DP11                     |     |

| ASYNCHRONOUS 16-LINE SINGLE SPEED               |     |

| MULTIPLEXER, DM11                               | 131 |

| FULL DUPLEX 8 BIT ASYNCHRONOUS                  |     |

| LINE INTERFACE, KL11                            | 151 |

| ASYNCHRONOUS NULL MODEM, H312A                  |     |

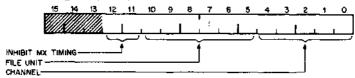

| Chapter 9 - DATA ACQUISTION AND CONTROL OPTIONS | 153 |

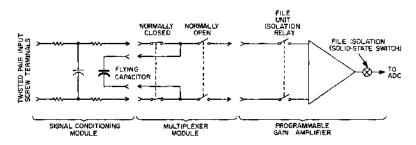

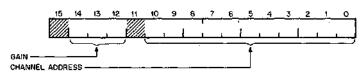

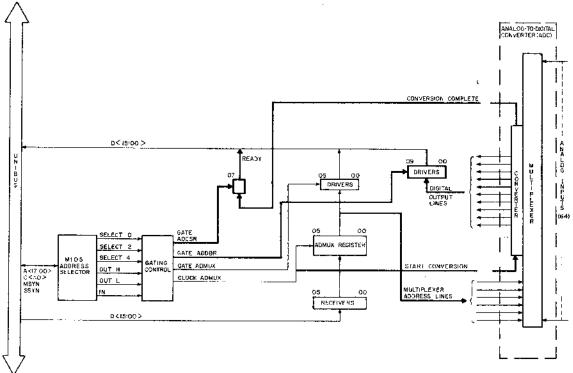

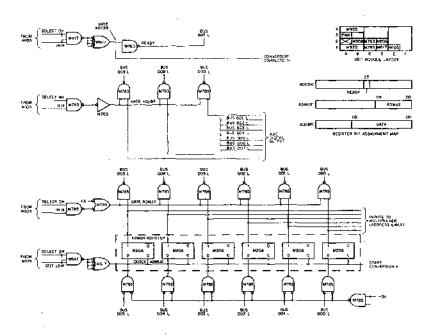

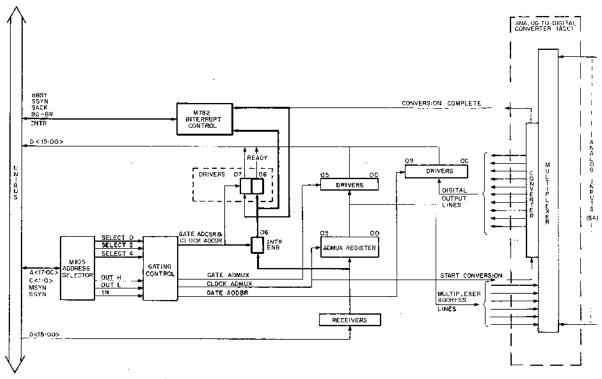

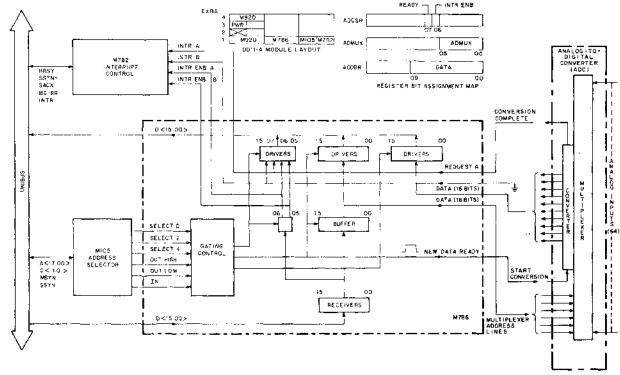

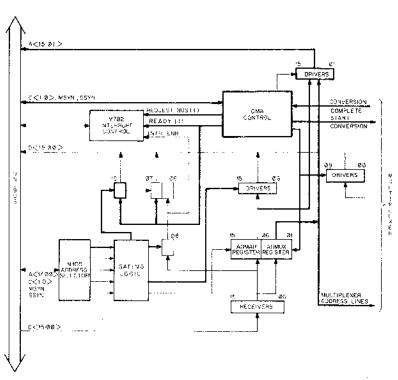

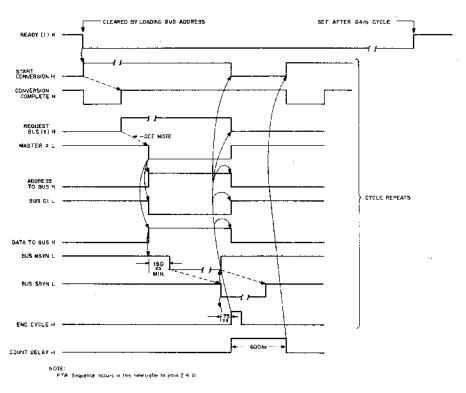

| LOW LEVEL ANALOG INPUT SUBSYSTEM, AFC11         | 153 |

| ANALOG TO DIGITAL CONVERSION                    |     |

| SUBSYSTEM, AD01D                                | 158 |

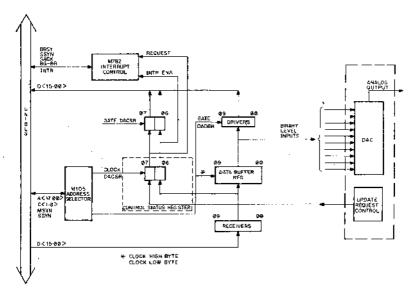

| DIGITAL TO ANALOG CONVERSION                    | _   |

| SUBSYSTEM, AA11D                                | 161 |

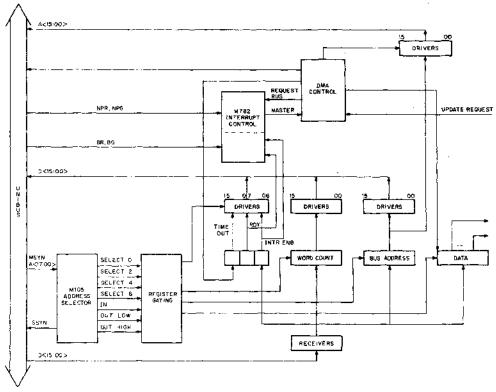

| UNIVERSAL DIGITAL CONTROL                       |     |

| SUBSYSTEM, UDC11                                | 163 |

|                                                 |     |

# **Programming Peripherals**

### 1.1 PROGRAMMING

Programming of peripherals is extremely simple in the PDP-11 -- a special class of instructions to deal with input/output operations is unnecessary. The UNIBUS permits a unified addressing structure in which control, status, and data registers for peripheral devices are directly addressed as memory locations. Therefore all operations on these registers, such as transferring information into or out of them or manipulating data within them, are performed by normal memory reference instructions.

The use of all memory reference instructions on peripheral device registers greatly increases the flexibility of input/output programming. For example, information in a device register can be compared directly with a value and a branch made on the result:

# CMP PRB, #101 BEQ SERVICE

In this case, the program looks for 101, in the paper tape reader data buffer (PRB), and branches if it finds it. There is no need to transfer the information into an intermediate register for comparison.

When the character is of interest, a memory reference instruction can transfer the character into a user buffer in core or to another peripheral device. The instruction:

### MOV PRB.LOC

transfers a character from the paper tape buffer into a user-defined location.

All arithmetic operations can be performed on a peripheral device register. For example, the instruction ADD #10, DSX will add  $10_s$  to a display's x-deflection register.

All peripheral device registers can be treated as accumulators. There is no need to funnel all data transfers, arithmetic operations, and comparisions through a single or small number of accumulator registers.

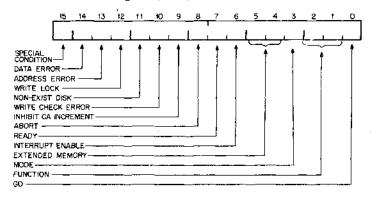

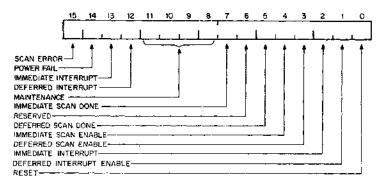

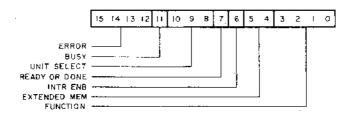

### 1.2 DEVICE REGISTERS

All peripheral devices are specified by a set of registers which are addressed as core memory and manipulated as flexibly as an accumulator. There are two types of registers associated with each device: 1) control and status registers: 2) data registers.

### 1.2.1 Control and Status Registers

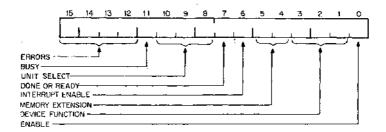

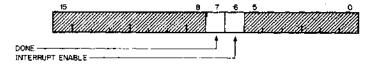

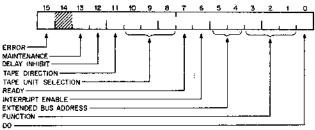

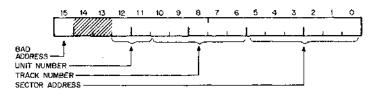

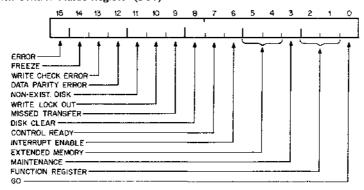

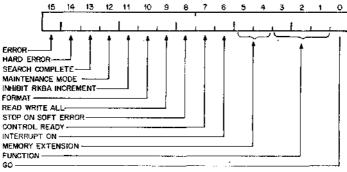

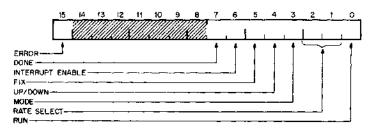

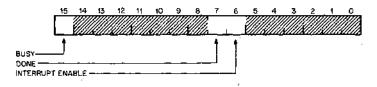

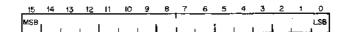

Each peripheral has one or more control and status registers that contain all the information necessary to communicate with that device. The general form, shown below does not necessarily apply to every device, but is presented as a guide.

Many devices require less than sixteen status bits. Other devices will require more than sixteen bits and therefore will require additional status and control registers.

The bits in the control and status registers are generally assigned as follows:

BIT NAME 15-12 Errors

### DESCRIPTION

Generally there is an individual bit associated with a specific error. When more bits are required for errors, they can be obtained by expanding the error section in the word or by using another status word. Generally Bit 15 is the inclusive OR of all other error bits (if there is more than one). Most devices will have "hard"error conditions which will cause an interrupt if bit 6 is set. Some may also have "soft"errors (warning types) which do not cause immediate interrupts. All errors are generally indicated by individual status bits.

11 Busy

10-8 Unit Select

Indicates that a step is being performed.

Some peripheral systems have more than one device per control. For example, a disk system can have multiple surfaces per control and an analog-to-digital converter can have multiple channels. The unit bits select the proper surface or channel.

7 Done or Ready

The register can contain a DONE bit, a READY bit or a DONE-BUSY pair of bits, depending on the device. These bits are set and cleared by the hardware, but may be queried by the program to determine the availability of the device. For example, the teleprinter status register (TPS) has a READY bit (7) that is cleared on request for output and then set when output is

complete. The keyboard status register (TKS) has a DONE-BUSY pair (bits 7 and 11) that distinguish between no input (DONE = BUSY = 0), input under way (DONE = 0, BUSY = 1), AND INPUT COMPLETE (DONE = 1, BUSY = 0).

The DONE bit could be used to control an input loop for reading from the paper tape reader as follows:

LOOP: TSTB PRS ;test low byte

of paper tape status

register;

BPL LOOP (branch back if ;DONE (bit 7)

is not set

6 Interrupt Enable

Independently programmable. If bit 6 is set, an interrupt will occur as a result of a function done or error condition. To initiate an interrupt routine to read from the paper tape reader, the instruction

MOV #101,PRS

could be used. This sets bit 0 and bit 6 of the paper tape reader control and status register (PRS). Setting bit 0 starts the read operation and setting bit 6 enables an interrupt to occur when the read operation is complete.

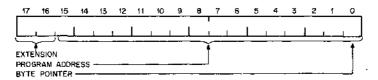

5-4 Memory Extension

Will allow devices to use a full 18 bits to specify addresses on the bus.

3-1 Device Function Bits

Specify operations that a device is to perform. For example, a paper tape read function could be "read one character". An operation for a disk could be "read a block of words from memory and store them on the disk."

0 Enable

When set, enables the device.

### NOTE

The "unused" and "load" only bits are always read as zeroes. Loading "unused" or "read only" bits has no effect on the bit position. The mnemonic "INIT" refers to the initialization signal issued by the processor.

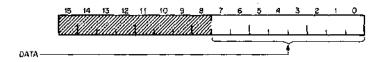

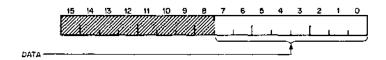

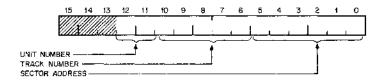

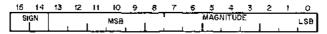

### Data Buffer Registers

Each device has at least one buffer register for temporarily storing data to be transferred into or out of the computer. The number and type of data registers is a function of the device. The paper tape reader and punch use single 8-bit data buffer registers. A disk would use 16-bit data registers and some devices may use two 16-bit registers for data buffers.

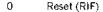

### 1.2.2 Interrupt Structure

If the appropriate interrupt enable bit is set, in the control and status register of a device, transition from 0 to 1 of the READY or ERROR bit causes an interrupt request to be issued to the processor. Also if READY or ERROR is a 1 when the interrupt enable is turned on, an interrupt request is made. If the device makes the request at a priority greater than that at which the processor is running and no other conflicts exist, the request is granted and the interrupt sequence takes place:

- a. the current program counter (PC) and processor status (PS) are pushed onto the processor stack;

- the new PC and PS are loaded from a pair of locations (the interrupt vector) in addressed memory, unique to the interrupting device.

Since each device has a unique interrupt vector which dispatches control to the appropriate interrupt handling routine immediately, no device polling is required. Furthermore, since the PS contains the processor priority, the priority at which an interrupt request is serviced can be set under program control and is independent of the priority of the interrupt request. The Return from Interrupt Instruction (RTI) is used to reverse the action of the interrupt sequence. The top two words on the stack are popped into the PC and PS, returning control to the interrupted sequence.

### 1.2.3 Programming Example

A paper tape reader interrupt service could appear as follows:

First the user must initialize the service routine by specifying an address pointer and a word count

INIT: MOV #BUFADR,POINTER ;set address pointer

MOV #COUNT.COUNTR ;set counter

MOV # 101,PRS ;enable reader program continues until in-

terrupt

When the interrupt occurs and is acknowledged, the processor stores the current PC and PS on the stack. Next if goes to the interrupt vector and picks up the new PC and PS beginning at location 70. When the program was loaded the address of PRSER would be put in location 70 and 200<sub>8</sub> in 72 (to set priority at 4). The next instruction executed is the first instruction of the device service routine at PRSER.

PRSER: TST PRS :test for error

BMI ERROR :branch if bit 15 set

MOV8 PRB.@POINTR :move character to buffer

INC POINTR :increment pointer

DEC COUNTR ;decrement character count

BEQ DONE ;branch when input done

INC PRS :start reader for next character

DONE: RTI :return to interrupt program

# Basic I/O Terminals

### 2.1 INTRODUCTION

This chapter describes the simplest and most common devices for entering data to and receiving data from a PDP-11 system; teleprinters, paper tape punches and readers, line printers and card readers.

The ASR 33 Teletype (DEC model number tT33-DC) is provided as standard equipment with some basic PDP-11 Family systems. It will type or print information at a rate of up to 10 characters per second and is equipped with low speed paper punch and reader (10 cps). A Teletype with keyboard and printer but without paper tape reader and punch (KSR) is also available. The LA30 DECwriter, a teleprinter completely designed by DEC, answers the need for a fast reliable, low-cost terminal and is particularly appropriate for systems requiring large numbers of highly reliable printer/terminals. It prints at speeds of up to 30 characters per second with low noise levels.

The PC11 High Speed Paper Tape Reader and Punch is available for users who need faster paper tape reading speeds than those offered by the standard ASR 33 Teletype. The PC11 reads perforated tape at rates of up to 300 characters per second and punches tape at 50 characters per second.

The LP11 high speed line printer, one of the few line printers available with 80-column width, will print a maximum of 356 full lines per minute (80-column, 64-character model). A 132 column model is also available as are 96 character sets giving upper and lower case printing.

Any combinations of these devices may be used with a PDP-11. For example, the RSTS-11 BASIC-PLUS timesharing system can accommodate up to 16 teleprinter terminals, in addition to other I/O devices.

DEC devices utilize American National Standard Code for Information Interchange (ANSCII), 1968 version, code.

The eight-bit code used by the Model ASR Teletype is ASCII modified. To convert ANSCII code to Teletype code, add 200 octal (ASCII + 200, = Teletype). This code is read in the normal octal form used in the computer.

On paper tape, bits are numbered from right to left, from 0 through 7, with bits 0 through 2 containing the least significant octal number. Holes corresponding to bits 2 and 3 are separated by a row of small feed holes for moving the tape.

### 2.2 TELETYPE

The standard ASR 33 Teletype can be used to type in or print out information, or to read in or punch out perforated paper tape. Printing, punching and reading are

ASR 33 TELETYPE

performed at rates of up to 10 characters per second. The KL11-A Teletype Control assembles or disassembles Teletype serial information for parallel transfer to, or from, the UNIBUS.

### 2.2.1 Operation

When the processor addresses the bus, the Teletype Control decodes the address to determine if the Teletype is the selected device and, if selected, whether it is to perform an input or output operation. Signals transferred between the Teletype and the control logic are standard serial, 11-unit code Teletype signals. They consist of "marks" and "spaces" which correspond to bias and idle current in the Teletype serial line, and 1's and 0's in the control and computer. The 11-bit code consists of a start bit, 8 data bits, and 2 halt bits.

### 2.2.2 Programming

The Teletype Control has four addressable registers. They have memory addresses and can be read or loaded using any PDP11 instruction that refers to their address.

| REGISTER                     | ADDRESS         |

|------------------------------|-----------------|

| Reader Status Register (TKS) | 777560          |

| Reader Buffer Register (TKB) | 777562          |

| Punch Status Register (TPS)  | 7775 <b>6</b> 4 |

| Punch Buffer Register (TPB)  | 777566          |

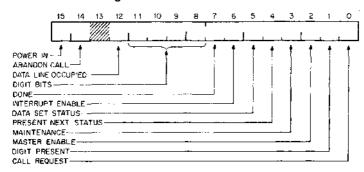

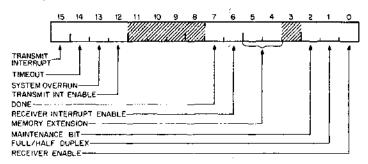

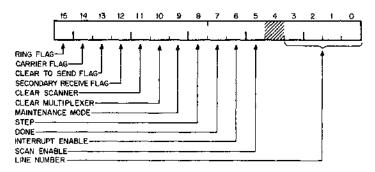

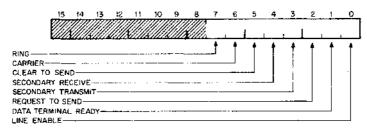

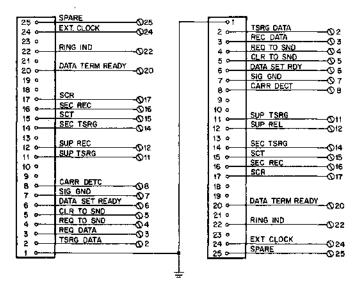

The bit assignments for the registers are shown below. The "unused" and "load only" bits are always read as zeros. Loading "unused" or "read only" bits has no effect on the bit position. The mnemonic "INIT" refers to the initialization signal issued by on, power up, console start, or RESET.

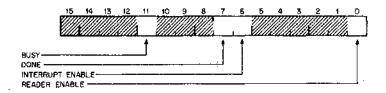

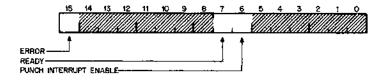

# Reader Status Register

| BIT<br>15-12 | NAME                    | DESCRIPTION<br>Not Used                                                                                                                                                               |

|--------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11           | Busy                    | Indicates that the Teletype Control is re-<br>ceiving a start bit or information bits.<br>Cleared by INIT, set by start bit, cleared<br>after reception of first halt bit. Read only. |

| 10-08        |                         | Not used                                                                                                                                                                              |

| 7            | Done                    | Character available in buffer. Cleared by INIT, cleared by referencing data buffer, causes interrupt when INTR ENB = 1. Read only. Cleared when RDR ENB is set.                       |

| 6            | Reader Interrupt Enable | Interrupts Enable. Enables Error or Done to cause an interrupt. Cleared by INIT.                                                                                                      |

| 5-1          |                         | Not used                                                                                                                                                                              |

| 0            | Reader Enable           | Enables reader (not keyboard) to read one character. Cleared by INIT; cleared when legitimate start bit is detected. Load only.                                                       |

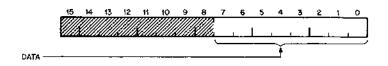

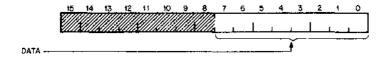

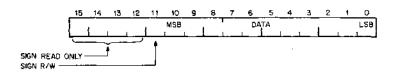

### Reader Buffer (TKB)

BIT NAME DESCRIPTION 15-8 Not used

7-0 Data Holds character read. Cleared by start bit. Read only.

Any reference to TKB (as word or byte) or TKB +1 clears DONE.

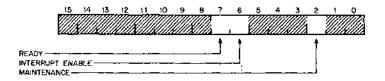

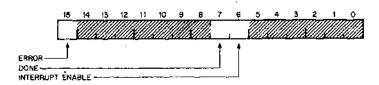

### Punch Status Register (TPS)

| BIT<br>15-8 | NAME             | DESCRIPTION<br>Not used                                                                                                                             |

|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7           | Ready            | Punch available. Set by INIT, cleared when buffer is loaded, set when punching complete. Caused interrupt if INTR ENB = 1. Read only.               |

| 6           | Interrupt Enable | Enables READY to cause interrupt. Cleared by INIT.                                                                                                  |

| 5-3         |                  | Not used                                                                                                                                            |

| 2           | Maintenance      | Maintenance function. Disables serial line input from Teletype unit and enables serial output of punch to feed into reader buffer. Cleared by INIT. |

| 1-0         |                  | Not used                                                                                                                                            |

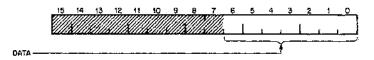

### Punch Buffer Register (TPS)

BIT NAME DESCRIPTION

15-8 Not used

7-0 Data Holds character to be punched. Cleared by INIT. Load only.

Any instruction that could modify TPB as a byte or word, clears READY and initiates punching, Other reference to either byte or word have no effect on the punch.

2.2.3 Programming Examples

Reading a Character (from reader or keyboard):

READ: INC TKS ;Set RDR ENB

LOOP: TSTBITKS ;Look for DONE

BPL LOOP ;Wait if DONE = 0

MOVB TKB.RO :Read character

Programming Example: Punching a Character

PUNCH: TSTB TPS ;Test for READY

BPL PUNCH : Wait if READY = 0

MOVB RO.TPB :Punch character

Programming Example: Echoing Keyboard

ECHO: TSTB TKS ;Character available?

BPL ECHO :Wait if DONE = 0

LOOP: TSTB TPS ;Is punch ready?

BPL LOOP ; Wait if READY = 0

MOVB TKB,TPB ;Punch character

BR ECHO ;Repeat for next character

Programming Example: Reading 10 Characters (by means of an interrupt)

START: MOV # 10,RO :Set up counter

MOV # 2000.R1 :Set up buffer pointer

MOV # 101,TKS :Set INTR ENB and RDR ENB

STALL: BR STALL :Hang up here until

:block is read

60: RDRINT

:Start of reader service

routine

62: 000200

;Raise processor to priority

;level 4

RDRINT:

MOVB TKB,(R1) +

;Put character into buffer

DEC RO

:Decrement counter

BEQ END

;If count = 0, get out

INC TKS

:Enable reader again

RT!

;Return from interrupt

END:

TST (SP) + (SP) +

:Reset stack

CLR TKS

:Clear INT ENB

JMP STALL + 2

;Back to program

### 2.2.4 Specifications

Space Requirement:

Requires a floor space of approximately 22 1/2 inches wide by 18 1/2 inches deep. The standard Teletype cable length restricts its location to within

8 feet of the side of the computer.

Weight:

70 lbs

Interrupt Vector Address:

Keyboard / printer: 60 Teleprinter / punch: 64

Priority Level:

BR4 (Teletype keyboard has precedence over Tele-

type printer.

Operating Temperature: Humidity:

50 -110 F 20% to 80%

KL11A Control:

Humidity: 20% to 90%

Temperature: 55 to 100 F.

The KL11A is capable of driving up to to 1,500 feet of cable if necessary.

| Model              | Туре | Power      | Description                                                                        |

|--------------------|------|------------|------------------------------------------------------------------------------------|

| LT33-DC<br>LT35-DC |      | 115, 60Hz  | Automatic send/receive unit, includes keyboard and a reader/punch for paper tapes. |

| LT33-DD<br>LT35-DD |      | 230V, 50Hz | same as above.                                                                     |

| LT33-CC<br>LT35-CC |      | 115V, 60Hz | Keyboard only. Does not include paper tape capability.                             |

| LT33-CD<br>LT35-CD |      | 230V, 50Hz | Same as above                                                                      |

### 2.4 HIGH SPEED READER PUNCH-PC11

The High Speed Reader & Punch is capable of reading eight-hole unoiled perforated paper tape at 300 characters per second, and punching tape at 50 characters per second. The system consists of a High Speed Paper Tape Reader/Punch and the PC11 Control. A unit containing a reader only (PR11) is also available.

### 2.3.1 Operation

In reading tape, a set of photodiodes translate the presence or absence of holes in the tape to logic levels representing is and Os. In punching tape, a mechanism translates logic levels representing is and Os to the presence or absence of holes in the tape. Any information read or punched is parallel-transferred through the Control. When an address is placed on the UNIBUS, the Control decodes the address and determines if the reader or punch has been selected. If one of the four device register addresses have been selected, the Control determines whether an input or an output operation should be performed. An input operation from the reader is initiated when the processor transmits a command to the Paper Tape Reader Status register. An output operation is initiated when the processor transfers a byte to the Paper Tape Punch Buffer Register.

The Control enables the PDP-11 System to control the reading or punching of paper tape in a flexible manner. The reader can be operated independently of the punch, either device can be under direct program control or can operate without direct supervision through the use of interrupts, to maintain continuous operation.

## 2.3.2 Programming

| REGISTER                               | ADDRESS |

|----------------------------------------|---------|

| Papertape Reader Status Register (PRS) | 777550  |

| Papertape Reader Suffer (PRB)          | 777552  |

| Papertape Punch Status (PPS)           | 777554  |

| Papertape Punch Buffer (PPB)           | 777556  |

High Speed Paper Tape Reader/Punch

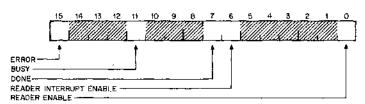

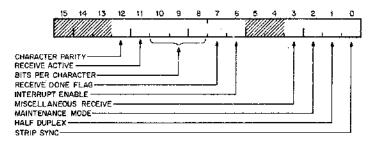

# Papertape Reader Status Register (PRS)

| BIT<br>- 15 | NAME<br>Error | DESCRIPTION Indicates one of three possible error conditions: no tape in reader, reader is offline, or reader has no power, Disables RDR ENB; causes interrupt if RDR INT ENB = 1. |

|-------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14-12       |               | Not used.                                                                                                                                                                          |

| 11          | Busy          | indicates that a character is in the process of being read. Cleared by INIT, set by RDR ENB, cleared when character is available in buffer. Read only.                             |

| 10.8        |               | Not used                                                                                                                                                                           |

| 7           | Done          | Character available in buffer. Cleared by INIT, set when character available, cleared by referencing reader buffer (PRR)                                                           |

cleared by setting RDR. ENB; causes interrupt when RDR INT ENB = 1. Read only.

6 Reader Interrupt Enable Interrupts enable. Enables ERROR or DONE to cause an interrupt Cleared by INIT.

5.1 Not used.

٥ Reader Enable

Enables reader to fetch one character. Clears DONE, sets BUSY, and clears reader buffer (PRB). Operation of this bit is disabled if ERROR=1; attempting to set it when ERROR = 1 will cause an immediate interrupt if RDR INT ENB = 1. Load only.

### Papertage Reader Buffer (PRB)

BIT NAME DESCRIPTION 15-8 Not used 7-0 Data Holds character to be read. Cleared by RDR ENB. Read only.

Note: Referencing either high byte or low byte or both bytes clears DONE. Referencing is any operation (read, load, test, compare).

### Papertape Punch Status (PPS)

BIT NAME 15 Error

### DESCRIPTION

Indicates one of two error conditions in punch; no tape in punch or punch unit out of power. Causes interrupt if PUN INT ENB (of PPS) = 1.

14.8

Not used.

7 Ready Ready to punch character, Set by INIT,

cleared by loading data buffer (see note under PPB), set when punching complete. Causes interrupt when PUN INT ENB = 1.

Read only.

6 Punch interrupt Enable Interrupts enable. Enables ERROR or

READY to cause interrupt. Cleared by

READY to cause interrupt. Cleared INIT.

5-0 Not used.

### Papertape Punch Buffer Register (PPB)

BIT NAME 7-0 Data DESCRIPTION

Write-only. Any instruction that could modify bits 7-0 of PPB clears Ready and initiates punching. An immediate interrupt will occur when punching is initiated if ERROR = 1 and PUN INT ENB = 1.

# 2.3.3 Programming Examples Reader Interrupt Service

The PDP-11 System can combine PC11 operations with other processing by using the interrupt mode of device operation. When a device operation has been initiated, the PC11 continues without supervision until the operation is complete (or an error occurs); the remainder of the PDP-11 System if free to perform other operations. When the PC11 Control requires further service, the processor is notified by an interrupt.

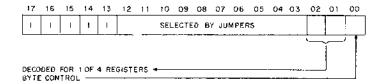

Each device that is operated in an interrupt mode must be initialized by commands from the processor. An interrupt service routine and an interrupt vector (at the address corresponding to the vector address selected by the jumpers on the M782 Module) must be provided.

The program that follows can be used to read a block of 128 characters from the paper tape to a buffer.

START: MOV #-200,RO ;INITIALIZE COUNTER

MOV # 101,PRS ;SET INTR ENB AND RDR ENB

HANG: BRIHANG ;HANG UP HERE UNTIL BLOCK

:IS READ

70: RDRINT ;VECTOR TO INTERRUPT ROUTINE

72: 200 ;SETS STATUS TO PRIORITY 4

RDRINT: TST PRS ;TEST FOR ERROR

BMI ERR ; TYPE OUT MESSAGE IF ERROR

MOVB PRB,BUFEND(RO) :FILL BUFFER STARTING AT

:BUFEND-200(OCTAL)

INC RO ;COUNT ONE BYTE AND MOVE

;POINTER

BEQ OUT :WHEN COUNT IS ZERO, EXIT LOOP

INC PRS ;ENABLE READER AGAIN

RTI :RETURN FROM INTERRUPT

OUT: ADD #4,SP :UNSTACK INTERRUPT PC AND PS

CLR PRS :INHIBIT FURTHER INTERRUPTS

JMP HANG + 2 ;CONTINUE MAIN PROGRAM

### NOTE

The position of the buffer used by this program is specified by the end of the buffer, not the beginning. The indexed address uses the negative counter values to access bytes at decreasing distances from this base address.

Two operations performed by this program require caution. When a program accesses the same or contiguous locations, the program operating speed increases if the locations are addressed through a register. If this is done either no other use can be made of this register or: a) the interrupt service routine must stack the former contents of the register, b) the counter must be moved from a temporary storage location to the register, c) the register must be used, and d) the storage operations reversed. In this example where the processor does not do any other processing, no conflicts with the use of the register occur.

A second caution refers to the terminating exit from the service routine. When the exit does not occur through an RTI instruction, the main program PC (Program Counter) and PS (Processor Status) words that are stacked by the interrupt must be removed from the stack. The ADD instruction at OUT performs the operation. If this operation is not performed, the values stacked by other operations previous to the interrupt are not properly accessible.

### Punch Programmed Service

The sequence of instructions that follows transfers one byte from register 0 to the paper tape. When controlling the punch, the READY bit of the PPS register is checked before the transfer; when controlling the reader, the DONE bit of the PRS register is checked after a command.

PUNCH: BIT #100200,PPS ;CHECK PUNCH STATUS

BEO PUNCH : IF NOT READY OR ERROR, WAIT

BMI ERROR ;PROCESS ERROR IF ANY

MOV RO, PPB GOUTPUT CHARACTER

### Punch Interrupt Service

This interrupt service routine outputs 8-bit codes to the paper tape, unless they are ASCII representations of the formatting characters Line Feed, Rubout, or Form Feed. Line Feeds and Rubouts are ignored (not punched), and the program stops punching when the character read from the buffer is a Form Feed. The Form Feed is not punched. The program transfers the contents of a buffer: a) starting at a preselected address to paper tape, b) stopping automatically when it reads an end-of-buffer character, and c) performing simple character editing.

The interrupt service routine is called into operation when the following sequence of instructions is encountered in the main program:

R0 = %0 ; REGISTER ZERO

SP = %6 : REGISTER SIX

PC = %7 :REGISTER SEVEN

PS = 177776 :PROCESSOR STATUS WORD

CLR PUNDON ;CLEAR SOFTWARE FLAG

MOV # BUFFER POINTER :SET UP BUFFER POINTER

MOV # 100.PPS :SET PUNCH INTR ENB

This instruction sequence sets up the system by initializing the service routine and enabling interrupts from the punch.

If the punch is idle, an interrupt occurs immediately; otherwise, the first interrupt is delayed until the current operation is completed. The software flag is used by the main program to provide a check on the progress of the output. This occurs in the following manner: The main program continues with other processing until the use of the punch is required, or further processing is dependent on completion of the output. At this point the sequence of instructions shown below is executed.

LOOP: TST PUNDON ;CHECK SOFTWARE FLAG

BPL LOOP

If the interrupt service routine has not set the ffag, the processor stays in this wait loop, allowing interrupts for further output operations, until the routine signals that it is finished.

In this example, the interrupt routine to service the punch requires the following sequence of instructions:

74: PCHINT :VECTOR TO ROUTINE

76: 200 :NEW STATUS WORD

PCHINT:

MOV RO.-(SP) :SAVE REGISTER ZERO

MOV POINTER, RO ;SETUP REGISTER

TST PPS ;CHECK NO ERRORS

BMI ERROR : IF ERROR, EXIT WITH LAST

:BUFFER POSITION IN RO

RETEST:

CMPB (RO), #212 ;LINE FEED?

BNE TEST2 ;NO, CONTINUE

INC RO ;YES, IGNORE CHARACTER

BRIRETEST :AND TEST NEXT CHAR.

TEST2: CMPB (R0),  $\pm$  377 ;RUBOUT?

BNE TEST3 ;NO, CONTINUE

INC RO :YES, IGNORE

BR RETEST

TEST3: CMPB (R0), #214 :FORM FEED?

BEQ OUT ;YES, EXIT

MOVB (R0) + ,PPB ;NO, OUTPUT CHARACTER

MOV RO.POINTER :SAVE REGISTER

MOV (SP) + .RO :UNSTACK PREVIOUS CONTENTS

RTI :NORMAL RETURN

OUT: MOV (SP) +,RO ;RESTORE TO PREVIOUS STATUS

COM PUNDON :SET SOFTWARE FLAG

CLR PP\$ ;CLEAR INT ENB

RTI

POINTER: 0

PUNDON: 0

# 2.3.4 Specifications READER/PUNCH

Reader: Photoelectric

300 Characters Per Second

Includes; light source, set of photodiodes, tape

transport, bins to hold and collect tape

Punch: 50 Characters Per Second

Includes: Punch Drive Motor, Punch Mechanism,

Mechanism to advance and position tape

PC11 CONTROL

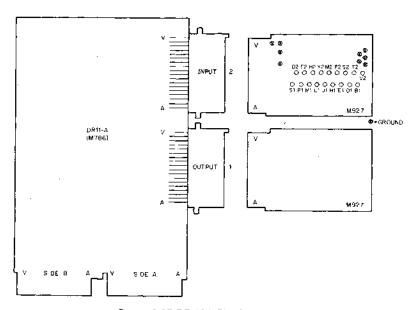

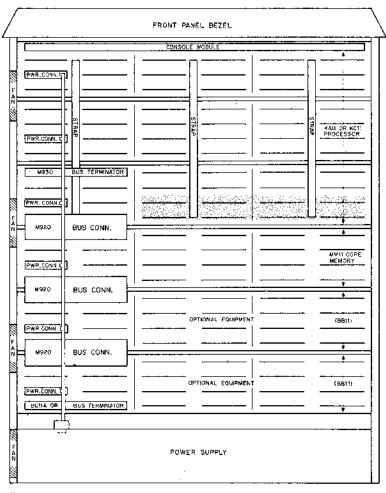

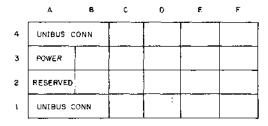

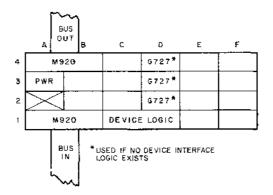

Consists of: 3 IC modules mounted on one-fourth of a DD11-A

system unit or general purpose slot of an 11 Fam-

ily processor

INTERRUPT

Vector Addresses:

Reader 70; Punch 74;

Priority Level:

BR4 (Reader has higher priority than punch if both

request service simultaneously)

19.5

PAPER TAPE

Type: Code: Ungiled fanfold, 8 holes per column

All bits are read and written

OPERATING TEMPERATURE: 55 ° to 100 °F

HUMIDITY:

20 to 95% (noncondensing)

SIZE/MOUNTING:

Fits in 10 1/2 - Inch frame that mounts in a stan-

dard 19-inch rack

MODELS:

PC11 READER/PUNCH = 60Hz, 117-V PC11A Reader Punch = 50 Hz 117 V PR11 Reader only = 50/60 Hz 117 V

### 2.4 HIGH SPEED LINE PRINTER - LP11

The LP11 High Speed Line Printer is available in several models, ranging from an 80-Column, 64-character model (LP11-FA) to an 132-column, 96-character model (LP11-HB). Either column-width printer can be ordered with 64- or 96- character print sets. The printer is an impact type using a revolving character drum and a hammer per column. Forms up to six-parts, may be used for multiple copies. Fanfold paper from 4-inch to 14-7/8 inches wide may be used with adjustment for pin-feed tractors. The print rate is dependent upon the data and the number of columns to be printed. Characters are printed 20 (24 on 132-col. model) at a time and if 20 (24) or less are used the rate can be as high as 1100 lines per minute.

### 2.4.1 Operation

Characters are loaded into the printer memory via the LPB (Line Printer Buffer) serially by character. When the memory becomes full (20 characters) they are automatically printed. This continues until the full 80 columns have been printed or a special character is recognized. The 132-column model prints 24 characters at a time. The special characters (non-printing) are:

CR (015<sub>s</sub>) Carriage Return. Causes the currently-stored characters to be printed, and resets the column counter to 1 (the next printing character loaded would print in column 1). Does not advance the paper.

LF (012) Line Feed. Causes the currently-stored characters to be printed, then resets the column counter to 1 and advances the paper one line.

FF (014.) Form Feed. Causes the currently-stored characters to be printed, then resets the column counter to 1 and advances the paper to top of next page.

LP11 HIGH SPEED LINE PRINTER

### 2.4.2 Programming

REGISTER Line Printer Status (LPS) Line Printer Data Buffer (LPB) ADDRESS 777514 777516

### Line Printer Status Register (LPS)

BIT NAME 15 Error DESCRIPTION

Set when an error condition exists in the printer. Errors are:

- a) Power off

- b) No paper

- c) Printer drum gate open

- d) Over temperature alarm

- e) Printer placed OFF LINE

May be read only. Reset only by manual correction of error condition.

14-8 Not Used

7 Done

6

Set whenever printer is ready for next character to be loaded. Indicates that previous function is either complete or has been started and continued to a point when the printer may accept the next command. May be read only. Set only by printer condition. Will not be set if printer is OFF-LINE.

Interrupt Enable

May be set or cleared under program control. Cleared by INIT signal on UNIBUS (RESET instruction or START console function). When set, an interrupt will be requested when DONE or ERROR becomes

a 1.

5-0 Not used

### Line Printer Data Buffer Register

RIT NAME DESCRIPTION

15.7 Not used

7-bit ANSCII character buffer. Characters 6-0 DATA

> are transferred to the printer by loading this buffer. The data in this buffer cannot

be read - it will always read 0.

2.4.3 Programming Example INTERRUPT SERVICE ROUTINE

:VECTOR TO SERVICE ROUTINE 200: LPSERV

SERVICE AT PRIORITY 4 242: 200

MAIN: BIS # 100,LPS :ENABLE INTERRUPT

LPSERV: TST LPS CHECK FOR ERROR

**BMI ERROR**

MOV RO. (SP) :SAVE RO

MOV BUFADR.RO :GET BUFFER POINTER

LOAD: MOVB (R0) + ,LPB :LOAD PRINTER BUFFER

> CMP RO, BUFEND :END OF DATA?

BHI PROOMP :YES, GO TO PRINT COMPLETE.

TSTB LPS :NO. CHECK DONE

BMI LOAD :NOT FULL, GET ANOTHER CHAR.

EXIT: MOV RO, BUFADR :SAVE BUFFER POINTER

MOV(SP) + R0:RESTORE RO

RTI

2.4.4 Specifications Printable Characters:

Character Set: 64 or 96

Type: Open Gothic print

Size: Typically 0.095 inches high and 0.065 inches wide

Characters: 64-character set

96-Character set

Code format: ANSCIL Characters per line: 80 or 132

Character drum: 1760 rpm(64 character drum) Speed: 1180 rpm(96 character: drum) Print Rate:

80-column Model

64 character: 356 Lines/minute, columns 1-80

460 Lines/minute, columns 1-60 650 Lines/minute, cloumns 1-40 1110 Lines/minute, columns 1-20

96 character: 253 Lines/minute, columns 1-80

330 Lines/minute, columns 1-40 478 Lines/minute, columns 1-20

132-Column Model

64 character: 245 Lines/minute, columns 1-132

290 Lines/minute, columns 1-120 356 Lines/minute, columns 1-96 460 Lines/minute, columns 1-72 650 Lines/minute, columns 1-48 1110 Lines/minute, columns 1-24

96 character: 173 Lines/minute, columns 1-132

205 Lines/minute, columns 1-120 253 Lines/minute, columns 1-96 330 Lines/minute, columns 1-72 478 Lines/minute, columns 1-48

843 Lines/minute, columns 1-24

80 column 132 column

Height: 46 inches 46 inches

Width: 24 inches 48 inches

Depth: 22 inches 25 inches

Weight: 200 pounds 220 pounds

Control: The LP11 controller is a "small peripheral con-

troller" which occupies 1/4 of a DD11-A or equiva-

lent space in a PDP-11 Family processor.

Operating Temperature: 50 - 110 degrees F

Humidity: 10%-80% (non-condensating)

Power Requirements

Printer: 117 Vac  $\pm$  10%; 60 Hz $\pm$ or 3 Hz, single phase or

234 Vac + 10%; 50 Hz + + Hz, single phase 250

Watts

Control: Supplied by H720 in mounting box where the con-

trol is mounted.

Signal Cable: 25 foot interconnecting signal cable is supplied

with system. Maximum allowable cable length is

100 feet.

### 2.5 PUNCHED CARD READER - CR11 AND MARK SENSE CARD READER - CM11

Model CR11 Card Reader reads EIA standard 80-column punched data cards at 300 cards per minute; model CM11 reads 40-column mark-sense cards, which can have punched holes, at 200 cards per minute.

The punched card reader uses a vacuum picker which works in conjunction with riffle air so that card wear is insignificant, card jam virtually impossible and the reader extremely tolerant of damaged cards. The riffling action separates the cards in the input hopper to prevent sticking. The picker uses a strong vacuum to grasp the bottom card and deliver it to the read station on demand. The picker and associated throat block prevent the unit from multiple picking to the extent that taped or stapled cards are not allowed to enter the card track. In such cases the reader stops with pick check alarm. The operator can separate the cards and enter them into the input hopper for normal reading. The card track is very short, so that, only one card is in motion at a time. The combination of damaged card tolerance, gentle card handling and short card track provide virtually jam-proof operation.

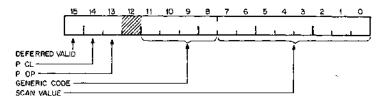

### 2.5.1 Operation

Cards are read by column, beginning with Column 1. A select instruction starts the card moving past the read station. Once a card is in motion, all 80 columns are read. Column information is read in one of two program-selected modes: card image or compressed code. In the card image mode 12 information bits in one column are loaded into the data buffer and are available to the program at CRB1 address. In the compressed code mode, the card image is encoded into 8-bit bytes and is available to the program at CRB2 address. A punched hole is interpreted as binary 1, and the absence of a hole as binary 0

### 2.5.2 Programming

| REGISTER                       | ADDRESS |

|--------------------------------|---------|

| Card Reader Status (CRS)       | 777160  |

| Card Reader Data Suffer (CRB1) | 777162  |

| Card Reader Data Buffer (CRB2) | 777164  |

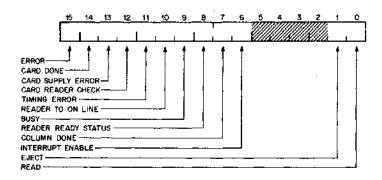

### Card Reader Status Register (CRS)

CM11 MARK SENSE CARD READER

CR11 PUNCHED CARD READER

| BIT<br>15 | NAME<br>Error           | DESCRIPTION When set, it indicates that an error has occurred.                                                                                                                                                                                     |

|-----------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14        | Card Done               | When set, indicates that one card has passed through the read station and another one may be demanded from the input hopper.                                                                                                                       |

| 13        | Card Supply Error       | When set indicates that the input hopper is empty or output stack is full. This signal is provided by mark sense card readers only and is not normally available with punched card units.                                                          |

| 12        | Card Reader Check       | Set to indicate abnormal condition in the card reader. Four conditions can cause this bit to be set: a)Feed error b)Motion error c)Stack Fail d)Dark Light Check These signals are only available from mark sense readers.                         |

| 11        | Timing Error            | When set it indicates that a new column of data arrived into the CRB before the previously loaded column was attended to by a program.                                                                                                             |

| 10        | Reader To on Line       | Indicates that the reader went on-line. Sensing an error or operating the stop switch on the card reader panel causes the reader to go off-line. Operating the start switch brings the reader on-line providing no error causing condition exists. |

| 9         | Busy                    | Indicates that a card is being read.                                                                                                                                                                                                               |

| 8         | Reader Ready Status     | When set, indicates the reader is off line; O indicates on-line and hence ready to accept read commands.                                                                                                                                           |

| 7         | Column Date             | Indicates that a column of data is ready in CRB.                                                                                                                                                                                                   |

| 6         | Reader Interrupt Enable | If declared as "1" while loading the status register, this bit allows the CARD DONE, COLUMN DONE, or ERROR bit, to cause a program interrupt.                                                                                                      |

| 5-2 |       | Not used                                                                                                                          |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| 1   | Eject | When set, column ready flag is inhibited from setting. However, data transfers between card reader and data buffer do take place. |

| 0   | Read  | If declared as "1"while loading the status register, this bit allows the feed mechanism to deliver a card to the read station.    |

A program can load and read information from the Card Reader Status (CRS) register using appropriate instructions and considering the following limitations:

- a. Bits 15-7 can only be read on the bus.

- b. COLUMN DONE bit is automatically cleared by reading the Data Buffer.

- c. Bits 15-8 are automatically cleared when an attempt to load the status register is made. However, if this loading is to read a card, and an error condition requiring manual intervention has not been attended by the operator, appropriate error bit will be set again to cause an interrupt Commands to READ CARD under these circumstances is not honored.

- d. BIT 0 is always read as zero on the bus.

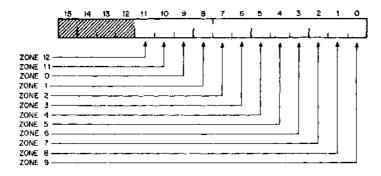

## Card Reader Data Buffer Register (CRB1, CRB2)

No information can be loaded into the Card Reader Data Buffer (CRB1) by any program; the content of this register can only be read.

Data from one column at a time of the card is loaded into this register.

| BIT   | DESCRIPTION |

|-------|-------------|

| 15-12 | NOT USED    |

| 11    | ZONE 12     |

| 10    | ZONE 11     |

| 9     | ZONE O      |

| 8     | ZONE 1      |

| 7     | ZONE 2      |

| 6     | ZONE 3      |

| 5     | ZONE 4      |

| 4     | ZONE 5      |

| 3     | ZONE 6      |

| 2     | ZONE 7      |

| 1     | ZONE 8      |

| 0     | ZONE 9      |

If the data buffer is addressed at CRB2, the 12-bit content is compressed into an 8-bit character by an encoding network before getting on to the bus as low order byte. The 8-bit code is:

| BIT<br>15-8 | DESCRIPTION<br>NOT USED                                                                                      |

|-------------|--------------------------------------------------------------------------------------------------------------|

| 7           | ZONE 12                                                                                                      |

| 6           | ZONE 11                                                                                                      |

| 5           | ZONE 10                                                                                                      |

| 4           | ZONE 9                                                                                                       |

| 3           | ZONE 8                                                                                                       |

| 2-0         | DATA encoded as follows:                                                                                     |

|             | 000 = ZERO ZONE 1-7                                                                                          |

|             | 001 = ZONE 1<br>010 = ZONE 2<br>011 = ZONE 3<br>100 = ZONE 4<br>101 = ZONE 5<br>110 = ZONE 6<br>111 = ZONE 7 |

In case of multiple zones twice, bits will be the inclusive OR of the octal codes of the zones.

2,5.3 Specifications

Speed: Up to 300 cards per minute (punched)

Up to 200 cards per minute (mark)

Hopper Capacity: 600 cards (400 cards mark sense)

Size (complete unit): 19 1/4 inches wide x 11 inches high x 14 inches

deep

Weight: 60 lbs

Environmental: + 50 degrees to + 122 degrees F. 10-90% humid-

ity, non-condensing

Input Power: 117± 10% 60 Hz 234 ± 10% 50 Hz

234  $\pm$  10% 50 Hz Single Phase

Power Consumption: 950 VA starting 400 VA running

BR 6 (may be changed by jumper)

Interrupt Vector Address: 230

#### 2.6 DECWRITER LA30

Interrupt Priority:

The LA30 DECwriter is a fast, reliable and low cost data terminal. It prints from a set of 64 characters at speeds up to 30 characters per second. Data entry is made from either a 97- or 128-character keyboard. It produces an original and one copy on a standard 9 7/8-inch wide, tractor-driven continuous form.

The DECwriter is delivered with an attractive stand. The noise generated by the terminal is less than that of an electric typewriter, a feature, welcomed in an office environment. Because of its low price, the DECwriter is particularly appropriate for systems requiring large numbers of highly reliable printer/terminals.

High reliability has been achieved through reduction of the number of mechanical parts. Clutches, brakes, dashpots and other similar parts have been eliminated from the printing mechanism. Instead, the DECwriter generates a 5 x 7 matrix. Seven solenoid-driven, spring-loaded pins are arranged vertically in the printing head. The head is advanced by solid-state logic; drive circuitry actuates selected pins to generate characters.

## 2.6.1 Programming

The LA30 interfaces to the PDP-11 via the LC11A Controller. All software control of LC11A is accomplished via four device registers. These are assigned memory addresses and can be read or loaded (with the exceptions noted) using any instruction that refers to their address.

| REGISTER                       | ADDRESS  |

|--------------------------------|----------|

| Keyboard Status Register (KBS) | 777560   |

| Keybuffer Register (KBB)       | 777562   |

| Printer Status Register (PRS)  | 777564   |

| Printer Buffer Register (PRB)  | , 777566 |

## Keyboard Status Register (KBS)

LA30-DECwriter

| BIT<br>15∙8 | NAME<br>Unused   | DESCRIPTION                                                                                                                  |

|-------------|------------------|------------------------------------------------------------------------------------------------------------------------------|

| 7           | Done             | Character available in Buffer cleared by INIT: cleared by referencing data buffer. Causes interrupt when $1D=1$ . Read only. |

| 6           | Interrupt Enable | When set, it enables done to cause interrupt, Cleared by INIT.                                                               |

| 5-0         | Unused           |                                                                                                                              |

## Keyboard Buffer Register (KBB)

BIT NAME 15-7 Unused DESCRIPTION

6-0 Data Buffer Holds character keyed in from keyboard. Read only.

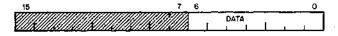

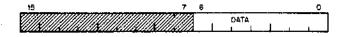

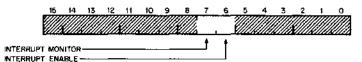

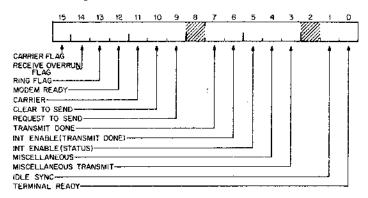

## Printer Status Register (PRS)

|         |           |             | 1_10  |  |

|---------|-----------|-------------|-------|--|

| READY-  |           | <del></del> | <br>1 |  |

| INTERRU | PT ENABLE |             | <br>  |  |

|         |           |             |       |  |

15-8 Unused 7 Ready

NAME

BIT

## DESCRIPTION

Printer available. Set on power of printer, reset or print. Strobe leading edge, is set when printing is complete. Note READY is set 2µs after CR is received by printer. This is to allow receipt of non-printing characters during carriage return time, i.e. LF. If a printing character is received during carriage return time, READY is reset and will be set after CR and printing are complete. READY will cause interrupt if ID = 1. Read only.

6 Interrupt Enable When set, enables READY to cause inter-

rupt. Cleared by INIT.

5-0 Unused

## Printer Buffer (PRB)

BIT 15-7 NAME

Unused

6-0

Data Buffer

DESCRIPTION

DATA BUFFER - Transfers the data from

the UNIBUS to the printer. Printer holds character strobed in to print. Load only.

Any instruction that could modify PRB as a byte or word clears READY and initiates printing.

## 2.6.2 Programming Examples

Read a character (from keyboard)

LOOP: TST TKS

: look for DONE

**BPL LOOP**

: Wait if DONE = 0-

READ: MOVITKB: RO

: Read character

ECHO keyboard

ECHO: TSTB TKS

: Character available?

**BPL ECHO**

: Wait if DONE = 0

STALL: TSTB TPS : Is punch readyff

**BPL STALL**

: Wait if READY = 0

BR ECHO

2.6.3 LA30 Specifications Printing Speed:

30 characters per second, asynchronous,

300ms carriage return

30 line feeds/sec

Line Length: Character Spacing: 80 character positions

10 characters per inch

Line Spacing:

6 lines per inch

Paper:

9.7/8 inches wide - tractor driven continuous form original plus one copy. With adjustment, up to 6

copies.

Typeface:

5 x 7 dot matrix

**Printing Characters:**

64 upper case ASCII subset (lower case codes print

as upper case)

Ribbon: 1/2 inch x 120 feet, nylon

Code: USASCII-1968 characters

Temperature: 50°F. - 130°F.

Humidity: 5-90% (noncondensing)

Dimensions: 20 1/2 inches wide x 31 inches high x 24 inches

deep

Interface: LC11A

DC Power: Self-contained

Types: LA30 PA 115V/60Hz

LA30 PB 234V/60Hz LA30 PC 115V/50Hz LA30 PD 234V/50Hz

# **Magnetic Tape Options**

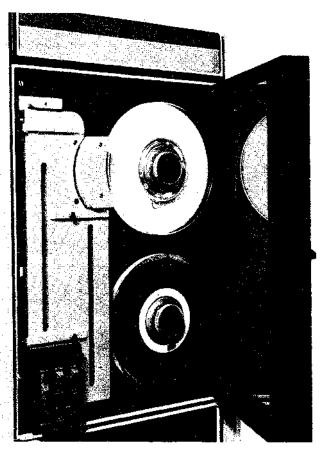

Two types of magnetic tape options are available to PDP-11 users:

- Small, dual 3.9 inch reel DECtape systems

- Large single 10 1/2-inch reel Magtape systems (industry compatible).

Both types of devices offer high performance at low cost. DECtapes are ideal for applications which do not require writing, reading or storage of large volumes of data. Magtapes, however, are suitable for handling large volumes of data.

## 3.1 DECTAPE TC11/TU56

#### 3.1.1 Introduction

The TC11/TU56 is a dual-unit, bidirectional magnetic-tape transport system for auxiliary data storage. Low cost, low maintenance and high reliability are assured by:

- simply designed transport mechanisms which have no capstans and no pinch rollers.

- hydrodynamically lubricated tape guiding (the tape floats on air over the tape guides while in motion)

- · redundant recording

- Manchester recording techniques (virtually eliminate drop outs)

Each transport has a read/write head for information recording and playback on five channels of tape. The system stores information at fixed positions on magnetic tape as in magnetic disk or drum storage devices, rather than at unknown or variable positions as in conventional magnetic tape systems. This feature allows replacement of blocks of data on tape in a random fashion without disturbing other previously recorded information. In particular, during the writing of information on tape, the system reads format (mark) and timing information from the tape and uses this information to determine the exact position at which to record the information to be written. Similarly, in reading, the same mark and timing information is used to locate data to be played back from the tape.

The DECtape system consists of the TU56 dual transport, the TC11 Control (which will buffer and control information for up to four dual transports) and DECtape 3/4-inch magnetic tape on 3.9-inch reels.

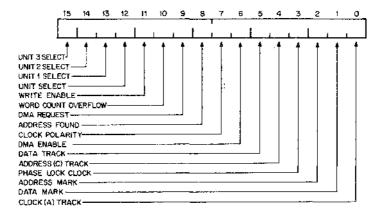

## 3.1.2 Operation

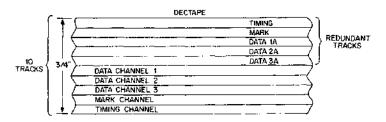

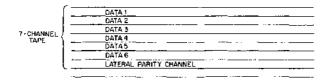

The system utilizes a 10-track read/write head. On a tape the first five tracks include a timing track, a mark track, and three data tracks. The other five tracks are identical counterparts and are used for redundant recording to increase system reliability. The redundant recording of each character bit on non-adjacent tracks materially reduces bit dropout and minimizes the effect of skew. The use of Manchester phase recording, rather than amplitude sensing techniques, virtually eliminates dropouts.

The timing and mark channels control the timing of operations within the control unit and establish the format of data contained on the information channels. The timing and mark channels are recorded prior to all normal data reading and writing on the information channels. The timing of operations performed by the tape drive and some control functions are determined by the information on the timing channel. Therefore, wide variations in the speed of tape motion do not affect system performance.

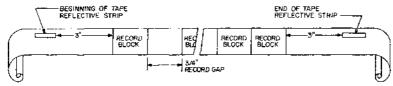

The standard format tape is divided into 578 blocks. The structure of each block is symmetric; block numbers and checksums are recorded at both ends of a block and thus searching, reading, or writing can occur in either direction. However, a block read in the opposite direction than it was written will have the order of the data words reversed.

Figure 3-1 - DECtape Format

Information read from the mark channel is used during reading and writing data to indicate the beginning and end of data blocks and to determine the functions performed by the system in each control mode. The data tracks are located in the middle of the tape where the effect of skew is minimum. The data in one bit position of each track is referred to as a line or as a character. Since six lines, or characters, make up a word, the tape can record 18-bit data words. During normal data writing, the Controller disassembles the 18-bit word and distributes the bits so they are recorded as six 3-bit characters. Since PDP-11 words are 16 bits long, the Controller writes the extra two bits 0's and ignores them when reading. However, during special modes, the extra two bits can be written and recovered.

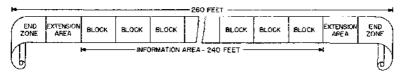

A 260-foot reel of DECtape is divided into three major areas: end zones (forward and reverse), extension zones (forward and reverse), and the information zone. The two end zones (each approximately 10 feet) mark the end of the physical tape and are used for winding the tape around the heads and onto the take-up reel. These zones never contain data.

The forward and reverse extension areas mark the end of the information region of the tape. Their length is sufficient to ensure that once the end zone is entered and tape motion is reversed, there is adequate distance for the transport to come up to proper tape speed before entering the information area.

The information area, consists of blocks of data. The standard is a nominal 578 blocks, each containing 256 data words (nominally). In addition each block contains 10 control words.

Figure 3-2 - DECtape Block Arrangement

The blocks permit digital data to be partitioned into groups of words which are interrelated while at the same time reducing the amount of storage area that would be needed for addressing individual words. A simple example of such a group of words is a program. A program can be stored and retrieved from magnetic tape in a single block format because it is not necessary to be able to retrieve only a single word from the program. It is necessary, however, to be able to retrieve different programs which may not be related in any way. Thus, each program can be stored in a different block on the tape.

Since DECtape is a fixed address system, the programmer need not know accurately where the tape has stopped. To locate a specific point on tape he must only start the tape motion in the search mode. The address of the block currently passing over the head is read into the DECtape control and loaded into an interface register. Simultaneously, a flag is set and a program interrupt can occur. The program can then compare the block number found with the desired block address and tape motion continued or reversed accordingly.

TU56 DECtape Unit

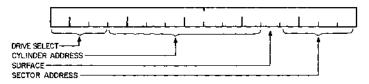

## 3.1.3 Programming

All transport operations are controlled by the controller from program instructions. The controller selects the transport, controls tape motion and direction, selects a read or write operation and buffers data transferred.

The controller can select any one of eight commands that control operation of the DECtape system. When the system is operated on-line, these commands are used for reading or writing data on the tape and for controlling tape motion. The desired command is selected by the program which sets or clears bits 03, 02, and 01 in the command register (TCCM) to specify an octal code representing the desired command.

#### The commands are:

| OCTAL<br>CODE<br>0 | MNEMONIC SAT | FUNCTION<br>Stops all tape motion.                                                                                                                                                                        |

|--------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | RNUM         | Finds the mark track code that identifies<br>the block number on the tape in the se-<br>lected tape unit. Block number found is<br>available in the data register (TCDT).                                 |

| 2                  | RDATA        | Assembles one word of data at a time and transfers it directly to memory. Transfers continue until word count overflow, at which time data is read to the end of the current block and parity is checked. |

| 3                  | RALL         | Reads information on the tape that is not read by the RDATA function.                                                                                                                                     |

| 4                  | SST          | Stops all tape motion in selected transport only.                                                                                                                                                         |

| 5                  | WRTM         | Writes timing and mark track information on blank DECtape. Used for formatting new tape.                                                                                                                  |

| 6                  | WDATA        | Writes data into the three data tracks. 16 bits of data are transferred directly from memory.                                                                                                             |

| 7                  | WALŁ         | Writes information on areas of tape not accessible to WDATA function.                                                                                                                                     |

|                    |              |                                                                                                                                                                                                           |

All software control of the TC11 DECtape system is performed by means of five device registers. They can be read or loaded using any PDP-11 instruction that refers to their address.

| REGISTER                           | ADDRESS         |

|------------------------------------|-----------------|

| Control and Status Register (TCST) | 777340          |

| Command Register (TCCM)            | 777 <b>34</b> 2 |

| Word Count Register (TCWC)         | 777344          |

| Bus Address Register (TCBA)        | 777346          |

| Data Register (TCDT)               | 777350          |

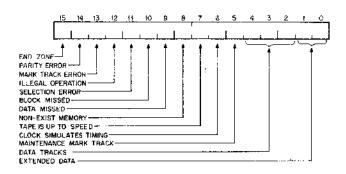

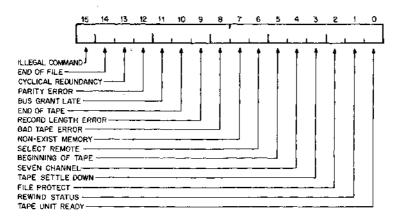

## Control and Status Register(TCST)

BIT

NAME

DESCRIPTION

| 15 | End Zone (ENDZ)        | Indicates that the selected tape unit is in an end zone region of the tape. Cleared by INIT; cleared by loading a 0 into bit 15 (ERROR) of command register; cleared by loading a 1 into bit 00 (D0) of the command register. Stops selected tape unit.                                               |

|----|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Parity Error (PAR)     | Indicates a parity error. The parity error occurs during RDATA function if the calculated and written checksums disagree, Cleared in the same manner an ENDZ.                                                                                                                                         |

| 13 | Mark Track Error(MTE)  | Indicates that an error occurred during decoding of the mark track. Stops selected tape unit. Cleared in the same manner as ENDZ (bit 15).                                                                                                                                                            |

| 12 | Iffegal Operation(ILO) | Indicates an iflegal operation caused by a conflict in switch positions of the WRITE ALL, WRITE T&M, and WRITE ENABLE/WRITE LOCK switches. These conflicts are:  a. WRITE LOCK on during WRTM, WALL, or WDATA modes b. WRITE T&M switch off during WRTM mode c. WRITE ALL switch off during WALL mode |

| 11 | Selection Error(SELE)  | Stops selected tape unit. Cleared when switches reset to valid positions and oper-                                                                                                                                                                                                                    |

|     |                              | ation repeated. Indicates that the program has either selected a non-existent tape unit or has attempted to select more than one tape unit. Stops selected tape unit. Disabled if MAINT bit (bit 13 in TCCM) is set or if function is SAT (bits 03, 02, and 01 in TCCM cleared). Cleared when unit selection switches set to valid positions and selection repeated. |

|-----|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10  | Block Missed (BLKM)          | Indicates a block was missed. The transfer from read block number (RNUM) to read data (RDATA) or write data (WDATA) functions occurred too late. Also, indicates switch from RDATA to WDATA was too late. Cleared in the same manner as ENDZ (bit 15).                                                                                                               |

| 9   | Data Missed (DATM)           | Indicates data was missed. Request for data transfer not honored in time during RDATA, WDATA, WALL, or RALL. Cleared in the same manner as ENDZ (bit 15).                                                                                                                                                                                                            |

| 8   | Non-Existent Memory(NEX)     | Indicates non-existent memory. This occurs when TC11 Controller is bus master and does not receive a SSYN response within 20 $\mu s$ after asserting MSYN. Cleared in the same manner as ENDZ (bit 15).                                                                                                                                                              |

| 7   | Tape Is Up To Speed(UPS)     | Indicates that selected tape unit is up to speed required for proper operation. Cleared by INIT; cleared when UNIT SELECT or REV bit is changed. Set when unit is up to speed; set when MAINT bit (bit 13 in command register) is set.                                                                                                                               |

| 6   | Clock Simulates Timing (CLK) | Used to simulate timing track. May be loaded when MAINT bit is set. When CLK is set, produces TP1: when cleared, produces TPO.                                                                                                                                                                                                                                       |

| 5   | Maint Mark Track (MMT)       | Used to simulate the bit read from the mark track. May be loaded when MAINT bit is set. Cleared by INIT.                                                                                                                                                                                                                                                             |

| 4.2 | Data Tracks (DT)             | Used to simulate output of the read amplifer. When MAINT bit is set, DTO loads into RWB2 and reads as RWB5; DT1 loads into RWB1 and reads as RWB4; DT2 loads into RWB0, reads as RWB3.                                                                                                                                                                               |

| 1.0 | Extended Data (XD)           | Extended data bit 17 or 16, which allow reading and writing on areas of the tape not accessible during 16-bit word transfers. Cleared by INIT,                                                                                                                                                                                                                       |

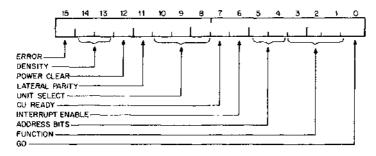

## Command Register (TCCM)

|           | 00                    |                                                                                                                                                                                                                                                |

|-----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT<br>15 | NAME<br>Error         | DESCRIPTION Indicates an error condition which is the inclusive OR of all error conditions (bits 15-8 in TCST). Causes an interrupt if enabled (see bit 6). Clears errors (except ILO and SELE) when loaded with zero. Sets READY bit (bit 7). |

| 14        | Unused                |                                                                                                                                                                                                                                                |

| 13        | Maintenance (MAINT)   | Used for maintenance functions, When set, enables operation of bits 6-2 in the TCST. Cleared by INIT.                                                                                                                                          |

| 12        | Delay Inhibit(DINHB)  | Set to inhibit the delay associated with<br>bringing a tape unit up to speed when<br>reselecting a tape unit known to be up to<br>speed by a previous command. Cleared by<br>INIT.                                                             |

| 11        | Tape Direction (REV)  | Specifies direction of tape motion. When set, specifies reverse motion; when cleared, specifies forward motion. Cleared by INIT.                                                                                                               |

| 10.8      | Unit Select           | Specify the number of the tape unit which is to receive the desired command. These three bits are set or cleared to represent an octal code which corresponds to the unit number of the tape unit to be used. Cleared by INIT.                 |

| 7         | READY                 | Indicates that the TC11 controller is ready to receive a new command. Cleared when DO (bit 00) is set. Set when command execution is complete; set by INIT or ERROR (bit 15). Read only.                                                       |

| 6         | Interrupt Enable (IE) | Allows an interrupt to occur provided either READY (bit 07) or ERROR (bit 15) is set. Cleared by INIT.                                                                                                                                         |

| 5-4       | Ext Bus Address (XBA) | Used to specify address line 17 (XBA17)                                                                                                                                                                                                        |

or address line 16 (XBA16) in direct memory transfers. Increments with the TCBA, Cleared by INIT.

3-1 Function Bits

Specify a command to be performed upon the selected transport. Cleared by INIT to SAT.

0 DO:

Loaded with a 1 when a new function is given. Clears READY

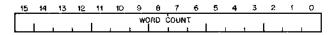

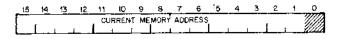

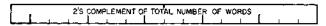

## Word Count Register (TCWC)

BIT NAME 15-0 Word Count

## DESCRIPTION

Contains two's complement of the number of words to be transferred. This register counts the number of word transfers made during RDATA (read data) and WDATA (write data) functions. When one of these functions is initiated, the word count register is loaded. The register is incremented by 1 after each transfer. When the contents of the register equals all zeros, further transfers are inhibited. Cleared by INIT. (Note: This register must not be modified by using byte instructions. Use only word instructions when loading).

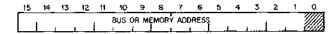

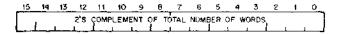

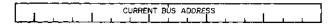

## **Bus Address Register (TCBA)**

BIT NAME 15-1 Address

#### DESCRIPTION

Specify the bus or memory address to or from which data is to be transferred during RDATA (read data) and WDATA (write data) operations. These bits are used in conjunction with bits XBA17 and XBA16 in the command register. After each transfer (during RDATA and WDATA) is made, this register is incremented to advance it to the next word location. The BA bits participate in the incrementation; they are a logical extension to this register. Cleared by INIT. (Note: the bus address register must not be modified by using byte instructions when loading this register).

0 Unused

## Data Register (TCDT)

BIT NAME 15-0 Data

## DESCRIPTION

Contains data word to be read from or written on the magnetic tape. These bits and bits XD17 and XD16 in the status register form three six-bit shift registers which are active during control operations. These 18 bits correspond one to one with the six three-bit characters read or written on the tape.

The data register accepts information under program control during WALL (write all) and WRTM (write timing and mark) operations. During RALL (read all) and RNUM (read block number) operations, the data register contains data read from the tape. During WDATA (write data) and RDATA (read data) operations, the data register is used to buffer information between the controller and memory. Cleared by INIT.

Note: The data register must not be modified by using byte instructions. Use only word instructions when loading this register.

## 3.1.4 Programming Examples

The following two examples represent typical methods of programming the TC11 Controller. The first example finds a specified block. The second example is a routine for writing data into a specific block.

a. Routine to find a specified block

;ENTER WITH RO = BLOCK WANTED ;FINDS BLOCK IN FORWARD DIRECTION

SEARCH:

MOVE RO. BWANT

SUB #3, BWANT MOV #4003, TCCM

UNIT O, REVERSE, RNUM, DO

L00P1:

BIT #100200, TCCM

CHECK READY AND ERROR

BEQ LOOP1 BMI ERROR

SUB TCDT, #BWANT

;CHECK BLOCK FOUND

BLT SEARCH

FORWRD:

MOV RO, BWANT

MOV #3, TCCM

JUNIT O, FORWARD, RNUM

DQ

:OFFSET

L00P2:

BIT #100200, TCCM

CHECK FOR READY AND ER-

ROR

BEQ LOOP2 BMI ERROR

SUB TCDT, BWANT

:CHECK BLOCK FOUND

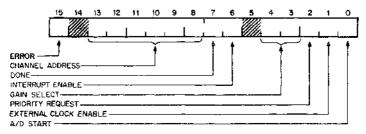

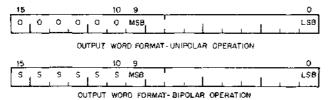

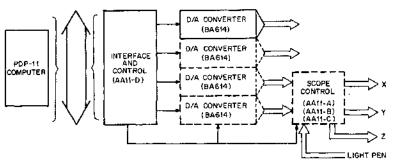

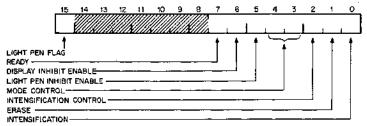

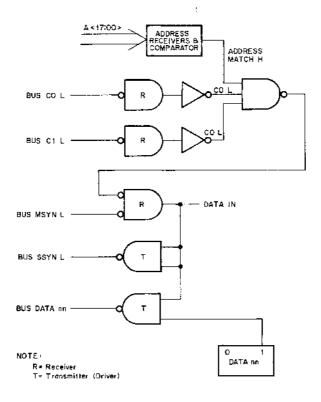

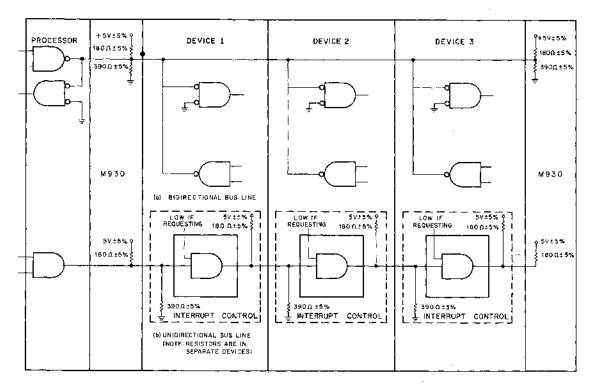

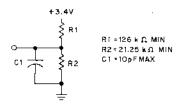

BGT FORWRD BLT SEARCH