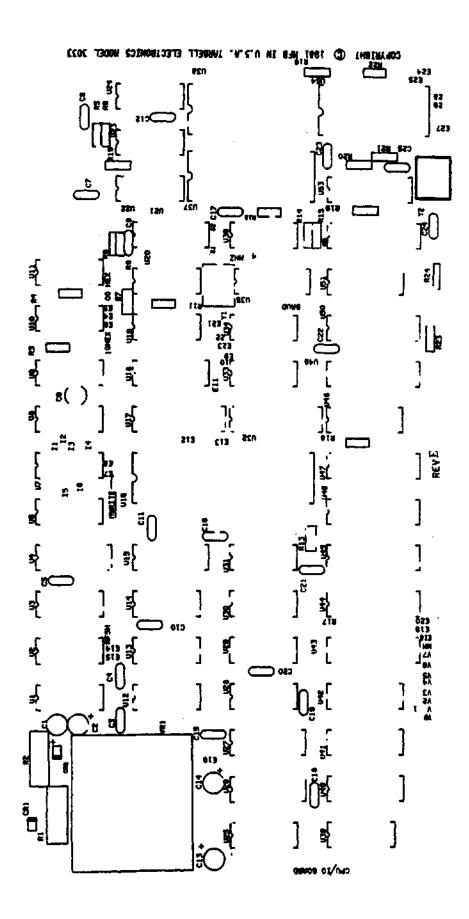

# C.P.U.A.IO BOARD MODEL OWNERS MANUAL

$\frac{1}{2} \left\{ \frac{1}{2} \left\{ \frac{1}{2}$

.

Copyright (c) 1980,1981,1982 Tarbell Electronics All Rights Reserved.

No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written permission of Tarbell Electronics, 950 Dovlen Place, Suite B, Carson, California, 90746 Tarbell Z-80 CPU Manual Rev E April 1,1982

.

|                   | Table of Contents |

|-------------------|-------------------|

| Fort Assignments  | Section 1         |

| Jumper Options    | Section 2         |

| Serial Ports      | Section 3         |

| Memory Management | Section 4         |

| Parts List        | Section 5         |

| Data Sheets       | Appendix          |

Tarbell Z-80 CPU Introduction

### April 8, 1981

The Tarbell Z-80 CPU board is designed to use the full power or the Z-80 CPU chip along with 2 serial ports, a timer chip, 8080 vector interrupt or Z-80 mode 2 interrupt, and extended memory management of 1 Megabyte with the capability of relocation on 4 Kbyte boundrys. The Tarbell Z-80 CPU board is designed around the IEEE S-100 standard and is directly compatible with all products sold by Tarbell Electronics.

The Tarbell Z-80 CPU board will run at either 2 MHz or 4 MHz by means of a jumper selection on the board.

The on-board timer, which is an 8253 timer chip, will generate timing intervals from 1 micro-sec. to 327 milli-sec. using 1 of the 3 timers available in the 8253. Provisions are made on the CPU board to chain the additional 2 timers together for increased time intervals. The 2 additional timers may also be used independently of the others.

The Tarbell Z-80 CPU has provisions for accepting 8080 vector restarts. The level of interrupt is also maskable with one exception in that neither RST 0 or RST 7 are maskable because of their use in CPM (r). The other 6 restarts are maskable by way of a register on an I/O port on the CPU board. As an option jumper, provisions have been made to allow the Mode 2 interrupt of the Z-80 to function.

The CPU board uses 2 8251 usarts for serial I/O operation. Each channel's baud rate is set by an on-board switch which controls an SMC-5016 baud rate chip. Baud rates from 50 to 19,200 are switch selectable for each channel. Each serial channel is RS-232 compatible with hand-shaking provided for DTR,RTS, DSR, and CTS lines.

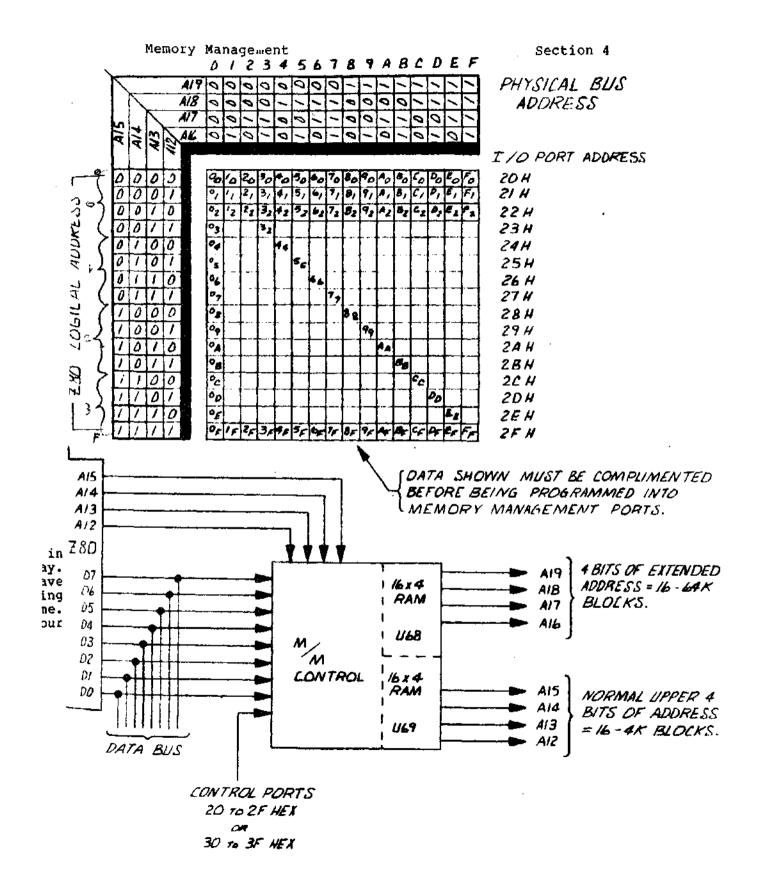

One unique feature of the Tarbell Z-80 CPU is it's Memory Management circuit. By using a ram mapping techinque, we can make the Z-80 appear to address 1 Megabyte address range, even though the Z-80 will only address 64 Kbytes directly. Besides the main advantage of being able to address 1 Megabyte of memory, the ram mapping technique also allows the programmer the ability to relocate software on 4 Kbyte boundries for dynamic memory allocation schemes.

Port assignments for the on-board I/O, Timer, Vector Interrupt mask port, and Memory Management are determined by jumpers E4, E5, and E6. When jumper E4 to E5 is connected, the base address for the I/O, Timer, and Vector Interrupt mask port starts at base 00 hex and the Memory Management ports start at 20 hex.

When jumper E4 to E6 is connected, the base address for the I/O, Timer, and Vector Interrupt mask port starts at 10 hex and the Memory Management ports start at 30 hex.

A breakdown of the ports and use will be described below.

Base address = 00 hex

(jumper E4 to E5)

| Port                                                                                                                                                                                       | use                                                                                                                                                                                                                                                                            | operation                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00 hex<br>01 hex<br>02 hex<br>03 hex<br>03 hex<br>04 hex<br>05 hex<br>05 hex<br>06 hex<br>07 hex<br>08 hex<br>09 hex<br>08 hex<br>09 hex<br>08 hex<br>00 hex<br>00 hex<br>00 hex<br>00 hex | serial port A<br>serial port A<br>serial port B<br>serial port B<br>counter 0<br>counter 1<br>counter 2<br>counter command port<br>interrupt latch clear<br>interrupt mask port<br>enable memory mang.<br>disable memory mang.<br>not used<br>not used<br>not used<br>not used | input/output data port<br>input status port/output init.<br>input/output data port<br>input status port/output init.<br>input/output<br>input/output<br>input/output<br>output only<br>input only<br>output only<br>output only<br>input only<br>input only<br>input only |

The Memory Management ports will be addressed starting at 20 H hex. OR 30 H

| Port         | use                    | operation                | 3FH   |

|--------------|------------------------|--------------------------|-------|

|              |                        |                          |       |

| 20 to 2F hex | init. memory mangement | output only, ram mapping | info. |

The initialization bytes for the memory management are as follows.

| Port   | Byte   |

|--------|--------|

|        |        |

| 20 hex | FF hex |

| 21 hex | FE hex |

| 22 nex | FD hex |

| 23 hex | FC hex |

| 24 hex | FB hex |

| 25 hex | FA hex |

| 26 hex | F9 hex |

| 27 hex | F8 hex |

| 28 hex | F7 hex |

### Port assignments for Tarbell Z-80 CPU-I/O Board

| 29 hex | F6 hex |

|--------|--------|

| 2A hex | F5 hex |

| 2B hex | F4 hex |

| 2C hex | F3 hex |

| 2D hex | F2 hex |

| 2E hex | Fl hex |

| 2F hex | F0 hex |

Because the ram on the CPU card can come up in any random bit pattern when power is first applied, the above initialization bytes must be sent out to set the ram into a known state before turning on the memory management for use. The above pattern sets the memory management for normal access to 64 Kbytes of system memory, and disables memory above 64 Kbytes by setting Al6,Al7,Al8, and Al9 to all zeros.

When the board is first powered up, the memory management is not enabled and the full 64 kbyte address space may accessed as if the memory management did not exist at all. In order to use the memory management, it must be initialized first, then turned on.

Section 1

÷.

Section 2

The Tarbell CPU may run at either 2 MHz or 4 MHz .

CPU Speed select

For 2 MHz operation - connect center to E2 \* For 4 MHz operation - connect center to E1

I/O Base Address Select

The base address of the onboard I/O ports may be set for either a base of 00 hex or a base of 10 hex. This allows you to move the CPU I/O ports to avoid any conflict which may exist with other boards in your system which use either of these base addresses.

For an I/O base of 00 hex - connect E4 to E5 \* For an I/O base of 10 hex - connect E4 to E6

Vector Interrupt Options

Two methods of vector interrupts may be used on this CPU board, but only one may be active at a time. One method is the normal 8080 interrupt vector which activates one of the restart vector lines on the S-100 bus. The other method uses the interrupt Mode 2 of the Z-80 and activates only the S-100 interrupt line (pin 73).

8080 interrupt mode - El6 open \* 2-80 interrupt mode 2 - El6 closed

NMI (Non-maskable Interrupt) Option

The non-maskable interrupt option has 3 possible configurations you may consider to use. As a note of caution, because the non-maskable interrupt of the Z-80 is locked to location 66 hex, the possibility of use while running CP/M does not look feasible because this location happens to be right in the middle of the file control block used by CP/M for file access. If you plan to use this CPU card in a stand-alone type system, then the whole situation is different. Typical uses for non-maskable interrupts are to monitor for power failures, errors due to parity bits in error, or monitoring hardware events which must have the highest possible priority in a system.

The three options are as follows:

Jumper El8 - NMI\ (direct input to Z-80 NMI pin.) Jumper El9 - PWRFAIL\ (system type power fail indicator.) Jumper E20 - ERROR\ (any status signal indication an error occured.)

Because these lines are suppose to be driven with open collector drivers, any or all of these jumpers may be tied together.

ī.

Section 2

# I/O Interrupts option

Each serial channel has provisions for generating an interrupt if needed. The outputs are all open collector, so they may be connected wired-or if you plan on using 1 interrupt line.

| Interrupt         |         | Connection |

|-------------------|---------|------------|

| Channel A         |         |            |

| Recieve Ready     | (RxRDY) | 15         |

| Transmitter Ready | (TxRDY) | 14         |

| Transmitter Empty | (TxE)   | 12         |

| Channel B         |         |            |

| Recieve Ready     | (RxRDY) | 16         |

| Transmitter Ready | (TxRDY) | 11         |

| Transmitter Empty | (TxE)   | 13         |

Timer options

The onboard timer has only 1 of the 3 internal timers committed. This timer is committed for use in generating an interrupt. This timer chip is driven by an external clock input frequency of 2 MHz from the CPU internal clock. The timer committed for this function is timer channel 2. The output of the timer sets a latch which drives the input of an 7406 open collector inverter. The output of the inverter may be connected to any of the 8 vector interrupt input lines (VIO to VI7). The latch is cleared by executing an input from port BASE+8 hex in your interrupt routine, where BASE is the base address you have chosen to use for your I/O port base.

The other 2 timers are available for general use with all the inputs available to each section of each timer. These 2 timers may be chained together for long time intervals, or may be used independently. For further information about the use of these timers, please refer to the end of this manual to the data sheets on the 8253 timer chip.

Below is a table of the jumpers for the unused timers.

E24 - counter 0 GATE input (pull up for enable if jumpered) E25 - counter 1 GATE input (pull up for enable if jumpered) E28 - counter 0 OUTPUT E29 - counter 1 OUTPUT E26 - counter 0 CLOCK input E27 - counter 1 CLOCK input

Section 2

Memory Management Option

The memory management is invisible when the CPU is first brought up in your system. You have the full 64K address space of the 2-80 cpu and will operate as a normal cpu card. This happens because the system reset clears the memory management to an off state.

To use the memory management on the CPU board, you must first initilize the on board memory chips as described in section 4 of this manual. After you have set the memory management chips up, you can enable it by doing an output instruction to port BASE+0A hex.

You may turn off the memory management at any time by doing an input instruction from BASE+0B hex. This will turn off the memory management circuit and you will have a normal 64K address space.

Mwrite

must Mars

PANEL PANEL

If your computer system does not have provisions for the generation of the Mwrite signal, you will find it generated on our CPU board. To enable this signal onto pin 68 of the S-100 bus, jumper E7 to E8. This signal is required by most memory boards in use today.

Used non-defined pins of S-100 bus Fin 21

To effectivly use the Z-80 interrupt Mode 2 with it's support I/O chips, the signal IORQ\ is needed. This signal can be made available on pin 21 by jumpering E9 to E10.

The signal MREQ\ is also available by jumpering Ell to ElO. This signal may be used by some dynamic memory boards in the future.

Pin 27

This line is being used for providing PWAIT for front panels. To use this feature jumper El2 to El3.

Pins 71 and 69

As part of the interrupt Mode 2 usage, some provision must be made for the daisy-chain of the Interrupt lines from each Z-80 support chip to the next. We would like to promote a standard which uses pin 71 as the IEI (interrupt enable input) line, and pin 69 as the IEO (interrupt enable output) line. This convention will be used for any support products which use any of the Z-80 I/O chips by Tarbell Electronics and Delta Products. We hope this will encourage other designers in the same direction.

nusi Pin 66

HAVE -----

Some dynamic memory boards have provisions for refreshing by using the Z-80 refresh signal. This signal may be made available to pin 66 by jumpering El4 to El5.

Section 2

Section 2

.

Wait States

Three options exist for wait states if needed.

I/O wait states

Ml wait states

Memory wait states.

The on board wait state generator only provideds 1 wait state and you may select any or all if needed. To select an wait state for I/O operations, jumper E23. To select an wait state for M1 cycles, jumper E21. To select an wait state for all memory cycles, jumper E22.

.

### Serial Port Description

### Section 3

The on-board serial ports are a pair of 8251's with full RS-232 handshaking. Each serial port has it's own baud rate generator which is controlled by an SMC-5016 baud rate generator. The baud rate is set in hardware by dip switch S-xx. The top four switch positions control Channel A baud rate, and the bottom four switch positions control Channel B baud rate. The layout of the switches are as follows.

S-xx

| A | [] |      |

|---|----|------|

| В | [] | Chan |

| С | [] | A    |

| D | [] |      |

| A | [] |      |

| В | [] | Chan |

| C | [] | в    |

| D | [] |      |

The following table shows the switch settings for desired baud a rate.

| Baud Rate | A   | в   | с   | D   |

|-----------|-----|-----|-----|-----|

|           |     |     |     |     |

| 50        | on  | on  | оп  | on  |

| 75        | off | on  | on  | on  |

| 110       | on  | off | on  | on  |

| 134.5     | off | off | on  | on  |

| 150       | on  | on  | off | on  |

| 300       | off | on  | off | on  |

| 600       | on  | off | off | on  |

| 1200      | off | off | off | on  |

| 1800      | on  | on  | on  | off |

| 2000      | off | on  | on  | off |

| 2400      | on  | off | on  | off |

| 3600      | off | off | on  | off |

| 4800      | on  | on  | off | off |

| 7200      | off | on  | off | off |

| 9600      | on  | off | off | off |

| 19200     | off | off | off | off |

Handshaking for the two serial ports is provided by the RS-232 line drivers and line receivers which are 1488's and 1489's by way of connector J2 at the top of the board. A break down of this connector is as follows:

| J2 pin number | channel | function      | in/out |

|---------------|---------|---------------|--------|

| 1             | A       | ground        | output |

| 2             | A       | ground        |        |

| 3             | A       | transmit data |        |

### Serial Port Description

| 4<br>5<br>6<br>7<br>8<br>9 | A<br>A<br>A<br>A | data terminal ready<br>request to send<br>receive data<br>data set ready<br>clear to send<br>+5 volts | output<br>output<br>input<br>input<br>input |

|----------------------------|------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 10                         |                  | +12 volts                                                                                             |                                             |

| 11                         |                  | -12 volts                                                                                             |                                             |

| 12                         |                  | ground                                                                                                |                                             |

| 13                         | В                | ťransmit data                                                                                         | output                                      |

| 14                         | В                | data terminal ready                                                                                   | output                                      |

| 15                         | В                | request to send                                                                                       | output                                      |

| 16                         | В                | receive data                                                                                          | inpūt                                       |

| 17                         | B                | data set ready                                                                                        | input                                       |

| 18                         | В                | clear to send                                                                                         | input                                       |

| 19                         | В                | ground                                                                                                |                                             |

| 20                         | В                | ground                                                                                                |                                             |

|                            |                  |                                                                                                       |                                             |

The I/O cable coming from the 20 pin connector on the CPU card to the pair of DB-25 connectors is defined as follows:

|            | RS-232<br>connect         | -                                                        | 20 pin<br>connector     |

|------------|---------------------------|----------------------------------------------------------|-------------------------|

| <br>A port | (2)<br>(3)<br>(4)<br>(5)  | Xmit Data (from cpu)<br>Recv Data (to cpu)<br>Rts<br>Cts | 3<br>6<br>5<br>8<br>) 7 |

|            | (6)<br>(7)<br>(20)        | Dsr (handshake line<br>Gnd<br>Dtr                        | ) 7<br>1,2<br>4         |

| pull up    | •5                        | +5<br>+12<br>-12                                         | 9<br>10<br>11           |

| <br>B port | (2)<br>(3)<br>(4)         | Xmit Data (from cpu)<br>Recv Data (to cpu)<br>Rts<br>Cto | 13<br>16<br>15<br>18    |

| B port     | (5)<br>(6)<br>(7)<br>(20) | Cts<br>Dsr (handshake line<br>Gnd<br>Dtr                 |                         |

Note: Software from Tarbell Electronics looks at DSR (pin 6 of RS-232 line), for handshaking with printers. This line is active low when the printer buffer full flag is active. This means that the cpu should stop sending characters until DSR goes high again. Some printers use Dtr (pin 20 of RS-232 line) as the handshake line back to the cpu. You should jumper pin 20 on the back side of the RS-232 connector board to pin 6 of the 20 pin connector. A hole has been provided for this connection. Some printers use the Alternate clear to send line on the RS-232 lines. This is usually pin pin 19 of the RS-232. This line should be connected to DSR (pin 6 of the 20 pin

Serial Port Description

Section 3

connector for proper handshaking). Some printers use clear to send for handshaking. If this is the case, you should jumper the clear to send line (pin 5 of the RS-232 line) to the DSR line (pin 6 of the 20 pin connecter) for proper handshaking.

If you are going to use a CRT on one port and a printer on the other, we would like to recommend that you use Chan A for the CRT port and Chan B for the printer port. This is the normal configuration that we here at Tarbell Electronics will be using in our software. The CRT port will use transmit data (J2 pin 3), receive data (J2 pin 6), and ground. The printer port will use transmit data (J2 pin 13), and some sort of buffer full handshaking, probably data set ready (J2 pin 17), and a ground. You should consult your printer and terminal manuals for any problems you may have.

As a service to our customers, we have provided some of the common printer configurations that we have checked out here. All of these configurations use the channel B port for the printer. As we become use other printers on the market, we will provide that information as well.

Page 4 starts the printer configuration section.

₽

NEC SHINMSILEL

EPSON MX-BO

ANADEX 9501

¢

DIABLU 1640

TI - 810

Memory Management

### Section 4

The on-board memory which is used for the Memory Management must be initialized before it is used. In order to use the CPU board in a normal 64 Kbyte system, the memory management would have to be set using the following subroutine.

| COUNT   | EQU  | 16 ;              | 16 values to move.                 |

|---------|------|-------------------|------------------------------------|

| MEMENB  | EQU  | ОАН ;             | enable port.                       |

| MEMPORT | EQU  |                   | either 20 Hex or 30 Hex for memory |

|         |      | i                 | management port base.              |

| ;       |      |                   |                                    |

| INIT:   | LXI  | D,TABLE ;         | point to memory discriptor table.  |

| INIT1:  | LXI  | B,COUNT SHL 8 OR  | MEMPORT                            |

| ILCOP:  | LDAX |                   | get a byte from table.             |

|         | CMA  | ;                 | compliment it for on-board memory. |

|         | OUTP | A ;               | output it to memory.               |

|         | ĨNR  | C ;               | bump port number to next.          |

|         | INX  | D ;               | point to next byte in table.       |

|         | DJNZ | ILCOP             | and loop 16 times till done.       |

|         | OUT  | MEMENB            | turn on memory management.         |

|         | RET  | ,                 | return to caller.                  |

| 1       |      |                   |                                    |

| TABLE:  | DB   | 00H,01H,02H,03H,0 | 04H,05H,06H,07H,08H                |

DB 09H, 0AH, 0BH, 0CH, 0DH, 0EH, 0FH

Now the situation arises where you may have multi-users on your system. You first will have to establish what users will be in what groups of memory at any user time slice. For example, you have 4 64 Kbyte memory boards. Your operating system will need 16 Kbytes of common memory for file operations. This will leave you with 48 Kbytes of user memory. This means that you will have 3 16 Kbyte blocks left over, 1 16 Kbyte block from each 64 Kbyte group. With these 3 16 Kbyte blocks, you would be able to run 5 users on your system, with each user sharing the one common area of the operating system. The following subroutine could be used to manage the memory useage.

BANKOSWITCH:

| Entry  | Reg A :                                                                                   | = user number (0                                                                            | to 4) to have the former take                                                                                                                                                                                                                                                                                                                                                               |

|--------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Exit   | User ba                                                                                   | ank selected                                                                                |                                                                                                                                                                                                                                                                                                                                                                                             |

| BANKL: | ADD<br>LXI<br>MOV<br>MVI<br>DAD<br>LXI<br>MOV<br>CMA<br>OUTP<br>INX<br>INR<br>DJNZ<br>RET | A<br>H, TABLE<br>C, A<br>B, 0<br>B, COUNT SHL 8<br>A, M<br>A $(R, GG <)$<br>H<br>C<br>BANKL | <pre>;double for computed index.<br/>;point to start of table pointers.<br/>;set up B,C for offset.<br/>;zero REG B.<br/>;H,L = User table value.<br/>OR MEMPORT ;count, port.<br/>;get memory init byte.<br/>;invert for on-board memory chips.<br/>;program the memory management.<br/>;bump pointer.<br/>;bump memory management port.<br/>;loop till done.<br/>;return to caller.</pre> |

Section 4

Memory Management

The on-board memory which is used for the Memory Management must be initialized before it is used. In order to use the CPU board in a normal 64 Kbyte system, the memory management would have to be set using the following subroutine.

| COUNT   | EQU  | 16 ;16 values to move.                       |

|---------|------|----------------------------------------------|

| MEMENB  | EQU  | OAH ;enable port.                            |

| MEMPORT | EQU  | 20H ;either 20 Hex or 30 Hex for memory      |

|         |      | ;management port base.                       |

| ;       |      |                                              |

| INIT:   | LXI  | D, TABLE ; point to memory discriptor table. |

| INIT1:  | LXI  | B, COUNT SHL 8 OR MEMPORT                    |

| ILOOP:  | LDAX | D ;get a byte from table.                    |

|         | CMA  | ; compliment it for on-board memory.         |

|         | OUTP | A joutput it to memory.                      |

|         | INR  | C ; bump port number to next.                |

|         | INX  | D ; point to next byte in table.             |

|         | DJNZ | ILOOP ; and loop 16 times till done.         |

|         | OUT  | MEMENB ;turn on memory management.           |

|         | RET  | ;return to caller.                           |

| ;       |      |                                              |

| TABLE:  | DB   | 00H,01H,02H,03H,04H,05H,06H,07H,08H          |

DB 09H, 0AH, 0BH, 0CH, 0DH, 0EH, 0FH

Now the situation arises where you may have multi-users on your system. You first will have to establish what users will be in what groups of memory at any user time slice. For example, you have 4 64 Kbyte memory boards. Your operating system will need 16 Kbytes of common memory for file operations. This will leave you with 48 Kbytes of user memory. This means that you will have 3 16 Kbyte blocks left over, 1 16 Kbyte block from each 64 Kbyte group. With these 3 16 Kbyte blocks, you would be able to run 5 users on your system, with each user sharing the one common area of the operating system. The following subroutine could be used to manage the memory useage.

BANKSSWITCH:

| ;<br>;Entry<br>;Exit<br>; | Reg <b>A</b> =<br>User ba                                                                 | = user number (0<br>ank selected | to 4) front to ADD 116 for most station                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------|-------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BANKL :                   | ADD<br>LXI<br>MOV<br>MVI<br>DAD<br>LXI<br>MOV<br>CMA<br>OUTP<br>INX<br>INR<br>DJNZ<br>RET | H,TABLE<br>C,A<br>B,O            | <pre>;double for computed index.<br/>;point to start of table pointers.<br/>;set up B,C for offset.<br/>;zero REG B.<br/>;H,L = User table value.<br/>R MEMPORT ;count, port.<br/>;get memory init byte.<br/>;invert for on-board memory chips.<br/>;program the memory management.<br/>;bump pointer.<br/>;bump memory management port.<br/>;loop till done.<br/>;return to caller.</pre> |

Parts List

Section 5

Qty. Descriptor Designator Resistors \_\_\_\_ 62 ohm 1 watt R1,R2 2 330 ohm 1/4 watt R11,R14,R15 3 15 1 K ohm 1/4 watt R3,R4,R7,R10,R12,R13,R16,R17 R18,R19,R20,R21,R22,R23,R24 4 4.7 K ohm 1/4 watt R5,R6,R8,R9 NW-15-1K Resistor pack 2 U40,U51 **U48** 1 NW-15-4.7K Resistor pack Capacitors \_\_\_\_\_ 20 .1 Mfd >10 volts C3,C4,C5,C7,C8,C9,C10,C11,C12 C15,C16,C17,C18,C19,C20,C21,C22 C23,C24,C25 10 Mfd 16 volt 4 C1,C2,C13,C14 1 22 Mfd 10 volt C6 Misc. ----DIP-SW8 8 position dip switch U35 HDR-20 20 pin header J2 1 1 E jumpers E jumpers 57 PIN Jumper pins BLOCK Jumper blocks 10 LM-323 Regulator 1 VRl 1 TO-3 Heatsink for VR1 TO-3 Heatsink top 1 for VR1 1N4742 Zener diode (12 volts)XTL-1616.00 Mhz crystal 2 CR1,CR2 1 Y1 1 XTL-5.0688 5.0688 Mhz crystal ¥2 Hardware ----2 6-32 x 3/8 screw 2 #6 washer 2 #6 nuts 2 2-56 x 1/2 screw 2 #2 washer 2 #2 nuts 40 pin socket 28 pin socket 1 2 1 24 pin socket 20 pin socket 18 pin socket 16 pin socket 14 pin socket 10 1

11 24

## Parts List

IC's

| 2<br>1<br>3<br>1<br>2<br>1<br>1<br>4<br>3<br>1<br>1<br>1<br>1<br>2<br>9 | 7400/74LS00<br>7402/74LS02<br>7404/74LS04<br>74S04<br>7406<br>7408/74LS08<br>7410/74LS10<br>74LS14<br>7432/74LS32<br>7474/74LS74<br>82S123/6331<br>74138/74LS138<br>74148/74LS148<br>74161/74LS161<br>74174/74LS174<br>74S189 | 8 line to 3 line encoder<br>Binary counter | U29,U33<br>U31<br>U2,U8,U12<br>U36<br>U6,U10<br>U13,U34<br>U19<br>U9<br>U5,U25,U30,U39<br>U14,U20,U28<br>U18<br>U4<br>U26<br>U21<br>U27<br>U41,U42 |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 9<br>1<br>2<br>1<br>2<br>1<br>1<br>1<br>1                               | 74LS260<br>8T98/74368<br>MC1488/SN75188<br>MC1489/SN75189<br>8304/8286<br>8251AC<br>8253C-5<br>SMC5016/BR1941-<br>280A                                                                                                        |                                            | U17,U43,U44,U4<br>U46,U47,U49,U5<br>U52<br>U1,U3<br>U15<br>U22,U24<br>U11,U23<br>U32<br>U37,U38<br>U54<br>U53<br>U16                               |

Tarbell 2-80 CPU Board Full 6 Month Warranty

1. Any faulty component part purchased from Tarbell Electronics, which is returned within 6 months after the date of purchase will be replaced at no charge. Components returned under this part of the warranty should be with a letter explaining what is wrong with the part.

2. Any factory-assembled 2-80 CPU interface, which does not work correctly, and is returned within 6 months after the date of purchase, will be restored to proper operating condition or replaced without charge.

3. Any Z-80 CPU interface kit, which in the opinion of the manufacturer has been assembled with reasonable care, and is returned for repair within 6 months after the date of purchase, will be repaired for a charge commensurate with the work required, (parts will be free) but in no case will exceed \$100 without notification of the owner.

4. Any 2-80 CPU interface not covered by the above condition will be subject to a charge commensurate with the work and parts required, but in no case wil exceed \$100 without notification of the owner.

5. Parts can be returned directly to the address below for replacement. Complete Z-80 CPU interfaces should be returned to the place of purchase. If this is not possible, or if it is very inconvenient, it may be returned to the address below, with proof of purchase.

6. Tarbell Electronics assumes no responsibility for consequential damages to other connected equipment, or for time lost, or programs or data lost, because of CPU malfunction or incorrect documentation.

7. If you are disatisfied with the operation of a factory-assembled Tarbell 2-80 CPU Interface Board for any reason, your money will be cheerfully refunded, provided the unit is returned within the six month warranty period.

8. Tarbell Electronics does not warrant that the CPU interface will work with all "S-100" computer systems. Call the factory or ask your local dealer about any possible conflicts in your system.

9. This warranty does not cover parts, or interfaces built from parts, which are not traceable to Tarbell Electronics.

10. A CPU which is assembled from a kit by a Tarbell dealer has only the parts covered by this warranty, not the labor. All CPU's which were sold as kits, will have a "K" marked on the solder side. The dealer may provide his own warranty in this case.

Defective parts or CPU's covered under this warranty should be sent WITH PROOF OF PURCHASE (like a receipt) to:

> Tarbell Electronics 950 Dovlen Place, Suite B Carson, California 90746

IEEE Specification, IEEE Task 696.1/D2 The following is a list of the IEEE pin functions, signals, type of signal, active level, and a description of the signal. The following conventions will be used: 1.  $\setminus$  = inverted signal or the NOT function. 2. M = master. 3. B = bus. 4. S = slave. 5. O.C. = open collector. 6. H = high or logic level 1 7. L = low or logic level 0Pin Signal Type Active Level Description \_\_\_\_ \_\_\_\_\_ 1 +8 volts В Instantaneous min greater than 7 volts, instantaneous max less than 25 volts, average max less than 11 volts. 2 +16 volts В Instantaneous min greater than 14.5 volts, instantaneous max less than 35 volts, average max less than 21.5 volts. 3 XRDY S Н One of two ready inputs to the current bus master. The bus is ready when both inputs are true (H). see pin 72. 4 /0IV L O.C. Vectored interrupt line 0. S 5 VII\ S L 0.C. Vectored interrupt line 1. 6 VI2∖ S L 0.C. Vectored interrupt line 2. 7 VI3\ S L 0.C. Vectored interrupt line 3. 8 VI4\ S Ł 0.C. Vectored interrupt line 4. 9 VI5\ Vectored interrupt line 5. S L 0.C. 10 VI6\ S 0.C. Ľ Vectored interrupt line 6. 11 VI7\ S L 0.C. Vectored interrupt line 7. 12 NMIN S Ľ 0.C. Non-maskable interrupt line. 13 PWRFAIL В L Power fail bus signal. 14 DMA3\ М L 0.C. Temporary master priority bit 3. 15 A18 M Ħ Extended address bit 18.

| 16 | A16            | М            | H            |      | Extended address bit 16.                                                                          |

|----|----------------|--------------|--------------|------|---------------------------------------------------------------------------------------------------|

| 17 | A1 <b>7</b>    | 14           | Ħ            |      | extended address bit 17.                                                                          |

| 18 | SDSB           | м            | L            | 0.C. | Disable signal for 8 status lines.                                                                |

| 19 | CDSB           | 11           | L            | o.c. | Disable signal for 8 control lines.                                                               |

| 20 | GND            | В            |              |      | Common with pin 100                                                                               |

| 21 | NDEF           |              |              |      | Not to be defined. Manufacturer must specify any use in detail.                                   |

| 22 | AD <b>SB</b> \ | 6            | L            | 0.C. | Disable signal for 16 address lines.                                                              |

| 23 | DODSB\         | M            | $\mathbf{L}$ | o.c. | Disable for 8 data out lines.                                                                     |

| 24 | φ              | в            | H            |      | Master timing signal for bus.                                                                     |

| 25 | pSTVAL\        | 11           | г            |      | Status valid signal.                                                                              |

| 26 | pHLDA          | М            | H            |      | Control signal used in conjunction<br>with HOLD\ to coordinate bus/master<br>transfer operations. |

| 27 | RFU            |              |              |      | Reserved for future use.                                                                          |

| 28 | RFU            |              |              |      | Reserved for future use.                                                                          |

| 29 | A5             | М            | н            |      | Address bit 5.                                                                                    |

| 30 | አ4             | М            | Ħ            |      | Address bit 4.                                                                                    |

| 31 | 23             | M            | H            |      | Address bit 3.                                                                                    |

| 32 | 415            | 11           | Ħ            |      | Address bit 15.                                                                                   |

| 33 | 012            | 11           | H            |      | Address bit 12.                                                                                   |

| 34 | A9             | 11           | Ħ            |      | Address bit 9.                                                                                    |

| 35 | DO1/DATA1      | M/MS         | Н            |      | Data out bit 1, bidirectional bit 1.                                                              |

| 36 | DOO/DATAO      | M/MS         | H            |      | Data out bit 0,bidirectional bit 0.                                                               |

| 37 | Δ10            | 14           | Н            |      | Address bit 10.                                                                                   |

| 38 | DO4/DATA4      | M/ <b>MS</b> | H            |      | Data out bit 4,bidirectional bit 4.                                                               |

| 39 | DO5/DATA5      | M/MS         | Ħ            |      | Data out bit 5, bidirectional bit 5.                                                              |

| 40 | DO6/DATA6      | M/MS         | H            |      | Data out bit 6, bidirectional bit 6.                                                              |

| 41 | DI2/DATA10     | S/MS         | н            |      | Data in bit 2, bidirectional bit 10.                                                              |

| 42 | DI3/DATA11     | S/MS | H |      | Data in bit 3, bidirectional bit 11.                                                                                                                         |

|----|----------------|------|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43 | DI7/DATA15     | s/ms | H |      | Data in bit 7,bidirectional bit 15.                                                                                                                          |

| 44 | sMl            | М    | н |      | Status signal indicating current cycle is op-code fetch.                                                                                                     |

| 45 | SOUT           | М    | Н |      | Status signal indicating data<br>transfer bus cycle to output device.                                                                                        |

| 46 | sINP           | 14   | H |      | Status signal indicating data<br>transfer bus cycle from input device.                                                                                       |

| 47 | SMEMR          | М    | H |      | Status signal identifying bus cycles<br>which transfer data from memory to a<br>bus master, which are not interrupt<br>acknowledge instruction fetch cycles. |

| 48 | SHLTA          | м    | H |      | Status signal indicating a HALT instruction has been executed.                                                                                               |

| 49 | CLOCK          | В    |   |      | 2 MHz (0.5%) 40-60% duty cycle.<br>Not required to be synchronous with<br>any other bus signal.                                                              |

| 50 | GND            | В    |   |      | Common with pin 100.                                                                                                                                         |

| 51 | +8 volts       | В    |   |      | Common with pin 1.                                                                                                                                           |

| 52 | -l6 volts      | В    |   |      | Instantaneous max less than -14.5<br>volts,instantaneous min greater than<br>-35 volts, average min greater than<br>-21.5 volts.                             |

| 53 | GND            | B    |   |      | Common with pin 100.                                                                                                                                         |

| 54 | SUAVE CLRV     | В    | L | 0.C. | Reset signal to reset bus slaves. Must<br>be active with POC\ and may also be<br>generated by external means.                                                |

| 55 | 201A0\         | 14   | L | o.c. | Temporary master priority bit 0.                                                                                                                             |

| 56 | / <b>IA</b> MC | 11   | L | 0.C. | Temporary master priority bit 1.                                                                                                                             |

| 57 | DMA2\          | М    | L | 0.C. | Temporary master priority bit 2.                                                                                                                             |

| 58 | sXTRQ\         | М    | L |      | Status signal which requests 16-bit<br>slaves to assert SIXTN\.                                                                                              |

| 59 | A1 9           | М    | H |      | Extended address bit 19.                                                                                                                                     |

| 60 | SIXTN\         | S    | L | 0.C. | Signal generated by 16-bit slaves in response to the 16-bit request signal                                                                                   |

3

sXTRQ\.

| 61                               | ۸20                                               | М                     | Ħ                     |              | Extended address bit 20.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------|---------------------------------------------------|-----------------------|-----------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 62                               | A21                                               | М                     | H                     |              | Extended address bit 21.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 63                               | A22                                               | М                     | H                     |              | Extended address bit 22.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 64                               | ۸23                                               | М                     | н                     |              | Extended address bit 23.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 65                               | NDEF                                              |                       |                       |              | Not to be defined signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6 <b>6</b>                       | NDEF                                              |                       |                       |              | Not to be defined signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 67                               | PHANTOM\                                          | M/S                   | L                     | 0.C.         | Bus signal which disables normal slaw<br>devices and enables phantom slaves.<br>Primarily used for bootstrapping<br>systems without hardware front panels                                                                                                                                                                                                                                                                                                                        |

| 68                               | MW RT                                             | В                     | H                     |              | Gating of pWR\ - sOUT. Signal must fo<br>pWR\ by no more than 30 ns.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 69                               | RFU                                               |                       |                       |              | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 70                               | GND                                               | В                     |                       |              | Common with pin 100.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 71                               | RFU                                               |                       |                       |              | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                  |                                                   |                       |                       |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 72                               | RDY                                               | S                     | Н                     | 0.C.         | See comments for pin 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 72<br>73                         | RDY<br>INT\                                       | S<br>S                | H<br>L                | o.c.<br>o.c. | See comments for pin 3.<br>Primary interrupt request bus signal.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                  |                                                   |                       |                       |              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 73                               | INT\                                              | S                     | L                     | 0.C.         | Primary interrupt request bus signal.<br>Control signal used in conjuction with<br>pHLDA to coorodinate bus master trans                                                                                                                                                                                                                                                                                                                                                         |

| 73<br>74                         | INT\<br>HOLD\                                     | S<br>М                | L<br>L                | o.c.<br>o.c. | Primary interrupt request bus signal.<br>Control signal used in conjuction with<br>pHLDA to coorodinate bus master trans<br>Signal used to reset bus master device<br>This signal must be active with POC\                                                                                                                                                                                                                                                                       |

| 73<br>74<br>75                   | INT\<br>HOLD\<br>RESET\                           | <b>S</b><br>И<br>В    | L<br>L<br>L           | o.c.<br>o.c. | Primary interrupt request bus signal.<br>Control signal used in conjuction with<br>pHLDA to coorodinate bus master trans<br>Signal used to reset bus master device<br>This signal must be active with POC\<br>and may be generated by external means                                                                                                                                                                                                                             |

| 73<br>74<br>75<br>76             | INT\<br>HOLD\<br>RESET\<br>PSYNC                  | S<br>М<br>В           | L<br>L<br>L<br>H      | o.c.<br>o.c. | Primary interrupt request bus signal.<br>Control signal used in conjuction with<br>pHLDA to coorodinate bus master trans<br>Signal used to reset bus master device<br>This signal must be active with POC\<br>and may be generated by external means<br>Control signal identifying BS1.<br>Control signal signifying the presence                                                                                                                                                |

| 73<br>74<br>75<br>76<br>77       | INT\<br>HOLD\<br>RESET\<br>PSYNC<br>PNR\          | S<br>M<br>B<br>П<br>М | L<br>L<br>L<br>H      | o.c.<br>o.c. | Primary interrupt request bus signal.<br>Control signal used in conjuction with<br>pHLDA to coorodinate bus master trans<br>Signal used to reset bus master device<br>This signal must be active with POC\<br>and may be generated by external means<br>Control signal identifying BS1.<br>Control signal signifying the presence<br>of valid data on DO bus or data bus.<br>Control signal that request data on th<br>DI bus or data bus from the currently                     |

| 73<br>74<br>75<br>76<br>77<br>78 | INT\<br>HOLD\<br>RESET\<br>PSYNC<br>PMR\<br>PDBIM | S<br>M<br>B<br>M<br>М | L<br>L<br>H<br>L<br>H | o.c.<br>o.c. | Primary interrupt request bus signal.<br>Control signal used in conjuction with<br>pHLDA to coorodinate bus master trans<br>Signal used to reset bus master device<br>This signal must be active with POC\<br>and may be generated by external means<br>Control signal identifying BS1.<br>Control signal signifying the presence<br>of valid data on DO bus or data bus.<br>Control signal that request data on th<br>DI bus or data bus from the currently<br>addressed slave. |

4

| 82  | Аб         | м    | B      | Address bit 6.                                                                                                                |

|-----|------------|------|--------|-------------------------------------------------------------------------------------------------------------------------------|

| 83  | A7         | М    | н      | Address bit 7.                                                                                                                |

| 84  | А8         | М    | H      | Address bit 8.                                                                                                                |

| 85  | A13        | M    | H      | Address bit 13.                                                                                                               |

| 86  | A14        | М    | н      | Address bit 14.                                                                                                               |

| 87  | A11        | М    | н      | Address bit 11.                                                                                                               |

| 88  | DO2/DATA2  | M/MS | н      | Data out bit 2, bidirectional bit 2.                                                                                          |

| 89  | DO3/DATA3  | M/MS | н      | Data out bit 3, bidirectional bit 3.                                                                                          |

| 90  | DO7/DATA7  | M/MS | н      | Data out bit 7, bidirectional bit 7.                                                                                          |

| 91  | DI4/DATA12 | S/MS | H      | Data in bit 4, bidirectional bit 12.                                                                                          |

| 92  | DI5/DATA13 | S/MS | н      | Data in bit 5, bidirectional bit 13.                                                                                          |

| 93  | DI6/DATA14 | s/ms | н      | Data in bit 6, bidirectional bit 13.                                                                                          |

| 94  | DI1/DATA9  | s/ms | н      | Data in bit 1, bidirectional bit 9.                                                                                           |

| 95  | DIO/DATA8  | s/ms | н      | Data in bit 0, bidirectional bit 8.                                                                                           |

| 96  | SINTA      | 11   | Н      | Status signal identifying the bus input<br>cycles that may follow an accepted<br>interrupt request presented on INT\.         |

| 97  | s₩O∖       | М    | L      | Status signal identifying a bus cycle<br>which transfers data from a bus master<br>to a slave.                                |

| 98  | BRROPN     | S    | L 0.C. | Bus status signal signifying an error condition during the present bus cycle.                                                 |

| 99  | 90C\       | В    | L      | Power-on clear signal for all bus<br>devices. During active condition, this<br>signal must stay low for at least<br>10 msecs. |

| 100 | GND        | В    |        | System ground bus.                                                                                                            |

|     |            |      |        |                                                                                                                               |