# 4K ROM Read-Only Memory Plug-In Printed Circuit

Assembly Instructions

April 1977

# TABLE OF CONTENTS

1

| General Information    |       |       | 1  |

|------------------------|-------|-------|----|

| 4K ROM Printed Circuit | Assem | bly   | 3  |

| Assembly of Components | in Ba | g #1  | 5  |

| Assembly of Components | in Ba | ig #2 | 7  |

| Assembly of Components | in Ba | g #3  | 9  |

| Assembly of Components | in Ba | .g #4 | 11 |

| Warranty               |       |       | 12 |

| Installation           |       |       | 13 |

| Theory of Operation    |       |       | 14 |

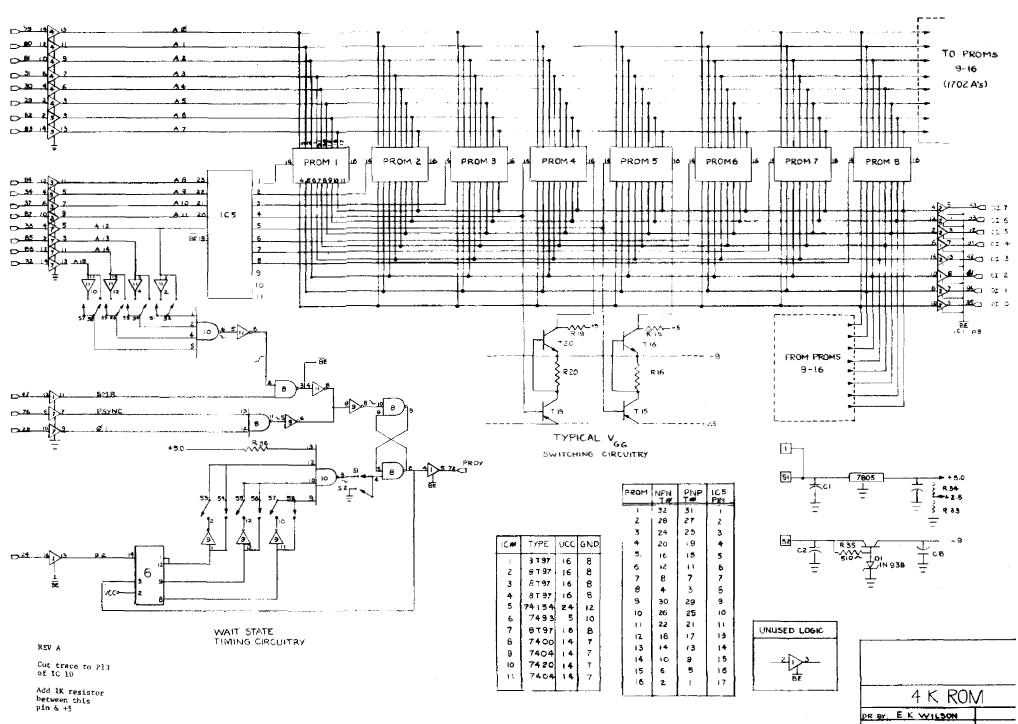

| Schematic Diagram      |       |       |    |

4K ROM

#### GENERAL INFORMATION

The Seals 4K ROM Printed Circuit is designed to accommodate the standard 24-pin integrated circuit ROM or PROM elements that are available from a variety of sources. The data are "burned" into each integrated circuit, with 8 bits at each of 256 addresses. The purpose of this plug-in printed circuit is to permit up to 16 such elements to be assembled onto the board and to allow random access to each stored data word by using its address and a read cycle. In a complex address, the low-order 8 bits identify a data word in one of the integrated circuits; the next higher 4 bits identify one of the 16 IC packages on a board; and the next 4 higher bits can be used to select one board out of a possible 16 boards in the computer. So the system can operate with as few as one 256-address ROM element or as many as 256 ROM elements. System expansion is simple.

There are several different types of components that will be assembled onto the printed circuit. All are mounted on the same side of the board, where the location guide is screened onto the board surface. Most are held in place by having their contact leads soldered onto the back side of the board, so the soldering is very important for two reasons; one reason is to hold the component in position on the board and the other is to complete the electrical circuit necessary for its operation. Always use rosin-core solder only (never use acid-core). Use as little solder and heat as necessary at each connection so that you get a smooth-shiny connection that does not spread out and short it to any other adjacent contact point. Excess heat can damage some of the electronic components, so a small low-wattage soldering tool must be used, rather than a large and cumbersome iron that would overheat and damage the components and the board circuits. The board surface also includes a solder mask for extra assurance, but careful assembly is recommended rather than dependence on the solder mask.

The resistors, diode, and capacitors are all components that are held in position by their two contact leads, soldered to the places where they connect to the foil pattern on the back of the board. Before each of these components is soldered in place, it should be held just off the front surface of the board (about 1/32" should be enough clearance for most, although disk capacitors may require a little more). The transistors are also lead-mounted by spreading their 3 leads to match the configuration on the board and holding them about 3/32" above the board surface while soldering the leads. Each transistor has a flat surface, which will be at the top when properly assembled; with this orientation, the emitter is at the right, the base at the center, and the collector at the left. After soldering the component in place, test its security by pressing gently against the mounting to be sure it is secure before proceeding to the next component.

The multi-pin integrated circuit packages have been protected against overheating by adding them into the plug-in sockets after all other parts, including the sockets, have been soldered into position on the board. No further soldering should be required after the integrated circuit packages have been installed. This construction plan includes installation of sockets for all 16 of the possible ROM or PROM units that can be used on the completed board.

#### 4K ROM PRINTED CIRCUIT ASSEMBLY

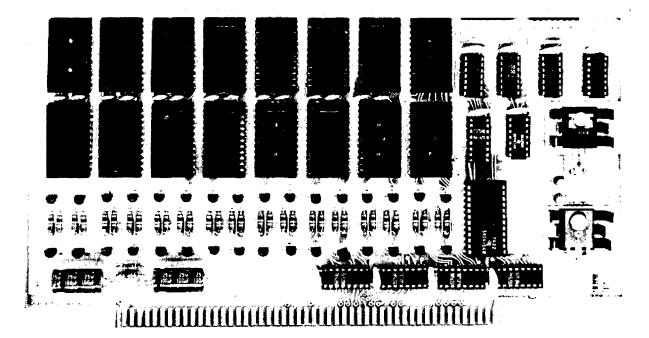

Figure 1 is a picture of a completed board that can be used for reference during assembly. The component designation is screened on the printed circuit to identify where each of the parts will be located during assembly. These reference designations are also shown in the schematic for the 4K ROM, and their functions can be identified with the aid of the theory of operation discussion.

All of the components, including the printed circuit board, are of the highest quality obtainable. Careful assembly and handling will maintain this quality as you complete the following steps and create the operating circuit that you will appreciate using for a long time to come. Although some of the steps may seem tedious, the extra care and patient procedure that you use to complete each step precisely as described will pay you dividends of long-term useful operation afterward. But a careless mistake could destroy the quality and usefullness that can be yours otherwise.

The components have been furnished in four numbered bags. The components in bag #1 should all be assembled to the board before those in bag #2, etc. However, it is a good idea to open each bag and check to see that it includes all of the components that are supposed to be included in the shipment. After checking to see that all components have been included, return them carefully to the bag to prevent loss, damage, or mixup with those that are in the other bags.

| <u>Bag 1</u> contains: 2 | heat sinks.         | Each includes a mounting screw and<br>nut for assembly, together with the<br>power supply element. |

|--------------------------|---------------------|----------------------------------------------------------------------------------------------------|

| . 1                      | IC package.         | Marked 7805, with a mounting tab and 3 contact leads.                                              |

| ~1                       | resistor.           | 510 $\Omega$ 1/8W, color-coded yellow, brown, brown, and a 4th band that indicates tolerance.      |

| 5.1 <b>1</b>             | diode.              | Type 1N4740, 9.6V Zener, with a band that indicates the cathode end.                               |

| • 1                      | transistor.         | Type 2N2955 or MJE2955.                                                                            |

| 2                        | capacitors.         | 6.8 $\mu$ F 35V, pear-shaped, marked + on                                                          |

|                          |                     | the positive side.                                                                                 |

| 2                        | capacitors.         | 100 $\mu$ F electrolytic, marked + on the                                                          |

|                          |                     | positive end of the case.                                                                          |

| <u>Bag 2</u> contains: 2 | resistors.          | 1K 1/8W, color-coded brown, black, red,                                                            |

| 32                       | resistors.          | and a 4th band that indicates tolerance.<br>10K 1/8W, color-coded brown, black,                    |

| 10                       | · · · · • • · · · · | orange, and a tolerance band.                                                                      |

|                          | •                   | 0.1 µF disc type.                                                                                  |

|                          | capacitors.         | 0.01 µF disc type.                                                                                 |

|                          |                     | Type 6520 NPN, with 3 leads.                                                                       |

|                          | IC sockets.         | 16-pin sockets for integrated circuits.                                                            |

| Bag 3 contains: 2        |                     | Each includes 8 miniature toggle switches.                                                         |

|                          |                     | Type 6522 PNP, with 3 leads.                                                                       |

|                          |                     | 24-pin sockets for integrated circuits.                                                            |

|                          |                     | 14-pin sockets for integrated circuits.                                                            |

| <u>Bag 4</u> contains:11 | ic packages.        | Each marked with its type designation;                                                             |

|                          | ***                 | 5 type <del>770</del> 4, 1 type 7400N, 2 type 7404N,                                               |

|                          |                     | 1 type 7420N, 1 type 7493AN, 1 type 74154.                                                         |

|                          |                     |                                                                                                    |

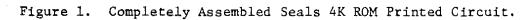

Figure 2. Location of Components Included in Bag #1.

$(\mathcal{X})$

$(\cdot)$

(...)

()

#### ASSEMBLY OF COMPONENTS IN BAG #1

Heat Sinks and Power Supply Components Select one heat sink, the type 7805 integrated circuit, one screw, and a nut for assembly to the board at the area marked 7805. Use a needle-nose pliers to bend each of the 3 IC leads at right angles to match the hole spacing on the board; the tab on the side opposite the 3 leads will be attached to the heat sink and board with the screw (through the back) and the nut (on the top). Solder all three leads to the foil pattern on the back of the board. Then clip off any excess lead lengths. Select the other heat sink, the type 2N2955 power transistor, and the other screw and nut. Use the same procedure to mount this transistor and heat sink at the location marked T33; this orientation places the emitter at the left, the collector at the center, and the base at the right as shown in Fig. 2. <u>Resistor</u> Obtain the 510 $\Omega$  resistor from the bag. Use a needle-nose pliers to bend the leads at right angles to match the hole spacing on the board at the R35 location. Insert the leads through the holes for R35 and hold it while you turn the board over and bend the leads out at a slight angle to hold the resistor on the board. Solder each lead on the back of the board and clip off any excess lead length. Test the resistor to see that it is secure mechanically and electrically.

<u>Diode</u> Obtain the 1N4740 diode from the bag. Use a needle-nose pliers to bend the leads at right angles to match the hole spacing on the board at location DL. Orient the diode with its banded end (cathode) at the bottom and insert its leads through the holes at DL. Hold the diode on the board while you turn the board over and bend the leads out at a slight angle. Solder both leads to the board terminals and clip off any excess lead lengths. Check for mechanical and electrical security.

NOTE: Be sure the cathode-end of the diode points DOWN on the board; the wrong orientation can result in permanent damage.

6.8 µF Capacitors Select the two 6.8 µF capacitors from the bag. Note that they include a marking that identifies the + lead, which must be matched with the + mark on the board. Place one capacitor at the C8 location on the board, with the + lead at the left. Insert both leads through the board and solder them on the back of the board. Clip off any excess lead lengths. Ensure that the capacitor is secure. Then place the other capacitor at the C9 location on the board, with its + lead at the right. Insert both leads through the board, solder them, and clip off any excess lengths. Ensure that this capacitor is secure. 100  $\mu$ F Capacitors Obtain the two 100  $\mu$ F capacitors from the bag. Note that they are marked to show which lead is the negative polarity. The capacitors will be installed at the C1 and C2 locations on the board, and both are oriented with the - lead toward the right. Use a needle-nose pliers to bend the leads at right angles to fit the hole spacing on the board at the Cl and C2 locations. Using the proper orientation, insert the leads in the holes through the board. Hold each capacitor in position while you bend its leads slightly outward on the back of the board. Then solder each lead and clip off any excess lead lengths. Check each for mechanical and electrical security.

Test the assembled power supply circuits by inserting the printed circuit into the computer and applying power. The voltage across C8 should measure approximately -9 V to ground, and across C9 should measure +5 V to ground.

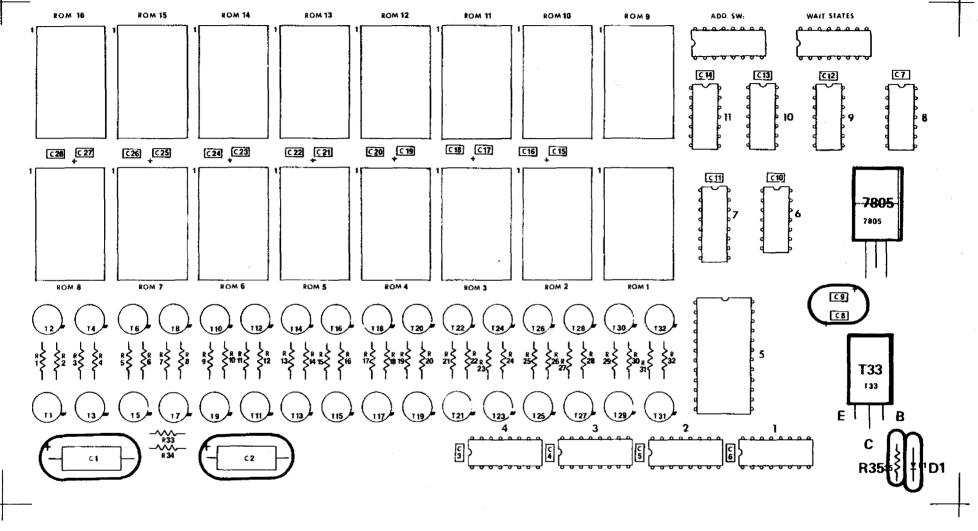

Figure 3. Location of Components Included in Bag #2.

Ś

## ASSEMBLY OF COMPONENTS IN BAG #2

4K ROM

()

()

()

()

()

<u>Resistors</u> Obtain the two 1K resistors from the bag; these are color coded brown, black, red. They will be located at R33 and R34 on the board. Use a needle-nose pliers to bend the leads at right angles to match the hole spacing on the board. Insert each resistor through the correct holes and hold the resistor while you turn the board over and band the leads out at a slight angle. Solder each lead to the back of the board and clip off any excess lead length. Check to be sure the resistor is secure in the board.

<u>Resistors</u> Obtain the remaining 32 resistors from the bag; each has a value of 10K and is color-coded brown, black, orange. They will be located across the row marked as R1 through R32 on the board. Install each in its location, using the same procedure as for the 1K resistors described above.

<u>Capacitors</u> There are two sizes of disc capacitors in this bag. The larger ones are 0.1  $\mu$ F and the smaller are 0.01  $\mu$ F. Select the 10 larger capacitors (0.1  $\mu$ F) for installation at the locations marked C3 through C7 and C10 through C14 on the board. Disc capacitors are not subject to orientation and can be installed by pushing the two leads through the pair of holes provided at each location on the board. Then bend the leads slightly outward at the back of the board, solder each lead to its contact, and clip off any excess lead lengths. Then select the remaining 14 smaller capacitors (0.01  $\mu$ F for installation at the locations marked C15 through C28 on the board. Install one at each of these locations, using the same procedure as described for the larger capacitors.

<u>Transistors</u> Select the 16 type 6520 NPN transistors from the bag. Note that each transistor body is flat on one side; this side will be oriented toward the top of the board when it is installed. The locations for these transistors are the even-numbered designations T2, T4, . . through T32 in a row across the board. Mount each transistor in its location by spreading its 3 leads to match the hole configuration on the board with the flat side of the transistor toward the top of the board. Press the transistor down to within about 3/16 inch of the top board surface and solder each of the 3 leads on the back of the board. Clip off the excess lead lengths and test the transistor to be sure it is securely mounted.

<u>16-pin Integrated Circuit Sockets</u> The remaining 5 components in bag #2 are 16-pin DIP IC sockets. They will be placed at locations 1 through 4 and 7 on the printed circuit board. For each socket, straighten all 16 of its leads as necessary with a needle-nose pliers and insert the leads through the board at one of the designated locations. There is no orientation to be considered for the socket. If desired, hold the socket in place with a short piece of masking tape while the 16 pins are soldered to their contacts on the back of the board. Be very careful to prevent solder bridges. Remove the masking tape and cut off any excess lead length after each socket has been assembled to the board and its leads have been properly soldered.

Figure 4. Location of Components Included in Bag #3.

()

()

$(\mathcal{S})$

()

()

Switch Assemblies Each of the two switch assemblies includes 8 miniature SPST switches numbered 1 through 8. Each switch is on when up or off when down. Obtain the assemblies from the bag and check the 16 leads (8 across the top and 8 across the bottom). Straighten these leads as necessary, using a needle-nose pliers, and install one at the ADD. SW. location and the other at the WAIT STATES location. Orient each so that the small switch numbers are across the top. Hold the assembly in position with a short length of masking tape. Turn the board over and solder each lead to its contact on the back of the board. Use as little heat and solder as possible at each contact, being sure the connection is secure and there are no solder bridges between adjacent contacts. Remove the masking tape and cut off any excess lead lengths. Instructions for selecting ON or OFF for each of the 16 individual switches is included in the operation section of this manual.

<u>Transistors</u> Select the 16 type 6522 PNP transistors from the bag. Note that each transistor is flat on one side; this side will be oriented toward the top of the board when it is installed. The locations for these transistors are the odd-numbered designations T1, T3, . . . through T31 in a row across the board. Mount each transistor in its location by spreading its 3 leads to match the hole configuration on the board with the flat side of the transistor toward the top of the board. Press the transistor down to within about 3/16 inch of the top board surface and solder each of the 3 leads on the back of the board. Clip off excess lead lengths and check for secure mounting for each of the 16 transistors.

24-pin Integrated Circuit Sockets Select the 17 large IC sockets from the bag. One of these will be located at the IC5 location near the power portion at the right side of the board and the remaining 16 are for locations ROM 1 through ROM 16. For each socket, straighten all 24 of its leads as necessary with a needle-nose pliers and insert the leads through the board at one of the designated locations. There is no orientation to be considered for the socket. If desired, hold the socket in place with a short piece of masking tape while the 24 pins are soldered to their contacts on the back of the board. Be very careful to prevent solder bridges. Remove the masking tape and cut off any excess lead lengths after each socket has been assembled to the board and its leads have been properly soldered.

<u>14-pin Integrated Circuit Sockets</u> Select the remaining 5 IC sockets from the bag. Each has 14 pins. They will be installed at locations 6 and 8 through 11 in the upper right portion of the board. Use the same procedure for each of these sockets as is described above for the 24-pin sockets.

Test the assembled board before transistors are added to the IC sockets to be sure that no solder shorts have been made that will degrade the required power levels. Insert the board into the computer and apply power. Measure -9 V across C8 to ground and +5 across C9 to ground.

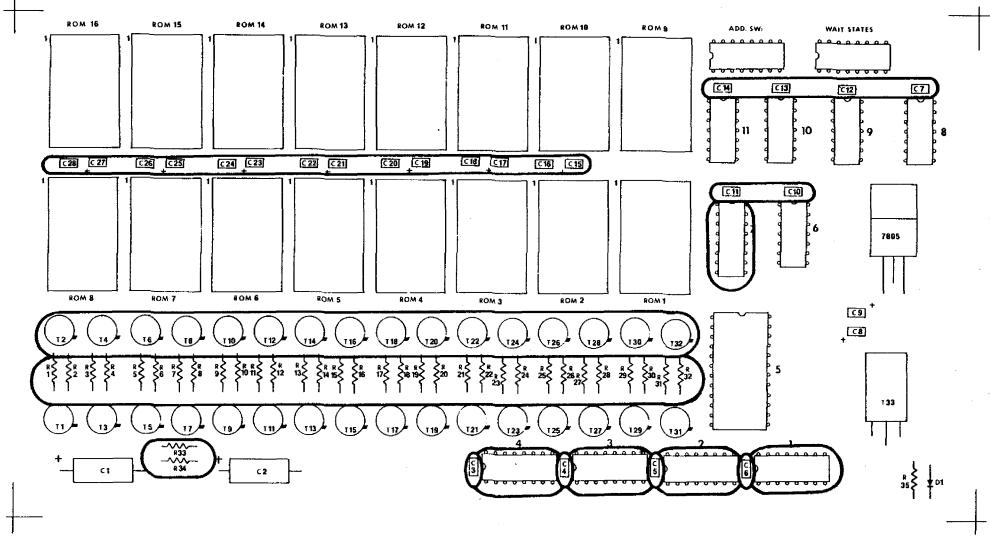

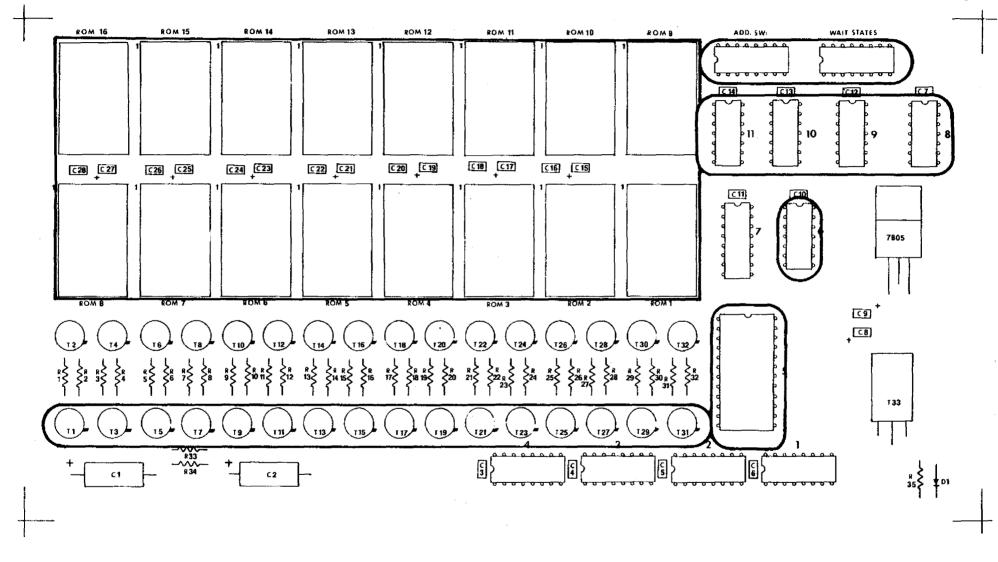

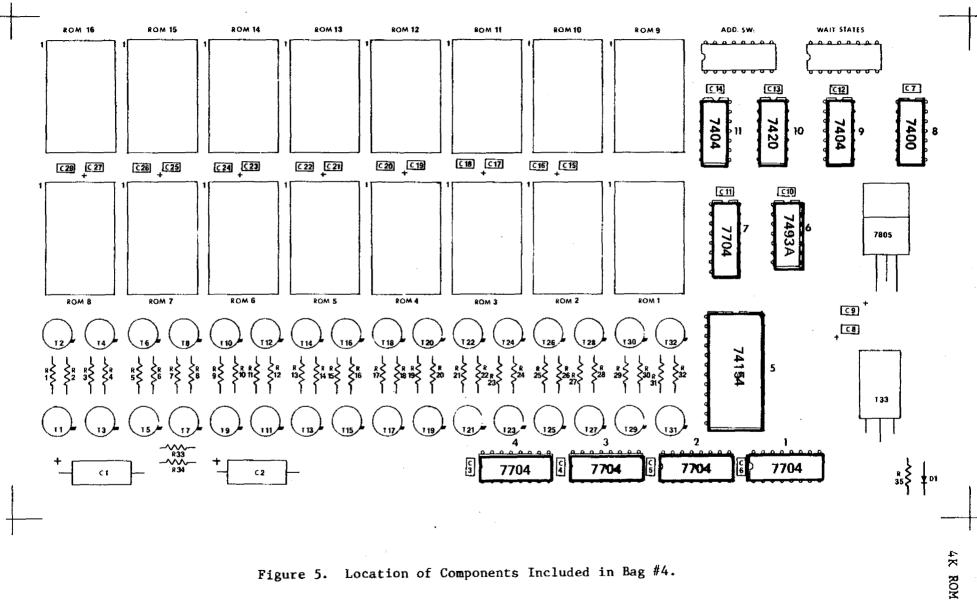

Figure 5. Location of Components Included in Bag #4.

#### ASSEMBLY OF COMPONENTS IN BAG #4

Bag #4 contains the transistors that will be added into the IC sockets on the board to complete the control circuits for the board. The integrated circuits for the ROM 1 through ROM 16 locations are not included and must be obtained separately; the board circuits will accommodate as many of these packages as desired, and they are to be added sequentially, starting at the ROM 1 location.

Select and identify each of the integrated circuits from bag #4. Five will be marked 7704, two will be 7404, and there will be one each of the other types, 7400, 7420, 7493, and 74154. Note that the IC package has a notch or recess at one end; in the board assembly, the notched end will be at the top (for vertical alignment) or at the left (for horizontal alignment). This orientation is important, since each can be plugged into its socket either correctly or reversed.

Using the correct orientation, plug one of the 7704 packages into each location, 1 through 4, at the bottom of the board. Then plug the other 7704 into location 7 (just below C11).

Again, observing the proper orientation, plug one of the 7404 packages into the socket at location 9 (below Cl2) and the other 7404 into location 11 (below Cl4).

Select the 7400 package and plug it into the socket at location 8 (below C7), with the notch at the top.

Select the 7420 package and plug it into the socket at location 10 (below Cl3), with the notch at the top.

Select the 7493A package and plug it into the socket at location 6 (below Cl0), with the notch at the top.

The remaining IC package is a type 74154, with 24 pins. Plug this into the large socket at location 5 with the notch at the top.

This completes the assembly of the 4K ROM board. The IC packages are not soldered into the sockets and may be removed and replaced at any time without damage to the board or its circuits. Be sure to use the proper integrated circuit for each location.

4K ROM

()

C)

()

$(\cdot)$

$(\cdot)$

()

#### WARRANTY

Seals Electronics warrants its equipment for a period of ninety (90) days from the date of shipment to be free from defects in workmanship and materials, provided that the equipment has been used in a proper manner as described in this set of instructions. Seals Electronics cannot be responsible for nor assume any liability for problems that are encountered with methods of installation or with installation results.

After the warranty period, or for any condition that is not covered by the warranty, Seals Electronics will repair or replace, at its option, any part or parts that are found to be defective. This service will be performed within a reasonable time for a service fee of \$20.00 per board plus parts. Shipping costs are the responsibility of the purchaser of the board and/or the repair service.

No other warranty is expressed or implied by Seals Electronics.

#### INSTALLATION

Set the eight switches on each of the two switch assemblies before plugging the board into the computer. In both assemblies, the eight switches are used as four pairs of switches to operate properly and make the selections that are available. The switch assembly at the left, marked ADD. SW., is an address selector that identifies the board as one of a possible 16 boards that can be used in a complex system. The assembly at the right, marked WAIT STATES, selects a preset count level to ensure compatibility with the speed of operation of the memory chips that are used.

For the address switch assembly, use the following logic:

| To identify  |     |     | Se  | et Sw: | <u>itche</u> | es         |     |     |        |          |

|--------------|-----|-----|-----|--------|--------------|------------|-----|-----|--------|----------|

| Board Number | 1   | 2   | 3   | 4      | 5            | 6          | 7   | 8   | Addre  | ss Range |

| 1            | On  | Off | 0n  | Off    | 0n           | Off        | On  | Off | 0 to   | 5 4K     |

| 2            | Off | On  | 0n  | Off    | 0n           | Off        | 0n  | Off | 4K to  | 5 8K     |

| 3            | On  | Off | Off | On     | On           | Off        | On  | Off | 8K to  | 5 12K    |

| 4            | Off | On  | Off | On     | 0n           | Off        | 0n  | Off | 12K to | 5 16K    |

| 5            | On  | Off | 0n  | Off    | Off          | On         | On  | Off | 16K t  | 5 20K    |

| 6            | Off | On  | 0n  | Off    | Off          | 0n         | On  | Off | 20K t  | o 24K    |

| 7            | 0n  | Off | Off | On     | Off          | 0n         | On  | Off | 24K t  | 5 28K    |

| 8            | Off | On  | Off | 0n     | Off          | On         | 0n  | Off | 28K to | 5 32K    |

| . 9          | On  | Off | 0n  | Off    | On           | Off        | Off | On  | 32K t  | 5 36K    |

| 10           | Off | On  | On  | Off    | On           | Off        | Off | On  | 36K t  | 5 40K    |

| 11           | 0n  | Off | Off | On     | On           | Off        | Off | On  | 40K t  | 5 44K    |

| 12           | Off | On  | Off | On     | On           | Off        | Off | On  | 44K t  | 5 48K    |

| 13           | 0n  | Off | On  | Off    | Off          | 0 <b>n</b> | Off | On  | 48K t  | 52K      |

| 14           | Off | On  | On  | Off    | Off          | 0n         | Off | On  | 52K to | 56K      |

| 15           | 0n  | Off | Off | On     | Off          | On         | Off | On  | 56K t  | o 60K    |

| 16           | Off | On  | Off | 0n     | Off          | 0n         | Off | On  | 60K t  | o 64K    |

For the Wait States switch assembly, use the following table:

| Number of         |          |     | S   | et Sw | <u>itch</u> | es  |      |     | Ready Signal         |

|-------------------|----------|-----|-----|-------|-------------|-----|------|-----|----------------------|

| <u>Wait State</u> | <u> </u> | 2   | 3   | 4     | 5           | 6   | 7    | 8   | <u>Duration (ns)</u> |

| 0                 | Off      | 0n  | 0n  | Off   | On          | Off | On   | Off | 0                    |

| 1                 | 0n       | Off | Off | On    | Оп          | Off | On   | Off | 500                  |

| 2                 | 0n       | Off | 0n  | Off   | Off         | On  | On j | Off | 1000                 |

| 3                 | On       | Off | Off | On    | Off         | On  | On   | Off | 1500                 |

| 4                 | On       | Off | 0n  | Off   | Оп          | Off | Off  | 0n  | 2000                 |

| 5                 | On       | Off | Off | On    | On          | Off | Off  | On  | 2500                 |

| 6                 | On       | Off | On  | Off   | Off         | On  | Off  | 0n  | 3000                 |

| 7                 | 0n       | Off | Off | On    | Off         | On  | Off  | On  | 3500                 |

After the switches have been set, plug the board into the computer at any unused connector on the motherboard. All connections are made in parallel between the boards and have been allocated properly to be compatible with the basic standard interconnections furnished between boards.

#### THEORY OF OPERATION

The Seals 4K ROM printed circuit card is a very low power, fast access, programmable read-only memory card that has been designed to accommodate up to 16 of the popular 1702A NMOS integrated circuits, or equal. The non-volatile memory is available in a variety of speeds and quality levels, and this card is compatible with most of them.

There are 16 locations that can be used to plug in the 1702A packages. Each IC provides access by address bits A0 through A7 for the selection of an 8-bit data word that has been stored at the selected address. The selection of one of the 16 possible ROM packages is determined by address bits A8 through A11. An address switch assembly on the board permits it to be identified as one of up to 16 possible boards, using address bits A12 through A15. The following address logic is used:

|    |                    |      |    |           |                                 | <u>A(</u>    | <u>idres</u> | <u>s B</u> ; | <u>its</u> |       |   |   |   |   |   |

|----|--------------------|------|----|-----------|---------------------------------|--------------|--------------|--------------|------------|-------|---|---|---|---|---|

| 15 | 14                 | 13   | 12 | 11        | 10                              | 9            | 8            | 7            | 6          | 5     | 4 | 3 | 2 | 1 | 0 |

| 16 | ect<br>poss<br>ROM | ible |    | 16<br>pac | ntif<br>poss:<br>kage:<br>ected | ible<br>s on | ROM<br>the   | ado          | ires       | ses 3 |   | - | - |   | М |

In addition to logically selecting the particular ROM for each read cycle, this board also includes logic that switches power for the selected ROM during only the interval during which it is addressed. During quiescent operation, all of the ROM packages have a Vgg power input of +5 V, which is a low-power state. When a ROM package is addressed, the Vgg for just that package is switched automatically to -9 V, which is the high-power state.

To operate the card in the computer, furnish the appropriate 16 address bits and a Read command. This enables the board, selects the address, and furnishes the 8-bit word stored at that address through the output common lines. At PSYNC and Øl from the computer, the board will normally generate a Ready output to hold the computer while it reads the output data word. If the computer can accept the data word within 500 nsec, Ready is not required and is not generated; the 4K ROM Wait States switches select the "0" wait state for this timing. To extend the transfer interval, the Wait States switches can be set to select from 1 through 7 additional 500-ns intervals and to generate the Ready output through the selected interval.

Note that the switches are used in pairs. If switch 3 is on, for example, switch 4 must be off. The pairings are switches 1 and 2; 3 and 4; 5 and 6; and 7 and 8. If both switches in a pair are set at On and power is applied to the board, this is a direct short across the +5 V power source and can damage the power supply irreparably. Both switches in the pair can be set at Off without damage.

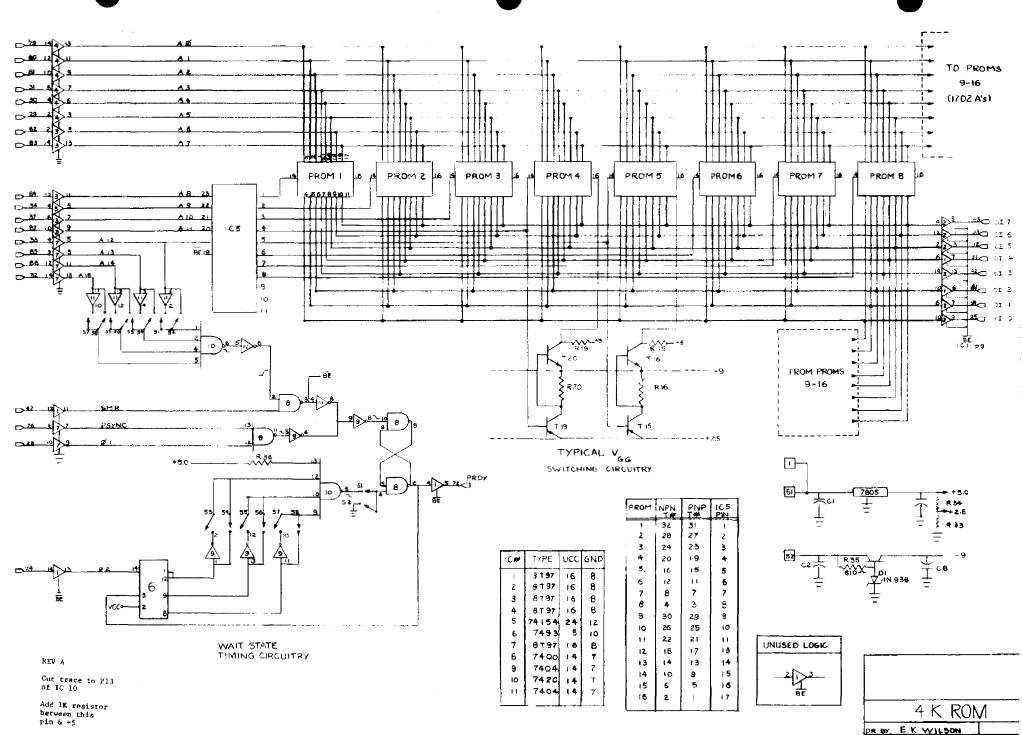

A schematic of the 4K ROM is included at the back of this manual for reference. The circuits are divided generally into three portions. One part is the address circuitry. The second part is the wait circuitry. And the third portion is the low-power switching circuitry.

The address circuitry accepts the 16-bit address from the computer and decodes the complete address. Address bits 12 through 15 are furnished through buffers IC7 and IC11 to the address switches. When the bit configuration matches the switch selection, pin 6 of IC10 goes low to identify that this board has been identified. The low at IC10-6 enables IC5 to accept and decode the input address bits 8 through 11 and to select one of the 16 ROM locations on the board. Address bits 0 through 7 are then decoded in the enabled ROM for the unique address, and the contents at that address are furnished through the eight common data lines to the output, shown at the right on the schematic.

When ICl0-6 goes low, to identify the board as being active, the signal is inverted through ICl1-6. This enables gate IC8-3 to switch its output to low when the computer furnishes the MEMR (Memory Read) signal. The low at IC8-3 is used as a Board Enable (BE) turns on the output gates in ICl and IC2; it also turns on the gates for  $\emptyset$ 2 input signals and for the Ready output signal (if generated). This condition is continued until either the MEMR signal is removed or the address is changed so that it does not select this board.

The wait circuitry is enabled by the low at IC8-3, inverted by IC11-8 which is wired-AND with the output of IC9-6. At  $\emptyset$ 1 and PSYNC from the computer, IC9-6 goes high and this sets flip-flop IC8-8 and IC8-6 unless Wait State switch S2 is set at On (for Wait State O). If Wait State switch S2 is Off and S1 is On, the flip flop is set and generates the Ready output through IC1-4 to the computer. Then counter IC6 counts the  $\emptyset$ 2 inputs from the computer until the combination set with the remaining six Wait State switches is matched by the counter output. When the preset level is reached by the counter, this resets flip-flop IC8-8 and IC8-6 and removes the Ready signal from the 4K ROM board within 500 ns after the MEMR signal is posted, or the Wait States can extend the time for transfer to as much as 3500 ns if this is required for compatibility.

When the board has been selected by address bits 12 through 15 and one of the ROM locations has been selected by address bits 8 through 11, the dc power level to that ROM location is also switched from +5 V (for low power) to -9 V (for full power). The output from the 74154 chip, IC5, is low for the ROM identification that it decodes from the A8 through A11 address lines. The low level turns on the associated PNP transistor, which then turns on its mated NPN transistor to switch the Vgg for the ROM package from +5 V to -9 V. The switching action requires only about 25 ns.

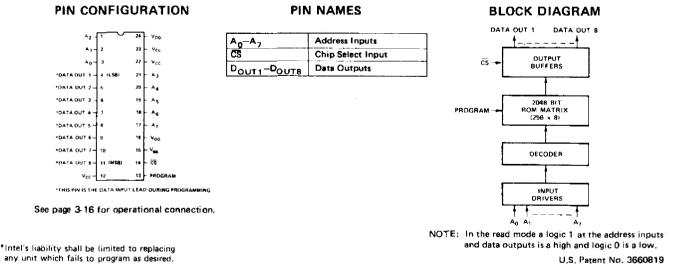

# 2048 BIT ELECTRICALLY PROGRAMMABLE READ ONLY MEMORY

Silicon Gate NOS 1502A/1702A-S614

1602A-S614-ELECTRICALLY PROGRAMMABLE 1702A-S614-ERASABLE & ELECTRICALLY REPROGRAMMABLE

- Fast Programming -- 2 minutes for all 2048 bits

- All 2048 bits guaranteed \* programmable -- 100% factory tested

- Fully Decoded, 256x8 organization

- Static MOS -- No Clocks Required

- Inputs and Outputs DTL and TTL compatible

- Three-state Output --OR-tie Capability

- Simple Memory Expansion --Chip select input lead

- 1.5 µs Access Time

The 1602A-S614 and 1702A-S614 are 256 word by 8 bit electrically programmable ROMs ideally suited for uses where fast turn-around and pattern experimentation are important. The 1602A-S614 and 1702A-S614, undergo complete programming and functional testing on each bit position prior to shipment thus insuring 100% programmability.

The 1602A-S614 and 1702A-S614 use identical chips. The 1702A-S614 is packaged in a 24 pin dual in-line package with a transparent quartz lid. The transparent quartz lid allows the user to expose the chip to ultraviolet light to erase the bit pattern. A new pattern can then be written into the device. This procedure can be repeated as many times as required. The 1602A-S614 is packaged in a 24 pin dual in-line package with a metal lid and is not erasable.

The circuitry of the 1602A-S614 and 1702A-S614 is entirely static; no clocks are required.

A pin-for-pin metal mask programmed ROM, the Intel 1302, is ideal for large volume production runs of systems initially using the S614.

The 1602A-S614 and 1702A-S614 are fabricated with silicon gate technology. This low threshold technology allows the design and production of higher performance MOS circuits and provides a higher functional density on a monolithic chip than conventional MOS technologies.

CAUTION: The 1702A-S614 is a quartz-lid device. The device environment should not exceed that to which a plastic package would be subjected.

ROMs

#### PIN CONNECTIONS

The external lead connections to the 1602A/1702A-S614 differ, depending on whether the device is being programmed<sup>[1]</sup> or used in the read mode. (See following table.)

| PIN         | 12<br>(V <sub>CC</sub> ) | 13<br>(Program) | 14<br>( <del>CS</del> ) | 15<br>(V <sub>BB</sub> ) | 16<br>(V <sub>GG</sub> )                    | 22<br>(V <sub>CC</sub> ) | 23<br>(V <sub>CC</sub> ) |

|-------------|--------------------------|-----------------|-------------------------|--------------------------|---------------------------------------------|--------------------------|--------------------------|

| Read        | V <sub>cc</sub>          | V <sub>cc</sub> | GND                     | V <sub>cc</sub>          | V <sub>GG</sub>                             | V <sub>cc</sub>          | V <sub>cc</sub>          |

| Programming | GND                      | Program Pulse   | GND                     | V <sub>BB</sub>          | Pulsed V <sub>GG</sub> (V <sub>IL4P</sub> ) | GND                      | GND                      |

### **Absolute Maximum Ratings\***

| Ambient Temperature Under Bias                         |

|--------------------------------------------------------|

| Storage Temperature                                    |

| Soldering Temperature of Leads (10 sec)                |

| Power Dissipation                                      |

| Read Operation: Input Voltages and Supply              |

| Voltages with respect to V <sub>CC</sub> +0.5V to -20V |

| Program Operation: Input Voltages and Supply           |

| Voltages with respect to V <sub>CC</sub>               |

#### \*COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

# READ OPERATION D.C. and Operating Characteristics

$T_A = 0^{\circ}C$  to 70°C,  $V_{CC} = +5V \pm 5\%$ ,  $V_{DD} = -9V \pm 5\%$ ,  $V_{GG}^{(2)} = -9V \pm 5\%$ , unless otherwise noted.

| SYMBOL           | TEST                                          | MIN,               | ТҮР.(3 | ) MAX.               | UNIT | CONDITIONS                                                                                       |                        |  |

|------------------|-----------------------------------------------|--------------------|--------|----------------------|------|--------------------------------------------------------------------------------------------------|------------------------|--|

| I <sub>LI</sub>  | Address and Chip Select<br>Input Load Current |                    |        | 1                    | μА   | V <sub>IN</sub> = 0.0V                                                                           |                        |  |

| LO               | Output Leakage Current                        |                    |        | 1                    | μΑ   | $V_{OUT} = 0.0V, \overline{CS} = V_{CC} - 2$                                                     |                        |  |

| ססם <sup>ו</sup> | Power Supply Current                          |                    | 5      | 10                   | mA   | $V_{GG} = V_{CC}, \overline{CS} = V_{CC} - 2$ $I_{OL} = 0.0 \text{mA}, T_A = 25^{\circ}\text{C}$ |                        |  |

| יסס              | Power Supply Current                          |                    | 35     | 50                   | mA   | $\overline{CS} = V_{CC} - 2$<br>$I_{OL} = 0.0 \text{mA}$ , $T_{A} = 25^{\circ}C$                 | ]                      |  |

| I <sub>DD2</sub> | Power Supply Current                          |                    | 32     | 46                   | mA   | CS=0.0<br>I <sub>OL</sub> =0.0mA , T <sub>A</sub> = 25°C                                         | Continuou              |  |

| DD3              | Power Supply Current                          |                    | 38.5   | 60                   | mA   | CS=V <sub>CC</sub> −2<br>I <sub>OL</sub> =0.0mA , T <sub>A</sub> = 0°C                           | Continuou<br>Operation |  |

| I <sub>CF1</sub> | Output Clamp Current                          |                    | 8      | 14                   | mA   | $V_{OUT} = -1.0V, T_A = 0^{\circ}C$                                                              |                        |  |

| I <sub>CF2</sub> | Output Clamp Current                          |                    |        | 13                   | mA   | $V_{OUT} = -1.0V, T_A = 25^{\circ}C$                                                             | J                      |  |

| l <sub>GG</sub>  | Gate Supply Current                           |                    |        | 1                    | μA   |                                                                                                  |                        |  |

| VIL1             | Input Low Voltage for<br>TTL Interface        | -1.0               |        | 0.65                 | V    |                                                                                                  |                        |  |

| VIL2             | Input Low Voltage for<br>MOS Interface        | VDD                |        | V <sub>CC</sub> –6   | V    |                                                                                                  |                        |  |

| VIH              | Address and Chip Select<br>Input High Voltage | V <sub>cc</sub> -2 |        | V <sub>CC</sub> +0.3 | V    |                                                                                                  |                        |  |

| I <sub>OL</sub>  | Output Sink Current                           | 1.6                | 4      |                      | mA   | V <sub>OUT</sub> = 0.45V                                                                         |                        |  |

| Іон              | Output Source Current                         | -2.0               |        |                      | mΑ   | V <sub>OUT</sub> = 0.0V                                                                          |                        |  |

| VOL              | Output Low Voltage                            |                    | 7      | 0.45                 | V    | I <sub>OL</sub> = 1.6mA                                                                          |                        |  |

| V <sub>OH</sub>  | Output High Voltage                           | 3.5                | 4.5    |                      | V    | I <sub>OH</sub> = -100 μA                                                                        |                        |  |

Note 2. VGG may be clocked to reduce power dissipation. In this mode average IDD increases in proportion to VGG duty cycle.

Note 3: Typical values are at nominal voltages and  $T_A = 25^{\circ}C$ .

DR BY. E.K. W1150N CK BY. DATE. 10-25-77

GK BY