#### ELECTRALOGICS 64k CMOS STATIC RAM BOARD

#### COPYRIGHT NOTICE

Copyright (c) 1981 by Electralogics Incorporated. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system or translated into any language or computer language, in any form or by any means.

These include electronic, magnetic, optical, mechanical, chemical, or otherwise, without the specific written approval of

Electralogics Incorporated, 39 Durward Place, Waterloo, Ontario, Canada N2L 4E5

#### DISCLAIMER

Electralogics Incorporated makes no representations or warranties with respect to the contents of this document and specifically disclaims any implied warranties of merchantibility or fitness for any particular purpose. Furthermore, Electralogics Incorporated reserves the right to revise this document and to make changes from time to time of the content hereof without obligation of Electralogics Incorporated to notify any person of such revisions or changes.

# TABLE OF CONTENTS

, i , i

| 1.   | WARRANTY REGISTRATION                                                                                                                                                                                                                                                                             | 1                           |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 2.   | <pre>GENERAL DESCRIPTION.<br/>2.0.1. Processor Compatibility.<br/>2.1. BASIC FEATURES.<br/>2.1.1. Basic Memory Size.<br/>2.1.2. Bank Selection.<br/>2.1.3. Extended Addressing.<br/>2.1.4. Power Requirements.<br/>2.1.5. Block Selection.<br/>2.2. COMPATIBLE MEMORY.</pre>                      | 234444445                   |

| 3.   | OPERATION.<br>3.0.1. Block Enable Switches (SW1 to SW4)<br>3.0.2. Phantom* Enable/Disable (Jumper J1-p)<br>3.0.3. MWRT / PWR* (Jumpers J3-m,-w)<br>3.0.4. Feature Selection (Jumpers J2-b,-x,-a)<br>3.0.5. Permanant Selection Mode<br>3.0.6. Bank Select Mode<br>3.0.7. Extended Addressing Mode | 6<br>7<br>8<br>8<br>9<br>10 |

| 4.   | 4.1. SIGNAL CHARACTERISTICS                                                                                                                                                                                                                                                                       | 12<br>13<br>13<br>13<br>13  |

| 5.   | FRONT PANEL MODIFICATIONS                                                                                                                                                                                                                                                                         | 15                          |

| 6.   | MEMORY TEST                                                                                                                                                                                                                                                                                       | 17                          |

| APPI | ENDICES                                                                                                                                                                                                                                                                                           |                             |

| A.   | PARTS LIST                                                                                                                                                                                                                                                                                        | 18                          |

| в.   | PARTS LAYOUT DIAGRAM                                                                                                                                                                                                                                                                              | 20                          |

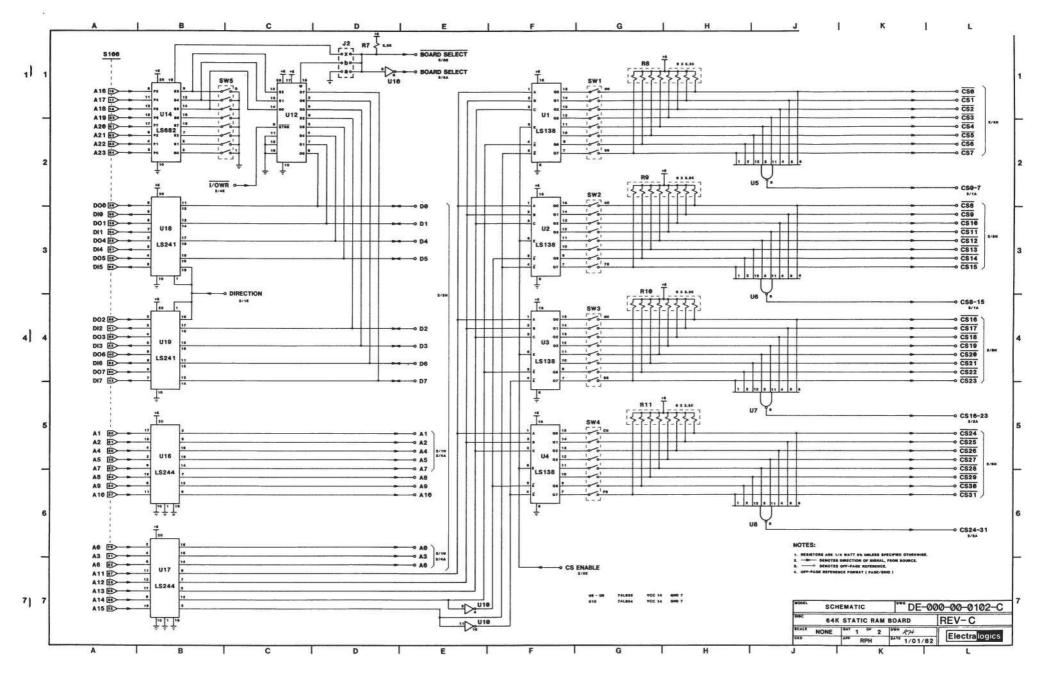

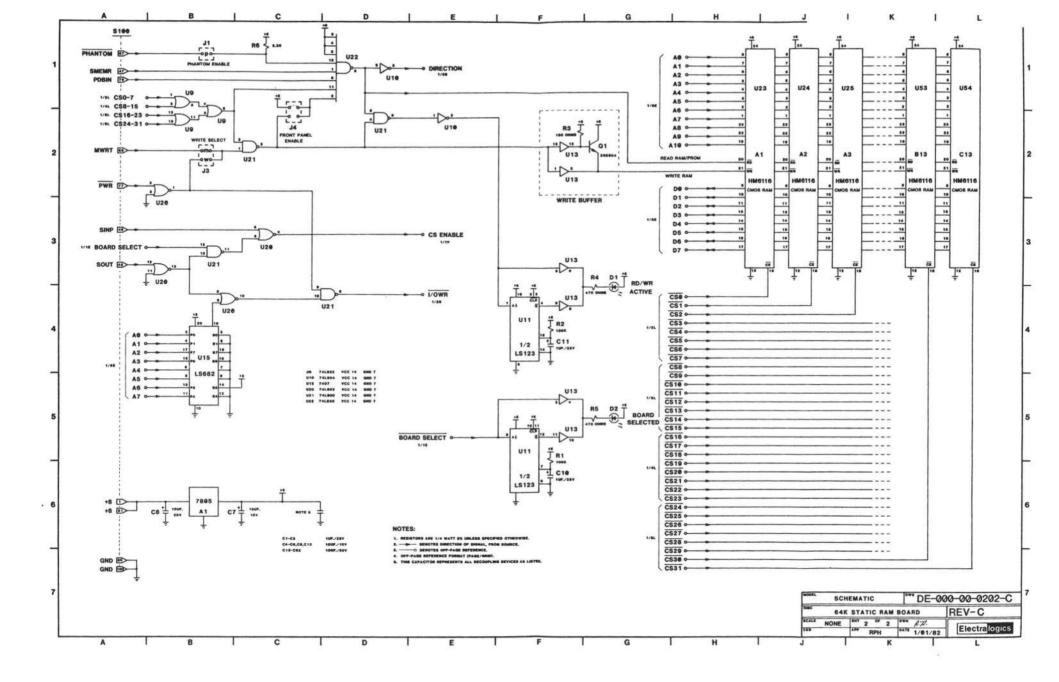

| с.   | SCHEMATIC DIAGRAM                                                                                                                                                                                                                                                                                 | 21                          |

| D.   | ELECTRALOGICS PRODUCT WARRANTY                                                                                                                                                                                                                                                                    | 22                          |

| E.   | USER'S COMMENTS                                                                                                                                                                                                                                                                                   | 23                          |

| F.   | SUBJECT INDEX                                                                                                                                                                                                                                                                                     | 25                          |

## LIST OF FIGURES

.

-

| 3-1: | Block | Enable | and | Disable Switches    | 6 |

|------|-------|--------|-----|---------------------|---|

|      |       |        |     | Disabled<br>Enabled |   |

# LIST OF TABLES

Si.

10

.

. .

\*

| 2-1:<br>2-2: | Micro-Processor Compatibility<br>Compatible Memory Devices | 3<br>5 |

|--------------|------------------------------------------------------------|--------|

| 3-1:         | Feature Select Jumper Designation                          | 8      |

|              | : Switch 5 - ctive Positions For Bank Select               |        |

| 3-3:         | Switch 5 - Settings For Specific Banks                     | 10     |

| 3-4:         | Switch 5 Functions - Extended Addressing Mode              | 11     |

|              | S-100 Bus Utilization                                      |        |

| 4-2:         | S-100 Bus Signal Characteristics                           | 13     |

| 4-3:         | Memory Address/Block Switch/Location                       | 14     |

#### 2. GENERAL DESCRIPTION

, <sup>6</sup>

٠.

Your 64k CMOS Static Ram Board uses state-of-the-art CMOS static memory devices and includes the following features:

Each of the 32 RAMs is addressable as a 2k block.

On-board Bank Select (Cromemco standard) is provided.

Extended-Addressing capability.

No wait-states necessary.

Phantom\* (S-100 line # 67 capability).

All S-100 bus lines fully buffered.

Schmitt-triggered logic used to reduce sensitivity to noise.

Printed circuit board is solder-masked and silk screened.

All S-100 fingers are gold plated to ensure minimum contact resistivity and long life.

2716 EPROM compatibility. Each memory device can be replaced with a 2716 EPROM. Allows permanent allocation of monitors, etc.

Single voltage power supply requirements.

Low power dissipation. Typical active board consumption of 350 milliamps at 8 Volts. Inactive power consumption is less than 250 milliamps at 8 Volts.

#### 2.0.1. Processor Compatibility

Electralogics Incorporated 64k CMOS Static Ram is guaranteed for use with the following processors and their slower versions:

|   | CPU     | 1 | MEM. | ACC. | . TIME | 1 | INST. C | YC. | TIME | 1 | CLK.H | FREQ. | _ |

|---|---------|---|------|------|--------|---|---------|-----|------|---|-------|-------|---|

| ſ | 8080A-1 | 1 |      | 320  | ns.    | 1 | 1.3     | us. |      | 1 | 3.2   | Mhz.  |   |

|   | 8085A-2 | 1 |      | 230  | ns.    | 1 | 0.8     | us. |      | 1 | 5.0   | Mhz.  |   |

|   | 8088    | 1 |      | 340  | ns.    | 1 | 0.8     | us. |      | 1 | 6.0   | Mhz.  |   |

|   | Z-80A   | 1 |      | 240  | ns.    | 1 | 1.0     | us. |      | 1 | 4.0   | Mhz.  |   |

Table 2-1: Micro-Processor Compatibility

The table above illustrates the relationship of memory access time, instruction cycle time and processor clock frequency. Clock frequency restrictions are often due to system bus, not memory, limitations.

The Hitachi 6116P-3 CMOS memory devices used on the 64k CMOS Static Ram Board have a very low power requirement which should result in total board consumption of less than 350 milliamps at 8 Volts. These 24-pin devices are internally organized in a "2k by 8" configuration and are 2716-compatible. Maximum Access Time is 150 nano-seconds.

Note: - Z-80 is the registered trademark of Zilog Corp. - 8080A, 8085A and 8088 are the registered trademarks of Intel Corp.

#### 2.1. BASIC FEATURES

#### 2.1.1. Basic Memory Size

Electralogics 64k CMOS Static Ram Board is available with a minimum population of 16k bytes of memory which can be upgraded in 2k byte increments to any capacity not exceeding 64k bytes.

#### 2.1.2. Bank Selection

Bank Selection is provided, allowing the memory to be used with Multi-User systems such as Digital Research's M/PM.

#### 2.1.3. Extended Addressing

Extended Addressing allows this board to be used in systems that have the ability to directly address up to 16 megabytes of memory (24 address bits).

#### 2.1.4. Power Requirements

Electralogics 64k CMOS Static Ram Board typically requires 350 milliamps of current at 8 volts for the full complement of 64k bytes. Maximum current requirements will not exceed 400 milliamps.

#### 2.1.5. Block Selection

Electralogics 64k CMOS Static Ram Board allows you to disable any 2k block of memory (at a 2k boundary) simply by turning off the appropriate Block Enable switch (switches 1 to 4). This flexibility is particularly suited to memory-mapped I/O or the use of EPROMs in which to locate a monitor or other firmware.

#### 2.2. COMPATIBLE MEMORY

Electralogics 64k CMOS Static Ram Board is manufactured and shipped with Hitachi 6116P-3 CMOS or similar, compatible, memory devices. Other pin-for-pin compatible memory devices are: ×

| SUPPLIER | 1 |          | MEM | ORY DEVICES |     |       |

|----------|---|----------|-----|-------------|-----|-------|

| SUFFLIEN | 1 | CMOS     | 1   | NMOS        | 1   | EPROM |

| Hitachi  |   | 6116P    |     |             |     |       |

| Intel    | i |          | i   |             |     | 2716  |

| Mostek   | 1 |          | Î   | MK4802      | - È |       |

| NEC      | 1 | uPD446   | 1   |             | 1   |       |

| OKI      | 1 | MSM5128  | 1   | MSM2128     | 1   |       |

| TI       | 1 | TMS4016  | 1   |             |     |       |

| Toshiba  | 1 | TC5517AP | 1   | TMM2016P    | 1   |       |

Table 2-2: Compatible Memory Devices

#### 3. OPERATION

3.0.1. Block Enable Switches (SW1 to SW4)

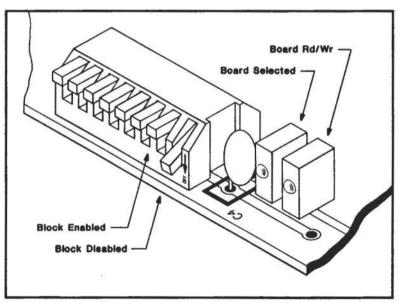

The Block Enable Switches (SW1 to SW4) are located at the top right of the board nearest to the voltage regulator. (See Figure below) Switches of the "piano" type were selected for use, and mounted along the top edge of the board, because they allow the user to alter the system's memory configuration without removing the memory board from the system.

It is NOT necessary to turn power off when changing the Block Enable Switch settings.

Each of the four switch assemblies contains 8 individual switch positions. Each switch position is responsible for enabling or disabling one of the 32 2k blocks of memory. When any switch is in the "ON" position, its associated 2k block is enabled and will function normally. When any switch is set to the "OFF" position, its 2k block is disabled. If a memory-read operation is performed to that 2k block, the board will not drive the bus.

It is not necessary to remove the memory device when it is disabled but it can be removed if you wish. Since each device draws only about 1 microamp when de-selected, very little power will be saved by removing it.

Two Light Emitting Diodes (LED's) are located on the top of the board immediately to the left of the Block Select switches. The yellow LED identifies the selected memory board in a system containing multiple memory boards. The red LED indicates when an active memory block is read from or written to. The red LED will never turn on unless the yellow LED is on (board selected). For additional information, see the later paragraph covering Board Selection.

Fig. 3-1: Block Enable and Disable Switches

#### 3.0.2. Phantom\* Enable/Disable (Jumper J1-p)

The S-100 PHANTOM\* line, when low, inhibits reading from all memory boards which have their Phantom Option enabled. Data can still be written to these same memory boards. This feature is useful when PROM-based bootstrap routines are used to perform system initialization. Plugging jumper J1-p enables the Phantom Option on the memory board. Removing jumper J1-p allows the board to function normally, ignoring the PHANTOM\* line, permitting memory to be written to, or read from, at any time. This jumper is located along the bottom of the board just above, and between, S-100 contact fingers 19 and 20.

#### 3.0.3. MWRT / PWR\* (Jumpers J3-m,-w)

Some systems, usually those having front panels, require that all memory boards respond to the MWRT signal which is generated by the front panel. Systems without front panels do not usually generate the MWRT signal and therefore, PWR\* must be used instead.

This option allows a memory board to be tailored to the system it is running in. If your system has a front panel, assume that this memory board should be strapped for MWRT and plug jumper J3-m. Otherwise, select PWR\* by plugging J3-p. These jumpers are located along the bottom of the board, just above S-100 contact fingers 25 and 26.

3.0.4. Feature Selection (Jumpers J2-b,-x,-a)

Before any memory read or write may be successfully performed, the board must be selected by the processor.

Three options are available (jumper selectable) to perform this function. These jumpers are located along the bottom of the board, just above S-100 contact fingers 22 to 24. They are:

| ł   | Jumper | ł | Feature               |

|-----|--------|---|-----------------------|

|     | 12 ~   |   | Danmanant Calastian 1 |

| î., | J2-a)  | i | Permanent Selection   |

| 1   | J2-b)  |   | Bank Select           |

| 1   | J2-x)  | 1 | Extended Addressing   |

Table 3-1: Feature Select Jumper Designation

#### 3.0.5. Permanant Selection Mode

The Permanent Selection Mode (Jumper J2-a plugged) is most commonly used. When this Mode is selected, the board is always enabled and all memory read or write operations access the board. Only one memory board may be used in the system.

This mode is usually selected in systems whose addressing range is limited to 64k bytes. Whenever the Permanent Selection Mode is enabled, Extended Address and Bank Select features are ignored. Switch 5 is non-functional.

#### 3.0.6. Bank Select Mode

Bank Select Mode (Jumper J2-b plugged) accomplishes board selection by having the user write one control byte of data to a "bank select" I/O port. This memory board recognizes the Cromemco standard for bank selection, that is, Port 40H as the Bank Select Control Port. Each bit of the control byte (when high) enables one 64k address space (one bank). By setting Switch 5's three high order positions to a binary value of 000 to 111, the board can be enabled for any one of 8 banks. When the control byte is written which corresponds to switch 5's setting, the board will be selected. Switch 5 settings are describes in appropriate sections of this manual.

On system initialization, a "write" to Port 40H should be performed to ensure that a bank is selected (Note: on power-up it is possible for more than one bank to be selected at the same time. Writing to Port 40H ensures that only the required bank will be enabled).

This mode is generally used in systems where more memory space is required and Extended Addressing is either not available or not desired. An example of such a system would be an 8080 or 8085 (or other 16 bit address bus) system running Digital Research's MP/M. A memory board containing 16k bytes of memory could be permanently enabled for running MP/M. Additional banks (up to 8 separate boards) of up to 48k bytes would be switched in and out as each user required service.

|     |   | BANK SELECT MODE            |

|-----|---|-----------------------------|

| SW5 |   | FUNCTION                    |

| 1   |   | Non-functional in this mode |

| 2   | 1 | Non-functional in this mode |

| 3   | 1 | Non-functional in this mode |

| 4   | 1 | Non-functional in this mode |

| 5   | 1 | Non-functional in this mode |

| 6   | 1 | LSB Bank Select Mode        |

| 7   | 1 | Bank Select Mode            |

| 8   | 1 | MSB Bank Select Mode        |

Table 3-2: Switch 5 - Active Positions For Bank Select

| Bank | Selected | ł | SW5-8 | ł   | SW5-7 | ł | SW5-6 |

|------|----------|---|-------|-----|-------|---|-------|

|      | 0        | 1 | ON    | 1   | ON    | 1 | ON    |

|      | 1        | - | ON    | 1   | ON    | Ì | OFF   |

|      | 2        | 1 | ON    | 1   | OFF   | 1 | ON    |

|      | 3        | 1 | ON    | 1   | OFF   | 1 | OFF   |

|      | 4        | 1 | OFF   | 1   | ON    | 1 | ON    |

|      | 5        | 1 | OFF   | - È | ON    | 1 | OFF   |

|      | 6        | 1 | OFF   | 1   | OFF   | Ì | ON    |

|      | 7        | 1 | OFF   | Ť.  | OFF   | 1 | OFF   |

Table 3-3: Switch 5 - Settings For Specific Banks

Note: Any switch "ON" = logical 0 "OFF" = logical 1

#### 3.0.7. Extended Addressing Mode

The Extended Addressing Mode (Jumper J2-x plugged) allows a direct memory address range of up to 16 megabytes (24 address bits). When using the Extended Addressing Mode, the 8 high- order address lines (IEEE 696 lines specified as A16 to A23) are compared to SW5 via U15 (74LS682). When the results of the comparison are equal, the board is selected and the yellow LED will be turned "ON". In this mode, all read and write operations will be ignored by the board unless it is selected.

This mode of operation is generally used by systems containing a processor board with extended addressing capabilities (that is, more address lines than the conventional 16) or, systems utilizing memory-management procedures (a means of extending the address range of a processor).

|     |   | TENDED AD |     |         |      |    |

|-----|---|-----------|-----|---------|------|----|

| SW5 |   |           | FUI | NCTION  |      |    |

| 1   |   | Compared  | to  | Address | Line | 23 |

| 2   | 1 | 11        |     | 11      | 11   | 22 |

| 3   | 1 | 99        |     | 11      | 11   | 21 |

| 4   | 1 | 11        |     | **      | 11   | 20 |

| 5   | 1 | 11        |     | **      | 11   | 19 |

| 6   | 1 | 11        |     | 11      | 11   | 18 |

| 7   | 1 | **        |     | 11      | 11   | 17 |

| 8   | Í | 11        |     | **      | tt   | 16 |

Table 3-4: Switch 5 Functions - Extended Addressing Mode

•

Note: Any switch ON = logical "0" OFF = logical "1"

Therefore, in order for the board to respond to addresses 000000H to 00FFFFH, set SW5 as follows:

| A          | 23    |    |    |    |    |     |    |    |    |    |    |    |    |    |    | ł  | 116 |

|------------|-------|----|----|----|----|-----|----|----|----|----|----|----|----|----|----|----|-----|

|            | -     |    |    |    |    | • • |    |    |    |    |    | -  |    |    |    | -  | -   |

| SW.5 POS'N | 1     | 1  | ł  | 2  | ł  | 3   | 1  | 4  | ł  | 5  | ł  | 6  | 1  | 7  | ł  | 8  |     |

|            | - i - |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    | - i |

| ON/OFF     | 1     | ON | 10 | NC | 10 | DN  | 10 | NC | 10 | NC | 10 | ON | 10 | ON | 10 | ON | 1   |

|            | -     |    | -  |    |    |     |    |    |    |    |    | -  | -  | -  | -  |    |     |

For the board to respond to addresses C30000H to C3FFFFH, set SW5 as follows:

|            | A2 | 3  |   |     |       |    |    |    |    |    |   |    |   |     |       | ł   | 116 |

|------------|----|----|---|-----|-------|----|----|----|----|----|---|----|---|-----|-------|-----|-----|

|            |    |    |   |     |       |    |    | -  |    | -  |   |    |   |     |       |     | -   |

| SW.5 POS'N | 1  | 1  | ł | 2   | ł     | 3  | ł  | 4  | 1  | 5  | ł | 6  | 1 | 7   | 1     | 8   | ł   |

| ON/OFF     | 10 | OF |   | OFF | -   ( | ол | 10 | оN | 10 | ON | ( | ом | ( | OFE | -   ( | OFF | 71  |

### 4. S-100 BUS LINE UTILIZATION

.

| PIN # NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | INPUT/OUTPUT                                                                 | CHARACTERISTICS                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 1         +8 VDC           15         A18           16         A16           17         A17           20         GND           29         A5           30         A4           31         A3           32         A15           33         A12           34         A9           35         D01           36         D00           37         A10           38         D04           39         D05           40         D06           41         D12           42         D13           43         D17           45         SOUT           46         SINP           47         SMEMR           50         GND           51         +8 VDC           53         GND           59         A19           61         A20           62         A21           63         A22           64         A23           67         PHANTOM           68         MWRT           70         GND | 1 Amp. max.<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I<br>I | A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A |

| 83       A7         84       A8         85       A13         86       A14         87       A11         88       DO2         89       DO3         90       DO7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                              | A<br>A<br>A<br>A<br>A<br>A<br>A<br>A                                                        |

| 91  | DI4 | 0 | В |

|-----|-----|---|---|

| 92  | DI5 | 0 | В |

| 93  | DI6 | 0 | В |

| 94  | DI1 | 0 | В |

| 95  | DIO | 0 | В |

| 100 | GND |   | - |

Table 4-1: S-100 Bus Utilization

#### 4.1. SIGNAL CHARACTERISTICS

4.1.1. (A) Input

- logical 1 input voltage => 2.0 V. logical 0 input voltage <= 0.8 V. input hysterisis voltage 0.4 V. typical logical 1 input current 20 uA. max. logical 0 input current -200 uA. max.

4.1.2. (B) Output

- logical 1 output voltage => 2.4 V. logical 0 output voltage <= 0.5 V. logical 1 output current => 3 mA. logical 0 output current => -24 mA.

4.1.3. (C) Input

- logical 1 input voltage => 2.0 V. logical 0 input volyage <= 0.8 V. logical 1 input current 20 uA. max. logical 0 input current -360 uA. max.

Table 4-2: S-100 Bus Signal Characteristics

Note: All inputs and outputs are IEEE - 696 compatible.

### 4.2. MEMORY MAP

.

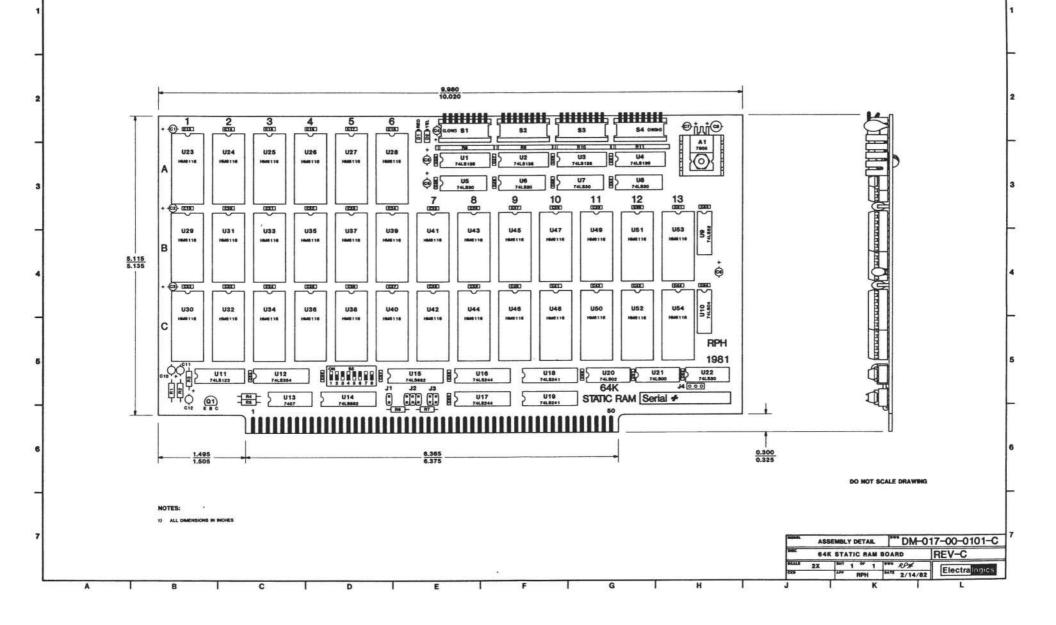

In order to accomodate the necessary 32 memory and associated support devices on the printed circuit board in a logical and esthetically appealing manner, it was necessary to arrange the memory in two horizontal rows of 13 and an additional row of six, devices.

The following chart indicates the hexadecimal address, memory block switch number and location for each device.

| Hex. Address                                                         | Block Sw. No.                                                                 | Location                                             |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------|

| 0000H                                                                | SW1-1                                                                         | A1                                                   |

| 0800H                                                                | SW1-2                                                                         | A2                                                   |

| 1000H                                                                | SW1-3                                                                         | A3                                                   |

| 1800H                                                                | SW1-4                                                                         | A4                                                   |

| 2000H                                                                | SW1-5                                                                         | A5                                                   |

| 2800H                                                                | SW1-6                                                                         | A6                                                   |

| 3000H                                                                | SW1-7                                                                         | B1                                                   |

| 3800H                                                                | SW1-8                                                                         | C1                                                   |

| 4000H                                                                | SW2-1                                                                         | B2                                                   |

| 4800H                                                                | SW2-2                                                                         | C2                                                   |

| 5000H                                                                | SW2-3                                                                         | B3                                                   |

| 5800H                                                                | SW2-4                                                                         | C3                                                   |

| 6000H                                                                | SW2-5                                                                         | B4                                                   |

| 6800H                                                                | SW2-6                                                                         | C4                                                   |

| 7000H                                                                | SW2-7                                                                         | B5                                                   |

| 7800H                                                                | SW2-8                                                                         | C5                                                   |

| 8000H                                                                | SW3-1                                                                         | B6                                                   |

| 8800H                                                                | SW3-2                                                                         | C6                                                   |

| 9000H                                                                | SW3-3                                                                         | B7                                                   |

| 9800H                                                                | SW3-4                                                                         | C7                                                   |

| A000H                                                                | SW3-5                                                                         | B8                                                   |

| A800H                                                                | SW3-6                                                                         | C8                                                   |

| B000H                                                                | SW3-7                                                                         | B9                                                   |

| B800H                                                                | SW3-8                                                                         | C9                                                   |

| C000H<br>C800H<br>D000H<br>D800H<br>E000H<br>E800H<br>F000H<br>F800H | SW4-1<br>SW4-2<br>SW4-3<br>SW4-4<br>SW4-5<br>SW4-6<br>SW4-6<br>SW4-7<br>SW4-8 | B10<br>C10<br>B11<br>C11<br>B12<br>C12<br>B13<br>C13 |

#### Table 4-3: Memory Address/Block Switch/Location

14

#### 5. FRONT PANEL MODIFICATIONS

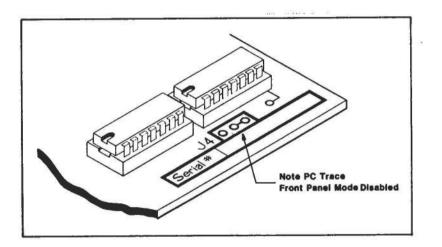

Some older system types, such as the MITS Altair 8800 and the IMSAI 8800, do not fully comply with the IEEE-696 S-100 Standard. Owners of these systems will not be able to "DEPOSIT" data into this memory board as shipped. All of the remaining front panel functions will perform normally.

In order to allow the front panel to perform all of its normal functions when using this memory board, locate the three jumper pads labelled "J4" in the lower right corner of the board just above the serial number. (See Figure below)

A printed circuit jumper is permanently connected between the centre and right hand pads. Cut this land, using a sharp knife. Make sure that you remove a short length of copper to prevent intermittent problems.

Fig. 5-1: Front Panel Mode Disabled

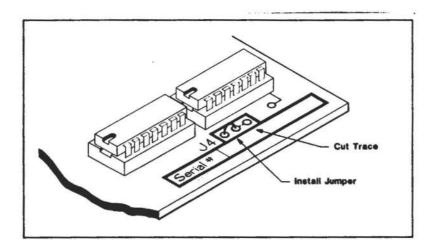

Then, using a fine-tipped soldering iron (25 to 35 Watts is best), install a jumper between pads 1 and 2 as shown.

The front panel will now function normally.

Fig. 5-2: Front Panel Mode Enabled

#### 6. MEMORY TEST

Your 64k CMOS Static Ram Board was shipped assembled and extensively tested. Instructions are provided for board set-up which can be followed with little difficulty. Since short memory tests are of little benefit in detecting memory problems, we have decided to leave the selection of a memory test to the user for many reasons.

We will presume that a user ordering a 64k memory board does have a functional system. Memory tests can be performed by removing an existing memory board from the user's system and, by setting the proper Block Select switches, substituting the same amount of memory as the removed board provided. Existing user tests can then be run on those blocks selected.

An excellent memory test program, which we use to test our products, is MEMRS.ASM. This test is often available from a Remote CP/M (RCPM) system. If you are not aware of any RCPM, or other similar system, in your area, check with your local computer store for information.

Some magazines devoted to the micro-computer user have recently published address lists of these systems.

Canadian CP/M users may procure diskettes containing memory tests and other public domain software from the BDSC User's Group, the CP/M User's Group, RCP/M User's Group and the SIG/M User's Group from by sending \$10.00 Canadian, (for any single 8-inch diskette from the above groups), to the address below. The price includes a diskette and postal charges.

> Toronto RCP/M, c/o G.J. Newell, 4691 Dundas Street West, Islington, Ontario M9A 1A7

CP/M User's Group diskettes are also available from:

CP/M User's Group, 1651 Third Avenue, New York, N.Y. 10028

### A. PARTS LIST

٠

.

| Description                                                                                                                                                                                                                                                                                               | Qty.                                           | Identification                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------|

| 100k 5% 1/4 Watt Resistor<br>150 Ohm 5% 1/4 Watt Resistor<br>2.2k 5% 1/4 Watt Resistor<br>470 Ohm 5% 1/4 Watt Resistor                                                                                                                                                                                    | 2<br>1<br>2<br>2                               | R1 R2<br>R3<br>R6 R7<br>R4 R5                                                                |

| Res. Network #4610X-101-332                                                                                                                                                                                                                                                                               | 4                                              | R8-R11                                                                                       |

| 0.01 uFd. 50V Ceramic Cap.                                                                                                                                                                                                                                                                                | 50                                             | C13-C62                                                                                      |

| 1.0 uFd. 35V Tantalum Cap.<br>10 uFd. 10V Tantalum Cap.<br>10 uFd. 25V Tantalum Cap.                                                                                                                                                                                                                      | 5<br>6<br>1                                    | C1-C3 C10 C11<br>C4-C7 C9 C12<br>C8                                                          |

| 2N3904 NPN Signal Transistor                                                                                                                                                                                                                                                                              | 1                                              | Q1                                                                                           |

| LED Red Dialco #555-2001<br>LED Yellow Dialco #555-2401                                                                                                                                                                                                                                                   | 1<br>1                                         | D1<br>D2                                                                                     |

| 7805 Voltage Regulator 1.5 Amp.                                                                                                                                                                                                                                                                           | 1                                              | VR1                                                                                          |

| 7407 Hex Buffer (OC)                                                                                                                                                                                                                                                                                      | 1                                              | U13                                                                                          |

| 74LS00 Quad 2-Input NAND<br>74LS02 Quad 2-Input NOR<br>74LS04 Hex Inverter<br>74LS30 8-Input NAND<br>74LS32 Quad 2-Input OR<br>74LS123 Dual Single Shot<br>74LS138 3-8 Line De-Mux<br>74LS241 Octal Buffer (TS)<br>74LS244 Octal Buffer (TS)<br>74LS354 8-1 Line Data Select.<br>74LS682 Octal Comparator | 1<br>1<br>5<br>1<br>1<br>4<br>2<br>2<br>1<br>2 | U21<br>U20<br>U10<br>U5-U8 U22<br>U9<br>U11<br>U1-U4<br>U18 U19<br>U16 U17<br>U12<br>U14 U15 |

| HM6116P-3 2k*8 Static Ram                                                                                                                                                                                                                                                                                 | 32                                             | U23-U54                                                                                      |

| 8 Pos'n Switch AMP #435640-5<br>8 Pos'n Switch Piano Type<br>AMP #435802-1                                                                                                                                                                                                                                | 1<br>4                                         | SW5<br>SW1-SW4                                                                               |

| Programming Shunt                                                                                                                                                                                                                                                                                         | 3                                              |                                                                                              |

| 14 Pin IC Socket<br>20 Pin IC Socket<br>24 Pin IC Socket                                                                                                                                                                                                                                                  | 10<br>7<br>32                                  | U5-U10 U13 U20-U22<br>U12 U14-U19<br>U23-U54                                                 |

| Double Row 0.025 Post Header<br>Double Row 4-Pin 0.025 Post<br>Double Row 6-Pin 0.025 Post                                                                                                                                                                                                                | 1<br>1<br>1                                    | J1<br>J3<br>J2                                                                               |

64k Ram Printed Circuit Board164k Ram User's Manual14-40 X 5/16 Pan Head Screw14-40 Hex Nut14-40 Star Lockwasher1TO-220 Mica Insulator1

· ·

### F. SUBJECT INDEX

### (

.

•

(A) Input, 13

(B) Output, 13

(C) Input, 13

### A

Access Time, 3 maximum, 3

### B

```

Bank Select Mode, 9

Bank Select

standard, 2

Bank Selection, 4

Basic Memory Size, 4

Block Enable Switches (SW1 to SW4), 6

Block Selection, 4

```

### C

```

Compatibility, 3

2716, 3

processor, 3

Compatible

CMOS, 5

EPROM, 5

NMOS, 5

memory, 5

pin-for-pin, 5

```

### E

Extended Addressing, 4 Extended Addressing Mode, 10

### F

```

Feature Selection (Jumpers J2-b

-x,-a), 8

Front Panel, 15

Altair, 15

IMSAI, 15

jumper, 15

```

s<sup>2</sup> •

Μ

```

MWRT / PWR* (Jumpers J3-m

-w), 8

Memory Test, 17

programs, 17

selection, 17

Memory

wait states, 2

```

### N

```

Noise

sensitivity, 2

```

### P

```

PHANTOM*

jumper location, 7

line, 7

Permanant Selection Mode, 8

Phantom* Enable/Disable (Jumper J1-p), 7

Power Requirements, 4

Processor Compatibility, 3

```

### R

```

Repair, 22

cost, 22

following the warranty period, 22

warranty, 22

```

### S

S-100 MWRT, 8 PWR\*, 8 Phantom\*, 2 contacts, 2

### W

1

Warranty, 22 period, 22 refund, 22 repair, 22

.

.

1

R

1

C

1

D

1

E

1

F

1

1

J

1

ĸ

1

L

н

1

G

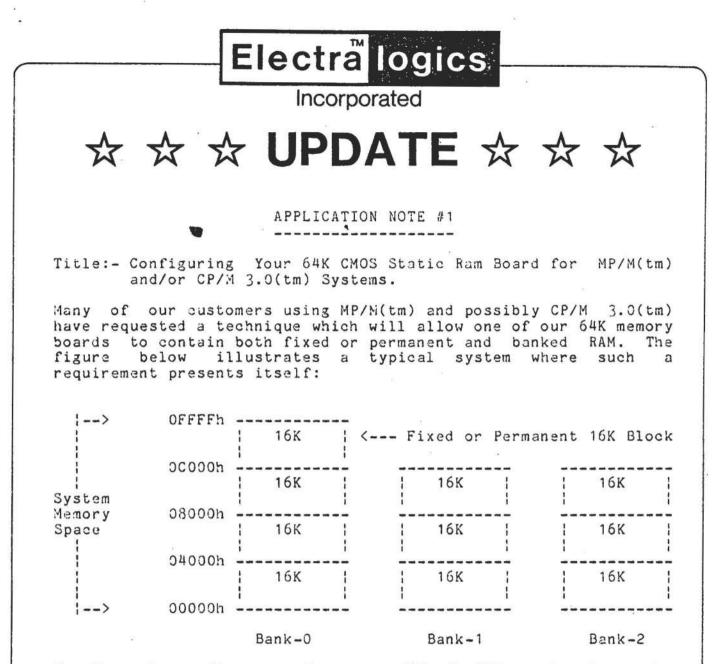

In the above diagram, the upper 16K of RAM must always be resident whereas the lower 48K must be bank selectable. Without the modifications which are to follow, 4 memory boards would be required to implement this system. The first board would contain the fixed 16K portion while the additional 3 boards would each be populated to 48K and be used to implement each of three banks. A technique is needed to allow one board to support not only the fixed portion of RAM, but also the memory for one bank.

The criteria for this modification were simple -

a) Keep it simple.

b) Don't destroy the product in the process.

Who knows, you may want to sell the board some day!

Modification: - Examining the schematics for your 64K RAM board will show that all the chip selects are generated by U1-U4 as follows: (These are the 74LS138's located below the dip switches)

U1 - 0000h to 3FFFh

U2 - 4000h to 7FFFh

U3 - 8000h to BFFFh

U4 - Q000h to FFFFh

To make any of these 16K blocks of RAM fixed is as simple as:

- a) Locate the proper IC (U1-U4).

- b) Lift pin 5 on the selected device and bend it back over the top of the chip.

- c) Use a small piece of wire and jumper pin 6 to pin 16(+5).

- d) Replace the IC.

The following example may help illustrate such a modification.

EXAMPLE: - The goal is to implement a system with three 48K banks which are bank selectable and range from 0000h to BFFFh and has 16K of RAM fixed from C000h to FFFFh.

SOLUTION: - This system will require 3 memory boards, one populated with 64K of RAM and two populated with only 48K.

On the 64K board, lift U4 and modify the chip as listed above. Replace U4. This operation has fixed the top 16K of this board. Note that any block which is modified as shown will not respond to the jumper option J2-b. Since the lower 48K of this board is to be used as one of the 3 banks, the jumpers should be set as follows:

J1 - as required by user.

J2 - select "b" for bank select.

J3 - select "m" for MWRT.

Assuming this bank is to be bank 0, set SW5 as follows:

SW5-1 to SW5-5 = don't care.

SW5-6 to SW5-8 = "on".

(See page 10 of User's Manual)

Note that SW1 to SW4 must have all switches "on".

2

The two 48K boards are to be setup as banks 1 and 2, and should be populated from 0000h to BFFFh. SW1 to SW3 should have all switches set to "on" while SW4 has all switches set to "off". Setting the jumpers as previously mentioned enables bank select on these boards as well.

Since one of the two boards is to be bank 1, SW5 will have to be set as follows:

SW5-1 to SW5-5 = don't care.

SW5-6 = "off".

۰.

SW5-7 to SW5-8 = "on"

Similarly, the board to be used as bank 2 should have SW5 set as follows:

SW5-1 to SW5-5 = don't care.

SW5-6 = "on".SW5-7 = "off".

SW5-8 = "on".

The banks are selected by sending the proper bank select code to port 40h. (Refer to User's Manual for more detail.) Notice however that the top 16K will always appear in the system's address space.

#### GOOD LUCK!

Notes: - All switch designations are as follows:

SW5-7 <--- Switch Designation

CP/M and MP/M are trademarks of Digital Research Inc.

3