ſ

# Processor Technology Corporation

7100 Johnson Industrial Drive Pleasanton, CA 94566 Telephone (415) 829-2600

Copyright © 1978, by Processor Technology Corporation First Edition, First Printing, July, 1978 Manual Part No. 730027 All rights reserved.

# CAUTION

Please read Section 2, Handling Precautions and Unpacking, before unpacking or handling your 48KRA-1 any further.

J

# CONTENTS

CONTRACTOR OF STREET, S

Sec. 1

C

í

C

| SECTION |       |                         |                                                              | PAGE               |

|---------|-------|-------------------------|--------------------------------------------------------------|--------------------|

| 1       | INTRO | DUCTION                 | AND GENERAL INFORMATION                                      |                    |

|         | 1.1   | INTRODU                 |                                                              | 1-1                |

|         | 1.2   | GENERA                  |                                                              | 1-1                |

|         | 1.3   | SPECIFI                 | CATIONS                                                      | 1-1                |

| 2       |       |                         | CAUTIONS AND UNPACKING                                       |                    |

| 2       | 2.1   |                         |                                                              | 2-1                |

|         | 2.2   |                         |                                                              | 2-2                |

|         |       |                         |                                                              |                    |

| 3       |       |                         |                                                              | 0.4                |

|         | 3.1   |                         | Y DISABLE OPTION                                             | 3-1                |

|         | 3.2   | SETTING                 | STARTING ADDRESSES                                           | 3-1                |

|         |       | 3.2.1<br>3.2.2          | Before Setting Switches<br>Instructions for Setting Switches | 3-1<br>3-1         |

|         | 3.3   | INSTALL                 | ATION                                                        | 3-3                |

|         | 3.4   | EXTEND                  | ED ADDRESSING AND 16-BIT DATA WORD OPTIONS                   | 3-4                |

| 4       | MEMO  | DRY TEST                |                                                              |                    |

|         | 4.1   | TEST BE                 | FORE OPERATING                                               | 4-1                |

|         | 4.2   | THE REC                 | COMMENDED PRE-OPERATING MEMORY TEST                          | 4-1                |

|         |       | 4.2.1                   | Test Procedure (Long Memory Test)                            | 4-1                |

|         | 4.3   | SHORT I                 | MEMORY TEST                                                  | 4-3                |

| 5       | THEO  | RY OF OP                | ERATION                                                      |                    |

|         | 5.1   | OVERVIE                 | Ε₩                                                           | 5-1                |

|         |       | 5.1.1                   | S-100 Bus Interface                                          |                    |

|         |       | 5.1.2<br>5.1.3          | Memory Array                                                 |                    |

|         |       | 5.1.4                   | Dynamic Memory Refreshing                                    |                    |

|         |       | 5.1.5<br>5.1.6          | Addressing<br>Write and Read Operations                      | 5-2<br>5-2         |

|         | 5.2   |                         |                                                              | 5-2                |

|         | 5.3   | MEMOR                   | Y CYCLES                                                     | 5-3                |

|         |       | 5.3.1                   | Timing Scheme Enables Independent Refresh                    | 5-3                |

|         |       | 5.3.2<br>5.3.3          | Timing of Memory Cycles         Types of Memory Cycles       | 5-3<br>5-5         |

|         | 5.4   | OPERAT                  | IONS: The State Machine                                      | 5-6                |

|         |       | 5.4.1                   | Variations of the Six Operations                             | 5-6                |

|         | 5.5   | REQUES                  | STS FOR MEMORY OPERATIONS                                    | 5-9                |

|         |       | 5.5.1<br>5.5.2<br>5.5.3 | Normal Access, Selected<br>Deposit<br>Refresh                | 5-9<br>5-9<br>5-10 |

|         |       |                         |                                                              |                    |

|   | 5.6     | EXTEND         | ED ADDRESSING                                                                       | 5-12 |

|---|---------|----------------|-------------------------------------------------------------------------------------|------|

|   |         | 5.6.1<br>5.6.2 | Types of Extended Addressing                                                        |      |

|   |         | 5.6.3          | Extended Selection Logic<br>Modification Guidelines for<br>Extended Selection Logic |      |

|   |         | MODIFIO        |                                                                                     |      |

|   | 5.7     | MODIFIC        | ATION FOR 16-BIT DATA WORDS                                                         | 5-14 |

| 6 | MAINT   | ENANCE         | AND DIAGNOSTICS                                                                     |      |

|   | 6.1     | SERVICE        | ·                                                                                   | 6-1  |

|   | 6.2     | REPLAC         | EMENT PARTS                                                                         | 6-1  |

|   | 6.3     | TROUBL         | ESHOOTING AND DIAGNOSTIC TEST PROGRAMS                                              | 6-1  |

|   | 6.4     | HARDWA         |                                                                                     | 6-1  |

| 7 | DRAW    | INGS           |                                                                                     |      |

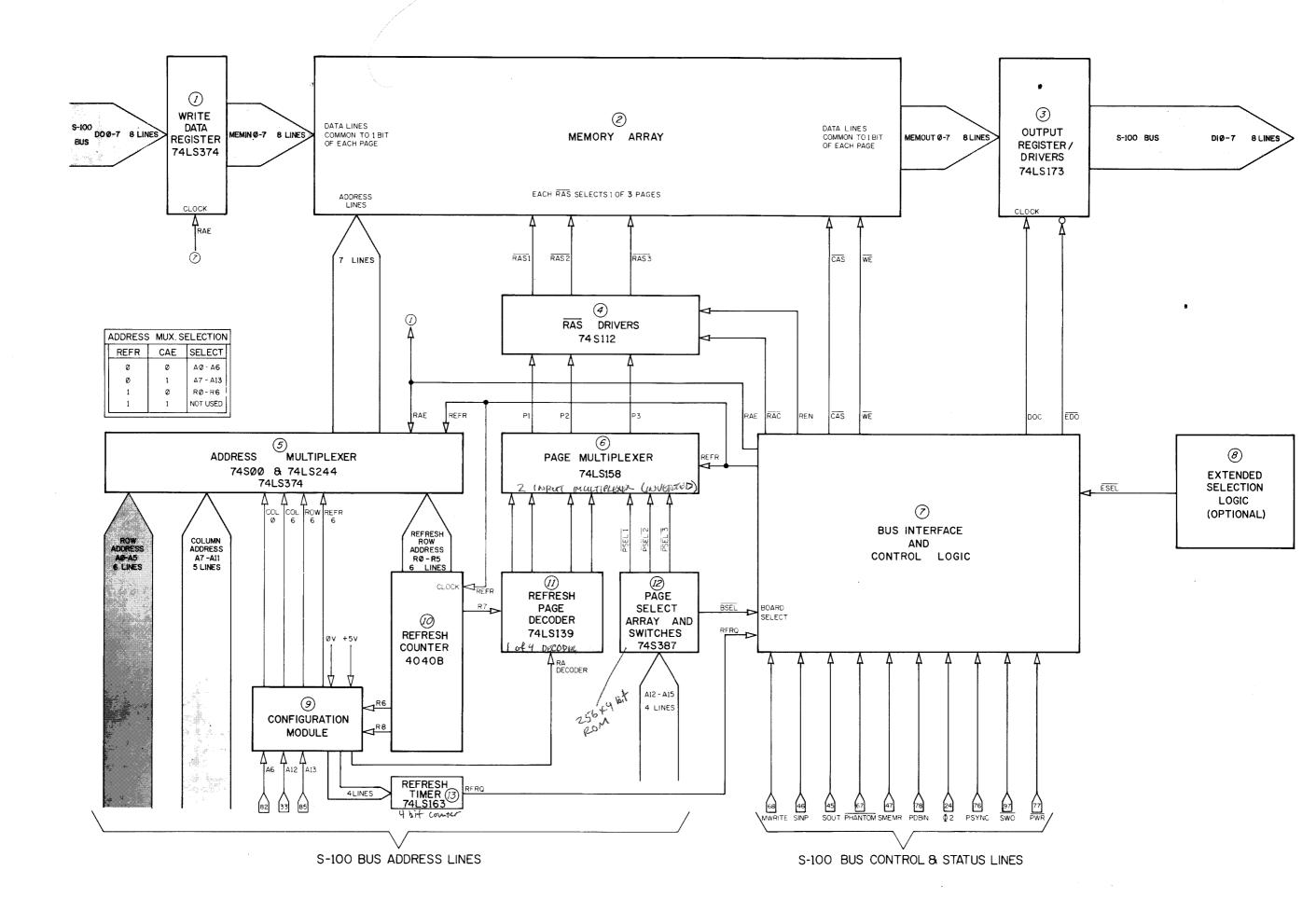

|   | Fig. 7- | 1. 48KRA       | -1 System Block Diagram                                                             |      |

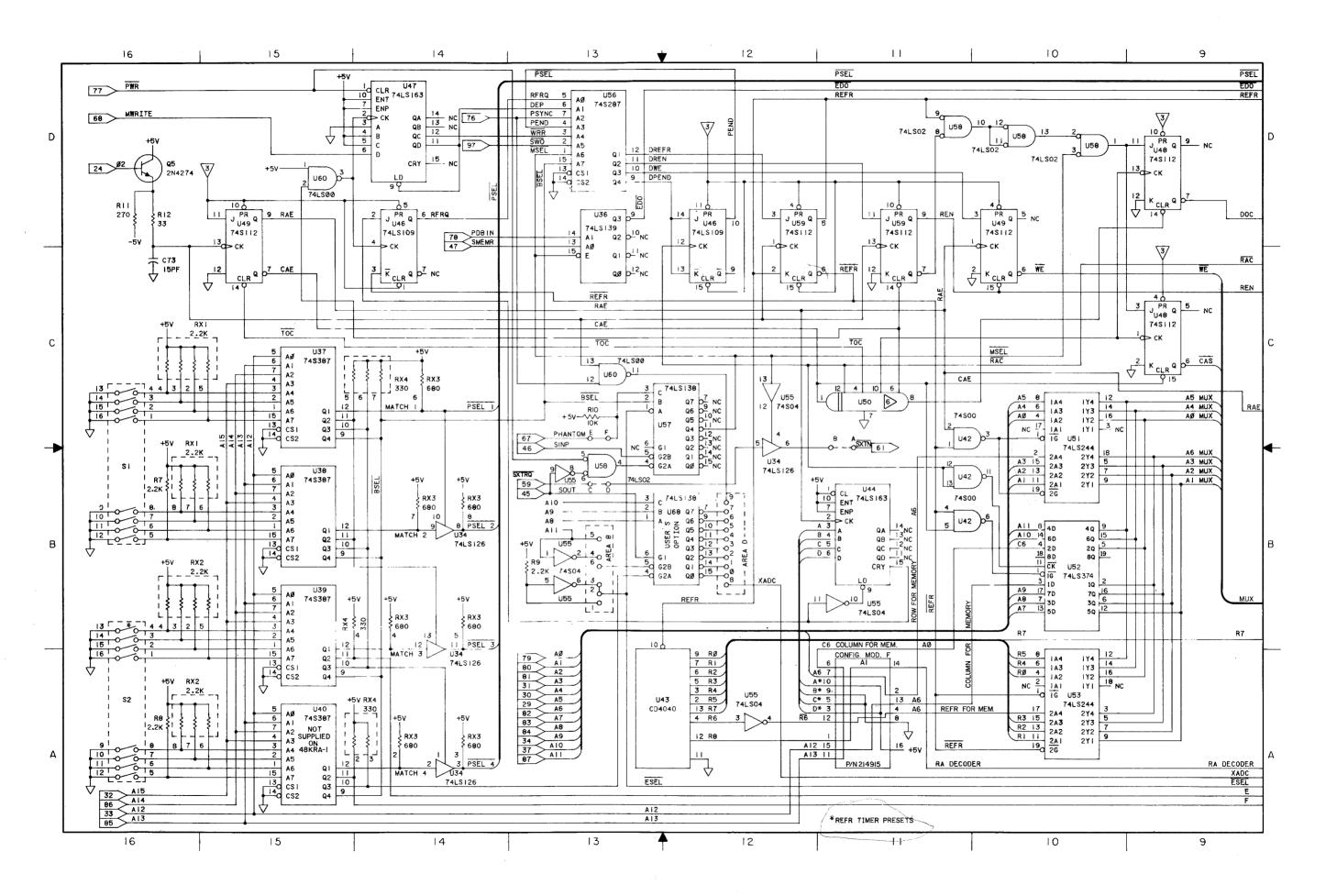

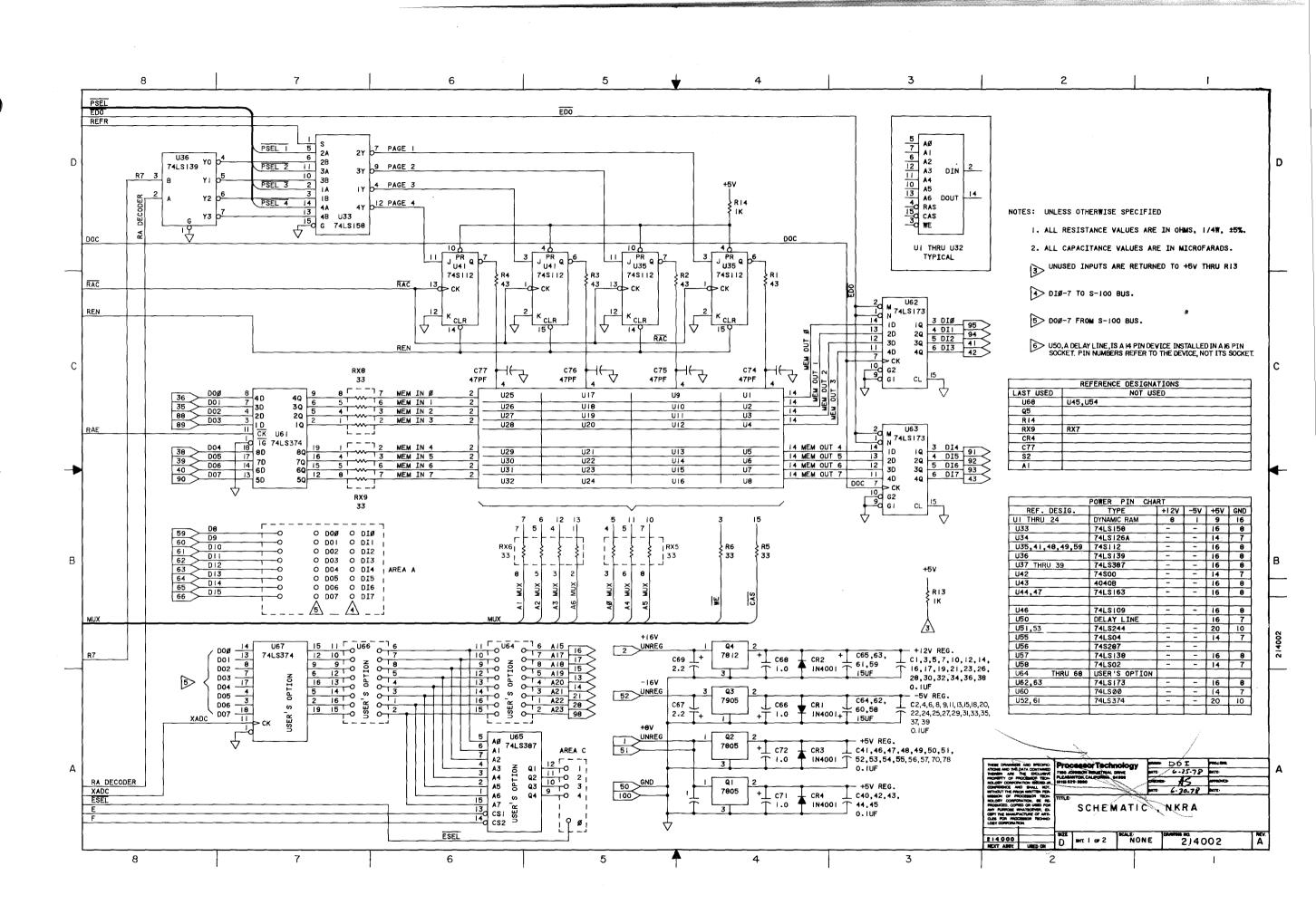

- Fig. 7-2. 48KRA-1 Schematic, Sheet 1 Fig. 7-3. 48KRA-1 Schematic, Sheet 2

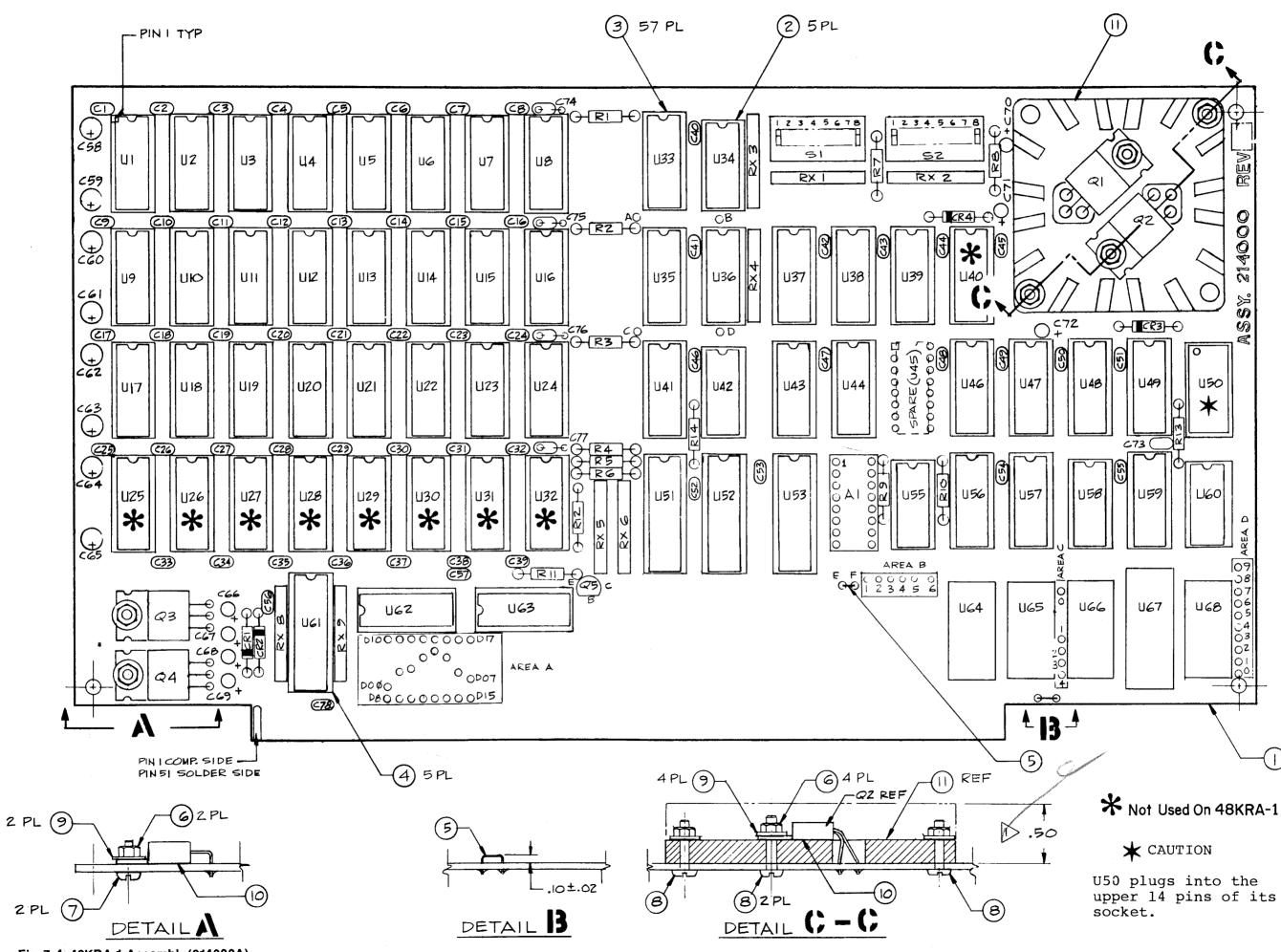

- Fig. 7-4. 48KRA-1 Assembly

- Fig. 7-5. 48KRA-1 PCB Traces

# APPENDICES

- 1 LONG MEMORY TEST PROGRAM, Listing

- 2 SHORT MEMORY TEST PROGRAM, Listing

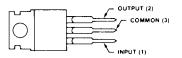

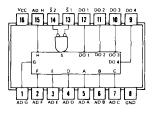

- **3 IC PIN CONFIGURATIONS**

# TABLES

| 3-1 | 48KRA-1 ADDRESS SWITCH SELECTION                  | 3-2  |

|-----|---------------------------------------------------|------|

| 5-1 | THE NINE STATES OF THE STATE MACHINE              | 5-8  |

| 5-2 | S-100 BUS SIGNALS OF THE 48KRA-1<br>MEMORY MODULE | 5-16 |

| 5-3 | INTERNAL SIGNALS OF THE 48KRA-1 MEMORY MODULE     | 5-17 |

| 7-1 | KEY TO SYSTEM BLOCK DIAGRAM                       | 7-2  |

# FIGURES

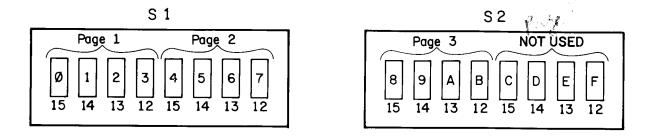

| 3-1 | Page and Address Assignments for 48KRA-1 Selection Switches . | 3-2  |

|-----|---------------------------------------------------------------|------|

| 4-1 | Page and Bit Assignments in Memory Array                      | 4-2  |

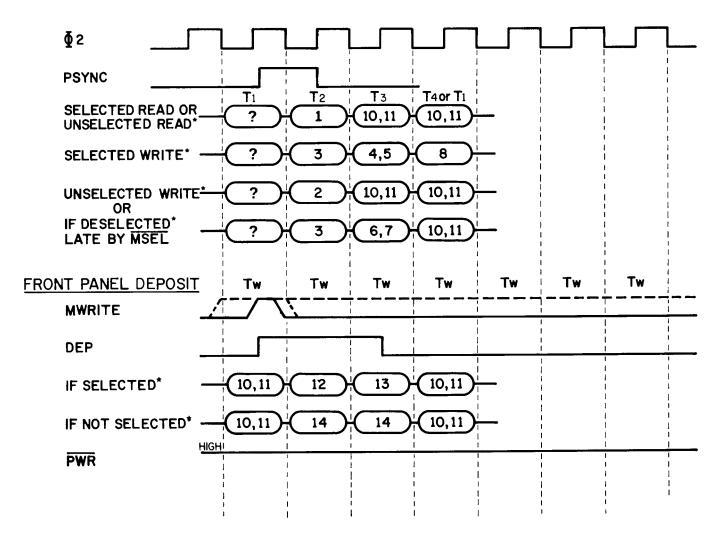

| 5-1 | Timing of Typical Read Cycle                                  | 5-4  |

| 5-2 | Sequences of the Operation Request Logic                      | 5-7  |

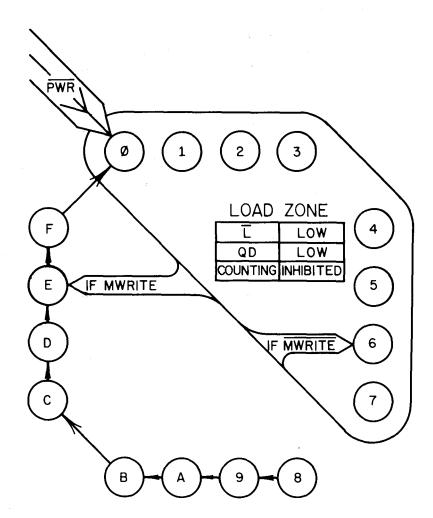

| 5-3 | States of the Synchronous Counter Producing DEPOSIT           | 5-11 |

iv

# SECTION 1

# INTRODUCTION AND GENERAL INFORMATION

#### **1.1 INTRODUCTION**

This manual supplies the information needed to test, use and maintain the 48KRA-1 Dynamic Read/Write Memory Module. In order that you might use your module most effectively and safely, we suggest that you read the entire manual before attempting to use the memory module.

#### **1.2 GENERAL INFORMATION**

The 48KRA-1 has a capacity of 49,152 8-bit words (bytes), stored in 24 16K-bit RAMs (Random Access Memories). The 48KRA-1 operates in a dynamic mode. Periodic refreshing is done automatically by the module.

The 48KRA-1 is designed to operate in the Sol S-100 bus and a number of other 8080-based computers which have a 2 MHz PHASE 2 rate without imposing *wait* states. Lines interfacing the S-100 bus are fully buffered.

Address allocation is switch selectable. The 48KRA-1 is organized into three pages of 16,384 bytes each. Each page may be independently assigned to any of 16 starting addresses at 4096-byte intervals, starting with address 0000 (hexadecimal). If the starting address is D000, E000, or F000, that part of the page which would fall beyond FFFF is assigned to memory space in the range 0000-2FFF. (Refer to Table 3-1, 48KRA-1 Address Switch Selection.)

A wide variety of extended addressing schemes are available as user options. Modifications for 16-bit data words can also be made by the user.

#### **1.3 SPECIFICATIONS**

The 48KRA-1 Memory requires the following ranges of unregulated DC supply:

+7.5 to +10 VDC at 1.20 A max +15 to +18 VDC at 0.20 A max -15 to -18 VDC at 0.02 A max

Access time is 460 ns; cycle time is 489 ns min.

Memory IC technology: MOS (Metal Oxide Semiconductor).

# SECTION 2

# HANDLING PRECAUTIONS AND UNPACKING

#### 2.1 HANDLING PRECAUTIONS

ŝ

4

Your memory module and its components are delicate electronic devices. If the following precautions are not observed, they could be damaged during handling, installation, removal, trouble-shooting, or component replacement.

1) Before installing or removing the memory module, turn the computer power OFF. To remove or install it with computer power on can damage the module or the computer.

2) Before installing or removing ICs, turn OFF power to the memory module. To remove or install them with power on can damage the ICs.

3) The memory ICs used on the memory module are MOS devices. MOS (Metal Oxide Semiconductor) devices are constructed with a very thin insulating layer of silicon dioxide (glass) separating the metal gate from the substrate. This layer can be punctured by electric fields, such as static electricity, as small as 100 V carrying only 10 pA. To avoid any possible static electricity discharge damage to the MOS elements, always take care to handle the memory module or its MOS ICs in such a way that no discharge flows through them from your body or from tools.

- a. When installing or removing the memory module or its MOS ICs, before touching the module with one hand, always place the other hand on the computer chassis first to discharge static.

- b. When grasping the module, grasp it by its edge-connector or the bus traces around its perimeter.

- c. Avoid unnecessary handling of the module and the ICs. When handling the MOS ICs, wear cotton clothing (rather than synthetic). Be sure to discharge your body static field before touching the MOS ICs.

All ICs other than the memory ICs and U43 are Schottky TTL and low power Schottky TTL. These do not require precautions against static electricity.

## 4) Ground Test Point Connections

Attach ground clip leads only on the test point (wire loop) installed for this purpose at pin 50 in the lower right corner of the component side of the module. (Refer to Fig 7-4, 48KRA-1 Assembly.) Do not attach clip leads to the ground or power buses around the perimeter of the board. Such connections are liable to short to IC pins.

## CAUTION

The heatsink is a poor ground because its finish is nonconducting. Do not attach clip leads to the heatsink.

#### 5) Manufacturing Options

A1 is a special configuration module which is varied by the factory according to the memory ICs used in a given production run. Do not interchange or mix the configuration modules of your 48KRA-1 with those of any other memory module which contains a different make and/or type of memory IC.

#### 2.2 UNPACKING INSPECTION

1) Examine the shipping container for signs of possible damage to the contents during transit.

2) READ SECTION 2.1, HANDLING PRECAUTIONS, CAREFULLY.

3) Carefully open the container and withdraw the memory module. Do *not* sink a knife blade deep within the container.

4) Save the shipping materials for possible use in returning the module to your dealer, and in case the dealer needs to ship it to the factory.

5) Visually inspect the module for obvious physical damage. Check that all integrated circuits (ICs) are fully seated in their sockets.

6) If your 48KRA-1 is damaged, please contact the carrier and your dealer immediately, describing the condition of both the shipping container and its contents so that they can take appropriate action.

# SECTION 3

# SETUP AND INSTALLATION

#### 3.1 MEMORY DISABLE OPTION

The 48KRA-1 comes with the memory disable option (PHANTOM) installed in the form of a jumper wire between pads E and F. It is recommended that you retain this option which allows the memory module, at address Ø, to be disabled by the signal PHANTOM which is supplied on S-I00 bus pin 67 by the Sol computer and Processor Technology firmware modules such as ALS8 and GPM. PHANTOM is also produced by various other S-100 subsystems available from microcomputer vendors.

If necessary, PHANTOM can be disabled by snipping off the jumper between E and F. E and F are located below the configuration module A1. (Refer to Fig. 7-4, 48KRA-1 Assembly.)

# 3.2 SETTING STARTING ADDRESSES

# 3.2.1 Before Setting Switches

Each of the four pages can be independently allocated with the DIP (Dual Inline Package) switches located near the upper right edge of the module. (Refer to Fig 7-4, 48KRA-1 Assembly.) Page and address assignments for these switches are shown in Figure 3-1, Page and Address Assignments for 48KRA-1 Selection Switches.

You may assign the same starting address to two, or all three pages on *one* module with no ill effect.

In general, you may *not* assign to a module any memory space that is already assigned to another module if they are to share the same bus simultaneously. To do so will cause the bus drivers to contend for possession of the bus resulting improper operation or damage. (One exception to this general rule is if the PHANTOM memory disable option is installed. This option allows the ALS8 to share address zero with a 48KRA-1.) Another exception is bank select or extended addressing. See section 5.6 on extended addressing.

## 3.2.2 Instructions for Setting Switches

Since the DIP switches are located on the top edge of the memory module, they are accessible after the module is installed in the S-100 backplane; however, to avoid removing the cover of the computer unnecessarily, it is recommended that you set the address switches before installing the module.

1) To select the desired starting address for a page, refer to Table 3-1, 48KRA-1 Address Switch Selection.

# 1K = 1024 bytes $(2^{10})$ Table 3-1. 48KRA-1 Address Switch Selection

|         | STARTING | G ADDRESS | ENDING A | DDRESS | DIF | I SETTING | INGS |      |  |

|---------|----------|-----------|----------|--------|-----|-----------|------|------|--|

| 1.4     | Decimal  | Hex       | Decimal  | Hex    | A15 | A14       | A 13 | A 12 |  |

| OK      | 0        | 0000      | 16,383   | 3FFF   | 0   | 0         | 0    | 0    |  |

|         | 4,096    | 1000      | 20,479   | 4FFF   | 0   | 0         | 0    | 1    |  |

|         | 8,192    | 2000      | 24,575   | 5FFF   | 0   | 0         | 1    | 0    |  |

|         | 12,288   | 3000      | 28,671   | 6FFF   | 0   | 0         | 1    | 1    |  |

| 152     | 16,384   | 4000      | 32,767   | 7FFF   | 0   | 1         | 0    | 0    |  |

|         | 20,480   | 5000      | 36,863   | 8FFF   | 0   | 1         | 0    | 1    |  |

|         | 24,576   | 6000      | 40,959   | 9FFF   | 0   | 1         | 1    | 0    |  |

|         | 28,672   | 7000      | 45,055   | AFFF   | 0   | 1         | 1    | 1    |  |

| Jan San | 32,768   | 8000      | 49,151   | BFFF   | 1   | 0         | 0    | 0    |  |

|         | 36,864   | 9000      | 53,247   | CFFF   | 1   | 0         | 0    | 1    |  |

|         | 40,960   | A000      | 57,343   | DFFF   | 1   | 0         | 1    | 0    |  |

|         | 45,056   | B000      | 61,439   | EFFF   | 1   | 0         | 1    | 1    |  |

| St. Jam | 49,152   | C000      | 65,535   | FFFF   | 1   | 1         | 0    | 0    |  |

|         | 53,248   | D000      | 4,095    | ØFFF   | 1   | 1         | 0    | 1    |  |

|         | 57,344   | E000      | 8,191    | 1FFF   | 1   | 1         | 1    | 0    |  |

|         | 61,440   | F000      | 12,287   | 2FFF   | 1   | 1         | 1    | 1    |  |

0 = Switch open (or OFF - in down position - memory block inactive)

1 = Switch closed (or ON - in up position - memory block active)

Fig. 3-1. Page & Address Assignments for 48KRA-1 Selection Switches

2) Find the desired starting address for the first page of the memory module in the field titled "STARTING ADDRESS." (Only the indicated starting addresses are available. No intermediate addresses can be used.)

3) On the same horizontal line as the desired starting address, find the corresponding settings for the four switches A15, A14, A13, and A12 in the column titled "DIP SWITCH SETTINGS".

4) On the memory module, find the group of four DIP switches associated with the first page. These are the first four in Switch 1. Refer to Fig 3-1, Page and Address Assignments for 48KRA-1 Selection Switches. Set the four switches to the selected pattern.

5) In the same manner, set the 4 switches associated with each of the remaining pages.

**EXAMPLE 1:** Note that each page takes up four 4K blocks. For continuous memory from 0000 to BFFF, the switch settings would be:

|              | Page 1 | Page 2 | Page 3 |

|--------------|--------|--------|--------|

| START. ADDR: | 0000   | 4000   | 8000   |

| SETTINGS:    | 0000   | 0100   | 1000   |

EXAMPLE 2: For MEMORY at D000-FFFF and 0000-4FFF.

|              | Page 1 | Page 2 | Page 3 |

|--------------|--------|--------|--------|

| START. ADDR: | D000   | F000   | 1000   |

| SETTINGS:    | 1101   | 1111   | 0001   |

Note that Page 1 covers both D000-FFFF and 0000-0FFF, and that Page 2 covers both F000-FFFF and 0000-2FFF.

| EXAMPLE 3:   | FØR MEMØRY RT 0000-6FFF. |        |        |  |  |  |  |  |

|--------------|--------------------------|--------|--------|--|--|--|--|--|

|              | Page 1                   | Page 2 | Page 3 |  |  |  |  |  |

| START. ADDR: | 0000                     | 3000   | 3000   |  |  |  |  |  |

| SETTINGS     | 0000                     | 0011   | 0011   |  |  |  |  |  |

Note that is is permissible for a page to overlap part of another page, or a full page, and that the order of assignment is not important.

You may change address switches with the board installed and power on. But to do this with a program running may crash the program.

#### 3.3 INSTALLATION

1

(Be sure you have read 2.0, Handling Precautions.)

1) Turn OFF AC power to the host computer.

2) If you are using a Sol computer, make sure it is jumpered for the standard 2.045 MHz clock rate. If you are using another computer, make sure its clock rate is 2.045 MHz or less.

3) Discharge any possible static charge from your body.

4) Be sure the address selection switches are set as desired. (Refer to the previous subsection 3.2, Setting Address Switches.)

5) Orient the memory module to correspond with Fig 7-4, 48KRA-1 Assembly. (The legend should be in the readable position.)

6) Find pin 1 on the computer S-100 bus connector.

7) Orient the memory module edge-connector so that its own pin 1 will mate with pin 1 of the S-100 bus connector. On the component side of the board, edge-connector pin 1 is at the left end of the connector and pin 50 is at the right. Pins 51 through 100 are from left to right on the solder side (backside).

Ć

3-3

ł

#### CAUTION

If the memory module is installed reversed, the memory module and/or computer could be damaged when power is applied.

8) Slide the memory module into the card guides until its edge-connector just enters the bus connector.

9) Gently push on the module until it is fully seated in the bus connector.

# 3.4 EXTENDED ADDRESSING AND 16-BIT DATA WORD OPTIONS

Several options for extending addressing beyond 64K are provided for on the memory module. Because of the multiplicity of extended addressing schemes possible and presently used, only general guidelines for its implementation are given. The guidelines, together with the theory, are found in Section 5.6, Extended Addressing. A method for modifying the board to provide 16-bit data words is described in section 5.7.

# SECTION 4

# **MEMORY TEST**

# 4.1 TEST BEFORE OPERATING

Your 48KRA-1 memory module is fully inspected and tested before shipment to ensure that it is operating to specifications. It is packaged for safe transit under normal shipping conditions. Your memory module should, therefore, arrive in your hands ready for use. Nonetheless, we recommend that you test your 48KRA-1 before using it.

This section describes the use of two memory tests: a short test and a "long" test. Actually, the difference in run time between the two tests is not significant. The size of the long test is 15F (hex); the short test is 4C (hex). It is recommended that you use the long version since it is more thorough and more useful for trouble-shooting. Your dealer will allow you to make a tape copy of the long test. If necessary, the short test can be keyed into the computer and used instead. The long test can be entered in an evening's work.

Both these memory tests may also be used as diagnostic tools at any time after their initial use as pre-operating tests.

# NOTE

The memory test programs are written for use with Processor Technology SOLOS or CUTER monitor programs. If you are not using either, you will need to modify the test programs to work with your monitor program.

## 4.2 THE RECOMMENDED PRE-OPERATING MEMORY TEST

(A listing of the long memory test is in the Appendix.)

In addition to testing your memory module, the long memory test prints out a complete map of the memory ICs as they are arranged on the board, marking bad ICs with an X.

#### 4.2.1 Test Procedure (Long Memory Test)

1

1) Obtain a copy of the test on cassette from your dealer. If you own a 48KRA-1, you may copy the program without violating the copyright. If you cannot obtain a copy, at the next step of this procedure, key in the program from the listing in the Appendix. Once in the computer, the program can be saved on tape for later use.

2) Set the page assignment switches for continuous memory from Ø to 48K, referring to section 3.2, Setting Starting Addresses.

Fig. 4-1. Page & Bit Assignments in 48KRA-1 Memory Array.

48KRA-1

4-2

3) Load the long memory test into memory at C900 (hex). The Sol computer contains built-in system memory at the necessary locations. The program could be reassembled to run at a different address if necessary.

4) Type: EXEC C900 Press RETURN:

The test displays a copyright notice and displays two options for selection by a key stroke:

**Press C** The test echoes "C" and repeats the test continuously, accumulating a record of errors. After each pass through the test, this option updates the test results, a map of ICs.

**Press any** The test echoes the key typed and runs one complete test cycle, displays the map of ICs, and returns control to SOLOS/CUTER.

For the pre-operating memory test, select the C option.

#### EXAMPLE OF ERROR MAP

| AVIZE J     | GG GG GG GG |                    |

|-------------|-------------|--------------------|

| 81. Sec 6-> | XG GG GG GG | G = Good Memory IC |

| 12=3        | GG GG GG GG | X = Bad Memory IC  |

Reading left to right, top to bottom, each character in the map represents one of the 24 memory ICs, UI through U24. The characters are displayed in the same position as the memory ICS on the circuit board, when the board is oriented as in the assembly drawing, Fig 7-4. (For page and bit assignments in the memory array, refer to Fig. 4-1.)

The example map above therefore shows that U9 made one or more errors during the test.

Any memory IC reported as an "X" must be replaced.

5) If the continuous test runs for 30 minutes with no "X" appearing, consider the memory module as having passed.

6) To return control to SOLOS/CUTER at any time, press ESCAPE or UPPER CASE and REPEAT simultaneously.

7) If you have keyed in the program by hand and it runs correctly, save it on cassette for later use, using the SOLOS/CUTER SAVE command. (Refer to SOLOS/CUTER User's Manual.)

## 4.3 SHORT MEMORY TEST

(Refer to the Appendix for the listing.)

Use this short version only if the long version is not available.

1) Set the page select switches for continuous memory from 0 through 48K. (Refer to 3.2, Setting Starting Addresses.)

2) Load the program into memory at C900 (hex). The Sol computer contains built-in system memory at this location. The program could be reassembled to run at a different address if necessary.

# 3) Type: EXEC C900

If no errors are encountered, the program repeats continuously. If the test runs for 30 minutes without the SOLOS/CUTER prompt appearing, consider the memory module to have passed the test.

4) Return control to SOLOS/CUTER by simultaneously pressing: UPPER CASE and REPEAT.

5) If the SOLOS/CUTER prompt appeared while the test was running, the read data did not match the write data. An error report is stored in four locations of memory, which may be viewed as follows:

a. Enter the command: DU C949 C94C <CR>.

The resulting display shows:

| Byte 1 and 2 | The memory address where the error occurred. (Most significant |

|--------------|----------------------------------------------------------------|

|              | byte first.)                                                   |

Byte 3 Correct Data.

Byte 4 Erroneous Data.

- b. If the most significant digit of the error address (in hex) is 1, 2, or 3, the error is in an IC in Page 1.

- $j \in \mathcal{I}$  c. If it is 4, 5, 6, or 7, the error is in Page 2.

$^{\prime}$  d. If it is 8, 9, A, or B, the error is in Page 3.

- e. Determine the bad bit by comparing the correct and erroneous data stored in bytes 3 and 4 of the error report.

- f. Knowing the bad bit and page, find the bad IC from Figure 4-1 and replace it.

with hed a south from.

# SECTION 5

# THEORY OF OPERATION

#### 5.1 OVERVIEW

As you read this section refer to the block diagram, Figure 7-1 and the schematic, Figures 7-2 and 7-3. Note that the schematic is divided into two sheets which may be folded out in both directions, and that signals which go between the two sheets line up at the binding of the manual.

The encircled numbers following the name of a functional block of circuitry described in this section correspond to the key numbers for the referenced block on the system block diagram, Fig. 7-1 and Table 7-1, Key to System Block Diagram.

# 5.1.1 S-100 Bus Interface

The host computer and the 48KRA-1 communicate with one another over the S-100 Bus. Table 5-2, S-100 Bus Signals, identifies these signals and their sources and defines their functions. Table 5-3 briefly describes internal signals of the memory module.

## 5.1.2 Memory Array

The memory array (2) consists of 24 16K dynamic memory ICs arranged in three rows of eight. Each dynamic RAM can store 16,384 bits. Each row of eight ICs stores 16,384 bytes. Each of the three rows is a page of memory.

## 5.1.3 Manufacturing Options

The memory module can support a wide variety of memory ICs which are 16-pin DIP ICs requiring +12 V, +5 V, and -5 V. Four pins are used for power supplies. One pin connects data-in and another connects data-out. Seven pins carry address information (14 bits in two samples). WE indicates whether to read or write, CAS provides timing, and RAS provides timing and selection. The memory module is designed to operate using a wide variety of memory ICs having various speeds. Any of a number of types may have been supplied with your module. Circuit variations required for the different memory ICs are provided in a variable 16-pin configuration module (A1) which plugs into a standard IC socket.

# 5.1.4 Dynamic Memory Refreshing

Since the memory ICs used in the 48KRA-1 are dynamic memories in which the data cells operate by stored electrical charge which gradually dissipates, stored data must be restored periodically. Otherwise, current leakage would eventually change the stored data. The restoring process is called "refreshing" the memory, or simply "refresh." The 48KRA-1 itself provides memory refresh as required without any external intervention. In all cases it is done without introducing any delay to the CPU or DMA device controlling the module.

# 5.1.5 Addressing

Assignment of the S-100 address lines are as follows:

| AØ-5            | Row addressing.                                                      |

|-----------------|----------------------------------------------------------------------|

| A7-A11          | Column addressing.                                                   |

| A12-A15         | Page selection or 4K block selection.                                |

| A6, A12 and A13 | May be used for row or column, depending upon the type of memory IC. |

Address lines A12-A15 are compared to the three sets of four DIP switches to select one or none of three 16K memory arrays called "pages." Each page consists of one row of eight 16K RAM (Random Access Memory) ICs.

Address lines A0 through A5 and A7 through A11 are applied to the Address Multiplexer (5) in two groups. These two groups are selected in succession to the memory address inputs. Row Address Strobe (RAS) is applied by the RAS Drivers (4) to the eight memory ICs of the selected page. The leading edge of RAS causes these eight ICs to store A0-A5, the first group of address bits, called the row address, and to start a memory cycle.

Subsequently, Column Address Strobe ( $\overline{CAS}$ ) (generated from the Bus Interface and Control logic (7)) is applied to all of the memory ICs. The leading edge of  $\overline{CAS}$  causes those memory ICs selected by  $\overline{RAS}$  to store the second group, A7-A11, called the column address.

Note that the column address section of the address multiplexer contains a Type D register which samples the S-100 lines at the same instant that RAS is causing the memory ICs to sample the ROW addresses. These latched address bits are subsequently moved to the memory ICs by CAS.

# 5.1.6 Write and Read Operations

CAS samples Write Enable (WE) to determine whether the current cycle is to write data into memory or to read data from memory. The contents of the Data-Out Bus (DOØ-DO7) are applied to the MEM IN pins of the memory array by the Write Data register (1). This register is clocked at the rise of RAE with the start of each memory cycle. Each bit from the Data Out bus is applied to three memory ICs, one in each of the three pages. In a memory write operation, CAS causes the selected eight memory ICs to store the data found on their Data-In pins in an input latch. This data is subsequently stored at the location described by the row and column addresses.

In a memory read operation, the selected eight memory ICs retrieve data from the memory address indicated by the row and column addresses, send it to their output latches, and enable their output drivers. At the end of RAS and CAS, the read data is latched into the output register (3), and is sent to the Data In Bus (DIØ-DI7) if EDO (Enable Data Output) is low.

# 5.2 PAGE SELECTION

Page selection and board selection depend on the address bits A12-A15 and on three quartets of switches. Each quartet of switches can be set to one of 16 possible starting addresses. Each quartet of switches corresponds to one page of eight memory ICs. The contents of each quartet of switches is compared to address bits A12-A15 by a ROM (Read Only Memory) in the Page Select Array (12) (U39 - U42). If a match is found, the output line from that ROM goes low. There are three such output lines, one per ROM, called MATCH lines.

Each MATCH line corresponds to a page. A zero (low) on any MATCH line causes the PSEL (Page Select) lines of higher page number to be held high, thus only one page can be enabled (that with the lowest page number) even though more than one switch set may match A12-A15. This feature allows the memory module to be used in systems where less than its full memory extent is needed.

During memory cycles, the three  $\overrightarrow{\text{PSEL}}$  (Page Select) lines are selected by the Page Multiplexer  $\widehat{(6)}$  to drive the three PAGE lines. The PAGE lines select one or none of three  $\overrightarrow{\text{RAS}}$  (Row Address Strobe) Drivers  $\widehat{(4)}$ . Each  $\overrightarrow{\text{RAS}}$  selects one of three pages in the memory array  $\widehat{(2)}$

ŧ

))

# 5.3 MEMORY CYCLES

(As defined in terms of the 48KRA-1, a cycle is a timed sequence of events that may perform one memory access.)

#### 5.3.1 Timing Scheme Enables Independent Refresh

48KRA-1 memory cycles correspond to S-100 bus T-cycles. This means that the memory module will not work in systems in which the PHASE 2 clock period is shorter than the minimum cycle period specified for the memory module: 489 ns. This allows a simple control logic design which does its needed refreshing totally independent of the S-100 bus and the CPU. There are no "coincidence" cycles in which the bus and the refresh logic contend for possession of the memory. There are no "wait" states, and the memory module does not use the ready lines.

#### 5.3.2 Timing of Memory Cycles

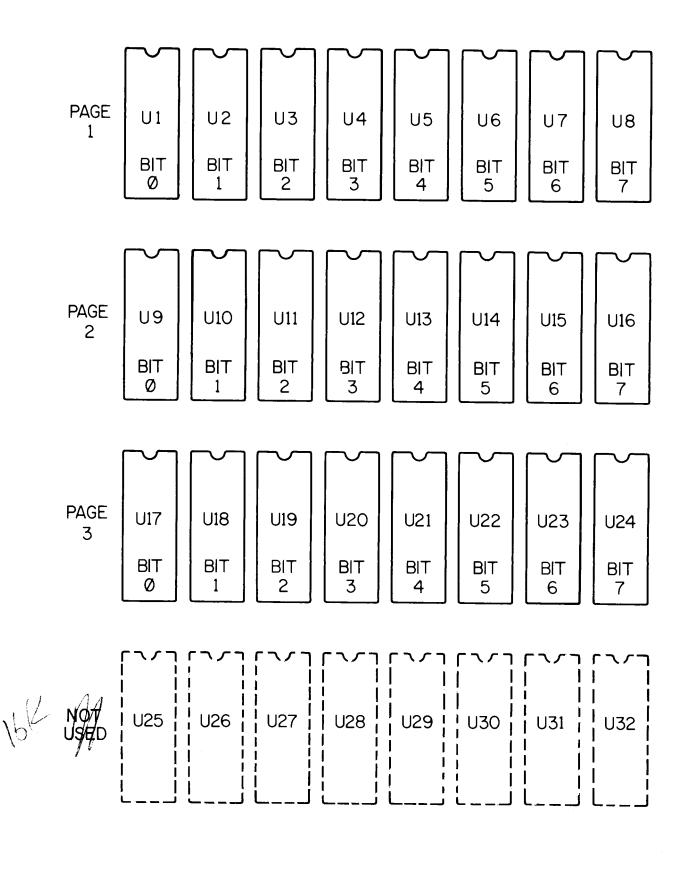

Located in the Bus Interface and Control Logic (7), the cycle timing circuitry consists of a latch and delay line driver, a delay line with five taps (U50) and a number of latches to provide the specific signals needed.

When the S-100 bus clock, PHASE 2, goes low, a latch, RAE (U49-9), is set. The delay line input goes low. A negative step moves down the delay line. When it reaches the second tap, it resets the latch at the input end, and the delay line input rises. A positive step moves down the delay line. The fall of the next PHASE 2 starts another cycle.

The delay line determines the specific durations of various features of a cycle. The timing of a typical read cycle is shown in Fig. 5-1.

Fig. 5-1 Timing of Typical Read Cycle

.

5-4

1

))

5

## 5.3.3 Types of Memory Cycles

There are four types of memory module cycles: NULL, READ, WRITE, and REFRESH.

Within the delay line all are identical. At the fall of PHASE 2, the state machine (part of the Bus Interface and Control logic (7)) considers its inputs and sets two outputs to new values. These two outputs, REFR and REN, partially determine the type of cycle. Later, two more outputs, WE and PEND, are set, completely determining the type of cycle.

#### Null Cycle

A Null cycle is distinguished by REN (Row Enable) low. RAS and CAS do not occur. RAE (Row Address Enable) occurs but has no consequence. None of the memory ICs in the memory array do anything during a Null cycle.

## Read Cycle

(Refer to Fig. 5-1, Timing of A Typical Read Cycle.)

A Read cycle is distinguished by REN high,  $\overline{WE}$  high, and REFR low. Just after PHASE 2 falls, REN occurs, enabling the three RAS drivers (4), and RAE rises causing the address multiplexers to present the row address to memory. RAC occurs, clocking the selected page into the RAS drivers. RAS occurs at the selected page of memory. ICs in that page of memory store the row address.

CAE rises; the address multiplexers present the column address to the memory ICs. Soon CAS occurs. The memory ICs selected by RAS now store the column address, and set a bit to indicate that this is a read cycle. Then they get the data from the indicated address, and present it at their output pins. There is some variation among memory types in the details of how and when the outputs are enabled and the data is valid, but the output must be valid and enabled at the rise of DOC (Data Output Clock).

At the end of the read cycle, REN is removed, ending  $\overline{RAS}$ . The output data is clocked to the output register (3) at the rise of DOC. This data will be enabled to the DI bus if  $\overline{BSEL}$ ,  $\overline{ESEL}$  and  $\overline{MSEL}$  are all low, and SMEMR and PDBIN are both high.  $\overline{CAS}$  rises at the fall of PHASE 2 with the start of the next cycle.

Three ROM outputs (1 from each of three ROMs) in the Page Select Array (12) are connected together to form BSEL (Board Select). BSEL will be low if any page on the memory module is selected. ESEL (Extended Select), produced by the Extended Selection Logic (8), and MSEL produced by the Bus Interface and Control Logic, must also be low during a Read; SMEMR and PDBIN (both from a requesting processor on the S-100 bus) are both high. These are all used by the Bus Interface and Control Logic (7). The output EDO will be low enabling the tri-state outputs of the memory data output latch (3) to drive the DI Bus completing the Read operation when the board is selected.

In the above cycles, memory ICs in the array, but not in the selected page, execute CAS-only cycles. Nothing of consequence happens in the memory module during these CAS-only cycles, but some types of memory ICs require these CAS-only cycles as part of their data output enabling scheme.

### Write Cycle

A Write cycle is distinguished by REN high, REFR low and  $\overline{\text{WE}}$  low. Shortly after PHASE 2 falls, REN occurs enabling the four RAS drivers (4), and RAE rises, causing the address multiplexers to present the row address to memory, and clocking the data to be written into the Write Data Register (1). Next RAC occurs (U50-14), clocking the selected page into the RAS drivers. RAS occurs at the selected page of memory. ICs in that page of memory store the Row Address. Next, CAE rises, the Address Multiplexers (5) present the column address to the memory ICs. WE goes low, indicating a write cycle. Soon CAS occurs. The memory ICs selected by RAS now store the column address, a bit to indicate that this is a write cycle, and the data to be written from the Data In pins. At the end of the cycle, RAS and WE are removed. Before the

removal of  $\overline{CAS}$ , some data, not necessarily that just stored, is set into the output latch (3). This is not valid data and is not read because it does not get enabled onto the DI bus, since PDBIN is low at U36 keeping  $\overline{EDO}$  high.  $\overline{CAS}$  rises at the fall of PHASE 2 which starts the next cycle.

# Refresh Cycle

A Refresh cycle is distinguished by the state machine in the Bus Interface and Control Logic (7) outputs, WE, REN and REFR high. REFR causes the Address Multiplexer (5) to present the address supplied by the Refresh Counter (10) to the memory ICs. REN occurs, enabling the four RAS drivers. RAC occurs, clocking the page number into the RAS drivers.

RAS occurs at the selected page of memory. ICs in that page of memory store the refresh address as the row address, and in doing what they would normally do with it during a read, they refresh an entire row of memory within the active page.

CAE occurs. This is of no consequence.  $\overline{CAS}$  does not occur. At the end of the cycle, REN goes low, removing  $\overline{RAS}$ . At the fall of PHASE 2 in the next cycle, REFR goes low, causing the refresh Counter (10) to count 1 and returning the Address Multiplexer outputs to the S-100 bus based row address.

# 5.4 OPERATIONS: The State Machine (7)

An operation is one or more cycles which are designed to achieve a desired result. An operation of the memory module is in response to a request from some other S-100 device. The memory module performs six types of operations: SELECTED READ, SELECTED WRITE, UNSELECTED READ and UNSELECTED WRITE, SELECTED DEPOSIT and UNSELECTED DE-POSIT. Figure 5-2, Sequences of the Operation Request Logic, shows a typical sequence of states for each of the six operation types.

# 5.4.1 Variations of the Six Operations

Each of these operations has many variations consisting of different sequences of possible states of the state machine. The state machine consists of an 8-input, 4-output ROM (U56) and four clocked latches. These variations are caused by two variables:

- 1. The presence of T4, T5 and Tw cycles.

- 2. The need for refresh.

Operation request and sequencing is controlled by a state machine. Table 5-1, Sequences of the Operation of the State Machine, shows the possible states of this state machine expressed in terms of the ROM inputs and outputs. The state machine changes its outputs REFR and REN at the fall of PHASE 2. It changes its output  $\overline{WE}$  at the fall of REN. It changes its output PEND at the rise of  $\overline{RAC}$ .

Each of the 14 possible states are variations of one of the four types of memory cycles: Null, Write, Refresh and Read. (Refer to 5.3.3, Types of Memory Cycles.)

D

\* Operations are marked with an asterisk.

# Fig. 5-2. Sequences of the Operation Request Logic

Ţ

Æ

r

48KRA-1

|                                   |         |           | CONDITIONS TO ENTER CYCLE |      |        |        |         | CLE   | OUTPUT D<br>LATCHI<br>DURING C |        |     | CHE    | D      | HEXA.<br>OUT |        |        |

|-----------------------------------|---------|-----------|---------------------------|------|--------|--------|---------|-------|--------------------------------|--------|-----|--------|--------|--------------|--------|--------|

| CYCLE                             |         | STATE     | BSEL                      | MSEL | SWO    | WRR    | PEND    | PSYNC | DEP                            | RFRQ   |     | DPEND  | DWE    | DREN         | DREFR  |        |

| READ                              | 1       | READ      | -                         | -    | -      | х      | х       | 1     | х                              | x      |     | -      | 0      | 1            | 0      | -      |

|                                   | 1P      |           | Х                         | -    | 1      | Х      | х       | 1     | х                              | х      |     | 0      | 0      | 1            | 0      | 2      |

| READ                              | 2<br>2P | UWP READ  | -<br>1                    | -    | -<br>0 | X<br>X | X<br>X  | 1     | X<br>X                         | X<br>X |     | -<br>0 | 0<br>0 | 1<br>1       | 0<br>0 | -<br>2 |

| READ                              | 3<br>3P | SWP READ  | -<br>0                    | -    | -<br>0 | X<br>X | X<br>X  | 1     | X<br>X                         | X<br>X |     | -<br>1 | 0<br>0 | 1<br>1       | 0<br>0 | -<br>A |

| NULL                              | 4       | SWP NULL  | 0                         | 0    | 0      | 1      | 1       | 0     | 0                              | 0      |     | 1      | 0      | 0            | 0      | 8      |

| REFRESH                           | 5       | SWP REFR  | 0                         | 0    | 0      | 1      | 1       | 0     | 0                              | 1      |     | 1      | 0      | 1            | 1      | В      |

| NULL                              | 6       | UWP NULL  | A                         | Α    | 0      | 1      | 1       | 0     | 0                              | 0      |     | 0      | 0      | 0            | 0      | 0      |

| REFRESH                           | 7       | UWP REFR  | A                         | Α    | 0      | 1      | 1       | 0     | 0                              | 1      |     | 0      | 0      | 1            | 1      | 3      |

| WRITE                             | 8       | SW WRITE  | 0                         | 0    | 0      | 0      | 1       | 0     | 0                              | х      |     | 0      | 1      | 1            | 0      | 6      |

| READ                              | 9       | UW READ   | A                         | Α    | 0      | 0      | 1       | 0     | 0                              | Х      |     | 0      | 0      | 1            | 0      | 2      |

| NULL                              | 10      | NULL      | x                         | Х    | х      | Х      | 0       | 0     | 0                              | 0      |     | 0      | 0      | 0            | 0      | 0      |

| REFRESH                           | 11      | REFRESH   | x                         | Х    | х      | Х      | 0       | 0     | 0                              | 1      |     | 0      | 0      | 1            | 1      | 3      |

| WRITE                             | 12      | DEP WRITE | 0                         | 0    | х      | 1      | 0       | 0     | 1                              | х      |     | 1      | 1      | 1            | 0      | E      |

| READ                              | 13      | DEP READ  | 0                         | 0    | х      | 1      | 1       | 0     | 1                              | х      |     | 0      | 0      | 1            | 0      | 2      |

| READ                              | 14      | UDEP READ | A                         | Α    | х      | 1      | x       | 0     | 1                              | х      |     | 0      | 0      | 1            | 0      | 2      |

| TIME FROM FALL OF<br>PHASE 2 (ns) |         | 170-0     | 170-126                   | 0-85 | 350    | 150    | 170-300 | 350   | 350                            |        | 150 | 100    | 0      | 0            |        |        |

1 = SIGNAL HIGH

0 = SIGNAL LOW

A = EITHER/BOTH A's HIGH

X = DON'T CARE

- = NOT READY YET

ł

٩

1

5-8

# 5.5 REQUESTS FOR MEMORY OPERATIONS

Three requests are possible:

1. Normal access SYNC high, MESEL, BSEL, ESEL, all low.

Normal access has higher priority than Deposit. They will not normally occur at the same time.

| 2. Deposit | DEP high, SYNC low. | . MSEL, BSEL, ESEL, all low. |

|------------|---------------------|------------------------------|

|------------|---------------------|------------------------------|

3. *Refresh request* REFR low.

Refresh request has low priority. It will cause a refresh if both the other requests are absent.

# 5.5.1 Normal Access, Selected

Normal access, selected, and SWO high cause a Read state followed by a Refresh state or a Null state.

Normal access, selected, and  $\overline{SWO}$  low cause a WP READ followed by a Selected Write, followed by a Refresh or a Null state.

Normal access, unselected, and SWO high cause a read state followed by a Refresh state or a Null state.

Normal access, unselected, and SWO low cause a UW (Unselected Write) Read state followed by a Refresh state or a Null state.

## 5.5.2 Deposit

# Description

Deposit results from the use of the front panel Deposit switch while the system is in a continuous train of Tw states usually showing showing a fetch status. The deposit pulse (MWRITE and *not* PWR) is several T-cycles long. The first of these results in a Dep Write, the second results in a Dep Read so that the data just written will appear on the DI bus and the front panel data lights. The third will be a Null or a Refresh state. This sequence of three states will happen repeatedly. Eventually MWRITE will go away, causing a return to the normal Default or Refresh condition.

# Front Panels Which Use Deposit

The memory module is intended to perform deposits for front panels or similar devices which meet the following description.

S-100 front panels normally have a run-stop switch which stops the processor in an indefinite series of Tw states, showing a fetch status. When switched to stop, PHASE 1 and PHASE 2 clocks continue to be present. All other bus signals are stationary. Lights normally display the 16 address bits and the eight DO bits.

The address may be changed by operating a switch called EXAMINE. This causes the processor to resume operation for three cycles by forcing the DI lines to correspond to the command JUMP; the front panel tricks the processor into believing that the fetch which was being held incomplete by Tw states was really a JUMP. The processor now reads two consecutive bytes which the front panel supplies from its address switches. Next the processor places these two bytes on the address bus and starts another fetch (from that address.) The front panel stops this fetch with another indefinite series of Tw states. The addressed memory location puts the requested data on the DI bus. The front panel displays the new address (which corresponds to its switches) and the new data.

## How the Memory Module Produces Deposit

(Refer to Fig. 5-3, States of the Synchronous Counter Producing DEPOSIT.)

To produce front panel deposit, the memory module uses a synchronous counter (U47). If MWRITE is present and PWR is absent, the counter produces a signal called DEP. DEP changes at about 350 ns after the trailing edge of PHASE 2. It will be high for two periods and low for one. This pattern will repeat until DEPOSIT is removed.

The first period of DEP (count of E) produces a write cycle (DEP WRITE).

The second period of DEP (count of F) produces a read cycle (DEP READ).

The third period, DEP low (count of Ø), produces a Refresh if one is requested.

## **Requirements for the Signal DEPOSIT**

DEPOSIT must produce MWRITE. DEPOSIT must not produce PWR. If synchronous, DEPOSIT must be stable at the clock 350 ns after the falling edge of PHASE 2. If asynchronous, DE-POSIT must be longer than one PHASE 2 period.

There is no upper limit to the length of DEPOSIT. DEPOSIT is typically not synchronous to the clocks and is of varying length. The memory module synchronizes Deposit and assures that a long DEPOSIT pulse does not prevent timely refresh. No part of the system may produce MWRITE without PWR unless a deposit sequence is an acceptable result. (DMA DEVICES should produce PWR).

WR is the processor's write strobe. PWR is WR applied to the S-100 bus. A DEPOSIT switch on the front panel produces a pulse which requests the contents of the DO lines (the contents of the front panel data switches) to be written to the memory location indicated by the address lines.

The DEPOSIT pulse is normally ORed with PWR to produce MWRITE which is the write strobe used by memory.

The memory module is expected to do the indicated storage in response to MWRITE. It is also expected to place the stored result on the DI bus so that it may appear on the front panel data lights confirming the results to the operator. With most dynamic RAMs this requires a read cycle after the write cycle; thus the memory board must distinguish between MWRITE due to  $\overline{PWR}$  (normal processor write) and MWRITE due to Deposit.

## 5.5.3 Refresh

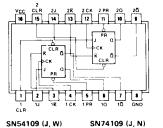

The refresh request counter (of the Bus Interface and Control Logic (7)) is a 74LS163 (U44). It counts PHASE 2 cycles. The terminal carry is used to produce RFRQ (Refresh Request) which is used by the state machine to request a refresh. REFR goes high when the refresh actually occurs. The clock at the end of terminal carry loads the counter to the complement of the required count. This preset number is established by the manufacturing optional configuration module (9) which varies with the memory ICs used.

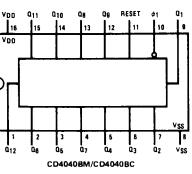

A CMOS 4040 provides a 9-bit Refresh Counter (10) (U43) which counts on the trailing edge of Refresh. The low order six outputs, R0-R5, deliver a refresh row address to the Address Multiplexer. R6 is optionally used for row or column address or page selection. R7 is used for page selection; R8 is used optionally for page selection. Their use depends upon the requirements of the memory ICs used. This selection is established by the optional configuration module (A1).

IF IN LOAD ZONE, STATE ON NEXT CLOCK WILL BE:

IF MWRITE HIGH

1

IF MWRITE LOW

| ١F | PWR HIGH | IF PWR LOW |

|----|----------|------------|

|    | E        | Ø          |

|    | 6        | v          |

If E, then F, then Ø. Or, if  $\overline{PWR}$ , then Ø. MWRITE •  $\overline{\overline{PWR}}$  produces two periods of DEP followed by one period of  $\overline{DEP}$ .

# Fig. 5-3. States of the Synchronous Counter Producing DEPOSIT.

# 5.6 EXTENDED ADDRESSING

# 5.6.1 Types of Extended Addressing

The 8080 and most other microprocessors used in S-100 bus systems are able to address a memory space of 2 to the 16th power addresses (about 65 thousand). There are a number of methods in use or proposed which extend the memory addressing capability beyond 2 to the 16th. This is often described as "bank selection."

The 48KRA-1 memory module is equipped with optional circuitry which will accommodate many different extended addressing methods. Once the details of the particular method are known, it is implemented by installing wires, ICs, and component carriers in the empty locations at the lower right corner of the board. This circuitry is referred to as Extended Selection Logic (8) in the block diagram, Fig. 7-1. Extended addressing methods which can be supported by the memory module can be classified by the methods by which the extended address is supplied to the memory board:

1) The extended address is supplied on a group of S-100 lines assigned to this purpose.

A. The extended address is "encoded," i.e., it consists of a number less than  $2^n$  represented by the  $2^n$  combinations of the n signals.

B. The extended address is "decoded," i.e., it consists of a number less than or equal to n, represented by an "active" signal on one or none of the n lines.

2) The extended address is supplied to the memory module by an OUT instruction which addresses the selected memory module as an output port. The address arrives at the memory board via the data bus (DO).

A. Encoded (as in example 1).

B. Decoded (as in example 1).

3) The extended address is supplied to the memory module on the data bus (DO) during SYNC. It is to be captured and latched by the memory module from the computer's DO lines in the same way that Status is captured and latched by the CPU from the processor's Data lines.

- A. Encoded (as in example 1).

- B. Decoded (as in example 1).

The memory module can be configured to respond to any of these three classes of extended addresses. Whatever the method used, the extended address is examined by the circuit and reduced to a single signal, <u>ESEL</u> which enables the memory module if low, and disables it if high. <u>ESEL</u> is not the same as <u>PHANTOM</u>. The two are independent of one another.

## 5.6.2 Circuit Operation of the Extended Selection Logic

This circuit examines a group of signals in one of a large number of configurations, and condenses the signals into one single yes or no signal, ESEL. Because of its convergent nature it is easier to understand if it is examined from output to input, contrary to the usual practice. ESEL is the essential product of this process. If ESEL is low, the memory module will be selected and will respond as expected of a normal memory module. If ESEL is high, the memory module will not respond to either memory read or memory write signal sequences on the S-100 bus. It will, however, continue to refresh itself and maintain its contents. It will be ready for use when selected again.

# 5.6.3 Modification Guidelines for Extended Selection Logic

(Refer to Fig. 7-4, 48KRA-1 Assembly, for references to Areas A through D and lettered jumper pads.)

## How to Produce ESEL

In the standard memory module  $\overrightarrow{ESEL}$  is driven by an inverter (U55-6). The input of the inverter (U55-5) is held at +5 V by R9. The output holds  $\overrightarrow{ESEL}$  low and the module is always enabled. Several simple two-bank and one of n-bank schemes can be implemented using this inverter and the option pads at its input and output. If the inverter input is to be wired to an S-100 line, R9 should be removed to avoid loading the S-100 line unnecessarily.

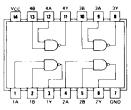

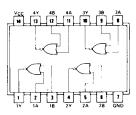

For most extended addressing methods you will need to cut the trace between ESEL and U55-6 (Area B, pads 2 and 3) and install a jumper connecting ESEL to U65-9, 10, 11 or 12, (Area C, pads 1, 2, 3 and 4) and install a device in socket U65. (Refer to Areas B and C on the 48KRA-1 Assembly, Fig. 7-4.) For most methods the device installed in U65 will be a programmed PROM. For some simple methods, a component carrier with wire jumpers may suffice. U65 will normally be a 74S287 or 74S387. These are fusible link programmable read only memories. They have eight inputs, two disables, and four outputs. Each output can be programmed (permanently) to produce any function of eight input variables, controlled on an on-or-off basis by two more variables, the disables. Only one output will normally be needed. The other three can be left unprogrammed for later use, or can be programmed with alternate patterns to minimize the number of varieties of ROMs needed. The desired pattern is selected by the output jumper connecting U65, pads 9, 10, 11 or 12 to ESEL (Areas B and C).

The 74S287 has 3-state outputs. The 74S387 has open collector outputs. If a pullup resistor is needed, install a jumper between  $\overline{\text{ESEL}}$  and R9 near U55. (Refer to the 48KRA-1 Assembly, Fig. 7-4, Area B, pins 1 to 2.)

### Wiring the Address Inputs to U65

The eight inputs of U65 must receive the extended address. These may be connected in one of several ways:

1. From an octal latch (74LS374) installed in U67, via jumpers on a component carrier installed in U66.

2. From the "Extended Address," a set of eight S-100 lines via jumpers on a component carrier installed in U64.

3. Via wire jumpers from any other points which may be appropriate.

4. Any combination of the above.

The octal latch, if used, takes its data from the DO Bus at the rising edge of its clock, XADC (Extended Address Clock). XADC is jumper-optioned to nine sources at the lower right corner of the board. (Refer to the assembly drawing, Fig. 7-4, Area D.) The first option is to the signal PSYNC • PHASE 2. If this option is used, extended address will be captured from the S-100 DO Bus just after the PHASE 2 fall during PSYNC. How the extended address gets put on the DO Bus at this time is a problem which must be solved externally to the memory module.

The remaining eight options are the eight outputs of a 74LS138 which may be installed at U68. If one of these eight is chosen, the extended address will be latched from the DO Bus at the leading (falling) edge of  $\overrightarrow{PWR}$  during an OUTPUT operation to the selected port. The port number (eight bits, PØ - P7) is specified as follows:

| PORT BIT                         | FROM S-100 BIT                        | SPECIFIED BY                                         |

|----------------------------------|---------------------------------------|------------------------------------------------------|

| PØ                               | A8 )                                  |                                                      |

| P1                               | A9 }                                  | Selection of one of eight options at U65 outputs.    |

| P2                               | A10)                                  |                                                      |

| P3                               | A11                                   | Selection of All or All to U68-5 by jumper. (Area B) |

| P4                               | A12)                                  |                                                      |

| P5                               | A13                                   | Decoded at U40 Pin 10 by program in PROM.            |

| P6                               | A14 (                                 |                                                      |

| P7                               | A15)                                  |                                                      |

| P1<br>P2<br>P3<br>P4<br>P5<br>P6 | A9<br>A10<br>A11<br>A12<br>A13<br>A14 | Selection of All or All to U68-5 by jumper. (Area B) |

# Modifying U40

A PROM is required in U40 to decode the high order four bits of the port address. The memory module may be manufactured containing PROMs at U40 inappropriate to this use. You may, therefore, need to substitute a different PROM at U40-10.

Notice that the octal latch used, a 74LS374, is specified by most suppliers to sink 24 mA. This IC is suitable for use as an S-100 bus driver. Thus, one memory module equipped with the latch may be wired to drive the S-100 "Extended Address" bus of up to eight wires, and serve as the memory controller for other memory boards. It also may be used as an output port for any other purpose if not needed for extended addressing.

# **Disable Inputs to U65**

The PROM which generates ESEL, has two DISABLE inputs. One of these is driven by PROM U40-9. The other by U39-9. These two PROMS can be programmed so that response by the memory module can be controlled by any one function of S-100 addresses A12-A15 and switches S2, sections 1, 2, 3, 4 and also by any one function of S-100 addresses A12-A15 and switches S2, sections 5, 6, 7 and 8.

In implementing extended addressing, you may need PROMs for U39 and U40 other than those found on a stock memory module.

These disable controls are provided so that extended address selection can be governed in block sizes down to 4K, selectable by manual switch.

The DISABLE inputs of U65 (Pins 13 and 14) can be jumpered to ØV (enabled) and the lines from U39-11 and U40-11 can be jumpered to the A6 and A7 inputs for a more versatile control with only six extended address bits.

# Timing of ESEL

The eight inputs and two disables of U65 may be driven by virtually any signals which meet certain timing requirements. ESEL must not change while it is being used by the memory module. The rules describing the ESEL timing constraints are summarized as follows:

- 1. ESEL may change at the falling edge of PHASE 2 during PSYNC.

- 2. ESEL may change at the falling edge of PWR when SOUT is high.

- 3. ESEL may change at any time that the S-100 Address may change.

# 5.7 MODIFICATION FOR 16-BIT DATA WORDS

(Refer to Fig. 7-4, 48KRA-1 Assembly, for lettered option areas.)

Option Area A provides pads which may be useful in S-100 systems which extend or alter the normal data configuration.

The original S-100 configuration provided a DI bus (DATA IN to the CPU) and a DO bus (DATA OUT from the CPU), both eight bits. These are tied together into a single 8-bit data bus in the Sol. The memory module can be modified to provide bits 8-15 so that two memory modules provide 16-bit wide memory for S-100 bus systems. This can be done by defining an additional set of eight lines to be DATA 8-15, and jumpering the memory module's input and output lines

î

5-14

together to these pins in Area A and cutting the connections to the DO and DI S-100 pins.

12

2

Alternately it can be done by re-defining the DO and DI sets as D0-7 and D8-15 and making the appropriate cuts and jumpers.

For systems which wish to mix 16-bit and 8-bit memory or input/output devices, the signals SXTRQ (Sixteen Request), S-100 pin 59, and SXTN (Sixteen Acknowledge), S-100 pin 61 may be provided by adding jumpers AB and CD. (Refer to Fig. 7-4, 48KRA-1 Assembly.) Note that these pin assignments are in conflict with the DATA 8-15 assignments.

# Table 5-2. S-100 Bus Signals of the 48KRA-1 Memory Module

| SIGNAL     | PIN | SOURCE                                            | FUNCTION                                                                                                  |

|------------|-----|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| AØ-A5      | *   | Processor                                         | Row address for memory.                                                                                   |

| A7-A11     | *   | Processor                                         | Column address for memory.                                                                                |

| A6, 12, 13 | *   | Processor                                         | Row or column address depending on memory IC type.                                                        |

| A12-15     | *   | Processor                                         | Page and 4K block selection.                                                                              |

| A16-23     | *   | Processor or<br>Extended<br>Address<br>Controller | Extended address lines.                                                                                   |

| DIØ-7      | *   | Memory                                            | (Data In) Read data lines.                                                                                |

| DOØ-7      | *   | Processor                                         | (Data Out) Write data lines.                                                                              |

| D8-15      | *   | Any                                               | Extended read data lines.                                                                                 |

| MWRITE     | 68  | Computer                                          | (Memory Write) Write-strobe to memory.                                                                    |

| PDBIN      | 78  | Processor                                         | (Processor Data Bus In) Indirectly enables DI bus drivers during read.                                    |

| PHANTOM    | 67  | Computer                                          | Disables memory (optional) during power-on initialization program.                                        |

| PHASE 2    | 24  | Computer                                          | Clocks Bus Interface and Control Logic 7.                                                                 |

| PSYNC      | 76  | Processor                                         | (Processor Sync) Controls requests for memory operations.                                                 |

| PWR (      | 77  | Processor                                         | (Processor Write) High during front panel deposit. Low during processor-controlled write.                 |

| SINP       | 46  | Processor                                         | (Status Input) Disables certain operations of the Bus Interface, and Control logic $\widehat{7}$ .        |

| SMEMR      | 47  | Processor                                         | (Status Memory Read) Indirectly enables DI bus drivers $(3)$ .                                            |

| SOUT       | 45  | Processor                                         | (Status Output) Disables certain operations of the Bus<br>Interface and Control Logic.                    |

| SWO        | 97  | Processor                                         | (Status Write Out) Controls requests for read or write operations of the Bus Interface and Control Logic. |

| SXTN       | 61  | Memory                                            | (Sixteen Acknowledge) Extended data signal used in systems<br>which mix 8- and 16-bit S-100 cards.        |

| SXTRQ      | 59  | Computer                                          | (Sixteen Request) Extended data signal used in systems which mix 8- and 16-bit S-100 cards.               |

\*See Fig. 7-2 and 7-3, 48KRA Schematic, for pin number assignments.

Fi)-

.

ſ

\_

.....

(

| BSEL        | (Board Select) Input to state machine.                                                                                                                            |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CAS         | (Column Address Strobe) Drives all memory ICs, providing timing.                                                                                                  |

| DOC         | Data Output Clock) Clocks data to the output register $(3)$ .                                                                                                     |

| EDO         | (Enable Data Output)                                                                                                                                              |

| ESEL        | (Extended Select) Enable from Extended Selection Logic $(8)$ .                                                                                                    |

| MEM OUT Ø-7 | (Memory Output) lines of the memory array.                                                                                                                        |

| MSEL        | (Memory Selected) Signal of the Bus Interface and Control Logic $\overline{\mathcal{7}}$ .                                                                        |

| AØ-6 MUX    | (Multiplexed Address) Outputs of the Address Multiplexer $(5)$ .                                                                                                  |

| PEND        | (Cycle Pending) Output at the State Machine $(7)$ .                                                                                                               |

| PSEL        | (Page Select)                                                                                                                                                     |

| RAC         | (Row Address Clock) Clocks the $\overline{RAS}$ drivers $(4)$ , and the column address register $(7)$ .                                                           |

| RA DECODER  | (Refresh Address Decoder)                                                                                                                                         |

| RAE         | (Row Address Enable) when high, causes the address multiplexers $(5)$ to present the row address. Clocks the write data registerr $(1)$ .                         |

| RAS1 - RAS4 | The four Row Address Strobe lines to the four pages of memory ICs. One or none of these will be active in any one cycle, providing timing and selection to pages. |

| REFR        | (REFResh) State machine output which specifies refresh (when high).                                                                                               |

| REN         | (Row ENable) State machine output which Enables the RAS drivers.                                                                                                  |

| RFRQ        | (Refresh Request) Refresh counter output.                                                                                                                         |

| WE          | (Write Enable) Output of the state machine which specifies a write cycle (when low), a read cycle when high.                                                      |

| WRR         | (WR Reclocked) Output of the Deposit counter. This signal is produced by reclocking PWR, an S-100 bus signal.                                                     |

| XADC        | (Extended Address Clock) Signal produced by the Extended Selection Logic $(8)$ governing latching of the extended address from the DO bus.                        |

ŗ

٢

# SECTION 6

# MAINTENANCE AND DIAGNOSTICS

#### 6.1 SERVICE

Should you encounter a problem in using the memory module, first consult the manual for a possible solution. If you are still unable to solve the problem or if you have subsequent failures which you cannot service yourself, ask your dealer for help. Service on all Processor Technology equipment, in or out of warranty, is the responsibility of the selling dealer.

# 6.2 REPLACEMENT PARTS

Order replacement parts by Processor Technology part number, quantity and complete description (e.g., 6.8 ohm, 1/2 watt, 5% resistor). Your dealer may have a limited selection of replacement parts on hand. Certain standard parts may be available from electronic parts suppliers.

### 6.3 TROUBLESHOOTING AND DIAGNOSTIC TEST PROGRAMS

The "long" memory test used in Section 4, Memory Test, may be used for trouble-shooting the memory modules and for periodic testing to assure system reliability.

## **6.4 HARDWARE TROUBLESHOOTING**

Fig. 7-5, 48KRA-1 PCB traces, can be useful in signal-path tracing. This figure shows the traces on both sides of the PCB as viewed from the component side, but without the components obscuring the traces.

E)

U.

# SECTION 7

# DRAWINGS

- Fig. 7-1.48KRA-1 System Block DiagramFig. 7-2.48KRA-1 Schematic, Sheet 1Fig. 7-3.48KRA-1 Schematic, Sheet 2

- Fig. 7-4. 48KRA-1 Assembly

4

÷.

٨

ł

Fig. 7-5. 48KRA-1 PCB Traces

### Table 7-1. Key to System Block Diagram

(The encircled key numbers refer to matching numbers on Fig. 7-1, 48KRA-1 System Block Diagram. For ICs represented and other details, refer to Fig. 7-2 and 7-3, 48KRA-1 Schematic.)

.

| KEY # | NAME OF FUNCTIONAL BLOCK        | ICs REPRESENTED                      |

|-------|---------------------------------|--------------------------------------|

| 1     | Write Data Register             | U61                                  |

| 2     | Memory Array                    | U1 through 24                        |

| 3     | Output Register/Drivers         | U62, 63                              |

| 4     | RAS Drivers                     | U35, U41                             |

| 5     | Address Multiplexer             | U42, U51-U53                         |

| 6     | Page Multiplexer                | U33                                  |

| 7     | Bus Interface and Control Logic | U36 (partially)<br>U44, 46-50, 55-59 |

| 8     | Extended Selection Logic        | U60, U64-U68                         |

| 9     | Configuration Module            | A1                                   |

| 10    | Refresh Counter                 | U43                                  |

| (11)  | Refresh Page Decoder            | U36                                  |

| 12    | Page Select Array and Switches  | U34, U37 through<br>U39; S1, S2      |

| 13    | Refresh Timer                   | U44                                  |

Fig. 7-1. 48KRA-1 System Block Diagram

......

Fig. 7-3. 48KRA-1 Schematic (Sheet 2)

Fig. 7-4. 48KRA-1 Assembly (214000A)

|--|

| амроиет<br>+ + а<br>х као ч<br>х као ч<br>т ч<br>т ч<br>х као ч<br>т ч<br>т ч<br>т ч<br>т ч<br>т ч<br>т ч<br>т ч<br>т |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Copyright (C) 1978, by Processor Technology Corporation All rights reserved.

### NOTE:

Both these patterns are viewed from the component side. The component side is the screened pattern. The solid pattern is the trace side.

2, a K-1.5 Appendix 1

# LONG MEMORY TEST PROGRAM (Listing)

| 00                | 00 *             |          |          |                           |

|-------------------|------------------|----------|----------|---------------------------|

| C900 00           |                  | ORG      | 0С900Н   |                           |

| 0.0               |                  | XEQ      | 0С004н   |                           |

| 00                | 03               | LST      |          |                           |

| 00                | 04 <b>***</b> ₽  | ROCESSO  | R TECHNO | OLOGY 48KRA-1 TEST ***    |

| 0.0               | 05 <b>*</b>      |          |          |                           |

|                   | 06 <b>*</b>      | CO       | PYRIGHT  | (C) 1978, by              |

|                   | D7 *             |          |          | Technology Corporation    |

|                   | o8 <b>*</b>      |          |          | reserved.                 |

| 0.0               | 09 <b>*</b>      |          | 7        |                           |

|                   | 10 BEGIN         | EQU      | \$       | **** SETUP I/O ****       |