# ADVANTAGE Technical Manual

# TABLE OF CONTENTS

| Sec | tion       |                  |                                                                         | Page                     |

|-----|------------|------------------|-------------------------------------------------------------------------|--------------------------|

| 1   | INTE       | ODUCTIO          | N                                                                       | 1-1                      |

|     | 1.2        | System<br>Warran | this Manual<br>Description<br>ty<br>AGE Specifications                  | 1-2<br>1-3<br>1-6<br>1-7 |

| 2   | ADVA       | NTAGE O          | PERATION                                                                | 2-1                      |

|     | 2.1        | Operati          | ng Controls                                                             | 2-1                      |

|     |            | 2.1.2            | Keyboard<br>Rear Panel Controls<br>Diskette Loading/Unloading           | 2-1<br>2-4<br>2-6        |

|     | 2.2        | System           | Startup                                                                 | 2-7                      |

|     |            |                  | Standard Startup - Booting From Drive 1                                 | 2-7                      |

|     |            |                  | Alternate Startup - Booting<br>From Drive 2                             | 2-8                      |

|     |            |                  | Alternate Startup - Booting<br>From A Serial Port<br>Mini-Motor Startup | 2-8<br>2-8               |

|     | 2.3        | Restar           | ting The System                                                         | 2-9                      |

|     |            | 2.3.1            | Keyboard Reset                                                          | 2-9                      |

| 3   | IMPL       | EM ENTIN         | G ADVANTAGE FEATURES                                                    | 3-1                      |

|     | 3.1<br>3.2 |                  | rocessor Control<br>Control                                             | 3-1<br>3-1               |

|     |            |                  | Memory Mapping<br>Memory Parity                                         | 3-1<br>3-6               |

|     | 3.3        | Interr           | upts                                                                    | 3-7                      |

|     |            |                  | Maskable Interrupts<br>Non-Maskable Interrupts                          | 3-8<br>3-8               |

|     | 3.4        | Chared           | T/O Interface Pegisters                                                 | 30                       |

| Section |         |                                       | Page |

|---------|---------|---------------------------------------|------|

| 3.5.    | Keyboa  | rd Control                            | 3-16 |

|         | 3.5.1   | Keyboard Reset Enable                 | 3-16 |

|         | 3.5.2   | Reset                                 | 3-17 |

|         | 3.5.3   | Interrupt or Polled                   | 3-17 |

|         | 3.5.4   |                                       | 3-19 |

|         | 3.5.5   | Character Overrun                     | 3-19 |

|         |         | Cursor Lock                           | 3-12 |

|         |         | All Caps                              | 3-21 |

|         | 3.5.8   | Auto Repeat                           | 3-21 |

| 3.6     | Video 1 | Display Control                       | 3-22 |

|         | 3.6.1   | Screen Mapping                        | 3-23 |

|         | 3.6.2   | Forming Letters and Symbols           | 3-25 |

|         | 3.6.3   | Display Flag                          | 3-27 |

|         | 3.6.4   | Screen Blanking                       | 3-27 |

|         | 3.6.5   | Video Driver                          | 3-27 |

| 3.7     | Floppy  | Disk Drive Control                    | 3-31 |

|         |         | Power-on Initialization               |      |

|         | 3.7.2   | Motor Enable                          | 3-34 |

|         | 3.7.3   | Drive Selection                       | 3-34 |

|         | 3.7.4   | Seek                                  | 3-34 |

|         | 3.7.5   | Sector Selection                      | 3-35 |

|         | 3.7.6   | Read Data                             | 3-36 |

|         | 3.7.7   | Write Data                            | 3-37 |

|         | 3.7.8   | Write Data<br>Floppy Disk Data Format | 3-39 |

| 3.8     | Hard Di | isk Drive Control                     | 3-40 |

|         | 3.8.1   | I/O Commands                          | 3-40 |

|         | 3.8.2   | Head Positioning Data Format          | 3-45 |

|         | 3.8.3   | Data Format                           | 3-47 |

|         | 3.8.4   | Format Operation                      | 3-48 |

|         |         | Read Operations                       | 3-49 |

|         | 3.8.6   | Write Operation                       | 3-50 |

| 3.9     | Accessi | ing The I/O Boards                    | 3-51 |

|         | 3.9.1   | Reset                                 | 3-51 |

|         |         | Board Identification                  | 3-51 |

|         |         | Byte Transfers                        | 3-53 |

|         |         | Interrupt                             | 3-53 |

| Section | •                                                                                                                                                                                                               | Page                                         |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 3.10    | SIO Board                                                                                                                                                                                                       | 3-54                                         |

|         | 3.10.1 Reset 3.10.2 Board Identification 3.10.3 Data Transfers 3.10.4 Control 3.10.5 Status 3.10.6 Interrupt or Polled 3.10.7 SIO In Asynchronous Mode 3.10.8 SIO In Synchronous Mode                           | 3-54<br>3-55<br>3-55<br>3-57<br>3-58<br>3-66 |

| 3.11    | PIO Board                                                                                                                                                                                                       | 3-72                                         |

|         | 3.11.1 Reset 3.11.2 Board Identification 3.11.3 Data Transfers 3.11.4 Control 3.11.5 Status 3.11.6 Interrupt or Polled 3.11.7 Programming Example                                                               | 3-72<br>3-73<br>3-73<br>3-73<br>3-74<br>3-75 |

| 3.12    | Speaker Control                                                                                                                                                                                                 | 3-77                                         |

| 3.13    | Bootstrap Firmware                                                                                                                                                                                              | 3-78                                         |

|         | 3.13.1 Startup 3.13.2 Boot From Disk Drive 3.12.3 Boot From Serial Port                                                                                                                                         | 3-78<br>3-79<br>3-82                         |

| 4 THEO  | RY OF OPERATION                                                                                                                                                                                                 | 4-1                                          |

| 4.1     | Main PC Board                                                                                                                                                                                                   | 4-1                                          |

|         | 4.1.1 Central Processor 4.1.2 Main RAM 4.1.3 Boot PROM 4.1.4 Auxiliary Processor and Keyboard 4.1.5 Floppy Disk Controller 4.1.6 Dislay RAM and Video Generator 4.1.7 I/O Board Interface 4.1.8 Speaker Circuit | 4-36<br>4-41                                 |

| A 2     | 4.1.9 Voltage Regulators  Hard Disk Controller Board                                                                                                                                                            | 4-41                                         |

| Sec | tion |                                                                                                    | Page                                      |

|-----|------|----------------------------------------------------------------------------------------------------|-------------------------------------------|

|     |      | 4.2.1 Track and Sector Format<br>4.2.2 Hard Disk Controller<br>4.2.3 Hard Disk Drive               | 4-44<br>4-44<br>4-55                      |

| 5   | PREV | ENTIVE MAINTENANCE                                                                                 | 5-1                                       |

|     | 5.2  | Wear and Damage Inspection<br>Voltage Checks and Adjustment<br>Voltage Controlled Oscillator Check | 5-2<br>5-3                                |

|     |      | and Adjustment                                                                                     | 5-4                                       |

| 6   | DIAG | NOSTICS                                                                                            | 6-1                                       |

|     |      | The Mini-Monitor<br>The General Diagnostic Programs                                                | 6-2<br>6-4                                |

|     |      | · · ·                                                                                              | 6-4<br>6-6<br>6-8<br>6-11<br>6-12<br>6-13 |

|     | 6 2  | 6.2.7 Display Monitor Test  Hard Disk Diagnostic Procedures                                        | 6-22<br>6-23                              |

|     | 0.3  | Hard Disk Diagnostic Flocedures                                                                    | 0-23                                      |

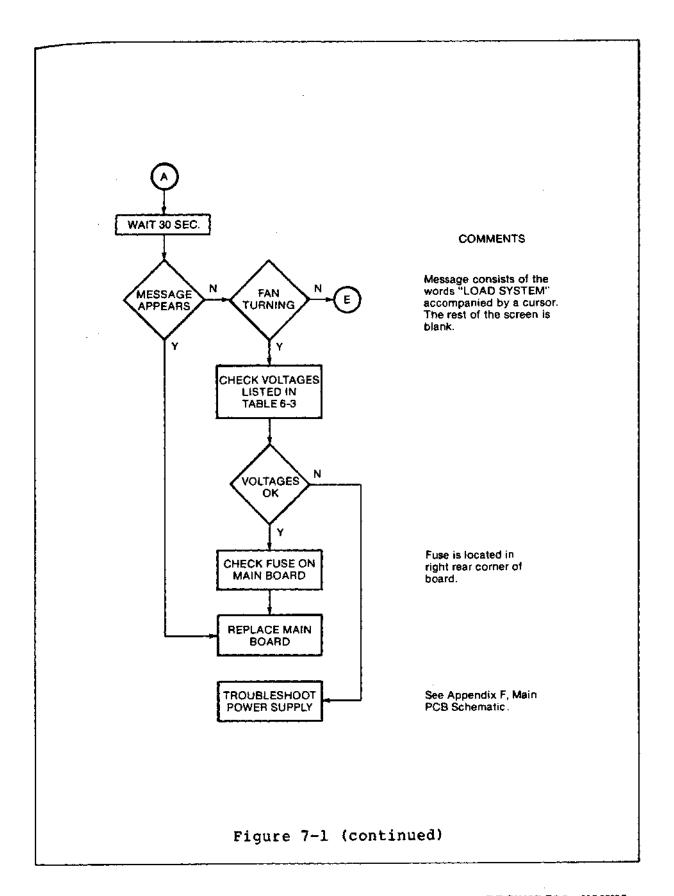

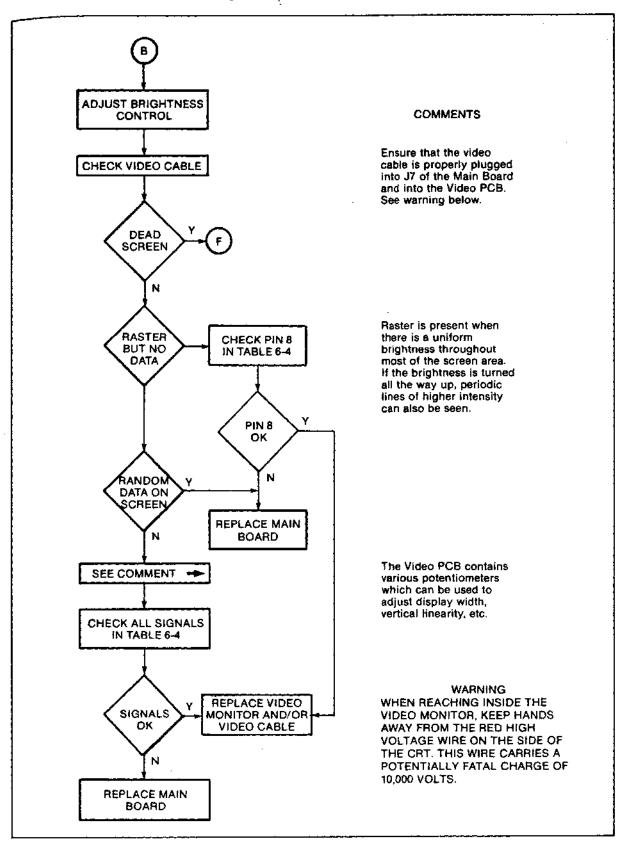

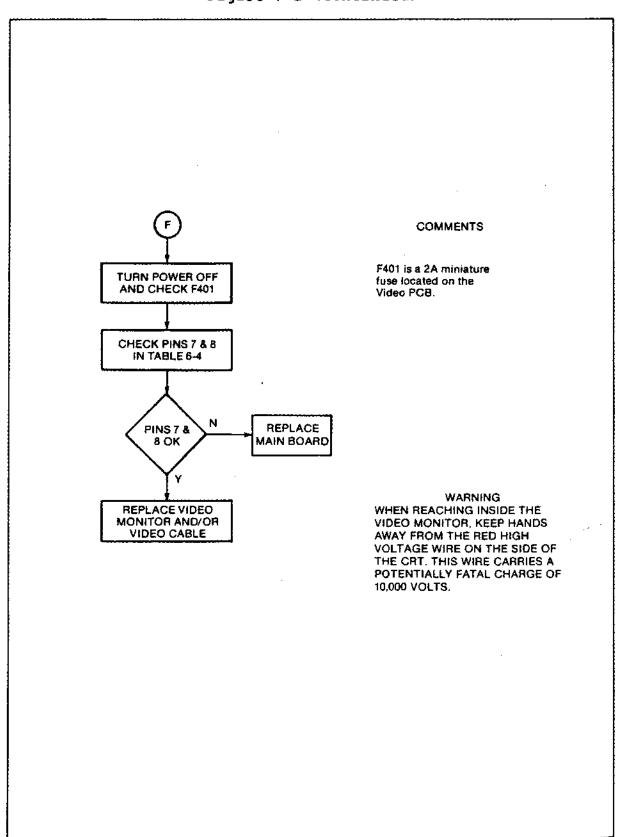

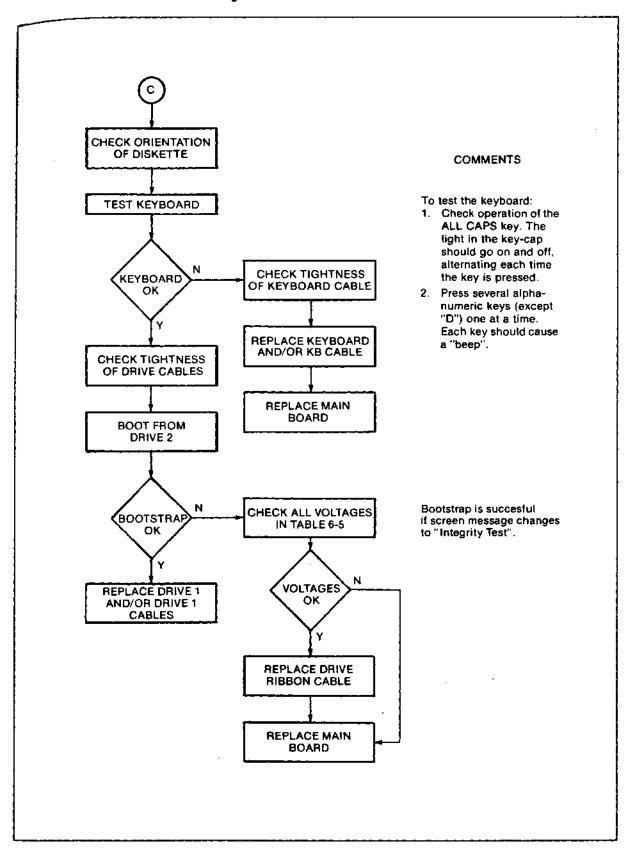

| 7   | TROU | BLESHOOTING AND REPAIR                                                                             | 7-1                                       |

|     |      | Tools and Test Equipment<br>Troubleshooting Procedures                                             | 7-1<br>7-2                                |

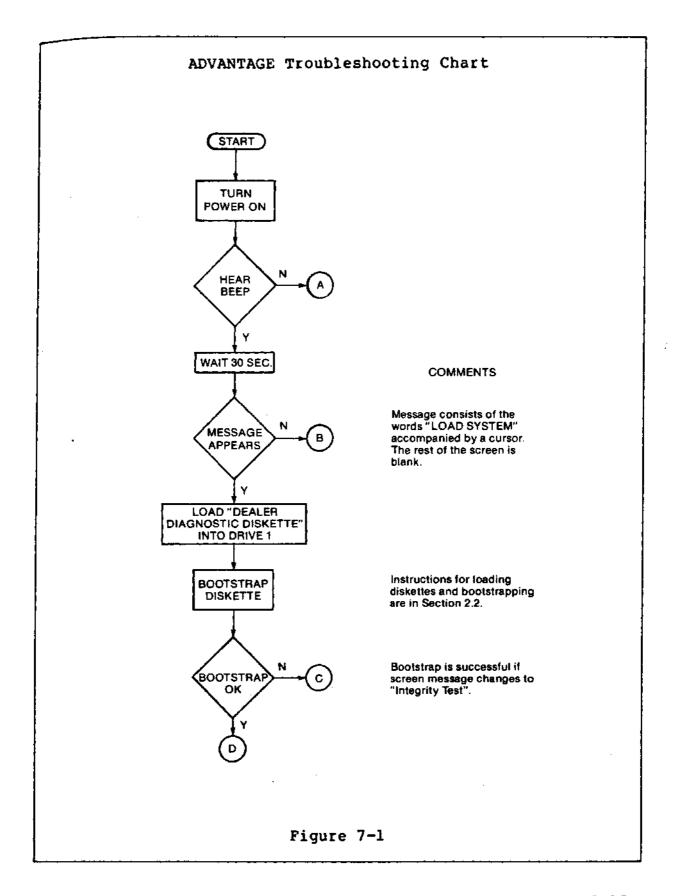

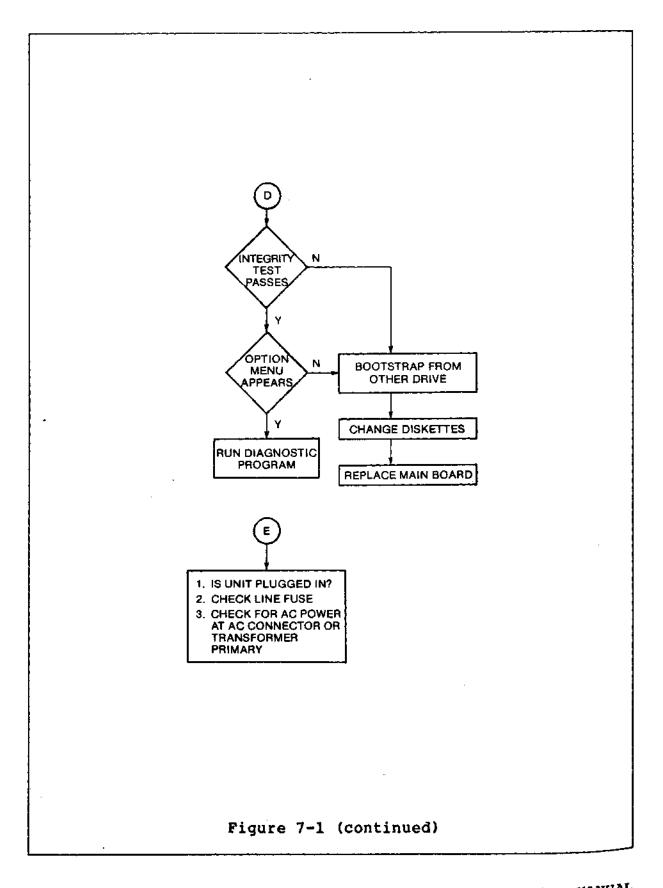

|     |      | 7.2.1 Troubleshooting Chart                                                                        | 7-2                                       |

|     | 7.3  | Assembly Replacement Procedures                                                                    | 7-15                                      |

|     |      | 7.3.1 Opening and Closing ADVANTAGE Cabinet                                                        | 7-16                                      |

|     |      | 7.3.2 Removing and Installing The Keyboard                                                         | 7-20                                      |

|     |      | 7.3.3 Removing and Installing The Main PC Board                                                    | 7-24                                      |

|     |      | 7.3.4 Removing and Installing a Disk Drive                                                         | 7-27                                      |

| Appendix |                               | Page       |

|----------|-------------------------------|------------|

| A        | CHARACTER CODE TABLES         | A-1        |

| В        | I/O ADDRESS SUMMARY           | B-1        |

| C        | PC BOARD JUMPERS              | c-1        |

| D        | ERROR MESSAGES                | D-1        |

| E        | PARTS LISTS                   | E-1        |

| F        | FULL ASSEMBLY DRAWINGS        | F-1        |

| G        | Z80 MICROPROCESSOR DATA SHEET | G-1        |

| H        | 8251 USART DATA SHEET         | H-1        |

| I        | SCHEMATICS                    | I-1        |

| J        | READER RESPONSE FORM          | <b>J-1</b> |

# ILLUSTRATIONS

| Figure     |                                             | Page       |

|------------|---------------------------------------------|------------|

| 1-1<br>1-2 | The ADVANTAGE Computer                      | 1-1<br>1-5 |

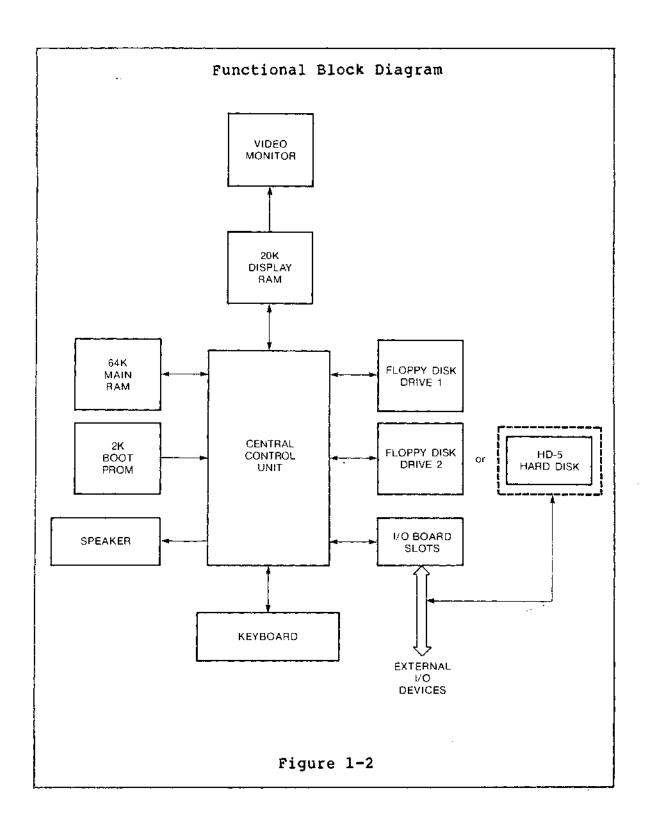

| 1-2        | Functional Block Diagram                    | 1-2        |

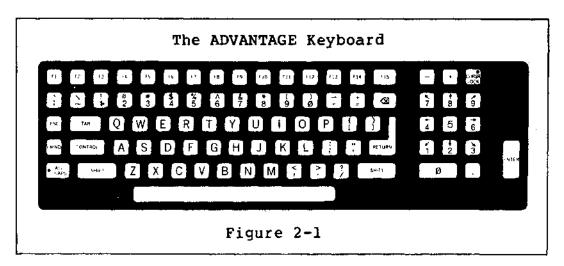

| 2-1        | The ADVANTAGE Keyboard                      | 2-1        |

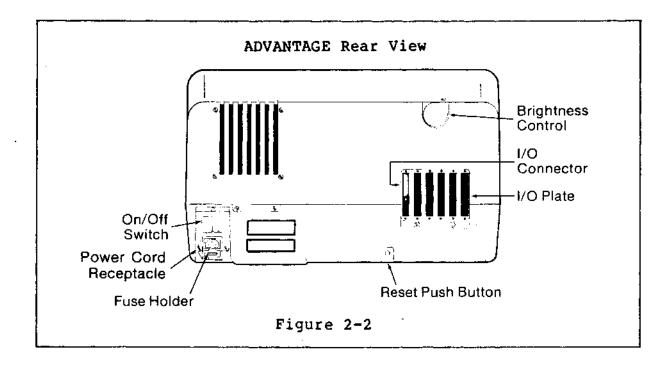

| 2-2        | ADVANTAGE Rear View                         | 2-4        |

| 2-3        | Loading a Diskette                          | 2-6        |

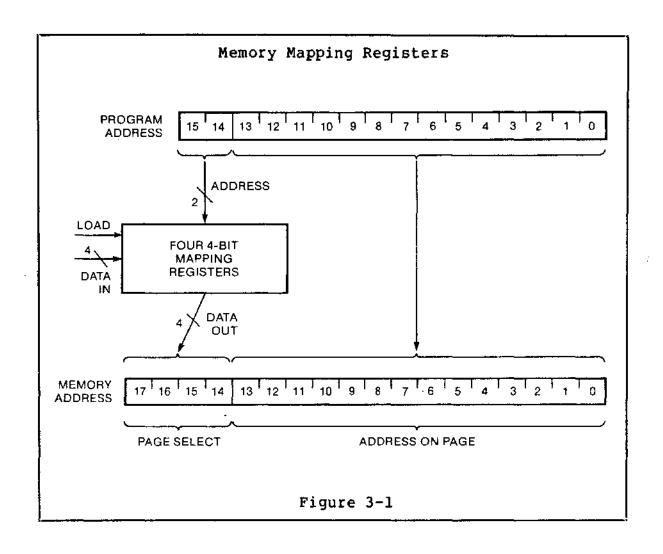

| 3-1        | Memory Mapping Registers                    | 3-3        |

| 3-2        | The Three Shared I/O Interface Registers    | 3-10       |

| 3-3        | Data Format In Display RAM                  | 3-24       |

| 3-4        | Disk Read/Write Timing                      | 3-38       |

| 3-5        | Floppy Disk Track and Sector Format         | 3-39       |

| 3-6        | Hard Disk Track and Sector Format           | 3-47       |

| 3-7        | Asynchronous Modem Configuration Header     | 3-59       |

| 3-8        | Asynchronous Terminal Configuration Header  | 3-60       |

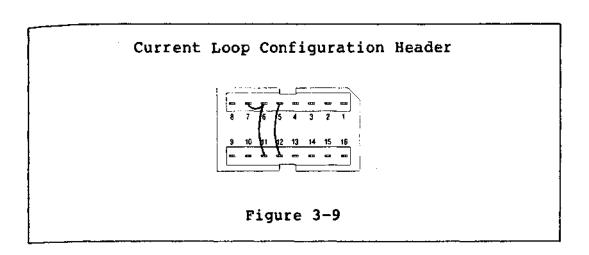

| 3-9        | Current Loop Configuration Header           | 3-61       |

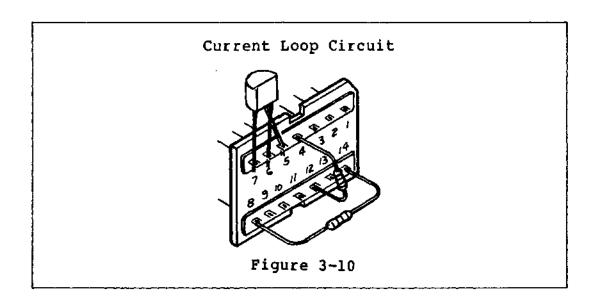

| 3-10       | Current Loop Circuit                        | 3-62       |

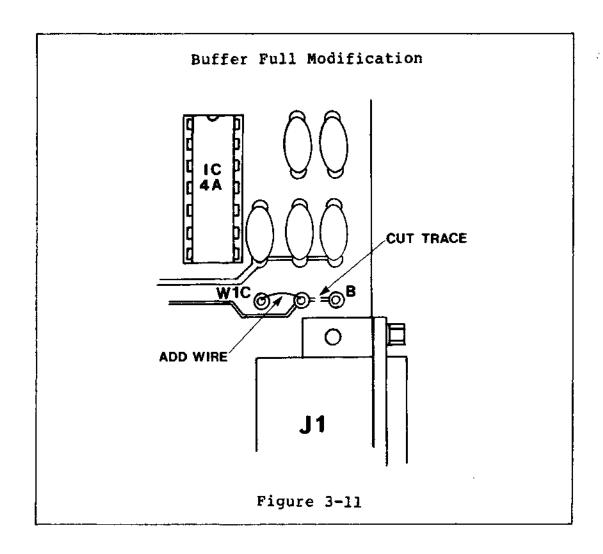

| 3-11       | Buffer Full Modification                    | 3-63       |

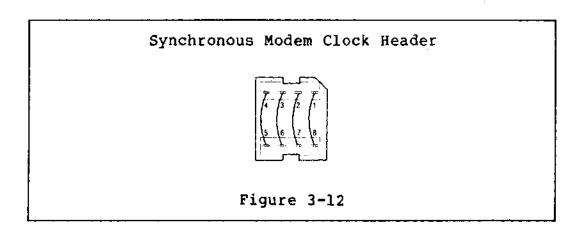

| 3-12       | Synchronous Modem Clock Header              | 3-66       |

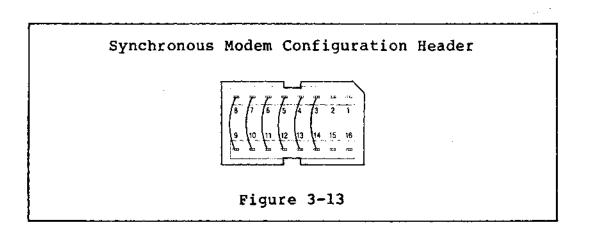

| 3-13       | Synchronous Modem Configuration Header      | 3-66       |

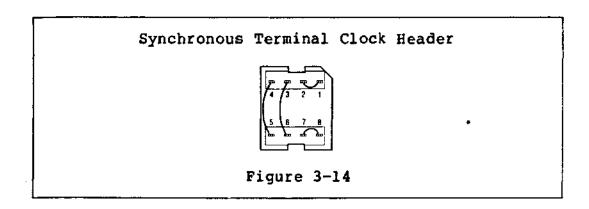

| 3-14       | Synchronous Terminal Clock Header           | 3-67       |

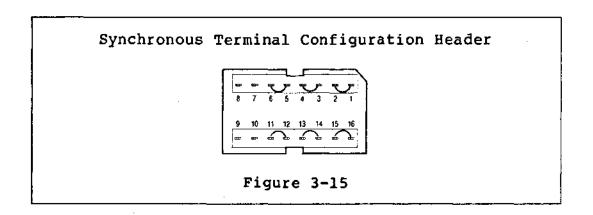

| 3-15       | Synchronous Terminal Configuration Header   | 3-67       |

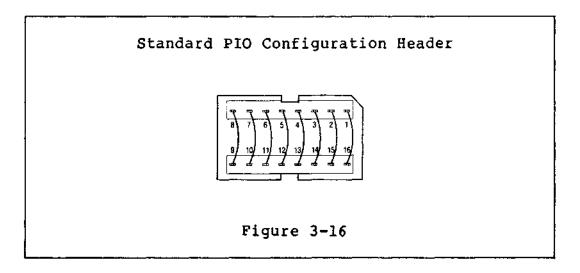

| 3-16       | Standard PIO Configuration Header           | 3-72       |

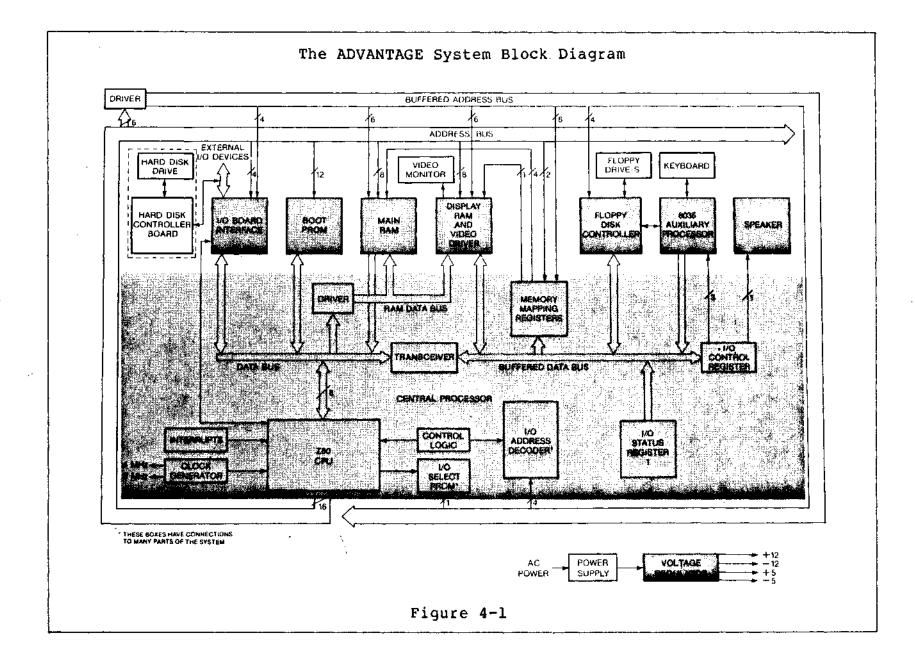

| 4-1        | The ADVANTAGE System Block Diagram          | 4-2        |

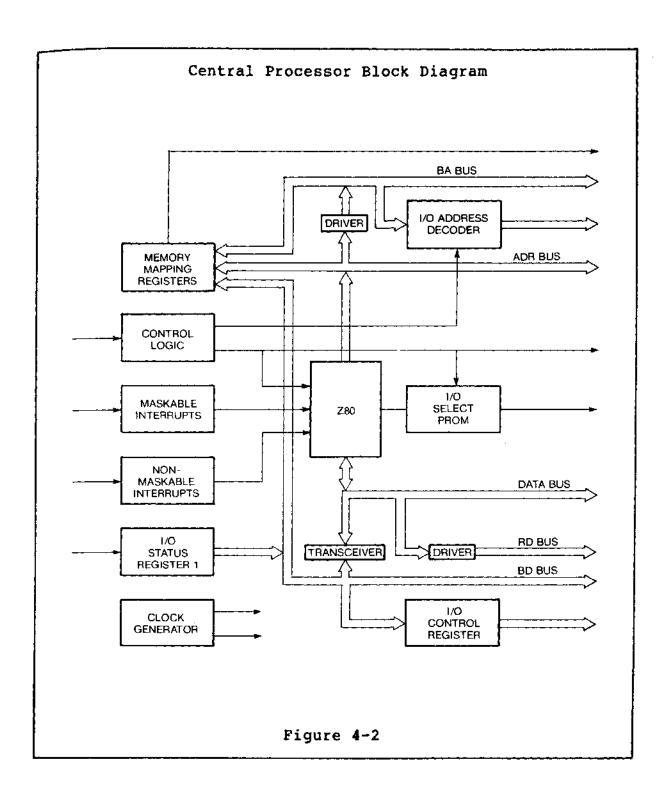

| 4-2        | Central Processor Block Diagram             | 4-5        |

| 4-3        | Main RAM Block Diagram                      | 4-15       |

| 4-4        | Main RAM Timing                             | 4-17       |

| 4-5        | Auxilliary Processor Block Diagram          | 4-19       |

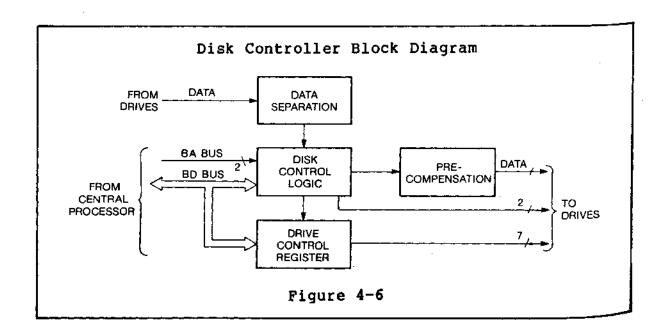

| 4-6        | Disk Controller Block Diagram               | 4-22       |

| 4-7        | Display RAM and Video Driver                | 4-26       |

| 4-8        | Horizontal Scan Timing                      | 4-31       |

| 4-9        | Vertical Scan Timing                        | 4-35       |

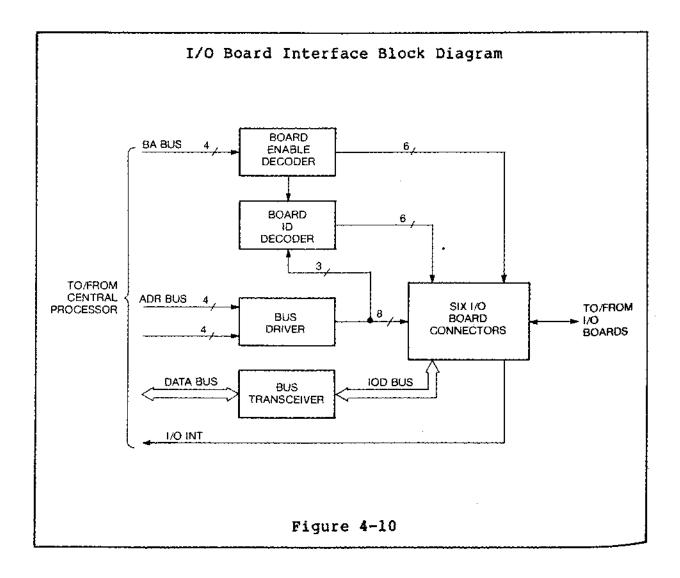

| 4-10       | I/O Board Interface Block Diagram           | 4-36       |

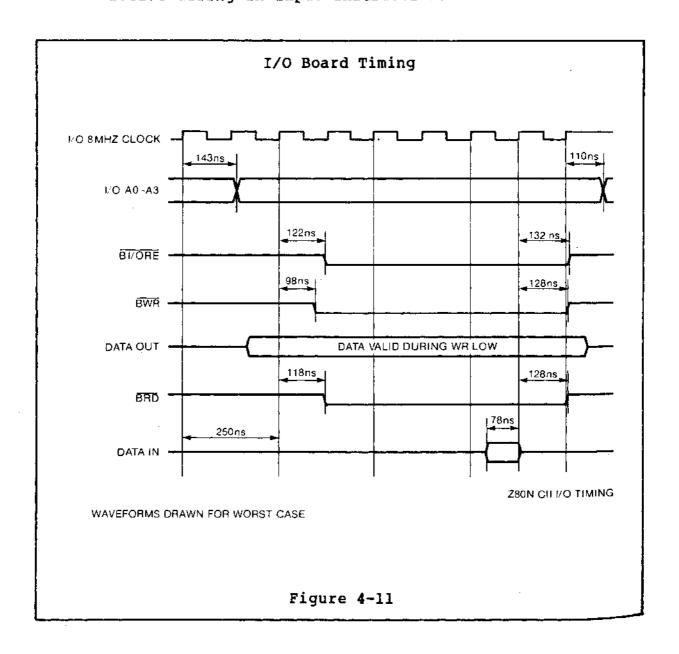

| 4-11       | I/O Board Timing                            | 4-40       |

| 4-12       | Voltage Regulators Block Diagram            | 4-42       |

| 4-13       | Hard Disk Controller Block Diagram          | 4-45       |

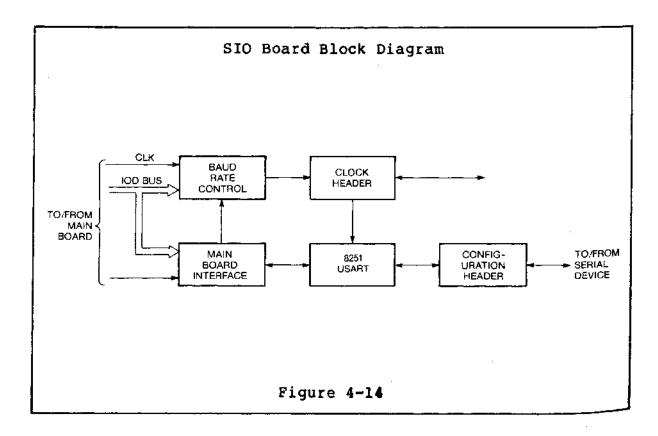

| 4-14       | SIO Board Block Diagram                     | 4-58       |

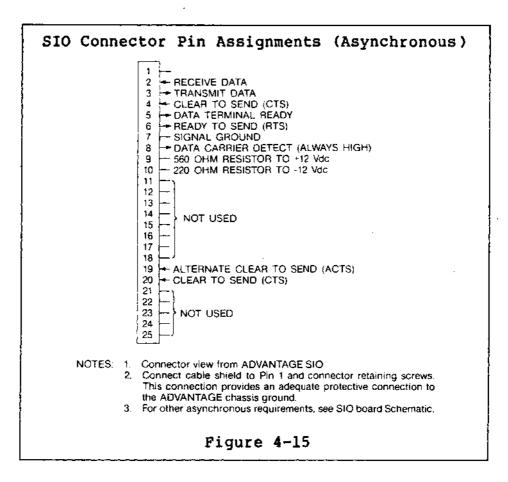

| 4-15       | Connector Pin Assignments (Asynchronous)    | 4-60       |

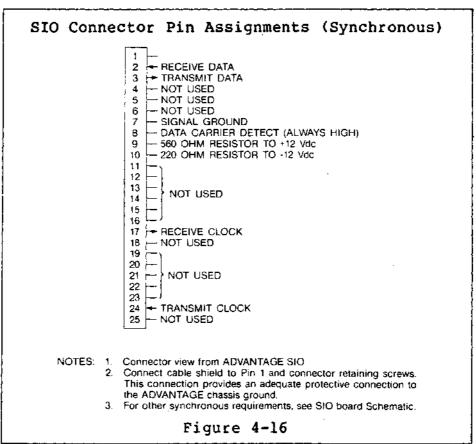

| 4-16       | SIO Connector Pin Assignments (Synchronous) | 4-60       |

| 4-17       | PIO Board Block Diagram                     | 4-63       |

| 4-18       | PIO Connector Pin Assignments               | 4-65       |

| 4-19       | Standard PIO Configuration Header           | 4-66       |

| 4-20       | PIO Port Timing                             | 4-68       |

# ILLUSTRATIONS (continued)

| rigure |                                             | Page |

|--------|---------------------------------------------|------|

| 6-1    | Single Block Mode - Display Format          | 6-5  |

| 6-2    | Floppy Disk Subsystem Test - Display Format | 6-7  |

| 6-3    | Executable Memory Test - Display Format     | 6-9  |

| 6-4    | Locating a Defective Main RAM Chip          | 6-10 |

| 6-5    | Loacating a Defective Video RAM Chip        | 6-11 |

| 6-6    | SIO Board Test - Display Format             | 6-12 |

| 6-7    | Keyboard Test Modules and Sections          | 6-14 |

| 6-8    | N-Key Rollover Test                         | 6-19 |

| 6-9    | Keyboard Test Summary                       | 6-20 |

| 6-10   | Display Format for Display Monitor Test     | 6-22 |

| 7-1    | ADVANTAGE Troubleshooting Chart             | 7-1  |

| 7-2    | Pin Locations on the Disk Drive             | 7-11 |

| 7-3    | Pin Locations on the Controller Board       |      |

|        | (Solder Side)                               | 7-13 |

| 7-4    | Power Cord Removal                          | 7-16 |

| 7-5    | Bottom View of the ADVANTAGE                | 7-17 |

| 7-6    | Cabinet Separation Sequence                 | 7-18 |

| 7-7    | Major Components Inside the ADVANTAGE       | 7-19 |

| 7-8    | ADVANTAGE 20 Base Assembly                  | 7-20 |

| 7-9    | ADVANTAGE HD-5 Base Assembly                | 7-21 |

| 7-10   | ADVANTAGE 20 Cable Connections              | 7-22 |

| 7-11   | ADVANTAGE HD-5 Cable Connections            | 7-23 |

| 7-12   | Main PC Board Removal                       | 7-25 |

| 7-13   | Disk Drive Shield Removal                   | 7-27 |

| 7-14   | Disk Drive Cabling                          | 7-28 |

| 7-15   | Upper Disk Drive Removed                    | 7-29 |

| 7-16   | Power Supply Components                     | 7-30 |

| 7-17   | Cover Assembly                              | 7-32 |

| 7-18   | Fan Cable Removal/Installation              | 7-32 |

| 7-19   | Video Components                            | 7-34 |

| 7-20   | Video PC Board                              | 7-35 |

| 7-21   | CRT Removal                                 | 7-36 |

| 7-22   | CRT Installation                            | 7-38 |

# ILLUSTRATIONS (continued)

| <u>Table</u> |                                          | Page |

|--------------|------------------------------------------|------|

| 1-1          | ADVANTAGE Specifications                 | 1-7  |

| 2-1          | ADVANTAGE Keys                           | 2-2  |

| 2-2          | Rear Panel Controls                      | 2-5  |

| 3-1          | 256K Address Space Allocation            | 3-2  |

| 3-2          | Memory Mapping I/O Addresses             | 3-4  |

| 3-3          | Memory Mapping Register Configurations   | 3-5  |

| 3-4          | Memory Parity I/O Address                | 3-6  |

| 3-5          | Memory Parity Status and Control Bytes   | 3-7  |

| 3-6          | Shared Register Addresses                | 3-9  |

| 3-7          | I/O Control Register Format              | 3-11 |

| 3-8          | I/O Commands for I/O Control Register    | 3-12 |

| 3-9          | I/O Status Register 1 Format             | 3-14 |

| 3-10         | I/O Status Register 2 Format             | 3-15 |

| 3-11         | Sample Routine for Reading Characters    | 3-20 |

| 3-12         | Video I/O Addresses                      | 3-26 |

| 3-13         | Video Driver Control Codes               | 3-28 |

| 3-14         | Video Driver Data Block Format           | 3-29 |

| 3-15         | Floppy Disk I/O Addresses                | 3-31 |

| 3-16         | Floppy Drive Control Register Format     | 3-33 |

| 3-17         | Hard Disk Drive I/O Commands             | 3-41 |

| 3-18         | Hard Disk Drive Control Register Format  | 3-43 |

| 3-19         | Hard Disk Controller/Drive Status Bits   | 3-44 |

| 3-20         | I/O Board Addresses                      | 3-52 |

| 3-21         | I/O Board Identification Codes           | 3-52 |

| 3-22         | First Digit of I/O Addresses             | 3−55 |

| 3-23         | SIO Interrupt Mask Format                | 3-56 |

| 3-24         | Serial I/O Addresses                     | 3-57 |

| 3-25         | Asynchronous Baud Rate Selection         | 3-64 |

| 3-26         | Sample Asynchronous I/O Routines for SIO |      |

|              | Board                                    | 3-65 |

| 3-27         | Synchronous Baud Rate Selection          | 3-68 |

| 3-28         | Sample Synchronous I/O Routines for SIO  |      |

|              | Board                                    | 3-69 |

| 3-29         | PIO Interrup Mask Format                 | 3-74 |

| 3-30         | PIO Status Byte Format                   | 3-75 |

| 3-31         | Parallel I/O Addresses                   | 3-76 |

| 3-22         | Sample Routine for Outputting PIO Data   | 3-77 |

| 3-33         | Boot PROM CRC Routine                    | 3-81 |

| 4-1          | I/O Status Register 1 Format             | 4-8  |

| 4-2          | I/O Address Decoder Signals              | 4-9  |

| 4-3          | I/O Select PROM Summary                  | 4-10 |

| 4-4          | I/O Control Register Format              | 4-12 |

| 4-5          | I/O Commands                             | 4-13 |

| 4-6          | I/O Status Register 2 Format             | 4-20 |

| 4-7          | Floppy Disk I/O Instructions             | 4-23 |

# ILLUSTRATIONS (continued)

| Figure                                       |                                                                                                                                                                             | Page                                         |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 4-8<br>4-9<br>4-10<br>4-11<br>4-12<br>4-13   | Floppy Disk Control Register Format HTIML Horizontal Scan PROM HTIMH Horizontal Scan PROM 60 Hz Vertical Timing PROM 50 Hz Vertical Timing PROM I/O Board Pin Assignments   | 4-24<br>4-28<br>4-29<br>4-33<br>4-34         |

| 4-14<br>4-15<br>4-16<br>4-17<br>4-18<br>4-19 | Hard Disk Controller Input/Output Signals SIO Board I/O Instructions SIO Board I/O Instructions PIO Board I/O Instructions PIO Status Byte Format PIO Interrupt Mask Format | 4-46<br>4-61<br>4-62<br>4-67<br>4-68<br>4-69 |

| 5-1                                          | Preventive Maintenance Schedule                                                                                                                                             | 5-1                                          |

| 6-1<br>6-2<br>6-3                            | Mini-Monitor Commands<br>Keyboard Test Abbreviation Codes<br>Keyboard Test Control Keys                                                                                     | 6-3<br>6-16<br>6-21                          |

| 7-1<br>7-2<br>7-3<br>7-4                     | Main Board Input Power (J11) Main Board Video Interface (J7) Main Board - Floppy Disk Power (J10) Driver Status Signals                                                     | 7-6<br>7-6<br>7-10<br>7-14                   |

# 1.2 SYSTEM DESCRIPTION

The North Star ADVANTAGE is packaged in a molded high impact plastic unit with an integral keyboard. The keyboard features an ASCII typewriter-like layout with programmable function keys and a numeric keypad.

The ADVANTAGE cabinet holds the 12-inch (diagonal) monitor, video circuit assembly, and main processor board which contains the CPU, the memory, the floppy disk controller, the I/O interface circuits, and the power supply regulator. The cabinet also houses either two floppy disk drives or one floppy disk drive and one 5" Winchester hard disk drive.

The ADVANTAGE uses a 4 MHz 280A microprocessor as the CPU. 64 Kbyte of 200 nsec dynamic random access memory (RAM) is provided for program storage, with a separate 20 Kbyte 200 nsec RAM for the bit-mapped display. A 2 Kbyte PROM contains the resident bootstrap program. An auxiliary 8035 microprocessor controls keyboard and disk input/output (I/O) to and from the CPU.

The display can operate as a 1920 character display with 24 lines x 80 characters or as a bit-mapped display with 240 x 640 pixels. Each pixel is controlled by one bit in the 20 Kbyte display memory.

The n-key rollover keyboard contains 49 standard typewriter keys, 9 symbol or control keys, a 14-key numeric/cursor control pad, and 15 programmable function keys.

In the ADVANTAGE 2Q, the two integral 5-1/4" floppy disk drives are quad capacity double-sided and double-density to provide 360 Kbyte of storage per diskette. In the ADVANTAGE HD-5, the Winchester hard disk drive provides 5 Mbytes of storage.

A simplified block diagram of the ADVANTAGE computer is shown in Figure 1-2. The blocks are described briefly below. Refer to Chapter 4, Theory of Operation for more detailed descriptions of ADVANTAGE component blocks.

- The Central Control Unit maintains primary control of the system. Contained herein are the Z80 and 8035 processors and the controllers for the I/O devices.

- The 64K Main RAM (Random Access Memory) provides temporary storage of programs and data. Programs are executed while residing in this RAM.

- The 2K Boot PROM (Programmable Read-Only Memory) provides bootstrapping and a built-in Mini-Monitor for debugging functions.

- The Video Monitor and 20K Display RAM produce a high resolution display that can be used for graphics applications, or to display messages for the operator.

- The floppy Disk Drive(s) use 5-1/4 inch quad capacity diskettes. The optional hard Disk Drive replaces the second floppy drive.

- The Speaker produces a tone used to signal the operator. The frequency and duration of the tone are under program control.

- The Keyboard includes the standard typewriter configuration, a numeric keypad and 15 programmable function keys.

- The I/O Board Slots allow the ADVANTAGE to be customized for specific applications. There are six board slots which may contain interface boards for external devices or other boards which expand the computing power of the ADVANTAGE. Two types of North Star boards are presently available for use in this area: the Serial Input/Output (SIO) Board and the Parallel Input/Output (PIO) Board. As supplied, the ADVANTAGE contains an SIO board installed in I/O slot one.In an ADVANTAGE HD-5 the Hard Disk Controller resides in I/O slot six.

# 1.4 ADVANTAGE SPECIFICATIONS

Table 1-1 lists the physical and electrical characteristics of the ADVANTAGE.

Table 1-1

| ADVANTAGE Specifications                        |                                                              |  |

|-------------------------------------------------|--------------------------------------------------------------|--|

| CABINET                                         |                                                              |  |

| Dimensions                                      | 48 cm wide x 51 cm long x 31.5 cm high                       |  |

|                                                 | (18-3/4 in x 20 in x 12-1/2 in)                              |  |

| Net Weight                                      | 19.5 kg (43 lbs)                                             |  |

| Composition                                     | High impact structural foam                                  |  |

| POWER REQUIREME                                 | NTS                                                          |  |

| External (with Internal Line F                  | ilter)                                                       |  |

|                                                 | 115 VAC, (98 to 132 VAC)<br>60Hz                             |  |

|                                                 | 230 VAC, (196 to 264 VAC)<br>50/60 Hz                        |  |

| Internal Supply ±5 VDC ±5% Voltages ±12 VDC ±5% |                                                              |  |

| Power<br>Consumption                            | 2 amps @ 115V<br>1 amp @ 230V                                |  |

| TEMPERATURE AND HUMIDITY                        |                                                              |  |

| Operating:<br>(with diskette)                   | 10 C to 40 C<br>(50 F to 104 F)<br>20% to 80% non-condensing |  |

| Non-operating                                   | -40 C to 60 C<br>(-40 F to 140 F)                            |  |

# Table 1-1 (continued)

Shipping

-40 C to 52 C (-40 F to 125 F)

5% to 95% non-condensing

PROCESSOR/MEMORY

CPU

Z80A Microprocessor, operating speed: 4MHz

8035 auxiliary processor for keyboard and disk

Memory

64K byte Main RAM 20K byte Display RAM 2K byte Boot PROM

**VIDEO**

Screen

28 cm (12 in) diagonal

P31 phosphor (green)

High impact, non-glare safety shield

Grid

1920 character display, 24 lines by 80 characters

5X7 character in 8x10 dot matrix

Graphics

resolution

240 pixel high x 640 pixel wide

Refresh rate

60 Hz

CRT Anode

17 KV maximum

Voltage

KEYBOARD

Keytops

Sculptured

Selectric-compatible

N-Key roll-over for fast data entry

Number of Keys: 87

Key Groups

49 Standard Typewriter Keys

14-key Numeric Pad with ENTER key 15 Programmable Function Keys

9 Additional Symbol/Control Keys

# Table 1-1 (continued)

Other features Full Cursor control

Special Shift-Lock Keys

5 Shift Modes Auto Repeat

# FLOPPY DISK DRIVES

Number of

Two floppy disk drives housed in cabinet

drives

Diskettes Standard 5-1/4 in floppy diskettes.

Recommended type: Dysan part No. 107/2D.

512 bytes/sector, 10 (hard) sectors/ track

35 tracks/side, 2 sides/diskette

Storage

Quad (double-sided, double-density)

360K bytes per diskette (formatted)

Transfer Rate

250K bits/second

Latency

100 ms

(average)

Access Time Track-to-Track

5 ms

Track Density

48 tpi

Tracks per Side 35

# ERROR RATES

Soft errors

1 per 108 bits read

Hard errors

1 per 10<sup>11</sup>bits read

Seek errors

l per 10<sup>6</sup> seeks

Disk speed

300 rpm  $\pm$  3.0%

# Table 1-1 (Continued)

| HARD DISK DRIVE                                                                                |                                                                         |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Capacity<br>Unformatted<br>Per Drive<br>Per Surface<br>Per Track                               | 6.38 megabytes<br>1.59 megabytes<br>10416 bytes                         |

| Formatted Per drive Per surface Per track Per sector Sectors per track                         | 5.0 megabytes<br>1.25 megabytes<br>8192 bytes<br>512 bytes<br>16        |

| Transfer Rate                                                                                  | 5.0 megabits per second                                                 |

| Access Time<br>Track to track<br>Average<br>Maximum<br>Settling time                           | 3 ms<br>170 ms<br>500 ms<br>15 ms                                       |

| Average Latency                                                                                | 8.33 ms                                                                 |

| Rotational Speed Recording Density Flux Density Track Density Cylinders Tracks R/W Heads Disks | 3600 rpm ± 1%<br>7690 bpi max<br>7690 fci<br>255 tpi<br>153<br>612<br>4 |

| Max Error Rates: Soft read errors = 1 per Hard read errors = 1 per Seek errors = 1 per         | 10 <sup>11</sup> bits read                                              |

| Less bad spots, if any (max 16)<br>Not recoverable within 16 retries                           | •                                                                       |

Table 1-1 (continued)

| INPUT/OUTPUT        |                                                                            |

|---------------------|----------------------------------------------------------------------------|

| I/O Bus             | Slots for up to six plug-in boards (up to five plug-in boards in the HD-5) |

|                     | Each board addressed by 16 I/O addresses                                   |

| Serial I/O<br>(SIO) | RS232 Serial Port                                                          |

| (810)               | Current loop option                                                        |

|                     | Asynchronous: 45 baud to 19.2 kilobaud                                     |

|                     | Synchronous: 2400 baud to 51 kilobaud                                      |

| Parallel I/O        | 8-bit data in and out with three handshake lines for each port             |

|                     | Maximum speed is limited by the processor.                                 |

This chapter describes startup and general operation of the ADVANTAGE. It contains a description of the keyboard and rear panel controls of the ADVANTAGE. It also provides instructions for loading diskettes in the floppy drive(s), booting a program, and methods for performing a system reset.

#### 2.1 OPERATING CONTROLS

The ADVANTAGE operating controls consist of the keyboard and rear panel controls. On the rear panel are a power switch, screen brightness control, and the system Reset button. For operation of the disk drives, diskette loading and unloading procedures are given.

# 2.1.1 Keyboard

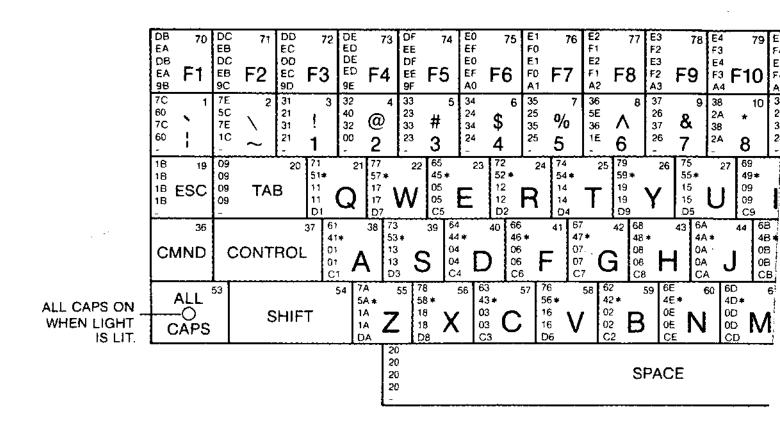

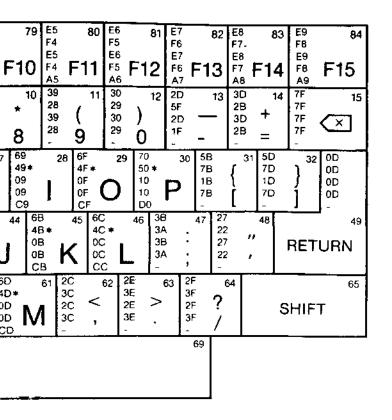

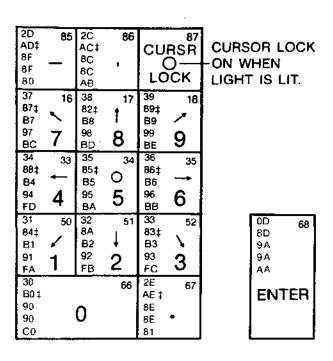

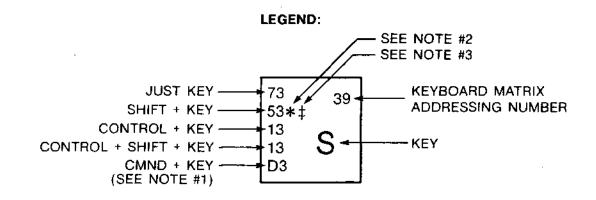

Primary system control is maintained by entering commands and data from the ADVANTAGE keyboard. The keyboard is illustrated in Figure 2-1. There are 87 keys, described in Table 2-1. The keys generate standard ASCII codes as well as additional 8-bit hex codes. Keys and their codes are listed under various tabulations in Appendix A.

Characters entered from the keyboard are displayed on the CRT screen under program control. A program-maintained cursor marks the position on the screen where the next character entry will be displayed.

Table 2-1

|                     | ADVANTAGE Keys                                                                                                        |                                                                                                                                                                                   |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Key Group           | Keys                                                                                                                  | Description                                                                                                                                                                       |  |

| CHARACTER           | ABCDEFGHIJKLM NOPORSTUVWXYZ 123456789010# \$%^&*()=+;: '",.<>/?[]{} (space)                                           | Alphabetic, numeric, and special symbols. Numbers and three symbols (.,-) are also available on the numeric pad.                                                                  |  |

| KEYBOARD<br>CONTROL | SHIFT                                                                                                                 | Either of two identical keys which cause most of the other keys to shift into upper case (see Appendix A).                                                                        |  |

|                     | ALL CAPS                                                                                                              | Shifts only alphabetic characters to upper case. Key is a "push on-off" type with LED to signal when function is active.                                                          |  |

|                     | RETURN                                                                                                                | Carriage return.                                                                                                                                                                  |  |

|                     | TAB                                                                                                                   | Position to next tab set on the line. Setting and releasing tabs is done under program control.                                                                                   |  |

|                     | <x]< td=""><td>Character delete, backspace, or delete and backspace depending upon the program being used.</td></x]<> | Character delete, backspace, or delete and backspace depending upon the program being used.                                                                                       |  |

|                     | ENTER                                                                                                                 | Numeric pad data entry key.                                                                                                                                                       |  |

| CURSOR<br>CONTROL   | 8 direction arrows                                                                                                    | All cursor activity is under program control.                                                                                                                                     |  |

|                     | CURSOR LOCK                                                                                                           | Shifts only cursor control keys (1-9 on numeric pad) to allow cursor positioning without using SHIFT key. Key is a "push on-push off" type with LED to signal when key is active. |  |

Table 2-1 (continued)

| Key Group | Keys                                                        | Description                                                                                            |

|-----------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| FUNCTION  | F1 F2 F3 F4 F5<br>F6 F7 F8 F9 F10<br>F11 F12 F13 F14<br>F15 | Special purpose keys entirely under program control. Each Function key can generate up to three codes. |

| PROGRAM   | ESC                                                         | (ESCAPE) key under program control.                                                                    |

|           | CONTROL                                                     | (CTRL) operates as a special shift for keys.                                                           |

|           | CMND                                                        | (Command) operates as a special shift for keys.                                                        |

# 2.1.2 Rear Panel Controls

A rear view of the ADVANTAGE is shown in Figure 2-2. Table 2-2 describes the controls shown in the figure.

Table 2-2

| Rear Panel Controls      |                                                                                                                                                                                                        |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                          |                                                                                                                                                                                                        |  |

| Control                  | Description                                                                                                                                                                                            |  |

| ON/OFF Switch            | Applies/removes electrical power to the unit.                                                                                                                                                          |  |

| Power Cord<br>Receptacle | Mates with power cord to provide electric current from AC power source.                                                                                                                                |  |

| Fuse Holder              | Contains the AC line fuse. Use 2A slo-blo (time delay) fuse for 115V operation and 1A time delay fuse for 230V operation.                                                                              |  |

| Reset Pushbutton         | Resets and initializes the system. After reset, data in Main Memory is indeter-minate but disk storage data is not affected.                                                                           |  |

| I/O Plate                | Openings in plate allow access to I/O connectors on I/O Boards 1 through 6. A Serial I/O Board is a standard installation in slot 1. In hard disk systems, the Hard Disk Controller resides in slot 6. |  |

| Brightness<br>Control    | Controls brightness of the display screen.<br>Turn clockwise to increase brightness.                                                                                                                   |  |

# 2.2 SYSTEM STARTUP

Startup is a function of the bootstrap routines contained in ROM. Drive I is programmed as the default drive in the bootstrap program; Drive I, therefore, is the drive normally used for booting the operating system.

# 2.2.1 Standard Startup - Booting From Drive 1

To boot from floppy disk drive 1, proceed as follows:

Insure that there are no diskettes in the floppy disk drive(s).

#### CAUTION

Turning power on or off with diskettes loaded may cause loss of data on the diskettes.

- Turn on ADVANTAGE power by pressing the ON/OFF switch at the rear of the cabinet to the ON position.

- 3. Insert a system diskette or diagnostic diskette into drive 1. Drive 1 is:

- the upper drive in an ADVANTAGE with dual floppy drives

- the lower drive in an ADVANTAGE with a hard disk.

- 4. Press RETURN after the message "LOAD SYSTEM" appears on the screen. A program is read from drive 1, and control is turned over to the operating system or the diagnostics.

- Proceed as prompted by the program loaded. If diagnostics have been loaded, refer to Chapter 6 for further information.

# 2.2.2 Alternate Startup - Booting From Drive 2

An ADVANTAGE with dual floppy drives may be booted from drive 2 (the lower drive). To boot from Drive 2, proceed as in Section 2.2.1, except as follows:

- At step 3 insert the system or diagnostic diskette into Drive 2.

- At step 4 when the "LOAD SYSTEM"-message appears, type D2 before pressing RETURN.

# 2.2.3 Alternate Startup - Booting From A Serial Port

The bootstrap program allows the system to load a program through a serial communication link. To use this feature, you must have a Serial I/O board installed in slot 3. Section 3.13.3 gives details of the communication link.

To boot from a serial port, proceed as follows:

- 1. Power up the ADVANTAGE (Section 2.2.1) or Reset (Section 2.3) to obtain the "LOAD SYSTEM" message.

- When the "LOAD SYSTEM" message appears, type S and then press RETURN. The system then boots from the serial port.

# 2.2.4 Mini-Monitor Startup

The built-in Mini-Monitor may be started up as follows. Refer to Section 6.1 for a description of Mini-Monitor commands:

- 1. Power up the ADVANTAGE (Section 2.2.1) or Reset (Section 2.3) to obtain the "LOAD SYSTEM" message.

- When the "LOAD SYSTEM" message appears, press CONTROL-C to enter the Mini-Monitor.

# 2.3 RESTARTING THE SYSTEM

The ADVANTAGE may be restarted by entering the unique keyboard Reset sequence, by cycling power, or by pushing the rear panel Reset button. Cycling the power forces the CPU program counter to the base address (0000H); the Reset switch and the keyboard sequence both send a non-maskable interrupt (NMI) to the CPU (refer to Section 4.1.1). This interrupt forces the ADVANTAGE to re-initialize and display the "LOAD SYSTEM" prompt.

#### CAUTION

Resetting the ADVANTAGE during program operation can cause loss of data. Use the keyboard reset feature to reset the ADVANTAGE only to recover from system hard errors.

RESET THE ADVANTAGE USING THE REAR PANEL SWITCH ONLY WHEN ALL RECOVERY METHODS HAVE FAILED.

# 2.3.1 Keyboard Reset

The ADVANTAGE system may be reset by pressing four keys simultaneously on the keyboard. The keys are: CMND, both SHIFT keys, and <X]. The effect of this reset is equivalent to pushing the Reset pushbutton on the rear of the ADVANTAGE cabinet.

The keyboard reset feature may be enabled and disabled under program control. When power is first applied to the ADVANTAGE or after the Reset pushbutton is pressed, the keyboard reset feature is enabled. Thereafter, the feature can be disabled and re-enabled by the program (see Section 3.5.1).

This chapter provides programming information for the various sections of the ADVANTAGE, including the I/O devices. It also explains how to reconfigure the SIO and PIO boards to change their mode of operation.

#### 3.1 MICROPROCESSOR CONTROL

The ADVANTAGE uses the Z-80A microprocessor as its central processing unit (CPU). Refer to the Appendix G for the programming details of this integrated circuit.

# 3.2 MEMORY CONTROL

# 3.2.1 Memory Mapping

The ADVANTAGE computer uses a memory mapping scheme to expand its memory addressing capabilities from 64K bytes to 256K bytes. This effectively expands the Memory Address bus from 16 bits to 18 bits.

The addressing scheme divides the 256K bytes into 16 pages of 16K bytes each (see Table 3-1). The three major areas of memory in the ADVANTAGE: the Main RAM, the Display RAM, and the Boot PROM, are permanently assigned to the addresses shown in the table.

Table 3-1

| 256K Address Space Allocation |                                                                  |                                                                                                  |

|-------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Page                          | 18-Bit Address                                                   | Contents                                                                                         |

| 0<br>1<br>2<br>3              | 00000 - 03FFF<br>04000 - 07FFF<br>08000 - 0BFFF<br>0C000 - 0FFFF | 16K bytes of Main RAM<br>16K bytes of Main RAM<br>16K bytes of Main RAM<br>16K bytes of Main RAM |

| 5<br>6<br>7                   | 14000 - 17FFF<br>18000 - 1BFFF<br>1C000 - 1FFFF                  | Not presently used                                                                               |

| 8<br>9<br>A                   | 20000 - 23FFF<br>24000 - 27FFF<br>28000 - 2BFFF                  | First 16K bytes of Display RAM Last 4K bytes of Display RAM repeated four times Not used         |

| В                             | 2C000 - 2FFFF                                                    | Not used                                                                                         |

| C<br>D<br>E<br>F              | 30000 - 33FFF<br>34000 - 37FFF<br>38000 - 3BFFF<br>3C000 - 3FFFF | 2K-byte Boot PROM repeats<br>to fill 64K bytes                                                   |

Memory mapping is implemented by four Memory Mapping registers. Figure 3-1 shows how these registers work.

First, output instructions are used to load the register with the appropriate bits. Thereafter, each time the memory is accessed, the upper two bits of the program address automatically generate four bits of memory address by selecting one of the four Memory Mapping registers. The remaining 14 bits of the program address are passed through to the memory address without change.

With any one configuration of the Memory Mapping registers, the program has access to only four of the 16 possible pages. In order to change the four pages it wishes to access, the program must change one or more of the Mapping registers.

# Table 3-10 (Continued)

# NOTES

- Bits 0-3 are only valid after bit 7 changes state to acknowledge that the command has been executed.

- When bits 0-3 contain the disk sector number, they have a range of 0-9 for the 10 sectors, or one of the following special codes:

E = disk drive motors off

F = index pulse detected

#### 3.5 KEYBOARD CONTROL

This section contains the programming information for the ADVANTAGE keyboard. Refer to the diagrams and tables in Section 3.4 for the following discussion.

# 3.5.1 Keyboard Reset Enable

The 4-key reset feature of the ADVANTAGE keyboard may be enabled or disabled under program control. This feature is initially enabled at power-up. It may be disabled under program control by issuing the two-command sequence "6,7" to the I/O Control register (I/O address FOH) when the feature is enabled. This command sequence complements the current state of the Keyboard NMI flag and places its current state into bit 0 of I/O Status register 2 (I/O address DOH).

The keyboard reset is enabled by power-on reset, pushing the RESET button, or by the program issuing the "6,7" sequence to the I/O Control register when the feature is disabled. Once enabled, the 4-key keyboard reset functions exactly like the RESET pushbutton reset. It forces a non-maskable interrupt to reset the system as described in the following section.

- 3. Wait for the Command Acknowledge bit to complement. This delay is in the range of 0.5 to 1.5 milliseconds.

- 4. Input from I/O Status register 2 and check bit 0. If this bit is on, the KB MI flag is now set.

- 5. If the KB MI flag is reset, repeat step 2 above.

When the keyboard causes an interrupt, the program can verify the source of the interrupt by inputting from I/O Status register and checking bit 0. This bit is on if the keyboard is interrupting.

To clear the interrupt, the program must input keyboard characters (see Section 3.5.4) until the Keyboard Data flag is reset. This flag is bit 6 of I/O Status register 2.

Polled. If the keyboard is to be polled rather than operated in interrupt mode, the KB MI flag must be reset. This flag is reset when the ADVANTAGE power is turned on, or when the ADVANTAGE Reset Button is pushed. The program may reset the KB MI flag by repeating the same sequence as above and checking the bit for "off" (zero) at step 4. Perform a repeat (step 5) if the KB MI flag is set.

The program polls the keyboard by periodically inputting from I/O Status register 2 (I/O address DOH) and checking bit 6. If the bit is on, the program reads the keyboard character(s) as described below.

# 3.7 FLOPPY DISK DRIVE CONTROL

The Floppy Disk Drive Controller uses a minimum of hardware and requires a sophisticated program, implemented in ROM, to read from and write to the disk drives. Some of the timing and motor control is determined by the program.

The program communicates with the Floppy Disk Controller in the following ways:

- 1. Through the Shared I/O Interface registers described in Section 3.4.

- 2. By outputting control bytes to the Drive Control register. The format for the register is shown in Table 3-16, and its I/O address is listed in Table 3-15.

- 3. By accessing the other I/O addresses given in Table 3-15.

Table 3-15

| Floppy Disk I/O Addresses    |           |                                                                                                                                                                                                                                    |

|------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O Address<br>(Hexadecimal) | Operation | Description                                                                                                                                                                                                                        |

| 80                           | INPUT     | Input Disk Data. Sets the processor into the wait state until the disk data is available, then reads the data. Inputting from this address when data is unavailable puts the processor into a continuous wait state.               |

| 80                           | ОИТРИТ    | Output Disk Data. Sets the processor into the wait state until the Disk Controller writes the data to the diskette. Outputting to this address before setting the Disk Write flag puts the processor into a continuous wait state. |

3-31

Table 3-15 (continued)

| 81 | INPUT  | Input Sync Byte. Sets the processor into the wait state until the sync byte is available, then reads the data. If the disk format is correct, the character read is a BFH. Inputting from this address when a sync byte is not available puts the processor into a continuous wait state. |

|----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 81 | OUTPUT | <u>Load Drive Control Register.</u> See<br>Table 3-16 for the register format.                                                                                                                                                                                                            |

| 82 | INPUT  | Clear Disk Read Flag. Terminates the disk read operation. The data input by this address is indeterminate.                                                                                                                                                                                |

| 82 | OUTPUT | Set Disk Read Flag. This flag is set as one of the steps in initiating a disk read operation. The output data is ignored.                                                                                                                                                                 |

| 83 | OUTPUT | Set Data Write Flag. This flag is set to initiate a disk write operation. The output data is ignored. The Disk Write flag is cleared on the leading edge of the next sector mark.                                                                                                         |

#### NOTES

- When these I/O addresses are decoded, bits 2 and 3 are ignored. This produces four address for each function that work equally well. For example, addresses 80, 84, 88 and 8C all produce identical results.

- If a disk operation causes the processor to go into a continuous wait state, the Main RAM refresh cycles are interrupted and data in Main RAM is lost.

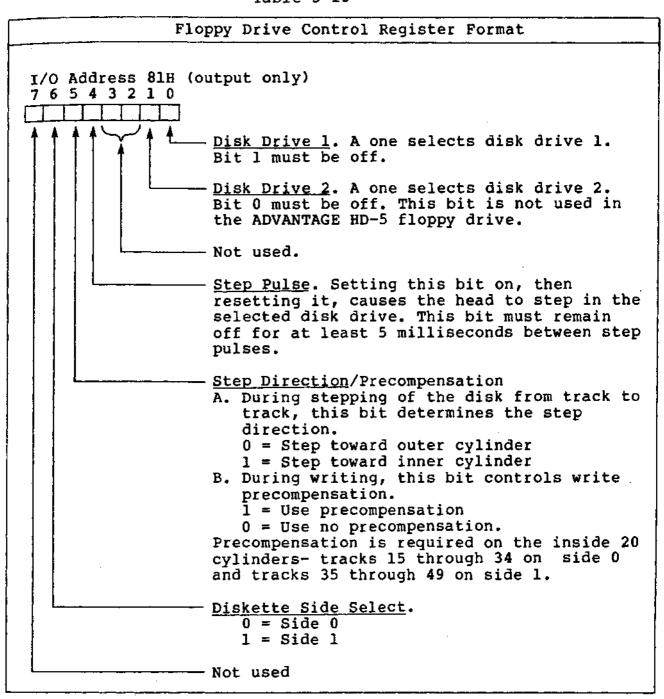

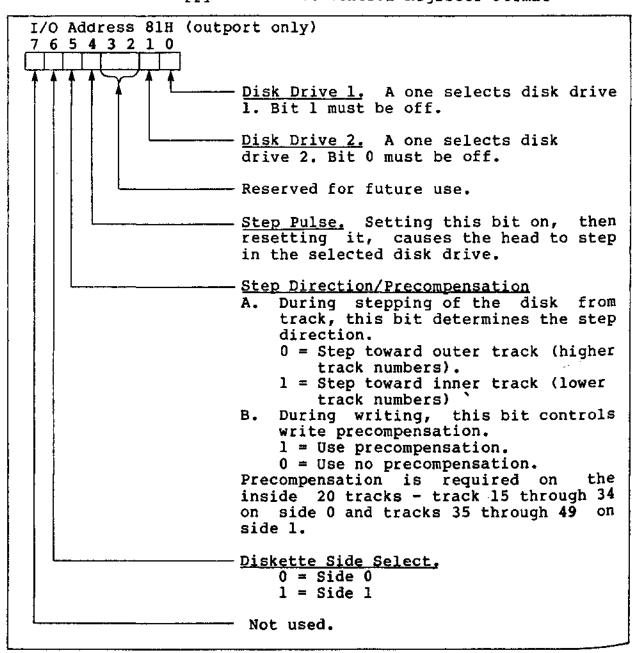

Table 3-16

A disk operation involves selecting the drive, enabling the motor, performing a head seek, selecting a sector, and then performing the read or write operation. These operations are described separately in the following subsections.

# 3.7.1 Power-On Initialization

The data separation circuitry must be initialized after power is applied to the disk controller but before a read or write operation. This is done by alternately setting and clearing the Disk Read flag (I/O address 82H)) at approximately 100-millisecond intervals for five cycles.

# 3.7.2 Motor Enable

Both disk drive motors are turned on whenever a command 5 is received (Start Disk Drive Motors, see Table 3-8). If the command 5 is removed for three seconds, the value 0EH is displayed as the sector number. After 100 microseconds both disk drive motors are turned off and the Drive Control register is reset to zeros. The 100-microsecond delay prevents the motors from being turned off in the middle of a read or write operation.

# 3.7.3 Drive Selection

After the drive motors are turned on, the program loads the Drive Control register (see Table 3-16) to select one of the two drives. In the ADVANTAGE HD-5, this drive is always disk drive 1, i.e., the floppy drive. At the same time the other bits of the register may be loaded in preparation for a head seek, read, or write.

#### 3.7.4 Seek

The positioning of the disk drive read/write head is entirely under program control. The program must keep track of the position of the head and generate the timing pulses required to move the head from track to track.

The head is initialized (set on Track 0) by stepping it one track at a time toward the outside of the diskette, and after each step, inputting I/O Status register 1 (I/O address EOH). Bit 5 of the register is on when the selected drive has its head positioned on track 0. There are 35 tracks per side.

The head is stepped by setting and then resetting bit 4 of the Drive Control register (I/O address 81H). When the head is moved by more than one track in either direction, this bit must remain off for at least 5 milliseconds between step pulses. When the head reaches its destination, the program must delay at least 20 milliseconds to allow time for the head to settle.

#### 3.7.5 Sector Selection

The sector number is read by performing the following sequence:

- 1. Input and record the state of the Command Acknowledge bit (I/O address DOH, bit 7).

- 2. Issue command 5 to the I/O Control register (I/O address FOH, refer to section 3.4).

- 3. Wait for the command acknowledge bit to complement. This delay is in the range of 0.5 to 1.5 milliseconds.

- 4. Input the Sector Mark bit (I/O address EOH, bit 6) until it is found to be zero.

- 5. Input the sector number (I/O address DOH, bits 0 through 3). This number is valid while the Sector bit is zero, and for 50 microseconds thereafter.

The number obtained by following the above procedure is actually the number of the previous sector. For example, if sector 6 is to be accessed, the program must search for sector 5. If the desired sector is not found on the first attempt, repeat steps 4 and 5 above until it is found.

When the correct sector has been located, the program goes into a loop, waiting for the sector mark to go from a zero to a one. The read or write operation sequence must be initiated on this transition.

## 3.7.6 Read Data

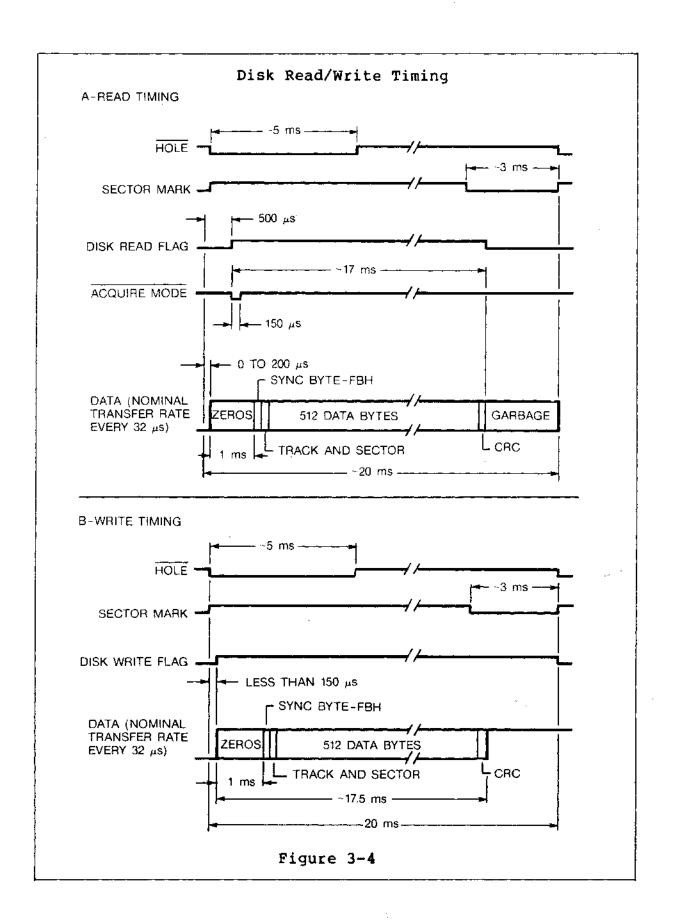

After the proper sector number is found, the read sequence is as follows:

- 1. Wait 500 microseconds after the zero-to-one transition of the Sector Mark bit.

- Set the Disk Read flag by outputting to I/O address 82H.

- 3. Change the Acquire Mode flag to zero (bit 3 of I/O address FOH).

- 4. Wait 150 microseconds, then change the Acquire Mode flag to a one.

- 5. Wait until the Disk Serial Data bit (I/O address EOH, bit 7) changes to a one.

- 6. Input the sync byte (I/O address 81H). This byte should be FBH.

- 7. Input from I/O address 80H for the remainder of the data. The next byte read is the second sync byte, which is (sector number) + (16 x track number) truncated to the lower eight bits. Following this are the 512 data bytes and the CRC byte. The CRC byte is not checked by hardware; a software routine is needed if checking is desired.

- 8. The program's task is complete at this point. The hardware will reset the Disk Read flag at the zero-to-one edge of the next sector mark. During the sector mark a new read sequence can be started.

Read timing is illustrated in Figure 3-4A. Note that the timing is such that consecutive sectors may be read.

#### 3.7.7 Write Data

After the proper sector number is found, the write sequence is as follows:

- Input the Write Protect bit (I/O address EOH, bit

The bit must be a zero to write on the diskette.

- 2. If writing to one of the inner tracks, set the Precompensation bit (I/O address 81H, bit 5). Precompensation is required on tracks 15 through 34 on side 0, and tracks 35 through 49 on side 1.

- 3. Set the Disk Write flag by outputting to I/O address 83H. This must be done within 150 microseconds after the zero-to-one transition of the Sector Mark bit (I/O address E0H, bit 6).

- 4. Output 33 consecutive bytes of zeros to I/O address 80H. This forms the preamble of the sector.

- 5. Output two sync bytes to I/O address 80H. The first contains the synchronization byte (OFBH), and the second contains the sector address (see READ DATA).

- 6. Output 512 data bytes to I/O address 80H.

- 7. Output the CRC byte to I/O address 80H. Note that the program must calculate the CRC byte.

- 8. The program's task is complete at this point. The hardware will reset the Disk Write flag at the zero-to-one edge of the next sector mark. During the sector mark a new write sequence can be started.

Note that it is possible to write contiguous sectors by waiting for the Sector Mark bit to return to zero, and starting again with step 3 above.

Write timing is illustrated in Figure 3-4B.

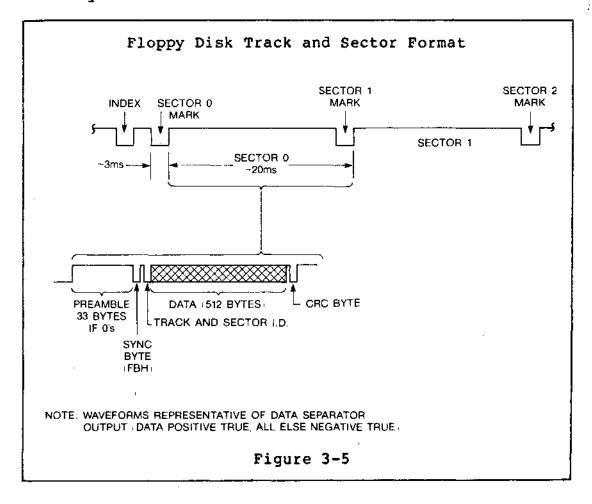

## 3.7.8 Floppy Disk Data Format

Each floppy disk is formatted for 35 data tracks per side, with each track containing 10 hard sectors. Index holes in the diskette media physically mark the beginning of each sector. An eleventh index hole provides the Floppy Disk Controller with an indication of one complete disk revolution. Actual disk recording begins approximately 96 microseconds after sector hole detection.

The data format is shown in Figure 3-5. Each sector contains a Preamble (16 bytes of zeros), a Sync Character (FBH) byte, 256 bytes of data, and a Check Character byte. The formatting program computes the Check Character constantly by setting it to zero, then exclusive ORing each successive data byte value with the current value of the Check Character and rotating the byte left one bit.

## 3.8 HARD DISK DRIVE CONTROL

The ADVANTAGE HD-5 has a separate Disk Controller board dedicated to the hard disk.

It requires its own disk driver program to perform read or write operations. The driver program must:

- Format the drive.

- Position the drive head over the desired track

- Locate the desired data sector.

- Initiate the read or write operation.

These operations are described in detail in this section.

The program communicates with the controller through 16 contiguous I/O ports (addresses). Although only eight of the addresses are used in performing a read or write operation, the controller responds to all 16. Commands used to communicate with the controller via the I/O ports are described in Section 3.8.1.

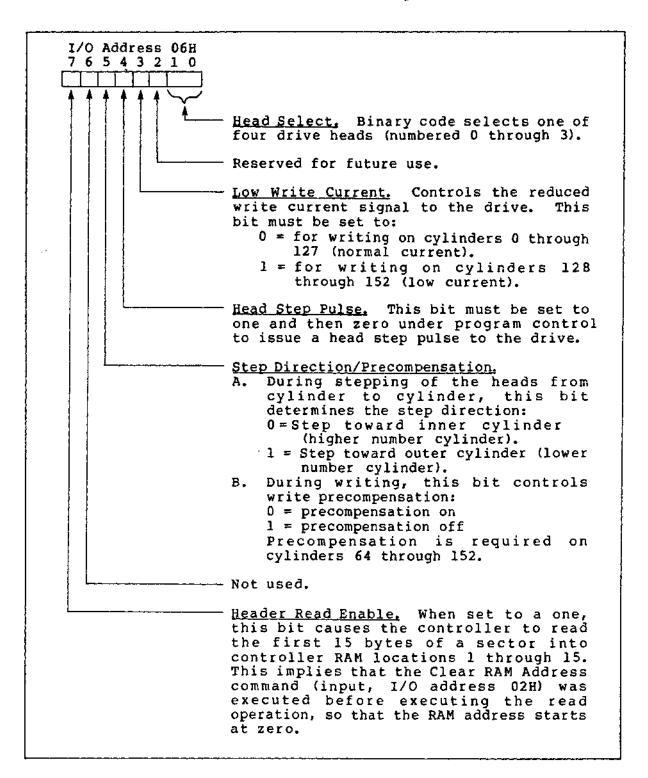

#### 3.8.1 I/O Commands

The controller occupies an address space of 16 consecutive I/O addresses. The controller responds to eight input commands and three output commands, as described in Table 3-17.

Table 3-17

Hard Disk Drive I/O Commands

| I/O Add | dress<br>ecimal) | Function                                                                                                                                                                                                                                                                    |  |  |  |

|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| OUTPUT  | COMMAN           | DS                                                                                                                                                                                                                                                                          |  |  |  |

| 05      |                  | Load Sector Counter. Loads the Sector Counter in the controller. This command is used only when formatting the disk drive to write the controller index pulse. It prevents an inadvertent sector pulse from stopping the write operation when the drive is being formatted. |  |  |  |

| 06      |                  | Load Control Register. Loads the Drive Control register in the controller. The control bits are defined in Table 3-18.                                                                                                                                                      |  |  |  |

| 07      |                  | Host Write RAM. Writes the data into the RAM location to which the RAM Address Counter currently points. The RAM Address Counter is incremented by 1 after the RAM write is complete.                                                                                       |  |  |  |

| INPUT C | OMMANDS          | <b>3</b>                                                                                                                                                                                                                                                                    |  |  |  |

| 00      |                  | Read RAM. Reads the data from the RAM location to which the RAM Address Counter currently points. At the end of the input operation, the RAM Address Counter is incremented by 1.                                                                                           |  |  |  |

| 01      |                  | Read Status. Transfers information from the Controller Status register to the computer. The status bits are defined in Table 3-19.                                                                                                                                          |  |  |  |

Table 3-17 (Continued)

| Function                                                                                                                                                                                                |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Clear RAM Address. Resets the RAM Address Counter to location 0.                                                                                                                                        |  |  |

| Clear Sector. Clears the sector pulse latch.                                                                                                                                                            |  |  |

| Start Sync. Sets the enable sync latch. This latch is set at the beginning of each read to allow the controller board to synchronize with the preamble at the beginning of the sector (see Figure 3-6). |  |  |

| Start Read. Sets the read enable flip-flop and clears the sync latch. This allows the controller to begin looking for the sector sync byte.                                                             |  |  |

| Start Write. Sets the write latch in the controller, enabling writing on the drive.                                                                                                                     |  |  |

| Format Write. Sets the write latch and clears the index one-shot. This command is used only when formatting the drive to permit writing during the index pulse.                                         |  |  |

|                                                                                                                                                                                                         |  |  |

## NOTE

In decoding the I/O address, the controller ignores bit 3. Thus, for each function, there are two addresses that work equally well: Addresses 00 and 08 produce identical results, as do 01 and 09, 02 and 0A, etc. In this table only the nominal form (bit 3=0) is listed.

Table 3-18

Hard Disk Drive Control Register Format

Table 3-19

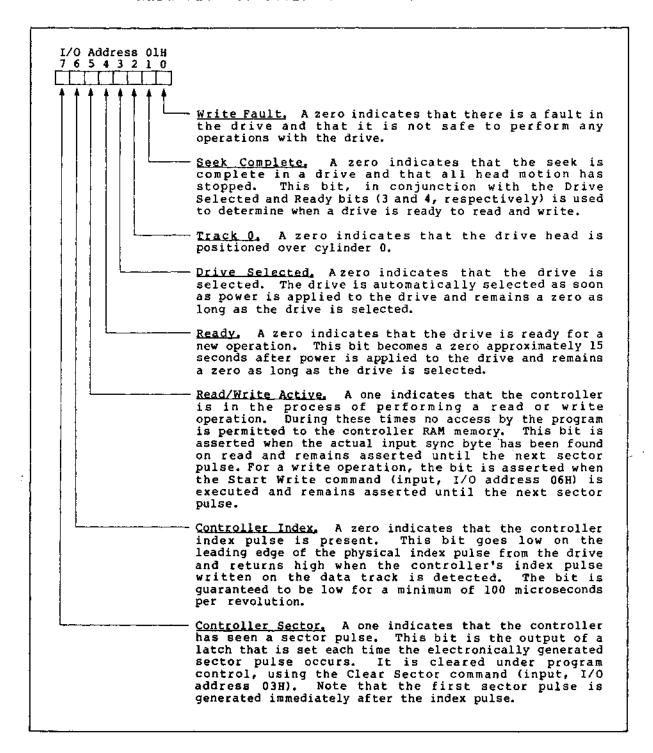

Hard Disk Controller/Drive Status Bits

# 3.8.2 Head Positioning

Positioning of the head over the respective cylinders is entirely under program control. The hard disk drive has 153 cylinders. Positioning from cylinder to cylinder is performed by a stepper motor (as in the floppy disk drive). The program is required to maintain the current cylinder number within the software and to determine the direction and number of tracks to move to get to a new track.

A bad spot table is maintained on track 0. Bad spots are tracks on which one or more sectors have proven to be unreliable in factory testing. Bad spots are also listed on the HD-5 Bad Spot Label located on the side of the disk drive. The program does not use tracks that have been designated as bad spots.

# Track 0 Sensing

The operation begins by sensing whether or not the disk drive is presently located over track 0 (Input, I/O address 01H, bit 2). If it is, the drive is stepped inward until the track 0 bit changes to a one.

This feature guards against the situation where the head has moved itself outside track 0 and is on a negative numbered track. The number of steps permitted in this inward direction is 20, which should ensure that the drive is not inside track 0. If it takes more than 20 steps, the drive is faulty.

Once the track 0 bit changes to a one, or if it was initially a one, the head is stepped towards the outside of the drive one step at a time until the track 0 bit changes again to a zero, showing that the head is located over track 0. If more than 153 track movements do not cause the track 0 indication to become true, the drive is faulty.

#### 3.10 SIO BOARD

The Serial Input/Output (SIO) Board provides a general facility for communicating with serial I/O devices. Synchronous and asynchronous operation are described in separate subsections. This section begins by describing those features of the board that are common to both synchronous and asynchronous operation.

#### 3.10.1 Reset

When the I/O Reset bit (I/O address FOH, bit 4) is set on, then off, it has the following effect on the SIO Board:

- The Interrupt Mask is cleared to zeros, preventing any interrupts from the board.

- 2. The Baud Rate register is cleared to zeros. Normally the register would now have to be reloaded to select the desired baud rate. See the appropriate section below.

- The USART is reset, in preparation for reprogramming.

Note that the I/O Reset bit resets all I/O Boards simultaneously.

#### 3.10.2 Board ID

The 8-bit identification code for the SIO Board is F7H. The I/O address used to input this code is determined by the board slot occupied by the SIO (see Table 3-20).

# 3.10.3 Data Transfers

The I/O address used to transfer a data byte to or from the SIO Board is xOH, where x is determined by the board slot occupied by the SIO (see Table 3-22). The standard location for the SIO Board is slot 1.

Table 3-22

| First Digit           | First Digit of I/O Address    |  |  |  |  |  |

|-----------------------|-------------------------------|--|--|--|--|--|

| Board Slot            | First Digit<br>of I/O Address |  |  |  |  |  |

| 6<br>5<br>4<br>3<br>2 | 0<br>1<br>2<br>3<br>4<br>5    |  |  |  |  |  |

#### 3.10.4 Control

١,

The operation of the SIO Board is controlled by specifying the Interrupt Mask and the baud rate, and by programming the 8251 USART IC (integrated circuit).

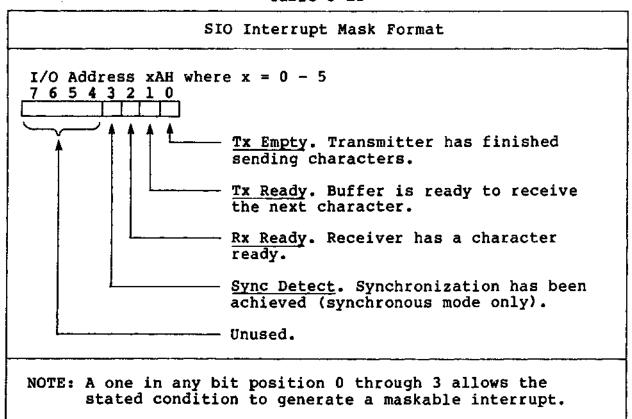

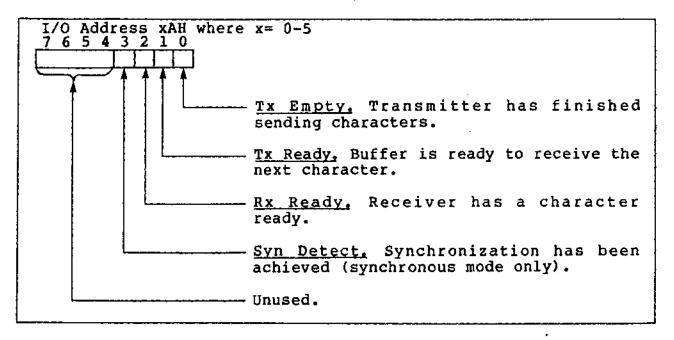

The format of the Interrupt Mask is shown in Table 3-23. A one in any of the bit positions 0 through 3 allows the SIO Board to generate a maskable interrupt if the stated condition occurs. The program defines this mask by outputting the appropriate bit pattern to I/O address xAH, where x is determined by the board slot occupied by the SIO Board (see Table 3-22).

The baud rate is specified by loading the Baud Rate register as described in the appropriate section: 3.10.7 for asynchronous mode, and 3.10.8 for synchronous mode.

Table 3-23

Programming the 8251 USART is done by resetting the SIO Board (see Section 3.10.1), then outputting a series of control bytes to the SIO. These bytes are output to I/O address xlH, where x depends upon the board slot occupied by the SIO Board. The control bytes necessary to configure the SIO for a particular mode of operation such as synchronous/asynchronous, number of bits per character, etc., are defined in the specification sheets for this IC, which can be found in Appendix H.

#### 3.10.5 Status

A status byte may be read from the SIO Board by inputting I/O address xlH, where x depends upon the board slot occupied by the SIO Board (see Table 3-22). The composition of this status byte is given in the specification sheets for the 8251 USART, which can be found in Appendix H.

Table 3-24

| Serial I/O Addresses         |              |                                           |  |  |

|------------------------------|--------------|-------------------------------------------|--|--|

| I/O Address<br>(Hexadecimal) | Operation    | Description                               |  |  |

| ХO                           | INPUT/OUTPUT | USART data                                |  |  |

| X1 INPUT/OUTPUT X8 OUTPUT    |              | USART Status/Comman<br>Baud Rate Register |  |  |

| XA                           | OUTPUT       | Interrupt Mask                            |  |  |

#### NOTES

- ◆ The first digit of these I/O addresses is determined by the board slot occupied by the SIO board (see Table 3-22).

- The Baud Rate register may also be accessed by using I/O address x9.

- The Interrupt Mask may also be accessed by using I/O address xB.

- Inputting from I/O addresses x8, x9, xA or xB causes indeterminate data to be loaded.

## 3.10.6 Interrupt or Polled

The SIO Board may be serviced in the interrupt mode or it may be polled by the program.

If the interrupt mode is used, one or more bits of the Interrupt Mask must be set to allow the USART to generate interrupts. The Interrupt Mask is discussed in Section 3.10.4.

When the SIO Board causes an interrupt, the program must determine the source of the interrupt. It does this by inputting from I/O address EOH and checking bit 1. The bit is a zero if any of the I/O boards including the SIO are interrupting. The program then inputs the status of all I/O boards to determine which board(s) is interrupting.

The program decides whether the SIO board has interrupted by comparing the status bits to the bits in the Interrupt Mask. The program can respond by inputting or outputting a data byte, as appropriate, or by simply masking the interrupting condition.

If the SIO Board is to be polled, the Interrupt Mask must be loaded with zeros. The program polls the SIO by periodically reading the status byte from the 8251 USART (see Section 3.10.5) and taking appropriate action.

## 3.10.7 SIO in Asynchronous Mode

## A. Asynchronous Modem Configuration

To establish a communication link between two electronic devices, one device must simulate a modem while the other simulates a terminal. If the ADVANTAGE is to communicate with a serial terminal such as an external CRT, a teletype, or a serial printer, the SIO must be configured to simulate a modem. Similarly, if the ADVANTAGE is to communicate with a modem, the SIO must simulate a terminal.

As shipped, the SIO is configured as a modem; it is ready for immediate connection to an asynchronous RS-232 terminal or a North Star-supplied printer. Connection to most asynchronous terminals and printers requires no configuration changes.

If the SIO has ever been reconfigured as a terminal, it can be restored to its original configuration as follows:

- Remove the Clock Header in board location 1A, if one is present.

- 2. Remove the Configuration Header, board location 3A, and replace it with a 16-pin header wired as shown in Figure 3-7.

Figure 3-7

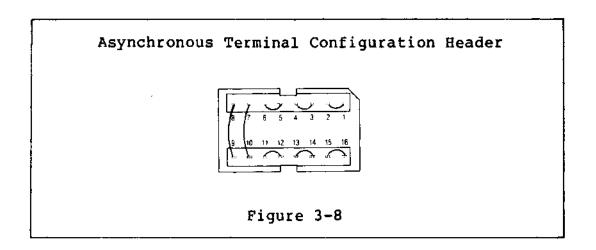

# B. Asynchronous Terminal Configuration

If the ADVANTAGE is to communicate with a modem (or with another computer simulating a modem) the interfacing SIO port must be configured to simulate a terminal.

To configure the SIO as a terminal, proceed as follows:

1. Remove the Clock Header in board location 1A, if one is present.

2. Remove the Configuration Header from board location 3A and replace it with a 16-pin header wired as shown in Figure 3-8.

# C. Current Loop Operation

Whereas most computers, terminals, and printers use RS-232 signal levels, some terminals, such as teletypes, use 20 mA current loop signals.