# **Introductory Manual for Technicians**

#### About this manual:

To my knowledge, this preliminary document is the only version ever produced- I don't believe that a finalized version was published. Because it is preliminary, there are lots of mark-ups, sketches, and corrections that were intended for the final version. These notes were done by the engineers and technicians who were creating the document, so they are valid.

The manuals that were included with computers purchased from MITS did not include this in-house document, so you'll want to add it to any other documentation you already have (however, if you purchased an 8800/8800A manual from altairmanuals.com, you already have this information).

Although it is primarily intended for the earlier models (8800 and 8800A), the manual should be very useful in troubleshooting any Altair 8800 version and any Altair memory board.

Steve Shepard altairmanuals.com 11/2006

altair"

# INTRODUCTORY TECHNICIANS MANUAL

For In-House Use Cally

IDC - Yh Dyn. 4 prom. tests

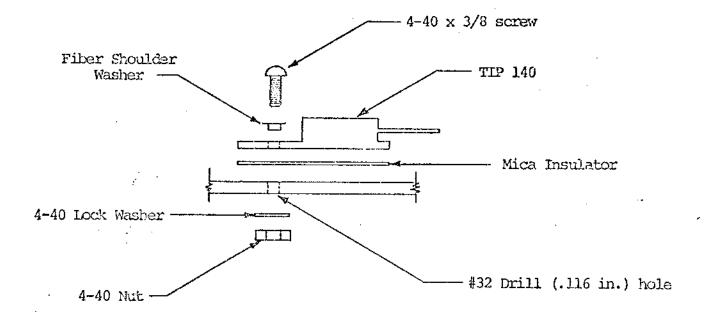

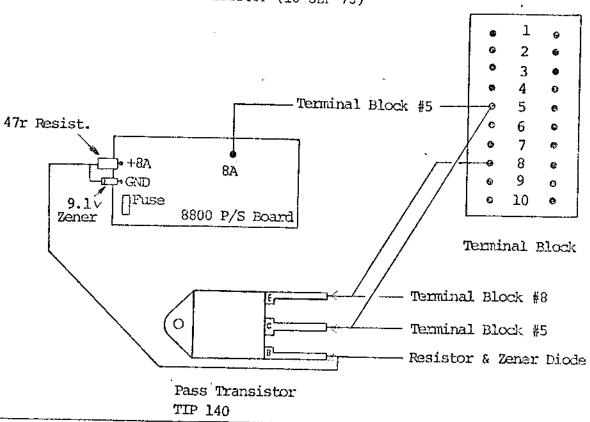

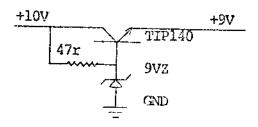

#### 2800 Pass Trans Mod (16 SEP 75) (Assembled Units)

- 1. This Mod should be made on all assembled units using the 10 volt transformer (#6139) 102613.

- 2. Components Used.

| TIP 140 (with mica insulator & fiber washer) | 102819 |

|----------------------------------------------|--------|

| 47r 1W                                       | 101955 |

| 9.1 volt zener (1N4739)                      | 100706 |

| 1 4-408 3/8 screw                            | 100908 |

| 1 4-40 lock washer                           | 100941 |

| 1 4-40 nut                                   | 100932 |

#### 3. CIK:

- a) Make sure acetate (mica) insulator is used with washer.

- b) Clean mounting surface; remove anodize.

- c) Tighten down transistor.

- d) Double insulate transistor leads with heat shrink.

- e) Make sure resistor and zener cannot short to fuse.

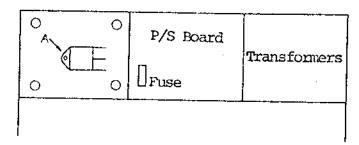

# 8800 P/S Wiring with Pass Transistor (16 SEP 75)

- 1) Drill hole in back cross member at point A using #32 drill (.116 in.).

- 2) Install tip 140 transistor as shown above.

- 3) NOTE: It is best to remove the P/S board from frame to install dicde and resistor. (DO NOT UNDO SOLDER CONNECTIONS.) This is so the underside of the P/S board may be accessed for soldering.

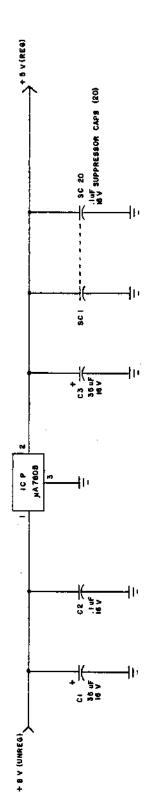

880-108 1K STATIC MEMORY ON-BOARD REGULATOR

#### 8800 BASIC SYSTEM EXPLANATION

A computer is a general purpose tool for processing data. It must have all of the following in order to function: a means of inputting and outputting data, a memory to store the data, a central processing unit (CPU) to manipulate the data, and a program to tell it what to do.

An Altair computer comes with a <u>chassis</u>, a power supply, a CPU, and a front panel with display lights and control switches. To this a person must add at least a memory board and usually an input/output (I/O) terminal. The front panel can be used as a terminal, but has limited usefulness.

In an Altair computer all the circuitry except the 8800a front panel is on PC boards that plug into any hundred pin connector. The connectors are mounted on a "mother board" and all pins are in parallel to each connector so that any board can plug into any connector. However, each board must be plugged in so that when you are facing the front panel the component side of the board is to the right. The connectors are tied to the "Altair Bus". Each line is assigned a particular function and a list of these can be found on page \_\_of the 8800a manual (enclosed).

### Power Supply

The 8800 systems have three unregulated supply voltages developed by the power supply (+8) (+16) and (-16). These voltages are all regulated on each board and delivered by the bus. The +8 line has the heaviest load, since all TTL chips require a +5 supply. TTL circuitry has leakage and bias current. The LSI chips are generally N-MOS and also require -5v and +12v supplies. Since they are field effect chips, they draw proportionately much less current. A check of the regulated voltages is always the first thing to do. It is easiest to check at the output of the regulator or for most TTL chips, pin 14. If the regulator output is wrong, lift the output pin from the board and retest.

The +5v supply must be above 4.8v and have less than .2v ripple. Usually there is more tolerance for the other supplies. They can be checked at the regulator or zener diode as the case maybe. Ground should be treated and measured as a supply voltage. When in doubt, measure the voltage on the chip itself. Always do this if the chip is working improperly.

The CPU

On the CPU board you will see as LSI chip (large scale integrates) labelled "8080A". A small wafer of 40 is silicon under the gold cap is the "brains" of the computer. The rest of the computer can be seen as support for this chip. All data is controlled and manipulated by the thousands of logic gates inside of it. These gates are controlled by a "program".

The CPU's operations are controlled by a two phase clock. This clock runs at 2MHz and is controlled by the crystal you see on the board. CPU is not running or is working erratically, check Ø1 and Ø2 with a level trace scope at any convenient location. Check to see that voltages are right (0-5v or 0-12v depending on where you check); that the frequency is 2MHz and that the relationship between the two phases is correct as shown below.

2200 I 8080

Rise and fall time: 50 nsec. max.

Øl pulse width, 60 nsec. min.

Ø2 pulse width, 220 nsec. min.

delay Ø1 to Ø2, O nsec. min.

delay Ø2 to Ø1, 70 nsec. min.

If the clock does not come on every time the computer is turned on, it may be due to inadequate feedback and a clock mod may be necessary. See accompanying article.

The other LSI chip on this board is the <u>8212</u>. This serves as a <u>status</u> <u>latch</u>. The operation of this chip is detailed in the Intel 8080 manual and we won't go into it here. Since the 8212 is socketed, it is always easy to exchange it with a known good one if the CPU is working badly.

The <u>8080A</u> chip is extremely reliable and unlikely to be a cause of error unless it has been mishandled or subjected to incorrect voltages.

Most of the signals going into or out of the CPU board are buffered by 74367 tri-state drivers (also called 8097's or 8T97's.) There are 6 buffers in each chip. They are amplifiers which isolate each side of the circuit and increase the fan-out capability of each line. These buffers are divided into two groups of 4 and 2. Amps 1-4 are enabled by a low (gnd) signal to pin 1 and amps 5-6 by pin 15. Until these inputs are enabled, the amp acts as a high impedance termination of the line. When enabled, it behaves as a unity gain amplifier. These buffers are a frequent cause of problems. Watch out for noisy buffers and replace them if indicated.

Data is communicated between the CPU and front panel by eight wires and a 10-pin plastic "molex" connector. Two of the sockets in the connector are therefore not used and should be plugged into the CPU with empty sockets toward the center of the board.

# Front Panel Display/Control Board

#### A. Addressing

You will notice a line of 16 lights and switches on the front panel labelled AO-A15. The lights display the location in memory that you are at. The switches allow you to examine any location by putting the appropriate switches up or down and pushing the examine switch. They are grouped in three's

for convenience. This is called "octal notation" because any group has eight possible values. When a switch is up, it has a value of "l", when down a value of "0". Look at the following table.

| $A_2$          | A٦ | $A_0$ | Octal Value |

|----------------|----|-------|-------------|

| A <sub>2</sub> | 21 | 20    |             |

| 0              | 0  | 0     | 0           |

| 0              | 0  | 1     | • 1         |

| 0              | 1  | 0     | 2           |

| 0              | 1  | 1     | 3           |

| 1              | 0  | 0     | 4           |

| 1              | 0  | 1     | 5           |

| 1              | 1  | 0     | 6           |

| 1              | 1  | 1     | 7           |

The address goes from 0-15 instead of 1-16 because each address represents a power of 2. Therefore,

$$A_0 = 2^0 = 1$$

$$A_1 = 2^1 = 2$$

$$A_2 = 2^2 = 4$$

$$A_3 = 2^3 = 8$$

$$A_4 = 2^{4} = 16$$

$$A_5 = 2^5 = 32$$

$$A_6 = 2^6 = 64$$

$$A_7 = 2^7 = 128$$

$$A_8 = 2^8 = 256$$

$$A_{15} = 2^{15} = 65, 536$$

The 8800 is an eight bit machine. This means it can only accept eight bits of data at one time. Therefore, it can recognize  $2^8$  or  $256_{10}$  possible combinations. Since it has 16 address lines, it can directly address  $2^{16}$  or 65, 536 (64K) locations in memory. Eight bits constitute a "byte". Grouping the eight bits in three's (actually 2,3,3) and giving their value in octal vastly simplifies byte description. To wit:

3 0 3

$10\ 101\ 110 = 256_8$

All addresses, instructions and data will be described in this manner from now on.

#### B. Data

The data lights display the contents of memory at the address shown at the address lights. At every address in memory one byte (eight bits) are stored. Data can be stored by setting the data switches in the desired pattern and then hitting the deposit or deposit next switch. The deposit next switch will deposit the data at next address after the one you are at, thereby eliminating the drugery of resetting the address switches after each byte.

(it resets the switches after each

The <u>run/stop</u> switch does exactly that. The <u>Reset</u> switch puts the program counter inside the CPU at zero address. The <u>single step</u> switch allows you to go through a program one instruction at a time. This is useful for debugging. The <u>Protect</u> switch essentially "locks" up a block of memory so that nothing can be accidently written into it, and thereby destroying a program. If the protect light is on, you cannot deposit data until you toggle the unprotect switch.

The upper eight address switches A8-A15 are also called <u>sense switches</u>.

Certain programs utilize data present on these switches for various purposes.

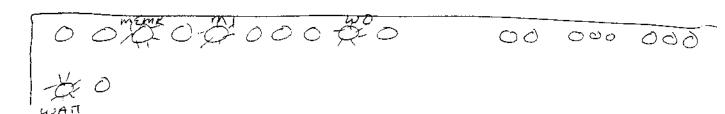

There are twelve status indicator lights on the front panel. We will not go into them in detail here. When the computer is stopped and reset, you should see the following indicators lit.

Wait - the CPU is in a wait condition

MEMR - the CPU is reading data from memory

$\underline{\text{M1}}$  - the CPU is at machine cycle one of an instruction cycle

WO - the CPU is writing out data

If these lights do not come on or if any others are on, you have a problem.

After turning on a computer, always hit stop and reset.

#### C Memory

MITS has several memory boards which differ in capacity and technology, but all are compatible and similar in layout. The actual storage of data is done on a Random Access Memory chip (RAM). All our chips (except on the 1K board) are configured so that they can store one bit at each address. Since there are eight bits to a byte, each board has a multiple of eight RAMs, so it can store a full byte at each address. Let's take a 4K x 1 chip for example.  $4K \times 1$  means it can store 1 bit for 4,096 locations. It requires four power supply connections. Vcc +5v,  $V_{BB}$  - 5v,  $V_{DD}$  +12v and GND. To address 4,096 locations it must have 12 ( $Q^{12}$  = 4,096) address lines. It requires a data in and data out line. It must have an input to tell it to read or write (R/W)

Meric

Buri Glen Villi Ed Curry Lukas Steve

16 Static page 23 t 24 + AH-880C + Th-of-0j

Intact Hart Wayner.

and it has a chip select input. This CS input can be used at the designer's discretion.

Since each board takes up only a fraction of the 64K of memory addressable by the Altair, each board must have an address. The first 4K memory board you put in will be addressed to zero, the second 4K will go to address four thousand, etc. Since 4K is our basic unit of memory, the first board is said to be addressed at zero, the second board is said to be addressed at one, and so on. You will see on each board either a switch or a place to hardwire the address. Here is a handy table. The symbol (—) means low or not.

| Board # | Jumpers                                      | Actual Address | Board # | Jumpers     | Actual Address |

|---------|----------------------------------------------|----------------|---------|-------------|----------------|

| 0       | A15 A14 A13 A12                              | 0              | 8       | 15 14 13 12 | 32K            |

| 1       | <del>15</del> <del>14</del> <del>13</del> 12 | 4K             | 9       | 15 14 13 12 | 36K            |

| 2       | 15 14 13 12                                  | 8K             | 10      | 15 14 13 12 | 40K            |

| 3       | 15 14 13 12                                  | 12K            | 11      | 15 14 13 12 | 44K            |

| 4       | 15 14 13 12 <sup>-</sup>                     | 16K            | 12      | 15 14 13 12 | 48K            |

| 5       | 15 14 13 12                                  | 20K            | 13      | 15 14 13 12 | 52K            |

| 6       | 15 14 13 12                                  | 24K            | 14      | 15 14 13 12 | 56K            |

| 7       | 15 14 13 12                                  | 28K            | 15      | 15 14 13 12 | 60K            |

So, if you wanted a board addressed to 12K, then you would jumper I1 to A12 I2 to A13, I3 to  $\overline{\text{A14}}$  and I4 to  $\overline{\text{A15}}$ .

# 0. Types of Memory

Semiconductor memory systems can be divided into two types: Dynamic and Static.

Dynamic memory is so called because it must be "refreshed" or it will forget. The actual memory cells are MOS devices, some of which are acting as capacitors. These will tend to discharge unless they are strobed every 2 milliseconds or so. By pulsing each row of cells in sequence, they are able to recharge themselves. This type of memory is fast, less expensive, and

requires less power than <u>Static</u> memory. Static memory behaves as if each cell is a switch which can be set high or low. It draws more power and is slower, but tends to be more stable than dynamic. Static memory requires less support circuitry.

#### Specific Memory Boards

As <u>4K Dynamic</u>--The 4K dynamic board was our first large memory board.

Because of some problems associated with it, you will see a great deal of these boards in repair. There is a good article in a past issue of <u>Computer Notes</u> (our company monthly) on troubleshooting this board.

Theory of Operation--Here is  $^{\alpha}_{\lambda}$  brief explanation of how it works.

Refresh--The refreshing is done on inputs AO-A5 of each RAM. ICs T, D and G divide the Ø2 clock by 64. 2MHz results in a 32 microsecond period. IC E then counts up to 64 on lines AO-5. There are 64 rows of cells in each RAM so first row O is refreshed then 1, 2, etc., up to 64. If the computer is running, it will go into a wait state (ready) while refresh is occurring.

This tells the CPU to wait because the memory board is temporarily unavailable.

Read--In order to be read the chip must be selected (pin 5 chip select must be low). This occurs when the board is properly stopped for the address you want to examine. IC J pin 8 is the key point to check.

Chip Enable is a pulse train that allows reading, writing and refresh to occur. This is a <u>key signal</u> and should be carefully checked! Set the scope for 200 ns. sweep, 5 volts/on and positive triggering. Look at the collector of the transistor, pin 17 of any RAM or IC Z, pin 2. Computer is stopped and the board is addressed.

0V = 400 ns > 400 ns > 450 ns >

If the pulses are too wide, decrease R6. If the time between pulses is too wide, decrease R5. Then play around with C4 and C5 as well as ICs H and I. Times given are + 10%.

Data becomes valid after a period of time and appears at the latch (IC N). A strobe to pin 11 latches the data to the output of N which is then available to the CPU.

Writing--For data to be deposited,  $\overline{CS}$  and  $\overline{CE}$  are still required and in addition the Write Enable input (12) must pulse low. This pulse cannot be seen on a normal scope. Data is buffered and inverted by ICs R and Z and appears at data in (pin 6). You can see this with a slow sweep if you try to deposit  $\emptyset$ 's. This is another key test point.

Here is a check out procedure for 4K dynamic:

- 1. Read complaint, if any.

- Visually inspect board for proper components, orientation, shorts, and solder bridges.

- 3. Check to see if board is a Rev. 2. If not, send to production for mods.

- 4. Strap board to zero ( $\overline{A15}$ ,  $\overline{A14}$ ,  $\overline{A13}$ ,  $\overline{A12}$ ).

- 5. If the bypass resistor for  $t^{1/5}$  v regulator is not a 10 ohm, 2 watt, then put one in.

- 6. If any timing capacitor (C2, C4, C5, C3, C1, C18, C22) has this mark on it "

", replace it.

- 7. If H and I are 26L123 chips, R5 should be 15K ohms, R6 30K ohms. If H e5 should be g6 should be and I are 74123s, then 20K ohms and 43K ohms.

- 8. On a pin 10 should be cut from the board, bent over to pin 11 and soldered to it. Insert a .01 uf capacitor between pin 5 and ground. (Protect mod.)

- 9. Insert into test chassis and check the following voltages on any RAM pin 1- $5v_3$  Pin 11-+5v, pin 18-+12 volts.

- 10. Deposit a zero at address 0, deposit D1 high at 0001, D2 high at 0002, Need this D3 high at 0003, etc., and back again. Examine what you deposited and see if it's right.

- Try to load up BASIC from PROM (explained later).

- 12. Try to load BASIC from disk with board strapped to zero (explained later).

- 13. Rowpat test overnight (explained later).

Some Troubleshooting Hints-If all the signals appear to be correct and board still does not work reliably, start changing some of the tri-state buffers (Q, P, P, S).

- If problems do not occur when board is first plugged in, suspect a thermal problem. Try to isolate with a freeze spray and/or heat gun.

- 4. Note that the original schematic is not valid where it involves chips H, L and A due to revisions. There is a supplemental sheet.  $\bigcirc$

- outlined in the <u>Computer Notes</u> article. This is another critical test Notes

- 6. Borrow and copy an annotated schematic from another technician. Do not be intimidated by the complexity of the schematic. Normally you will be dealing only with small sections of it.

- 7. Check to see if you are getting a data strobe on pin 11 of IC N (should pulse every 32 microseconds).

- 8. Check the RAMs for shorts and continuity. All the same numbered pins of each RAM should be common except pins 6 (data in), 7 (data out), 16 (no connection). Put an ohmmeter on high range (X100) and make sure they

are shorted together. Then make sure that no two pins with different numbers are shorted together. This has only to be done on one RAM. Shorts can occur underneath an IC socket. Most of them can be carefully pulled up with a hook-nosed scribe.

- 9. Bring the card edge up to your eye and look for bent pins. Look to see that the legs of capacitors are not shorting any PC braces.

- 10. Check to see that the jumpers are correctly installed by comparison with a known good board. Note that they do not all go to their labelled positions (esp. JG, J2 and J10).

- 11. If you find a bad RAM, move it to a different location to see that the socket is not the cause.

- 12. Do not hesitate to ask more experienced technicians for advice.

- 13. When in doubt about what you should be seeing a given point, compare it to a known good board.

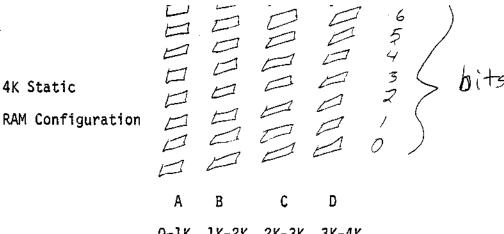

#### 4K Static Board and 16K Static Boards

I will not go into detail on these boards. Both have good troubleshooting sections in their respective manuals. There is also an article on trouble-shooting 16K boards in the <u>Computer Notes</u>. Most of this information is applicable to both boards.

The 88-S4K Dynamic Memory Board is a new replacement for the 88-4MCD Dynamic Board. It incorporates some new circuits to alleviate the timing problems associated with the 88-4MCD Board; and therefore, takes some explanation of operation.

The 88-4MCD Memory Board uses an asynchronous system for generation of refresh, chip enable, and PRDY pulses. The 88-S4K board uses the same signals, but derives them from existing signals in a manner which synchronizes them and ensures their timing specifications.

Basically the board consists of 8 4K x 1 bit Dynamic RAM memory chips with associated address and data buffers. (ICs EE, DD, CC, JJ, HH, BB, and AA). ICs EE and AA being address buffers; IC BB being an address inverter, and ICs DD, CC, JJ and HH being data buffers. ICs GG and FF are latches which latch data read from the RAMs on the falling edge of the STB pulse.

Board Decoding for Board Enable is done from address lines A12 through A15 which selects boards in increments of 4K blocks. IC W inverts these lines for the  $\overline{A}$  select position and switch S1 selects  $\overline{A}$  or A. If the board is selected, all inputs at IC V will be low, causing a low on  $\overline{RCS}$ , selecting the RAMs. This low is also routed to IC D for use in protect circuitry. The output of V is also inverted and fed to IC G for use in Refresh, Chip Enable, and STB. This output is also used to enable the Protect Status and the  $\overline{PRDY}$  buffers.

The actual refresh generation is complicated and is explained in the Theory of Operation Manual. It basically consists of a counter to determine the refresh address and two generators depending on mode of operation.

The only problems found with the board at this time are not too complicated. The first problems to be aware of are of a physical nature. Check all despiking capacitors to insure that they have been installed in the proper holes. Check for solder bridges, ICs partially out of the socket (or board), and proper orientation of all components. One silkscreen error is on the board on Transistor Ql. The marking for the emitter is wrong, but just make sure the flat side of the transistor is facing the bottom of the board.

We have experienced some problems with the protect circuitry. If the board is selected and you cannot protect or unprotect the board, check ICs U, and D and Diode D2. IC D is configured into an RS flip-flop and a state changes is caused by driving either pin 2 or 112 high depending upon condition. IC D is the most suspect. If the board comeson protected from power on; check

to see if it will come on protected at a position other than the O position. If it does, check ICs U, T and D, or dode D2. If not, do a protect mod which consists of a diode from IC T, pin 2, to IC D, pin 12, with the cathode end at D12. This mod may be made in either power on instance.

The only other problem is that the board may not work with certain other boards in the chassis, including a PROM board with Monitor or a 1K static. To cure this problem, a modification can be made to generate a refresh pulse during a wait state in order to refresh during operations involving slow memories. This modification is included.

### How to use the 8800 computer.

- Check to see that you have the necessary boards in the chassis.

- a. CPU board correctly plugged in.

- b. Adequate memory for what you want to do. The boards must be strapped consecutively starting at zero. You <u>cannot</u> have two boards at the same address. You need this amount of memory for the following:

- front panel tests-minimal

- ii. 4K BASIC PROM-4K

- iii. 8K BASIC tapes-8K

- iv. Extended BASIC tapes-12K

- v. Disk-20K

- vi. Rowpat-one 4K strapped to zero and the boards to be tested anywhere else (except 15 when using PROM)

- c. The correct I/O board for the terminal you are using:

- i. CRT or Compter-SIOA or 2SIO strapped for RS-232

- ii. Teletype-SIOC or 2SIO strapped for TTY. Check your baud rates and I/O addresses. Always connect cable so that black wire (ground) is at pin 4 (from left). Use the <u>right</u> cable!

- d. Do you need a PROM card for a bootstrap?

- e. Do you need the disk controller cards?

- 2. Are all cards plugged into the mother board correctly?

- 3. Turn on computer.

- 4. Lift stop and reset switches. Is status correct?

5. You are now ready to roll. The computer is waiting to be told what to do.

<u>Using the PROM cards</u>

A PROM is a Programmable Read Only Memory. When you turn off the computer, the memory does not die. The data in them is for reading only and can be altered only by special devices. PROMs are normally addressed to the top end of memory. On the PROM is a program to write data into a RAM and/or to tell a computer how to start going about its business. Such information as how the computer is going to input and output data. This is called a bootstrap. When you have your computer ready to go, merely send the computer to the starting address in the PROM by the address switches and hit RUN and the computer is ready for a program. The most frequently used PROMs are used as follows:

- 7. A15-A8 up except A9

- 2. Examine this address

- 3. You should see 041 (00100001) on data lights

- 4. Put down switches A15-A12 (if using a 2SIO board, leave A15 up)

- 5. Hit RUN

- 6. Terminal device should print out "4K memory test . . . which board to test, 1 = 4K, 2 = 8K, 3 = 12K . . . "

- 7. At this point you can either push the "C" key and the computer will cycle through each board continuously or you can type the number of the board you wish to test (1-14) and it will test that board one time.

- 8. After testing a board, the computer will say "And that's it"

- 9. To stop the computer, hit STOP

- 10 .Turn off power before removing any board!

If an error occurs, it will print something like "error address 031247 bad bits 5". This address is in octal in the same way the front panel switches are arranged.

#### For our example:

| Value                   | 32K                                                         | 16K | 8K     | 4K 2K  | 1K  | 512 | 256 | 128 | 64 | 32 | 16  | 8  | 4 | 2  | 1 |

|-------------------------|-------------------------------------------------------------|-----|--------|--------|-----|-----|-----|-----|----|----|-----|----|---|----|---|

| Address line            | 15                                                          | 14  | 13     | 12 11  | 10  | 9   | 8   | 7   | 6  | 5  | 4   | 3  | 2 | 1  | 0 |

| Sample Address (octal)  | 0                                                           | -   | 3      |        | 1   |     |     | 2   |    |    | 4   |    |   | 7  |   |

| Sample Address (binary) | 0                                                           |     | 011    |        | 001 |     |     | 010 |    |    | 100 |    |   | 11 | 1 |

| Decimal Value           | 8K+4K                                                       | +   | 512    | +      | 128 |     | +   | 32  | +  |    | 4+2 | +7 |   |    |   |

|                         | = 8192<br>4096<br>512<br>128<br>32<br>4<br>2<br>1<br>12,967 |     | imal a | ddress |     |     |     |     |    |    |     |    |   |    |   |

From this we can tell that the failure is at board 3 (0-4K = 0, 4K-8K = 1, 8K-12K = 2, 12K=16K = 3) and that it is at decimal address 967 of this board. If the board was a 4K static, which has 4 rows of 1,000 bytes each, we would know that the failure was in row A at bit 5 (the computer told us that earlier).

0-1K 1K-2K 2K-3K 3K-4K

At this point you would examine this chip and see if all pins were in the socket well. If a bent pin is found, you would straighten it and retest. If not, interchange bits 5 and 6 and retest. If it fails again at the same address with bit 6 bad, then the chip should be replaced and the board retested. If something else happens, it was probably a socket problem. DISK Boot Loader-This PROM loads the program that loads the Altair Floppy Disk. This is mass memory storage device. To load up a disk, do the following:

- Check to see that the Disk controller boards are in the Altair and that their cable is properly plugged into the disk drive cabinet.

- 2. Check to see that a disk is properly installed into the drive unit (label goes to top, right corner nearest you).

- 3. You need 20K of memory starting at 0.

- Turn on disk drive. 4.

- 5. Reset computer and set address switches A15-A8 high.

- 6. Examine this address, 041 should appear on data lights.

- 7. Put all address switches down (unless you are using a 2SIO as the I/O board. In that case, leave All high),

- Hit run, disk drive should click and all lights come on. 8.

- After a few seconds, the terminal should say:

Terminal

Your Response

Memory size?

Hit return button on keyboard

Terminal width?

Same

How many files?

Same

How many random files?

Same

It will then print out some information about the Disk Extended BASIC and finally print "OK". At this point you can start writing a program in BASIC. If you wish to read or write on the disk, you must "mount" it.

Type mount and hit return.

After about 10 seconds, it will print out OK.

- 2. If you want to know what is written on the disk, type files and hit return.

- 3. If you want to load a file into memory so that you can run it, type #LOAD ANYFILE YOU WANT" and hit return.

- 4. After it prints OK, type RUN and hit return.

#### WARNING

When the head is loaded, you cannot turn off the Altair. In order to unload it, type \*OUT 8, 128 and hit return. If that doesn't work, load this program:

Examine 0

Deposit 076 at zero

Deposit next 200

Deposit next 323

Deposit next 010

Examine 0

Reset

Run stop

The disk enable and head load lamp should go out.

4K BASIC PROM -- This PROM board loads a short version of a high level language directly into memory.

- 1. Switches A14, 11, 10, 9, 8 up (upper level address 057).

- 2. Examine-should be 041 on data lights.

- 3. Switches down-hit run,

- Terminal should print out "SN ERROR".

- 5. Type RUN and hit return and it will come back with "100 elements 1, 2, 3, 4" and keep counting. You can stop it by pushing the "C" key and the control key at the same time.

- 6. After step 4 or 5, you can write a simple BASIC program to test the board. For example:

10 x = 1 set on initial value for x 20 Print x, SQR (X) Print out X, then compute the square root of X and print that

30 X = X+1 Make X = equal to the previous value + 1

40  $\frac{60000}{60000}$  Go to statement 20 and print the new X and its square root

When you type RUN and hit return, you will see:

#### RUN

- 1 1

- 2 1.414

- 3 1.732

- 4 2

etc., This program is a loop and will run forever if not stopped by the operator.

#### 88-S4K Memory Board

#### Addenda Page

#### November, 1976

In order to make the 88-S4K Memory Board compatible with memory boards that use wait states (the 88-PMC or the 88-IMCS), the following modifications must be implemented. If neither of these boards are used, the modifications are not necessary. If your 88-S4K board was factory assembled, it can be returned to the factory for installation of these modifications. The only customer charge will be shipping costs.

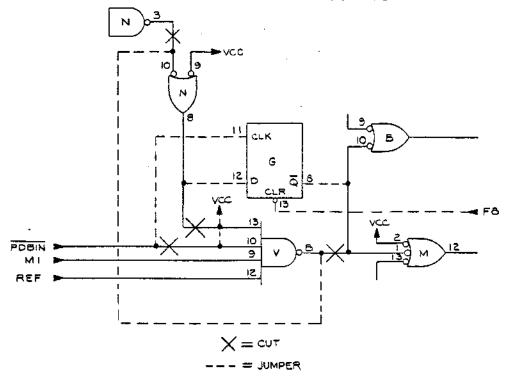

- 1. There are four lands on the silkscreened side of the S4K board that must be cut. One land comes off IC N, pin 3. The other three come off IC V at pins 10, 8 and 13. The small arrows in Figure 1 point to each of the lands and small "x's" designate the exact points at which the lands should be cut.

- 2. There are six jumper connections that must be made on the back of the S4K board. They are:

- a) V10 and V13 to +5v (V14)

- b) K3 to G11

- -c) N8 to G12

- d) V8 to N10

- e) G8 to M1

- f) G13 to F8

The locations for these connections are shown by the screened lines in Figure 2.

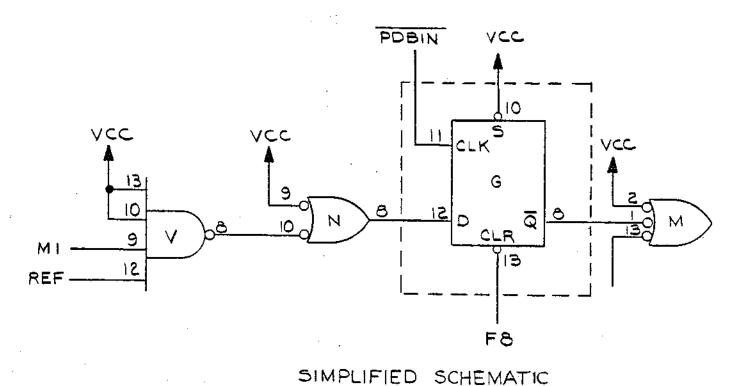

Refer to Figure 3 for a simplified diagram of where the land cuts and jumper connections should be made.

Figure 4 shows how the board should look when all of the modifications have been completed.

CUT VA, VIO, VI3 ¢ N3

JUMP VIO ¢ VI3 TO VCC

JUMP K3 TO GI1

JUMP NA TO GI2

JUMP VA TO NIO

JUMP GA TO MI & BIO

JUMP GIS. TO FA

Figure 3. Simplified Schematic

SCHEMATIC CHANGE

igure 4. Simplified Schematic with Completed Modifications

# REPAIR INFORMATION RECORD

NOTE: This is for the purpose of collecting data to be incorporated into a troubleshooting manual for MITS equipment. Please be precise and as detailed as possible. Turn this sheet into Tech. Writing when filled.

| UNIT            | PROBLEM/SYMPTOMS                                                                         | . SOLUTION/COMMENTS                                                                      |

|-----------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| FRONT<br>PANEL  | WON'T STEP AFTER RUNTAR -                                                                | > ONE END OF 31 CONNECTED IN WALKS THEE > LINE 79 CONNECTED TO WRONG AND ON MOTHER BOARD |

| CPU             | WRITES ON - OCO ALTERNATELY THRUGGT MEMIRY AFTER RUN REGARDLESS OF PROBREM               | I C "O" BAD                                                                              |

| CPU             |                                                                                          | C3 Connected to Washe PAD LC"Q" BAD                                                      |

| FRONT ANEL      | BAD STATUS                                                                               | → IC'X PINS 15416 SHORTED                                                                |

| 1 K<br>memozy   | PROT. UN PROT SWITCH<br>OPERATES IN REVERSE                                              | IC "N" BAD                                                                               |

| FRONT<br>PANEL  | EXAM NXT,<br>DEP NXT FLAKY                                                               | Noisy Switches                                                                           |

| CPU             | MHEN BOTH SWITCHES ARE                                                                   |                                                                                          |

| FRONT<br>PANEL  | RANDOM RUN-PSYNC<br>WON'T STOPENUSME PRAY<br>TO PULSE HI, R/S WERKS<br>BOT HOS NO EFFECT | PINS 124 13 ON IC'M'                                                                     |

| FRONT<br>PANEL  | NO EXAM FLARY BUN<br>EXAM NX+ WORKS                                                      | IC'S "U"+" J * BAD                                                                       |

| FRONT<br>PANEL  | FLAKY RUN, STOPS<br>WHEN CPU PLUG IS REMODE<br>& STOPEST IS HIT.                         | C7 SHOR-IED to ICG PIN 9                                                                 |

| 1 K<br>memory   | WASN'T DISABLING OUTPUT<br>DRIVERS WHEN YOU EXHAUR<br>OUT OF MENTERY                     |                                                                                          |

| FRON'T<br>PANEL | AFTER KUN (FLAKY TYPE RUN) IT Whatefr 1 +000 THREET MEMERY WOLLN'D WERE PREGRAMS         | THRU I C X                                                                               |

# REPAIR INFORMATION RECORD

NOTE: This is for the purpose of collecting data to be incorporated into a troubleshooting manual for MITS equipment. Please be precise and as detailed as possible. Turn this sheet into Tech. Writing when filled.

|                | iea as possible: 1411.                                                                                | SOLUTION/COMMENTS                                                                                  |

|----------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| UNIT           | PROBLEM/SYMPTOMS                                                                                      |                                                                                                    |

| FRONT PANEL    | EXAM INCREMENTS IN<br>3 STEPS INTO FLAKY RUNT-<br>BACK, EXAM UXT AEPNAT<br>DON'T COUNT (DISALAY)      | TETZ BAS NOT LETING PSINC                                                                          |

| Сро            | BAD STATUS                                                                                            | BREAK IN FOIL FROM PINIO FO'<br>TO LOF HT & ALSO BREAKIN FOIL<br>FROM PINIS OF STO POLL OF CIRCUIT |

| CPV            | PROGRAMS INVOLVING<br>SENSECUSITENSS<br>WOLLD'S WOCKE                                                 | BREAK IN FOIL FROM PIN<br>8 OF ICB' to GRAD                                                        |

| FRONT<br>PANEL | WOULD'ME EXAM EX LYT DEP OR DEP NXT. NO PULL COMMY FROM ANY OF THE SWITCHES                           |                                                                                                    |

| Cpu            | RANDEM EXAM<br>Etc.                                                                                   | PIN/I OF ICH SHOPPED TO PIN<br>70F IC"Q"                                                           |

| Cpu.           | DAD STATUS                                                                                            | BAD XTAL                                                                                           |

| FRONT<br>PHEL  | NO EXAMINE EVERYTAINS ELSE WORKS                                                                      | BAD SWITCH.                                                                                        |

| FRANT<br>PANEL | EVERYTHING WORKS EXCEP<br>EXM. WHED EXECUTED<br>AIS-AT LIGHT + STAYLIT<br>WHILE AT-A O FUNCTIONS O'LL | HOLDING CONFERENCE PENN                                                                            |

| FRONT<br>PANEL | DEP NXT CIRCUIT WAS ACTING LIKE IT WAS EVAN ENLY IT DID DEPOSIT. ALSES OUT OF F" WERNT ALDROIGH       | TIME CONSTANT COMPTONIA                                                                            |

| PRONT<br>PANEL | DEF NXT COUSED ALL DATE LIGHTS TO COME ON MESSE UP STATUS, AND AD NEUCH CAME ON WHILE COUNTING.       | h "F" to LAND I AND DED IZE                                                                        |

|                |                                                                                                       |                                                                                                    |

|                | · ·                                                                                                   |                                                                                                    |

# REPAIR INFORMATION RECORD

NCTE: This is for the purpose of collecting data to be incorporated into a troubleshooting manual for MITS equipment. Please be precise and as detailed as possible. Turn this sheet into Tech. Writing when filled.

| UNIT            | PROBLEM/SYMPTOMS                                                                           | mis sheet into Tech. Writing when fill        |

|-----------------|--------------------------------------------------------------------------------------------|-----------------------------------------------|

| MEMORY          | WOOLD NOT                                                                                  | SOLUTION/COMMENTS                             |

| IK              | DEPOSIT                                                                                    | WRONG PLACE                                   |

| MOTHER<br>BOARD | MOULD NOT DEPOSI<br>IN OR EXAM. 1ST MEN<br>LOCATION. DI-D7 ALL<br>LIGHT WHEN AR IS EXAMIN  | 1. 37 + WIRE to FRONT PANEL                   |

| MEMORY          | DX+D2 bep. Only<br>when Both Switches<br>ARE Up.                                           |                                               |

| FRONT<br>PANEL  | EXAM. CNLY EXAMS ADRESS 70: EXAM OXT DEP NXT NOT FUNCTIONING ONSTABLE STATUS               | PIN 74 PINS ON IC"S"                          |

| CPU             | RANDOM EXAMINE                                                                             | I C "R" BAD.                                  |

| FRONT<br>PANEL  | WCN'+ EXAMINE A+ ALL                                                                       | Ic"L" BAD                                     |

| FRONT<br>PANEL  | A7 + A15 STAY<br>LIT ALL THE TIME                                                          | LINE to D7 ON FRONT PANEL BROKEN              |

| FROUT<br>PANEL  | Al would Not<br>Light                                                                      | LINE to 79 ON FRONT<br>PANEL BROKEN (A) LINE) |

| FRONT<br>PANEL  | WHEN EXAMINING,<br>78-AIS WOULD LIGHT +<br>STRY THAT WAY. WHILE<br>AO-A7 FUNCTIONED NORMAL | Ic "U" BAD                                    |

| FRONT<br>PHNEL  | EVERYTHING WORKS EXCEPT PROGRAMS EXCEPT PROGRAMS EXCEPT PROGRAMS                           | IC'T" BAD                                     |

| PU              | NO EXAMINE                                                                                 | Ic'0+"R"                                      |

| ρυ              | DEDOSIT NOT                                                                                | D5 LINE OPEN                                  |

V111111117 110 5015

This is for the purpose of collecting data to be incorporated into a troubleshooting manual for MITS equipment. Please be precise and as detailed as possible. Turn this sheet into Tech. Writing when filled.

|                 | tea us possibles 1m1.                                                                         |                                                     |

|-----------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------|

| UNIT            | PROBLEM/SYMPTOMS                                                                              | SOLUTION/COMMENTS                                   |

| CPU             | RANDOM RUN<br>DON'T STOP PSYNC<br>ACTING LINE ITS SHOREFED TICKED                             |                                                     |

| FRONT           | MOULD NOT DEPOSIT  141 FEW SECONDS AFTER  MACHINE WAS TURNED ON IT  WOULD AFTER THAT NO DICE! | DUTPUTOF IC N' High,<br>HOLDING IC "G" IN ONE STATE |

| FRONT           | DETERMENT EXAMINE                                                                             | SSW DSD GROUNDED GROUND.                            |

| <u>C</u> Pu     | A3, A4, ON A5.                                                                                | IC B" BAD                                           |

| MOTHER<br>BEARD | Dr Westo not light                                                                            | DAN CONNECTION BETWEEN<br>QPU + MIEMORY BOARDS      |

| FRONT<br>PANEL  | NO RUNSTOP<br>FUNCTION                                                                        | Ic "S" DAD                                          |

| FRONT<br>PANEL  | Deposits ALL 1's                                                                              | C8 . 001 INSTEAD CF . 1                             |

| FRONT<br>PANEL  | RANDOM RUN                                                                                    | I c" N" WAS A 7414 INISTEAD OF A 74L00              |

| FRONT<br>PANEL  | RANDOM EXAM, EXAM<br>NXT. DEP. NEXT.                                                          | IC"N" IN IC"E" PLACE<br>+ VICE VERSA                |

| Pewer<br>Supply | TERT TEB NOT                                                                                  | POUR SUPPLY.                                        |

| Flowf<br>Ornel  | EXAM INCREMENTS IN Y STIEPS IN TO RUN TO OTHER FLAKY MODES REPETITIOUS LY                     |                                                     |

| FRENT<br>FANEL  | RANDOM EXAMINE<br>OR NO EXAMINE                                                               | Tells out but (Pinst)<br>OSCILLATINE                |