### XPU-80

A Z-80 Processor With Memory Management for the S-100 Bus

Copyright January 1982 Ithaca Intersystems, Inc Edition 1

| COPYI      | RIGHT | NOTICE                                 | ii               |

|------------|-------|----------------------------------------|------------------|

| 1.0        | INTRO | DUCTION                                | 1                |

|            |       | PHYSICAL DESCRIPTION                   | 2<br>2           |

|            | 1.2   | FEATURES                               |                  |

|            | 1.3   | SYSTEM INTEGRITY                       | 3<br>3           |

|            |       | 1.3.1 Memory Management                |                  |

|            | Q.    | 1.3.2 Real Time Clock                  | 4                |

|            |       | 1.3.3 Hardware Kernel                  | 4<br>5<br>5<br>7 |

|            |       | 1.3.4 Error Detection                  | 5                |

|            |       | FIONAL OVERVIEW                        | 10               |

|            | 2.1   | BLOCK DIAGRAM                          | 7                |

| 1.0.000.00 | 2.2   | CENTRAL PROCESSOR UNIT                 | 8                |

|            | 2.3   | CLOCK GENERATION                       | 8                |

|            |       | REAL TIME CLOCK                        | 9                |

|            |       | STATUS LOGIC                           | 10               |

|            |       | CONTROL SIGNALS                        | 11               |

|            |       | 2.6.1 Control Output Bus               | 11               |

|            |       | 2.6.2 Control Input Bus                | 12               |

|            | 2.7   | FRONT PANEL INTERFACE<br>RESET CIRCUIT | 13               |

|            | 2.8   | RESET CIRCUIT                          | 14               |

|            | 2.9   | WAIT STATE REQUESTS                    | 15               |

|            | 2.10  | DMA                                    | 15               |

|            | 2.11  | PARITY AND BUS ERROR                   | 17               |

|            |       | 2.11.1 Parity                          | 17               |

|            |       | 2.11.2 Bus Error                       | 17               |

|            |       | ERROR LATCH                            | 18               |

|            | 2.13  | EPROM                                  | 19               |

|            |       | 2.13.1 MMU Initialization              | 19               |

|            | 2.14  | MEMORY MANAGEMENT UNIT                 | 20               |

|            |       | 2.14.1 Address Translation             | 21               |

|            |       | 2.14.2 Attribute Byte                  | 23               |

|            |       | 2.15.3 MMU Enable                      | 23               |

|            | 2.15  | PROCESSOR CONTROL REGISTERS            | 24               |

|            |       | AND REQUESTS                           |                  |

|            |       | INTERRUPT DEVICE                       | 26               |

|            | 2.17  | SUPERVISOR/USER                        | 28               |

|            |       | 2.17.1 Leaving the Supervisor          | 28               |

|            |       | 2.17.2 Returning to Supervisor Mode    | 29               |

|            |       | SERVICE NET                            | 30               |

|            |       | BUS I/O                                | 30               |

| 3.0        |       | D SETUP                                | 31               |

| <b>F</b> 0 | 3.1   | FRONT PANEL OPERATION                  | 33               |

| 5.0        |       | AL APPLICABILITY AND BOARD REVISION    | 34               |

| 6.0        | PART  | S LIST                                 | 34               |

8~89X

- i -

MOITON THDISYLDS

1.1 PHYSICAL DESCREPTION 1.4 FRATURES

|                      | COPYRIGHT NOTICE             |      |    |   |

|----------------------|------------------------------|------|----|---|

|                      | COPYRIGHT NOTICE             |      |    |   |

|                      | 1.3.4 Error Decect           |      |    |   |

|                      |                              |      |    |   |

| Wherever referred    | to throughout this manual,   | Z-80 | is | а |

| registered trademark | of 7ilog Inc                 |      |    |   |

|                      | AVII COMPREME AVANA STA      |      |    |   |

|                      | 2.4 BEAL TIME CLOCK          |      |    |   |

|                      | 2.5 STATUS LOGIC             |      |    |   |

|                      | 2.6 CONTROL STGUALE          |      |    |   |

| 11 xu8 34            | 2.6.1 Control Outpu          |      |    |   |

| 5.1 Burg 1.2         | 2.6.2 Control Input          |      |    |   |

|                      | 2.7 FRONT PANEL LETENFAL     |      |    |   |

|                      | 2.8 RESET CIRCUIT            |      |    |   |

|                      | 2.8 WALT STATE REDUESTS      |      |    |   |

| 24                   | 2,10 DMA                     |      |    |   |

|                      | 2.11 PARITY AND BUE ERROR    |      |    |   |

|                      | ALTER LATES                  |      |    | 6 |

|                      |                              |      |    |   |

|                      |                              |      |    |   |

|                      | X+1 / 图理的公司                  |      |    |   |

|                      | CELEVISION AND ALL'S         |      |    |   |

|                      | (I) TUBMERARAN VALUEN FL.S   |      |    |   |

|                      | 2.14.1 Addrens Trans         |      |    |   |

|                      | 2.14.2 Attribute By          |      |    |   |

|                      | 2.15,3 MM L Englis           |      |    |   |

|                      | 1.15 PROCESSON COMPREL PI    |      |    |   |

|                      |                              |      |    |   |

|                      | SOLARD THEREESE ST. S        |      |    |   |

|                      | 3-113 SUPERVISOR/USER        |      |    |   |

|                      | s and parveal 1,51.5         |      |    |   |

| SUDERVIADY MODE 79   | 2.17.2 Recurning to          |      |    |   |

| 632                  | 1.10 SERVICE NET             |      |    |   |

|                      | 2.19 BUB 1/0                 |      |    |   |

| LE WO                | LUIZA GRADE U.E              |      |    |   |

|                      | 1.1 PRONT PANEL OPERATIC     |      |    |   |

| BOARD REVISION 34    | 5.0 MANUAL APPLICABILITY AND |      |    |   |

| 3.4                  | TELL EARTS LIST              |      |    |   |

|                      |                              |      |    |   |

The Ithaca Intersystems XPU-80 board is based on the ZILOG Z-80B (TM) processor and features built-in memory management.

The XPU-80 is a processor for 8-bit S-100 bus systems, and is oriented toward medium to large system support. The integration of the memory management enhances support of multi-user multi-tasking environments. The XPU-80 provides basic system features such as full S-100 bus support, optional wait states, optional MWRT generation, and provision for high speed (6 MHz) operation.

This manual provides the information required to prepare, install and operate the board in a system. The manual includes an introductory section, a functional overview of the board's operation, setup instructions for the board, a programmer reference section, and the board parts list.

The functional overview section of this manual contains a complete discussion of each functional section of the XPU-80 board.

- 1 -

Latenan that store writer information Compatibility with Flore Panel

### 1.1 PHYSICAL DESCRIPTION

The XPU-80 board is a standard 5 by 10 inch (12.7 by 25.4 cm), S-100 bus, plug-in circuit board. 1.2 FEATURES, and any average apts 1 of multisem the second to the second as the method and the second as the seco aulti-user milti-testing environments. The XPU-8: provide The XPU-80 board contains the following features: wait states, mutain MWRT generation, and provision for high 6 MHz operation (Optional 4 MHz operation with no wait states) Parity error checking and sebleated labore labore and \* User/Supervisor Mode

\* Hardware/Firmware can detect and correct errors \* Hardware/Firmware can detect and correct errors \* A signal LED that can signal messages under software reference section, and the board parts list. control + Processor slow-down software selectable wait states \* A page type MMU (Memory Management Unit)

\* Board I/O space can be doubled with hardware from 256 to 512 ports the state Latches that store error information

\* Compatibility with Front Panel

XPU-80

### 1.3 SYSTEM INTEGRITY

Spoll Buyit (Logi)

The XPU-80 board contains a variety of features that enhance system integrity.

cime-out directle is used if the system is hung up by a user

### 1.3.1 Memory Management

The memory management unit (MMU) provides two functions essential to advanced system control: memory address translation and attribute checking.

The XPU-80 hardware can provide absolute protection between the users and between the supervisor and user spaces.

In practice, the operating system determines the degree of protection provided.

In a typical application, the supervisor mode can be used such that only trusted operating code is run in the supervisor space (with potentially unreliable user code excluded from the space), users can be prevented from executing I/O, and controlled re-entry to the supervisor mode from user space can be ensured. The Supervisor/User Circuit (S/U) provides for controlled transfer between supervisor and user spaces.

Running system disgnmetics stored in EPREM Manspire but manning pages Slowing the system down by introducing one of two walt states into svery processor cycla Signaticuty on error with the board LD Dignalizing an error of the terminal

XPU-80

- 3 -

HUNG 201 (H774-H

### 1.3.2 Real Time Clock

The XPU-80 Real Time Clock (RTC) provides timing for several functions. A 1 Hz clock is output to the time out circuit, and optionally to the interrupt controller Int 5 input. The time-out circuit is used if the system is hung up by a user that has disabled interrupts. 1.1.1 Memory Management

A 50 Hz clock is output to the interrupt controller Int 3 input to provide a real time reference. The 50 Hz tick marks provide a timing reference for time keeping, task swapping, switching between users, and alternating between foreground and background tasks.

The XPU-80 hardware can provide absolute protection between the users and between the supervisor and user spaces.

### 1.3.3 Hardware Kernel

In practice, the operating system determines the degree of The Z80 processor (in Supervisor Mode) and EPROM constitute a hardware kernel that initializes the system and can perform self-diagnostics and error recovery. The hardware kernel is likely to be functional even if the system is down, providing a degraded level of operation, or in the event of major system failure, an indication of the source of the failure.

controlled re-matry to the supervisor mode from user space os The kernel can respond to system errors with a combination of the following responses. A real visque asserted interest ballo

- Running system diagnostics stored in EPROM

- Remapping bad memory pages . Slowing the system down by introducing one or two \* wait states into every processor cycle

- Signalling an error with the board LED

- Signalling an error with the terminal

XPU-80

1.3.4 Error Detection

The XPU-80 hardware provides several levels of error detection during normal system operation. A generalized error signal is used as an interrupt source.

Parity Circuit

The XPU-80 supports the Intersystems parity scheme. The XPU-80 parity circuit transmits parity on all writes and checks it on reads if PAREN\* is asserted by a board on the bus. (Parity is not checked during EPROM, Processor Control, or MMU operations.)

Bus Error

Bus line 98, ERROR\*, is monitored. The status signal indicates an error condition during the current bus cycle. When active, the signal becomes an interrupt source for the interrupt controller.

Power Failure

PWRFAIL\* (line 13) can be monitored. The signal indicates a power failure on the bus.

MMU Error

MMU Error is generated by an attribute violation.

ATTACK ASSAL PROVIDE A PROPERTY

- 5 -

Holdpalad lorns M.C.I

The XPG-80 hardware provides saveral levels of arror detection during normal system equivalent. A generalized struc signal is nard as an interrupt source.

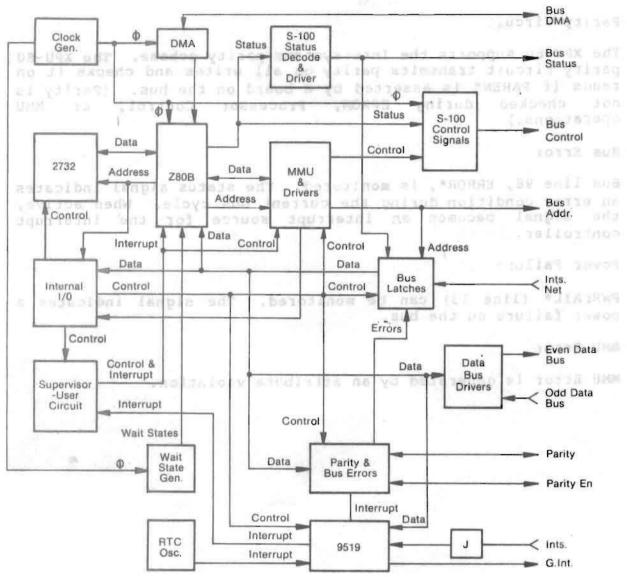

Figure 1 XPU-80 Block Diagram

XPU-80

6 -

### 2.0 FUNCTIONAL OVERVIEW

This section of the manual provides an overview of the operation of the XPU-80 circuit card. The XPU-80 is designed to operate as the permanent bus master in a S-100 bus microcomputer. As permanent bus master, the board is responsible for the initiation of all bus cycles, and for the generation of all signals necessary for the conduction of an unambiguous bus cycle. Bus control can be transfered from the permanent bus master, in this case the XPU-80, to a temporary bus master, a DMA device, as defined by IEEE 696 protocol. An example of a temporary bus master is the FDC II (floppy disk controller) board. The XPU-80 operates in a system with one or more bus slaves.

The XPU-80 operates in a system with one or more bus slaves. A bus slave is a circuit board that monitors all bus cycles, and if addressed, accepts or sends the message on the data lines. The bus slave examines and generates only those bus signals necessary to communicate with the bus master. An example of a bus slave is the 256KDR memory board.

The major functional areas of the XPU-80 board are described individually. Each functional description includes an explanation of what the functional area is, what it does, and how it works.

In several circuit descriptions distinction between S-100 bus and processor board signals with a common name is made by adding the designation XPU-80 to the signal name. For example XPU-80 RESET\* is the board reset signal.

the suc puts, this shirts 10 states our ball cycld

2.1 BLOCK DIAGRAM

The XPU-80 board is a CPU board. The CPU board consists of a CPU (see 3.2) and the logic elements required to allow tranmission of data between the CPU chip and external devices, to provide the clock generating timing signals required by the CPU, and to manage where data is to be read or where data must be sent.

The block diagram in Figure 1 is a graphic representation of the XPU-80 board. The diagram shows the major functional elements of the board as blocks. The lines connecting the boxes indicate the paths, along which information and/or control flows, between the functional areas. A block diagram is a guide to understanding the interrelationship of the functional areas described in this section of the manual.

PROCEASON

- 7--8

2.2 CENTRAL PROCESSOR UNIT

The CPU of the XPU-80 board is a Zilog Z-80B. The Z-80B is a 40-pin MOS/LSI chip, capable of operating at up to 6 MHz. The XPU-80 board is configured at the factory to operate at 6 MHz.

2.3 CLOCK GENERATION tol that told the story of a clistered

A clock is a repetitive signal used to time or control (synchronize) the events in the computer. The XPU-80 board provides all clock signals required for the CPU and S-100 bus as specified by the IEEE 696/S-100 Bus specification.

Z-80 CLK - 6 (or 4) MHz and broad sites a set average and A

S-100 CLOCK - 2 MHz PHI - 6 (OR 4) MHz

The S-100 bus CLOCK (pin 49) is a 2 MHz clock, not required to be synchronous with any other bus signal.

The S-100 bus PHI (pin 24) is the master timing signal for the bus. The 6 (or 4) MHz signal is normal bus PHI. The XPU-80 board is factory configured for 6 MHz operation and can be factory altered for 4 MHz operation. The 6 MHz board can be identified by the 12 MHz crystal located in the lower left hand corner of the board. The 4 MHz board uses a 8 MHz crystal.

Z80 PHI is bus PHI\*. This shifts Z-80 states one-half cycle from bus states.

The XPD-80 poard is a CPU board. The CPU board consists of a CPU reas 3.2) and the logic clements required to all a transiston of data between the CPU only and external levices. to provide the clock generating the no signals real of the CPU, and to datage share data is to be read or where data must be feat.

The birs diagram in Figure 1 is a graphic representation of the Kaw-80 board. The diagram shows the major tunctional elements of the board as blocks. The lines connecting the boxes indicate the paths, along which information and/or control flows, between the functional areas. A block diagram is a guide to understanding the interrelationship of the function areas of the manual.

- 8 - PROCESSOR

### 2.4 REAL TIME CLOCK

A real time clock (RTC) indicates the passage of actual time, as opposed to the fictitious time established by a computer program. The RTC on the XPU-80 provides a 50 Hz output and a 1 Hz output.

The 50 Hz clock is input directly to the interrupt controller Int 3 input to provide a real time reference. Tick marks can be used to provide timing reference for task swapping, switching between users, and alternating between foreground and background tasks. The 1 Hz clock is input to the time-out circuit (Z80 NMI\* and EPROM ON) and optionally (jumper option) to the interrupt controller Int 5 input.

The time-out circuit optionally times out a system hung up by a user that has disabled Z80 interrupts. In such a case, the Z80 NMI\* (non-maskable interrupt) input is driven within between one-half and one second of the unmasked interrupt (9519 Group Int\*). The NMI\* pulse also enables the XPU-80 EPROM.

The NMI\* timeout does not occur if the system Front Panel board is requesting a wait state, DMA occurs, or the board is in Supervisor mode.

1900 RD\*, SWD\* is apported iow between ovelow. Parity enable has the same timing 2.5 STATUS LOGIC

At the start of each machine cycle the XPU-80 outputs data on the S-100 status bus to indicate processor status and the type of operation about to be performed. The S-100 status bus consists of eight signal lines.

sMl (44) Indicates that the current cycle is an op-code fetch.

sMEMR (47) Identifies bus cycles that transfer data from memory to a bus master.

sHLTA (48) Acknowledges that a HALT instruction has been executed.

sINP (46) Identifies the data transfer bus cycle for an input device.

sOUT (45) Identifies the data transfer bus cycle to an output device.

- sWO\* (97) Identifies a bus cycle that transfers data from the bus master to a slave. S-100 sWO\* = Z80B RD\*. sWO\* is asserted low between cycles. Parity enable has the same timing as sWO\*.

- SINTA The XPU-80 does not utilize the SINTA line (the line is driven low). All interrupt acknowledges are handled by the XPU-80 interrupt controller.

sSXTRQ The XPU-80 does not utilize the sSXTRQ (sixteen-bit data transfer request) line. The XPU-80 is an eight-bit master.

XPU-80

- 10 -

### 2.6 CONTROL SIGNALS

W100 2338113

The control bus is a set of control lines, the function of which is carry the synchronization and control information necessary for the computer system.

2.6.1 Control Output Bus

The lines of the control output bus determine the timing and movement of data during any bus cycle. The S-100 control output bus consists of five signal lines. The lines are:

pSYNC (76) Indicates the start of a new bus cycle. pSYNC is generated either from the leading edge of MREQ\* or the delayed edge of IORQ\*. pSYNC is not generated for INTA cycles.

pSTVAL (25) The Processor Status Valid signal, in conjunction with pSYNC, indicates that stable address and status may be sampled from the bus in the current cycle. Three separate pSTVAL are jumper selectable to accommodate different clock rates and setup times. The board is correctly configured for the installation prior to shipment.

pDBIN (78)

A generalized read strobe that gates data from an addressed slave onto the data bus.

pWR\* (77) A generalized write strobe that writes data from the data bus into an addressed slave. pWR\* is gated off during Processor Control accesses, MMU and Supervisor Call stack writes, protected I/O writes, and protected memory writes.

pHLDA (26) Processor Hold Acknowledge. Used in conjunction with HOLD\* (74) to cooridinate bus master transfer operations.

- 11 1 4

### 2.6.2 Control Input Bus

A control input bus carries the signals that allow bus slaves to synchronize the operation of the bus master with conditions internal to the bus slave, and to request operations of the bus master. The lines are:

XRDY (3) One of two ready inputs to the bus master. The ready lines synchronize the bus master to the response speed of the bus slave. Bus cycles are suspended and wait states inserted until both ready lines are asserted. The bus is ready when both inputs are high.

The XRDY line is a special ready line used by front panel devices to stop and single step the bus master. RDY is the other ready input.

RDY (72) The RDY line is the general ready line for bus slaves.

> The INT\* line is used by a bus slave to request service from the bus master.

The NMI\* line is a non-maskable interrupt request line. It is not masked off by the bus master. The signal is asserted as a NMI\* (12) negative going edge.

SIXTN\* The SIXTN\* line is not used in an XPU-80 system. and margerils of online 120 barap at which

SIXTN\*

INT\* (73)

- 12 -

#### 2.7 FRONT PANEL INTERFACE

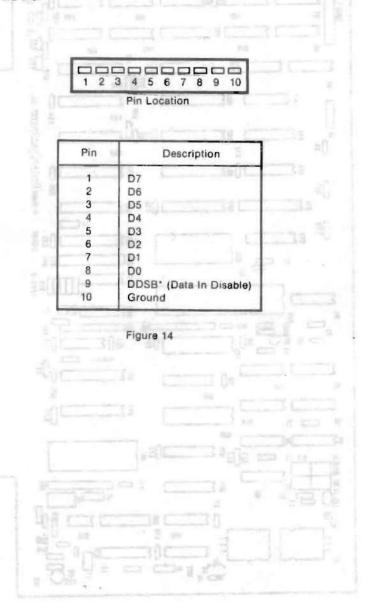

The XPU-80 board is compatible for use with the Intersystems Front Panel board and other front panel boards. The XPU-80 is connected to the Intersystems Front Panel via a 10-conductor flat cable. Figure 2 describes the pin assignment for the connector.

In addition to traditional front panel functions, a front panel can be used in systems with the XPU-80 to:

- \* Read and modify the high speed MMU RAM

- Read and write to the XPU-80 9519 interrupt controller controller

- \* Read and write to the Processor Control Registers and Requests

- \* Read the XPU-80 EPROM

|     | 1     | 1.00 |

|-----|-------|------|

| Pin | Local | 10   |

|     | 20000 |      |

|     |       |      |

| Pin | Description             |

|-----|-------------------------|

| 1   | D7                      |

| 2   | D6                      |

| 3   | D5                      |

| .4  | D4                      |

| 5   | D3                      |

| 6   | D2                      |

| 7   | D1                      |

| 8   | DO                      |

| 9   | DDSB* (Data In Disable) |

| 10  | Ground                  |

Figure 2 CONN 1

2.8 RESET CIRCUIT

In an S-100 bus computer, system reset functions are controlled by three bus lines: POC\*, SLAVE CLR\* and RESET\*.

POC\* (99) is the power-on-clear signal for all bus devices. Bus SLAVE CLR\* (54) resets all bus slaves during power-up. RESET\* (75) is used to reset all bus masters.

XPU-80 RESET\* resets the processor and sets flip flops that enable the EPROM and the Supervisor mode (see sections 2.13 and 2.17 respectively). The Modify Control Register is cleared. After a reset two wait states are requested for all bus cycles, the error circuit is disabled, and the MMU is enabled.

On the XPU-80, an RC network drives POC\* and SLAVE CLR\* active during power up.

POC\* is also used to clear the Service Net counter so that the Service Net line is at a logic ONE state following a power-up. See section 2.18.

The XPU-80 board is in the following state following a reset:

- \* Supervisor mode

- \* EPROM enabled in all pages of all spaces

- \* Software wait request is ON

- \* Bus and parity error circuits are disabled

- \* MMU-load mode enabled

- \* Power-off request is inactive

A typical booting up procedure is described in the EPROM description in this section of the manual.

XPU-80

- 14 -

### 2.9 WAIT STATE REQUESTS

Wait states are used to synchronize the bus cycles generated by the bus master (the XPU-80) with the response speed of the assorted bus slaves in the system, and certain functions of the XPU-80 board itself. During the bus cycle, a wait state (BSW) is entered if the RDY or XRDY line indicate that the bus slave (or XPU-80 function) is not ready for data transfer.

Ten signals on the XPU-80 can request wait states as described in Figure 3.

| XPU-80 No. of<br>Signal Walt States |                                              |

|-------------------------------------|----------------------------------------------|

| XRDY* culture .computed and (of     |                                              |

| PRDY CONST CONTROL VERY OCHUS       | Derived from S-100 RDY                       |

| M1 0, 1, or 2                       | Jumper Selected (J2)<br>Jumper Selected (J4) |

| MEMR 0, 1, or 2                     | Jumper Selected (J4)                         |

| 1/O REQ 0, 1, or 2                  | Jumper Selected (J4)<br>Jumper Selected (J1) |

| EPROM ENABLE SET                    |                                              |

| SUP CALL MUX* 2                     | During Supervisor Call Sequence              |

| Register) 1                         | Set by Software, P5=0 at Reset               |

| P4 (Modify Control                  |                                              |

| Register) 2                         | Set by Software, P4=0 at Reset               |

Figure 3 XPU-80 wait states

### 2.10 DMA

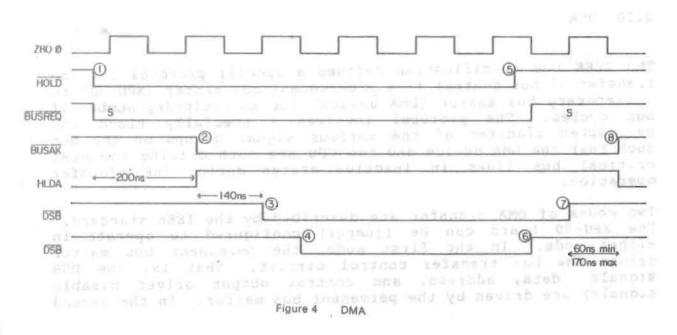

The IEEE bus specification defines a special protocol for the transfer of bus control from a permanent bus master (XPU-80) to a temporary bus master (DMA device) for an arbitrary number of bus cycles. The protocol involves a specially timed and overlapped transfer of the various signal groups on the bus such that the DMA device and the CPU are both driving the most critical bus lines in inactive states during the transfer operation.

Two modes of DMA transfer are described by the IEEE standard. The XPU-80 board can be (jumper) configured to operate in either mode. In the first mode, the permanent bus master drives the bus transfer control circuit. That is, the DSB signals (data, address, and control output driver disable signals) are driven by the permanent bus master. In the second

2012320114

- 15 -

mode, the temporary master drives the bus transfer control circuit. The DSB signals are driven by the temporary bus master. When the XPU-80 drives the bus transfer control circuit, the procedure for bus transfer is as follows (see

- The temporary bus master (DMA device) asserts a hold 1)

- 2)

- request. Line 74, HOLD\* is active. XPU-80 BUSAK\*, active. Line 26, pHLDA, is active. At the rising edge of Phi, XPU-80 ADSB goes active, S-100 ADSB\*, DDSB\*, and SDSB\* are taken low, 3) disabling the address, status and data output drivers of the XPU-80, and enabling the control output drivers of the temporary master.

- At falling edge of Phi, XPU-80 CDSB goes active, 4) S-100 CDSB\* goes active disabling the XPU-80 control output driver and enabling the address, status and data out drivers of the temporary master. Transfer

- state is terminated. With DMA transfer complete, temporary bus master 5) asserts HOLD\* inactive.

- XPU-80 ADSB clocked inactive, S-100 ADSB\*, DDSB\*, 7) and SDSB\* go inactive, enabling the address, data, and status output drivers of the XPU-80, disabling the control output driver of the temporary master.

- XPU-80 processor BUSAK\* asserted inactive. pHLDA 8) inactive.

The XPU-80 DMA sequencer features a high noise immunity lock out circuit.

- 16 -

PROCESSOR

### 2.11 PARITY AND BUS ERROR

BRAN IN STAR

PARITY ERROR\* and BUS ERROR\* are input to the Error Latch Circuit (Section 2.12).

### 2.11.1 Parity

Parity checking is a method of checking the integrity of data when the data is transferred to or from storage. An additional bit, the parity bit, is generated and transferred with the binary information being transferred. The parity bit is the single-digit sum of all the binary digits. The digit value is 0 for an odd number of 1's and 1 for an even number of 1's when the odd parity check is used.

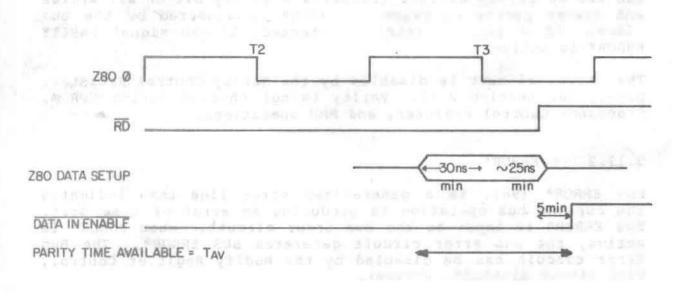

The XPU-80 supports the Ithaca Intersystems parity scheme. In this arrangement, S-100 bus lines 65 and 66 are assigned to PARITY and PAREN\* (parity enable) respectively. The PARITY line contains odd parity when the device driving the data bus drives PAREN\* active. The reciving device checks the parity and can drive the S-100 ERROR\* line active in response to an error.

The XPU-80 parity circuit transmits a parity bit on all writes and checks parity on reads if PAREN\* is asserted by the bus slave. If a parity error is detected, XPU-80 signal PARITY ERROR\* is active.

The parity circuit is disabled by the Modify Control Register, p3=0. See section 2.15. Parity is not checked during EPROM, Processor Control Register, and MMU operations.

### 2.11.2 Bus ERROR\*

Bus ERROR\* (98), is a generalized error line that indicates the current bus operation is producing an error of some sort. Bus ERROR\* is input to the Bus Error circuit. When ERROR\* is active, the bus error circuit generates BUS ERROR\*. The Bus Error circuit can be disabled by the Modify Register Control, P3=0 (ERROR DISABLE\*, active).

- 17 -

2.12 ERROR LATCH

It is desirable to save information describing the system status during an error.

In response to MMU ERROR\*, PARITY ERROR\* and BUS ERROR\* (see section 2.11) The error latch circuit performs two functions.

The error latch circuit is the INT 4 source for the interrupt controller. The error latch circuit drives the latch input of the Processor Control Registers

The stored information is available for retrieval at Processor Control Registers 0 through 3. Refer to section 2.15. Note that stored bus status is lost if an MMU write is performed prior to accessing the stored information.

Figure 5 is a timing diagram with the critical signals. A bus error that occurs very early in the bus cycle causes the storage of bus status from the previous cycle. Data for the current cycle is latched during the period defined by the end of pSYNC to the end of the read or write strobe.

XPU-80

- 18 -

2.13 EPROM

The XPU-80 EPROM can be programmed to provide a variety of functions. The XPU-80 is factory configured to accept a 2732 EPROM. The board can be reconfigured by Intersystems to accept a 2716 EPROM.

The EPROM plays a key role in the process of MMU initialization. The EPROM can contain system diagnostics and code that facilitates the recovery from system errors.

EPROM is enabled in one of two ways.

- 1) As an attribute function of any page in which d3 of the attribute byte equals ONE.

- 2) On every page, in every space, when the EPROM enable is set by XPU-80 RESET\* (power-up, reset) or NMI\*

Note: Processor Control Request EPROM RESET resets the flip flop.

One wait state is requested when the EPROM flip flop is enabled.

### 2.13.1 MMU Initialization

The EPROM can be used to initialize the MMU as, follows:

- 1) After reset or power-up, the EPROM is enabled in every page of every space. The Modify Control Register P7 (MMU Enable) is set low, so that the MMU is enabled (as R/W memory) after reset.

- 2) With the MMU enabled, the EPROM program loads the MMU and enables the Processor Control Registers (d4

- high).

3) With the Processor Control Registers enabled, the EPROM code can turn the MMU and itself ON or OFF. 4) Boot the DOS.

- 19 -

### 2.14 MEMORY MANAGEMENT UNIT

The two major functions of the memory management unit are allocating memory to various tasks, and protecting the memory.

The basic goals of an MMU are:

- To provide a flexable, predictable structure to memory that is independent of the limitations of the CPU logical address structure. Logical address refers to the 16-bit address output by the Z80 processor. Physical address refers to the 24-bit address that appears on the S-100 address bus.

- To protect the system involving:

- a) Protection from inadvertent mistakes such as "runaways".

- b) Protecting data from unauthorized access.c) Protecting the operating system from uncontrolled access by users.

- \* To provide support for multiple independent tasks that can share access to common resources and programs.

The MMU coordinates memory as eight 64 kbyte spaces.

Supervisor Space = Space 111 Stack Write Space = Space 000 User Spaces = Remaining Spaces

The Z80's 64 kbyte space is configured as 16 contiguous 4-kbyte pages. When enabled for loading, the MMU appears as RAM in the highest 16 bytes of every 4 kbyte page. The sixteen bytes consist of eight pairs of attribute byte and relocation byte (described below). The eight pairs correspond to the eight 64 kbyte MMU spaces, selected by the decoding of the MMU RAM multiplexed address bits A3 through A1.

XPU-80

- 20 -

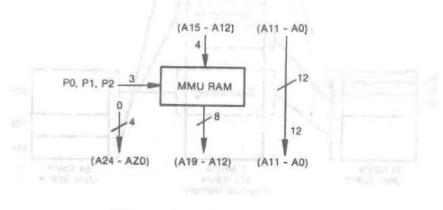

An MMU (logical) address is described in Figure 6.

| Address<br>15 |     | 13                           | 12                                 | 11                        | 12                                    | 11                           | 10 | 9     | 8 | 7                      | 6                          | 5               | 4                 | 3      | 2          | 1       | 0    |  |

|---------------|-----|------------------------------|------------------------------------|---------------------------|---------------------------------------|------------------------------|----|-------|---|------------------------|----------------------------|-----------------|-------------------|--------|------------|---------|------|--|

| Pg3           | Pg2 | Pg1                          | Pg0                                | 1                         | 1                                     | 1                            | 1  | 1     | 1 | 1                      | 1                          | 1               | 1                 | S2     | S1         | SO      | A*/R |  |

| Notes;        |     |                              |                                    |                           |                                       | election                     |    | 18.51 | A | */R = /                | Attribu                    | te byt          | e/Relo            | cation | byte s     | electio | on   |  |

|               | S   | 2 throi                      | ugh S0                             | = Spa                     | ace se                                | lection                      |    | 18.5  | A | · 0 s                  | elects                     | Attrib          | ute by            | te     | 151-10     |         |      |  |

| Notes;        | S   | 2 throi<br>000<br>111<br>All | ugh S0<br>= Sta<br>= Sup<br>others | ck Wr<br>bervise<br>= Use | ace se<br>ite Spa<br>or Spa<br>er Spa | lection<br>ace<br>ce<br>ices |    | 18.5  | 1 | • 0 s<br>1 s<br>= Logi | elects<br>elects<br>ic ONI | Attrib<br>Reloc | ute by<br>ation t |        | ari<br>Len |         |      |  |

ville, a vilotite relocation Bytw can be accessed infall,

Figure 6 MMU addressing

### 2.14.1 Address Translation

Relocation of programs and data areas is accomplished by an address translation mechanism that translates the CPU's logical addresses to physical addresses to be put on the S-100 address bus.

A physical address is formed by concatenating the lower twelve bits (All through AO) of the logical address with a relocation byte as shown in Figure 7. The result is a physical address to any of 256 possible 4 kbyte memory spaces in physical memory.

Figure 7 MMU address translation

201233110.00

- 21 -

When a specific page is addressed and the MMU is enabled for loading, a specific relocation byte can be accessed (AO=1). The relocation byte can have any value from 0 to FFH.

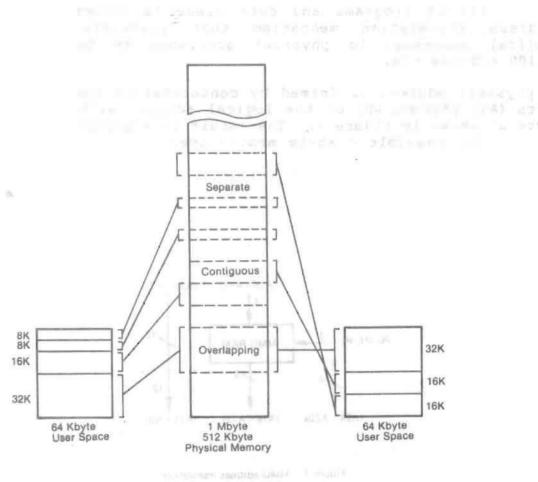

The 4 kbyte pages (for each of the spaces) are mapled into physical memory. Pages can be selectively mapped to be overlapping, contiguous, or totally separate. See Figure 8. User/Supervisor spaces share memory wherever relocation bytes are common. Spaces can be prevented from interacting by assigning no common relocation bytes.

When users have common relocation bytes, and therefore share areas of memory, the attribute byte (described below), for each page can be set to protect data against unauthorized use, and to protect supervisor space from access by users.

Figure 8 Address mapping

XPU-80

- 22 -

### 2.14.2 Attribute Bytessions our same cost contract sold sold and

There is an attribute byte for each logical page to provide for the restriction of memory access. The attribute byte is checked at each memory access to the page of memory. The attribute byte is described in Figure 9.

Attribute bit d3=1 enables EPROM and d4=1 enables the Processor Control Registers. Refer to section 2.11 for a description of EPROM and section 2.15 for a discussion of the Processor Control Registers.

Attribute bits d0, d2, d5, and d6 are input to a PAL that generates MMU ERROR\* if an attribute violation occurs.

MMU ERROR\* is output to two circuits. MMU ERROR\* is input to the Error Latch circuit (see section 2.12).

### 2.14.3 MMU Enable

MMU is enabled when the Modify Control Register P7=0 and logical address lines All through A4 are high. The space being accessed by the MMU operation is selected by processor address bits A3 through A1. The page being accessed is selected by logical address bits A15 through A12.

Stack write timing - MMU Enable is active throughout the cycle. Uses the same read and write strobes as MMU Read and Write.

| Bit            | Signal         | Description        | and a second second                |        |  |

|----------------|----------------|--------------------|------------------------------------|--------|--|

| d0             | Read Protect   | If ONE, interrupts | after a memory read cycle          |        |  |

| d1<br>d2<br>d3 | Not Used       |                    |                                    |        |  |

| d2             | Dirty Bit      | If ONE, interrupts | after a memory write               |        |  |

| d3             | EPROM          | If ONE, enables EF |                                    |        |  |

| d4             | System Control | If ONE, enables Sy | stem Control Registers             |        |  |

| d5             | I/O Protect    |                    | utputs, and interrupts after I/O ( | cycles |  |

| d5<br>d6       | Write Protect  |                    | rites, and interrupts after a men  |        |  |

| d7             | XPU-80 LED     | If ONE, turns XPU- |                                    |        |  |

Figure 9 Attribute byte

PROCESSEDA

- 23 - 5

### 2.15 PROCESSOR CONTROL REGISTERS AND REQUESTS

The Processor Control Registers are enabled in any user or supervisor page if the d4 attribute bit for that page is set to ONE. When enabled, the lower 16 bytes of the top 32 bytes of the page become Processor Control Registers and Requests. Figure 10 describes the form of a Processor Control Register address.

| Address<br>15 | 14  | 13  | 12  | 11 | 12 | 11 | 10    | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0   |  |

|---------------|-----|-----|-----|----|----|----|-------|---|---|---|---|---|---|---|-----|-----|-----|--|

| Pg3           | Pg2 | Pg1 | Pg0 | 1  | 1  | 1  | (01 y |   |   |   | 1 | 1 | 0 | x | PC2 | PC1 | PC0 |  |

| Notes:        |     |     |     |    |    |    | n     |   |   |   |   |   |   |   |     |     |     |  |

Figure 10 Processor Control Register and Request addressing

The Processor Control Registers and Requests structure of the XPU-80 consists of four eight-bit input registers, one eight-bit output Modify Control Register, three decoded Processor Control Requests, and the 9519 interrupt controller as shown in Figure 11.

|     | sa Bita |     | Destates    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |  |

|-----|---------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| PC2 | PC1     | PCO | Register    | Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |  |

| 0   | 0       | 0   | Register 1  | Modify Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |  |

| 0   | 0       | 1   | Register 2  | EPROM Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |  |

| 0   | 1       | 0   | Register 3  | Service Net Toggle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |  |

| 0   | 1       | 1   | Register 4  | Exit Supervisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |  |

| al  | l other |     | 9519 9519   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |  |

|     |         |     |             | second and provide the second state of the second | Derrich Der |  |

|     |         |     |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |  |

|     |         |     | Figure      | 11 Processor Control Registers and Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |  |

|     |         |     |             | restaure Interactionation and SMC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |  |

|     |         |     |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |  |

|     |         |     | 2100 200    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |  |

|     |         |     | antes antes |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |  |

.

PROCESSOR

- 24 -

The Processor Control Registers that save bus status during an error are described in Figure 12.

| Bit | ted . Tallet.  | Processor Con | trol Register    | netrisetet  |

|-----|----------------|---------------|------------------|-------------|

|     | 1              | 2.13130       | 110 cold 3 col 1 | 0 0 m c 1 m |

| 0   | Service Net    | AO            | 48               | A12         |

| 1   | SINP           | A1            | A9               | A13         |

| 2   | SOUT           | A2            | A10              | A14         |

| 3   | OFF Reg"       | A3            |                  | A15         |

| 4   | Int Bus Error* | A4            |                  | A16         |

| 5   | Parity Error*  | A5            | sM1              | A17         |

| 6   | Power Fail*    | A6            | sWO*             | A18         |

| 7   | Bus NMI*       | A7            | SHLTA            | A19         |

Figure 12 Processor Control Registers

The Processor Control Requests (Figure 13) are generated by writing any byte to the request address. Following EPROM Reset, reads are from system memory. The Service Net can be jumper (J8) configured as S-100 line 21.

| Processor<br>Control Request | Signal                          | Description exection in descript. In the    |

|------------------------------|---------------------------------|---------------------------------------------|

| Modify Control               | reolection at the second second | Describes selected space.                   |

| Register - In I to a         |                                 |                                             |

|                              | P2 1                            | all others = user space                     |

| Addatesteat ten              | P3 Error Disable                | If 0, disables Bus and Parity Error circuit |

|                              | P4 Two Wait Reg                 | If 0 requests two wait states               |

|                              | P5 One Walt Req                 | If 0, requests one wait state               |

|                              | P6 Power Off                    | If 1, drives bus POWER OFF* low             |

|                              | P7 MMU Enable                   | If 0, enables MMU                           |

| EPROM Reset                  |                                 | After Reset or NMI*, a flip flop            |

|                              |                                 | is set that turns EPROM ON in all pages     |

|                              |                                 | of all spaces. EPROM Reset resets the       |

| nia hi saquaas               |                                 | flip flop                                   |

| Service Net Toggle           |                                 |                                             |

| Supervisor Exit              |                                 | XPU-80 switches from Supervisor Mode        |

| oupervisor cxit              |                                 | to Licer Mode at the and of the fourth      |

|                              |                                 | processor cycle after this request.         |

Figure 13 Processor Control Requests

108330044

- 25 -

2.16 INTERRUPT DEVICE

The XPU-80 board uses a 9519-1 interrupt controller. Features of the interrupt controller include:

\* Fixed or rotating priorities

\* Common and individual vectoring

\* Master mask

\* Status register

\* Interrupt Service Register (ISR)

\* Information Transfers

#### 2.16.1 Interrupt Modes

The XPU-80 processor has three basic modes of interrupt operation that can be changed under software control. The interrupt controller can be programmed to operate in any of the modes. On the XPU-80, the processor interrupt mode and contents of the I register can be changed by the user.

Mode 0

In Mode 0, the interrupt device places an instruction on the processor data bus during the Interrupt Acknowledge (INTA) cycle. The processor executes this instruction instead of the next instruction in memory. In theory, any instruction can be placed on the data bus, but in practice only single byte instructions should be used because the processor only produces an INTA cycle on the first byte of a multiple byte instruction. The single byte call instructions, Restarts, execute a call to one of eight fixed locations in low memory, depending on the coding of the instruction. The interrupt controller can be programmed to supply any of the Restarts in response to any interrupt.

Mode 1

When Mode 1 is selected by the programmer all interrupts in the system respond with a call to location 38H. A common service routine should begin at that location.

Mode 2

much and the one of the board of

Mode 2 is the most powerful interrupt response mode. The processor forms a pointer from the byte received during the INTA and its I register. This pointer would normally be used to read a jump address from memory, but because the system user spaces have the ability to alter the I register, the jump

XPU-80

- 26 -

address supplied by memory is ignored; the bus data input buffer is disabled. Instead, two additional INTA pulses are generated, enabling the 9519 to output two more response bytes. The two response bytes are the jump address. The interrupt controller in this situation acts like RAM that overlays system memory.

Memory read or write signals during the period between the first INTA and the first Supervisor Ml cycle, activate the MMU circuit. The Supervisor Mode is forced. Stack writes during the period write into the MMU space 000. Reads during the period generate additional INTA pulses for the interrupt controller.

venies witch, newbry read, the write, and the resolutions.

halloustor

in totervisor Advant data it controls the tractic barance itervisor and assr moder, and merabilistics the under under all received and asses of the unit balance in astractions.

te lyigher and entrand thit.

ATSESS - Labor picks distances to a statement of the

The Process Control Request 14 Look be a still register till introduce a delay. The Seven bit your high at the and of the fourth processor syste after the request, allowing time fail if the life (Mterrupts) and the basis. The brand, therefore witches the bupervise to Use mode at the end of the second faile of the jump instruction. The jump is the risers (a sec of the all uses sparse.

## 2.17 SUPERVISOR/USER

Utilization of the XPU-80 takes place in one of two modes: Supervisor mode and User mode.

The Supervisor mode of operation is a non-protected (raw 2-80) mode. Any code sequence is faithfully executed under all conditions, assuming a benevolent Supervisor code sequence. It is possible for a program in Supervisor mode to commit suicide.

The User mode of operation is a protectable mode. The six user spaces that constitute the User mode can be protected against memory write, memory read, I/O write, and I/O read operations.

This section of the manual describes the procedures by which the transition between Supervisor mode and User mode is controlled.

The Supervisor/User circuit controls the transition between supervisor and user modes, and establishes the conditions under which transfers are conducted in the following situations:.

- Leaving the Supervisor (Supervisor to User)

- Returning to Supervisor (User to Supervisor)

3.17.1 Leaving the Supervisor

The XPU-80 is initially in supervisor mode because RESET\* enables Supervisor mode.

To leave the supervisor, the following code is executed:

STA ;Write to Processor Control Request , Supervisor Exit EI ; Jump;

The Processor Control Request is input to a shift register that introduces a delay. The S\*/U bit goes high at the end of the fourth processor cycle after the request, allowing time for EI (Enable Interrupts) and the jump. The board, therefore, switches from Supervisor to User mode at the end of the last memory fetch of the jump instruction. The jump is to any address in one of the six user spaces.

XPU-80

- 28 -

### 2.17.2 Returning to Supervisor Mode

The procedure for returning to Supervisor mode is more complicated than leaving the supervisor. Implementation of a traditional interrupt routine for handling the return to supervisor can generate special problems on the XPU-80.

- The stack write after INTA could overwrite user or supervisor program code.

- \* On the XPU-80, the user has the ability to alter the processor interrupt mode or the the contents of the I register. A user could therefore return to the supervisor at an incorrect address and crash the system.

To avoid these problems, the XPU-80 has special facilities. To avoid having the stack overwrite either supervisor or user code, a special space (MMU space 000) is reserved for supervisor call stack writes. To overcome problems due to the user changing the processor interrupt mode or the contents of the I register, each processor interrupt mode is handled differently.

Mode 0

The 9519 is programmed to place a restart instruction on the bus during INTA.

Mode 1

The processor jumps to 38H.

Mode 2

A special procedure is implemented. During a Mode 2 interrupt, the processor forms a pointer from the byte it receives during INTA and the contents of the I register. The processor uses the pointer to read a jump address from memory. The XPU-80, given the suspect validity of the contents of the I register, reads the jump address directly from the interrupt controller which performs like a floating RAM that overlays system memory. Two additional INTA pulses are generated by the supervisor call circuit so the interrupt controller outputs two more response bytes.

Memory reads or writes during this period enable the MMU circuit. Bus write strobes are suppressed, stack writes are stored in MMU space 000. Reads during the period generate additional INTA pulses for the interrupt controller.

1000 A

- 29 -

### 2.18 SERVICE NET

S-100 line 21 is an XPU-80 jumper selectable (J8) line. When configured as the Service Net line, the line is an open collector serial data transmission line. The line is toggled by writing any byte to Processor Control Request, Service Net Toggle. See section 2.15.

# 2.19 BUS I/O

Bus I/O is organized so that with hardware modification the following allocation of I/O ports is possible.

all master but any through the taken of the terror but

|   | Super | visor          | Users              | 5 1                      | nlussie z   |  |

|---|-------|----------------|--------------------|--------------------------|-------------|--|

|   |       | to develop the | is an and a second | 14 9 15.32<br>650 75, 11 | in prima in |  |

| * | Ports | 0-255          | None               | (I/O pr                  | otected)    |  |

| * |       | 0-255          |                    | 0-255                    |             |  |

| * | Ports | 0-255          | Ports              | 255-51                   | 1           |  |

ne sale privated to place a statut institute and an and

I-phast

The process

S HOOM

A special fit addre to impreter ted. Fulling a budg of restriction that price set forms a pointer read in nyrm of foreact deting tells and the contents of the fit an electric file decrease dees given the number valid by of the contents of the restrict controlist reads his jump adde of strengt from the transfer of the restrict while a pointer of the a limit and the restrict controlist while a pointer of the a limit and the restrict controlist strengther point files a firsting with the controlist while a pointer of the intercept outputs for superviser gail circuit to the intercept outputs for entry response byten

> Manuary reads of writes during shis unried, read to chronic. For write stropes are suppressed sheet stored in Multippate 600. Dwed, dufing the period additional INTE pares for the interrupt controller.

> > PROCESSOR

- 30 -

The XPU-80 board is configured prior to shipment and should not require modifications.

This section of the manual provides the information required to prepare the XPU-80 board for operation in Intersystems equipment. There are nine jumper areas on the XPU-80 board. Each jumper area is a box with a group of plated-through holes spaced 0.1 inches apart. To configure a jumper area, zero or more connections per box are made by a printed circuit trace on the solder side of the board or by a shunt that slides onto the 0.040 inch square posts that are soldered into the plated-through holes. To change a connection made by a shunt, the shunt is lifted from its position and set across the desired posts at the correct jumper position. To change a connection made by a circuit trace, the trace betweem the plated-through holes is cut, and a shunt is installed across the desired position.

All possible connections within a jumper area are given letter names. Letter names run A B C ... from left to right or top to bottom. Jumper area locations are identified in Figure 15.

J1 Jl selects the desired number of wait states for I/O cycles.

| A | 0 | wait | states |

|---|---|------|--------|

| в | 1 | wait | state  |

| С | 2 | wait | states |

J2 J2 selects the desired number of wait states for M1 cycles.

| A | 0 | wait | states |  |

|---|---|------|--------|--|

| В | 1 | wait | state  |  |

| С | 2 | wait | states |  |

ner andra farfallet ander oan titt

J3 J3 selects the delay for pSTVAL. a is earliest; c is latest.

| A | pSTVAL | а |

|---|--------|---|

| В | PSTVAL | b |

| C | PSTVAL | С |

88. C 1682.0W

- 31 - 26 ---

J4 J4 selects wait states for MREQ cycles.

| A | 0 wai | t states |  |

|---|-------|----------|--|

| B | 1 wai | t state  |  |

| C | 2 wai | t states |  |

J5 J5 configures the Service Net capability.

| A-B | Service Net out          | put or | S-  | 100 21.    |         | adunt no |

|-----|--------------------------|--------|-----|------------|---------|----------|

| B-C | S-100 21 disabl          | es dat | a i | nput, rece | eivers. |          |

| C-D | Top connector receivers. | pin    | 9   | drives     | data    | input    |

0.040 incu squate resta that are soldered into the J6 J6 selects a source for the 2 MHz clock signal. and the correct the correct ins

A-B 12 MHz crystal B-C 8 MHz crystal

J7 J7 selects the source for interrupt controller input VI4. of the from the Control of the source rotated ... l Hz clock (solder trace default)

the design bet fan

PROCESSOR

Bus VI5

J8 J8 selects the source for interrupt controller input VI7.

| A | VI7 | (solder | trace | default) |  |  |

|---|-----|---------|-------|----------|--|--|

| В | VI4 |         |       |          |  |  |

| C | VIO |         |       |          |  |  |

| C | VI3 |         |       |          |  |  |

J9 J9 configures the board for Front Panel or Front Panelless operation. .

XPU generates MWRITE: Front Panelless mode. A-B B-C XPU does not generate MWRITE: Front Panel

mode. Lavred tol gainb and appaires EL 21

- 32 -

XPI1-80

## 3.1 FRONT PANEL OPERATION

Use the following procedures to prepare the XPU-80 to operate with the Front Panel board.

- Configure the XPU-80 for operation with the front panel by setting jumper J9, B to C.

- 2) Install the ribbon cable between the Front Panel header and the XPU-80 top connector. The cable is oriented at the XPU-80 connector so that Pin 1 is at the left end of the connector and Pin 10 is at the right end, as viewed from the component side of the board.

at mught

2100 8550

- 33 -

### 5.0 MANUAL APPLICABILITY AND BOARD REVISION

This manual refers to boards identified as Boards are identified in the lower right corner.

Figure 15

34

XPU-80

| INTE | GRATED CIRC                        | JITS             |                     |        |              |

|------|------------------------------------|------------------|---------------------|--------|--------------|

| 0017 | 66 74ALS0                          | )                | 1                   | ba b   | U 1          |

| 0010 | 16 74LS00                          |                  | 3                   |        | U8,17,23     |

| 0010 | 15 74S00                           |                  | 1                   |        | U58          |

| 0010 | 18 74LS02                          |                  | 1                   |        | U {6         |

| 0010 |                                    |                  | 3                   |        | 04,21,45     |

| 0010 | 74504                              |                  | 2                   |        | U11,18       |

| 0010 | 25 7406                            |                  | 1                   |        | U46          |

| 0017 |                                    | 5                | 1                   |        | 054          |

| 0010 | 28 74LS08                          |                  | .1                  |        | U19          |

| 0017 | 05 74ALS1                          | )                | 1                   |        | U5           |

| 0010 | 30 74LS10                          |                  | i                   |        | U7           |

| 0010 | 29 74810                           |                  | 2                   |        | U6,20        |

| 0010 | 33 74LS20                          |                  | . 1                 |        | U10          |

| 0010 | 37 74LS30                          |                  | ANN TATER NO        |        | U 9          |

| 0017 | 27 74ALS3                          | 2                | 43 WA XS 1          |        | U56          |

| 0010 | 42 74ALS7                          |                  | 45 KANT 44 3        |        | 02,37,53     |

| 0010 | 041 74574                          |                  | 50 MRNJ 22 2        |        | U3,57        |

| 0017 | 68 74LS92                          |                  | 31 AF 1 31 3        | REL    | 022          |

| 0010 | 51 74LS12                          | 5                | 32 PETE 28 1        |        | U 4 4        |

| 0016 |                                    |                  | TO WENT & 2         |        | 013,27       |

| 0010 | 57 74LS15                          | 3                | 13 WEST 60.2        |        | 024,25       |

| 0010 | 58 74LS15                          | 5                | 42 May1 20 1        |        | U10          |

| 0010 | 59 74LS15                          |                  | નગ મારાખા તેવે 1    |        | 015          |

| 0010 | 062 74LS16                         | 1                | 4.2 webs < 1        |        | 055          |

| 0018 | 353 74S175                         |                  | 1                   |        | U 3 9        |

| 0010 | 70 74LS24                          | )                | ADTINA 201 ALE 1    | .8H0 1 | U47          |

| 0010 | 72 74LS24                          | 1                | 1                   |        | U51          |

| 0010 | 74LS27                             | 3                | 1                   |        | 042          |

| 0010 | 79 74LS27                          | )                | Busi 30881          |        | U 35         |

| 0010 | 080 74LS28                         | )                | neo succes of tabl  | ke S   | U 3 4        |

| 0016 | 94 74LS32                          | CLOCK GENERA     | TOR                 |        | U 3 8        |

| 0018 | 354 74LS36                         | 3                | 4                   |        | 043,48,49,50 |

| 0010 |                                    |                  | 4                   |        | 030,31,32,33 |

| 0016 | 96 74LS53                          | 3                | Ecote Dubra 2       |        | 052          |

| 0018 | 155 MM5368                         | NATIONAL         | - EAST NOT AN AND A |        | U 4 0        |

| 0018 | 156 AM9342                         | 2DC TAA=45ns max | 2                   |        | U26,28       |

| 0018 | 157 AM9519                         | -1 AMD           | 1                   |        | U 4 1        |

| 0018 | A TANKER AND A STREAM AND A STREAM |                  | 1                   |        | U12          |

| 0018 |                                    | )                | 1                   |        | U 1 4        |

| 0018 | 60 EPROM                           | 2732-4           | 1                   |        | U29          |

|      |                                    |                  |                     |        |              |

- 35 -

| CAPACII    |         | 1.1 | 0.1216.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |               |                        |          |