**OTHER IMSAI® PRODUCTS 8080 MICROCOMPUTER SYSTEM** FLOPPY DISK SYSTEM **DISK OPERATING SYSTEM** LINE PRINTER SYSTEM **MULTIPROCESSOR SYSTEM INTELLIGENT BREADBOARD SYSTEM AP-44 MINI-PRINTER HIGH-LEVEL LANGUAGES 8080 SYSTEM SOFTWARE PTR-30 CHARACTER PRINTER SYSTEM CRT TERMINAL SYSTEM COMPLETE LINE OF S-100 CARDS**

> IMSAI 14860 WICKS BLVD. SAN LEANDRO, CA.

# CAUTION

# FAILURE TO OBSERVE THESE IMPORTANT PRECAUTIONS WILL VOID WARRANTY

- 1. Read all material before beginning construction.

- 2. Use ONLY electronic quality rosin core solder.

- 3. Use extreme care with static-sensitive chips to prevent static discharge damage. (These chips are inserted in black conductive foam material in your kit.)

- 4. Do NOT plug or unplug boards while power is on.

- 5. Do NOT apply power to any board or circuit before checking each component and each trace.

- 6. Do NOT insert chips in socket before all soldering on the board is completed.

- 7. Do NOT use nonstandard parts such as fuses of a higher current rating.

- 8. Do NOT leave out any construction step.

- 9. Use only specified AC power.

- 10. Prevent flat cable end from touching areas of the system that may be carrying current.

- 11. Clean unit with soap and water or isopropyl alcohol only to prevent damage to plastic components.

- 12. Some repair operations are quite demanding. Do not attempt repairs beyond your level of skill to prevent damage to the board or the components.

- Use ONLY a 25 watt electronic soldering iron for assembly of your IMSAI kit.

- 14. Do NOT perform any solder work on a board while power is applied.

- 15. Do NOT plug or unplug a chip from a socket while power is applied.

- 16. Check power supply voltages BEFORE inserting any boards into chassis.

- For all assembled units, read USER GUIDE section for jumpering instructions.

- 18. To register your kit for warranty protection, fill out warranty cards and mail to IMSAI. Kits without warranty cards on file are NOT covered by warranty.

IMSAI

FLOPPY DISK SYSTEM

Copyright 1976 IMSAI Manufacturing Corporation 14860 Wicks Boulevard San Leandro, Ca. 94577 Made in U. S. A. All rights reserved worldwide.

# Errata 4/7/77

### IMPORTANT NOTICE

A Floppy Drive with Floppy Power Supply Rev. 3 is not compatible with a drive with FPS Rev.'s 0, 1 and 2; i.e., a dual drive system will not operate with a FPS Rev. 3 and one of the others. FPS Rev.'s 0, 1 and 2 are compatible, however. The difference is that with FPS Rev. 2 or earlier each drive requires a PLO Card, and with FPS Rev. 3 one PLO card is used for up to 4 drives. If you have recently purchased a drive with FPS Rev. 3 to modify a single drive system to dual, first check the Rev. # on the power supply in your present system. If it isn't Rev. 3, please notify one of our salespeople at 415-483-2093 before installing the new drive.

### IMSAI FLOPPY DISK SYSTEM MANUAL

TABLE OF CONTENTS

### PART 1 SYSTEM MANUAL

FUNCTIONAL DESCRIPTION System Components

SYSTEM THEORY OF OPERATION Operation of a Simple Floppy Disk System IMSAI Floppy Disk System

SYSTEM CONFIGURATION AND TESTING System Configuration System Testing

SYSTEM USER GUIDE User Controls System Initialization System Bootstrap Programming Guide

### PART 2 COMPONENTS OF THE SYSTEM

----THE CONTROLLER-----

INTERFACE MASTER Functional Description Theory of Operation Assembly Instructions User Guide

FLOPPY INTERFACE BOARD Functional Description Theory of Operation Assembly Instructions User Guide

FIRMWARE Functional Description Theory of Operation User Guide

### IMSAI FLOPPY DISK SYSTEM MANUAL

# TABLE OF CONTENTS

### -----THE DRIVE ASSEMBLY-----

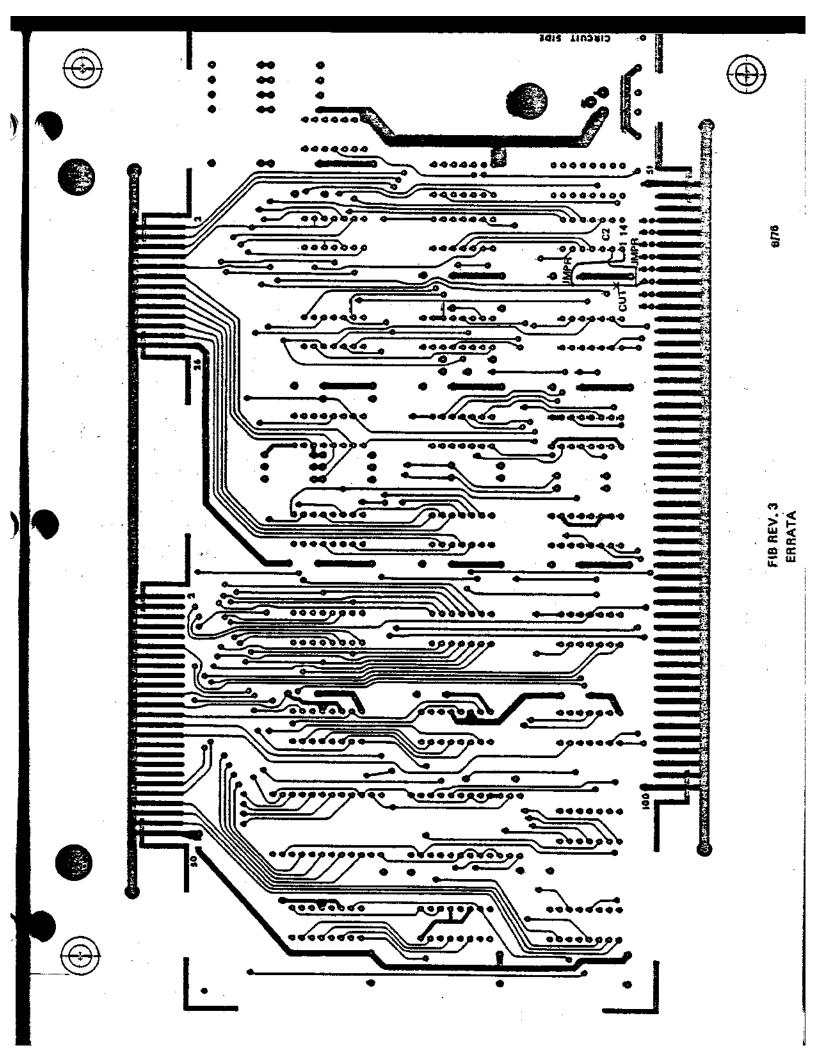

FLOPPY POWER SUPPLY Functional Description Theory of Operation Assembly Instructions User Guide

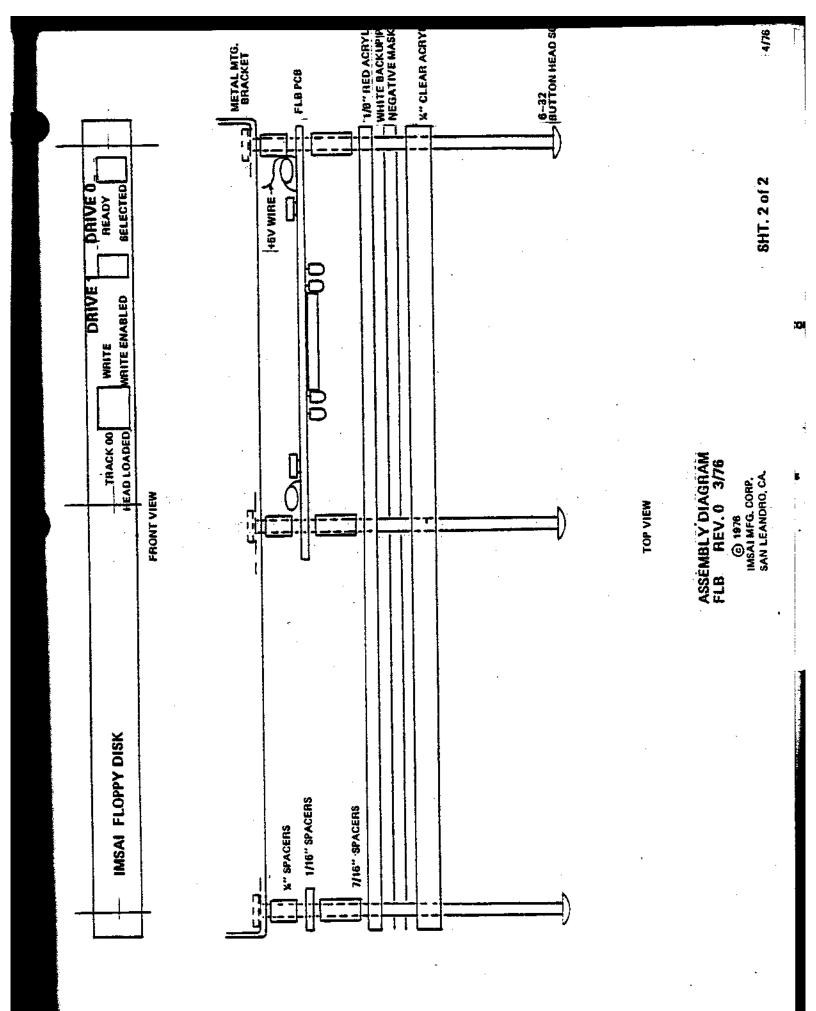

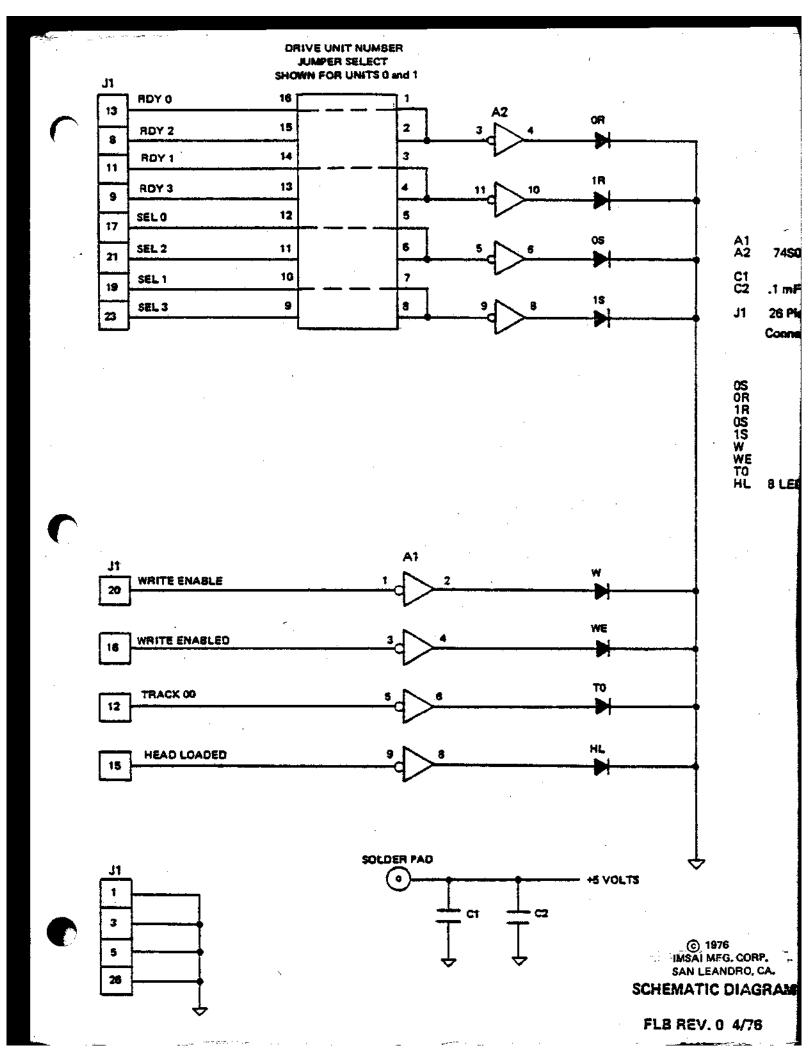

FLOPPY LIGHT BOARD Functional Description Theory of Operation Assembly Instructions User Guide

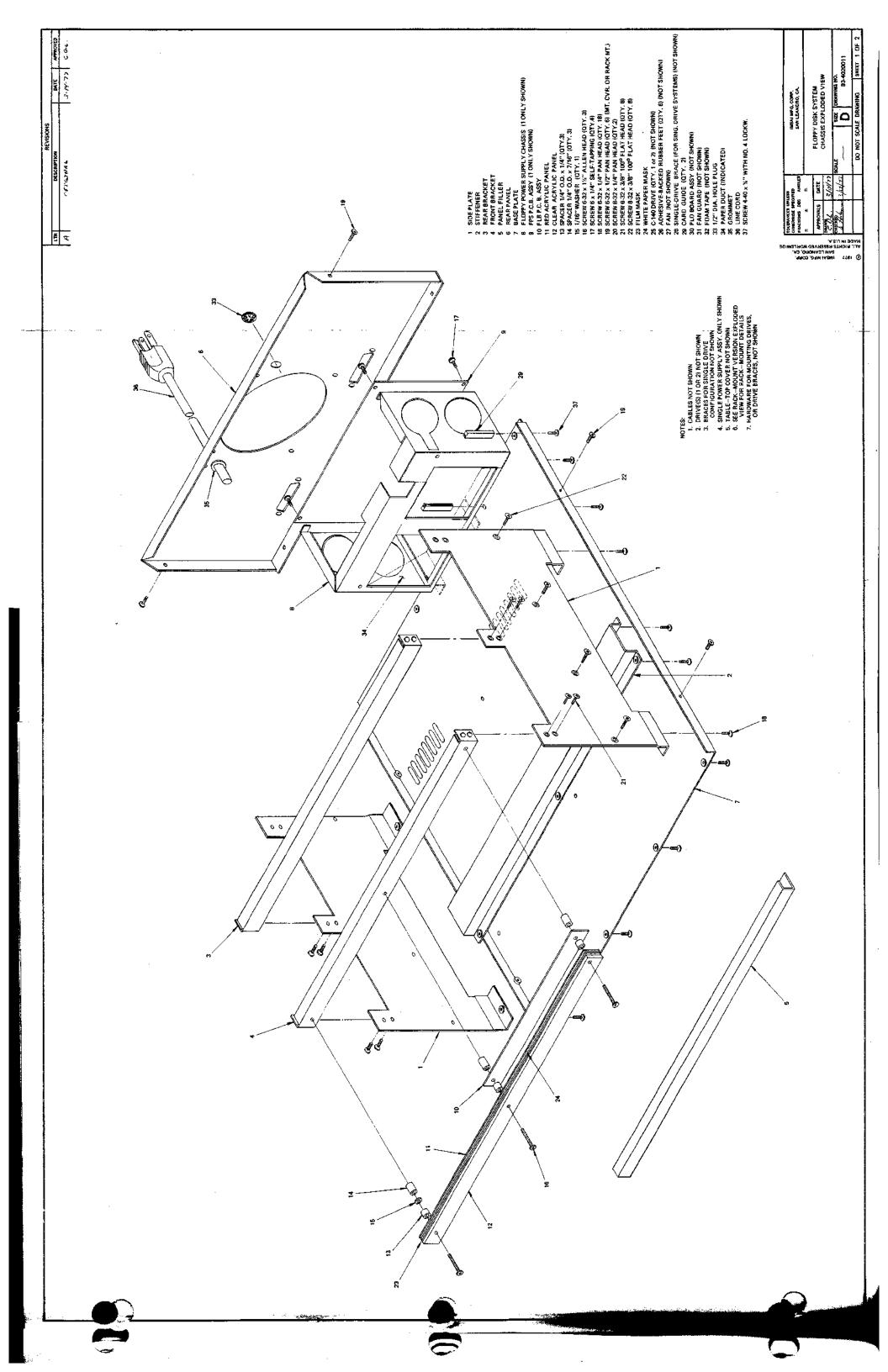

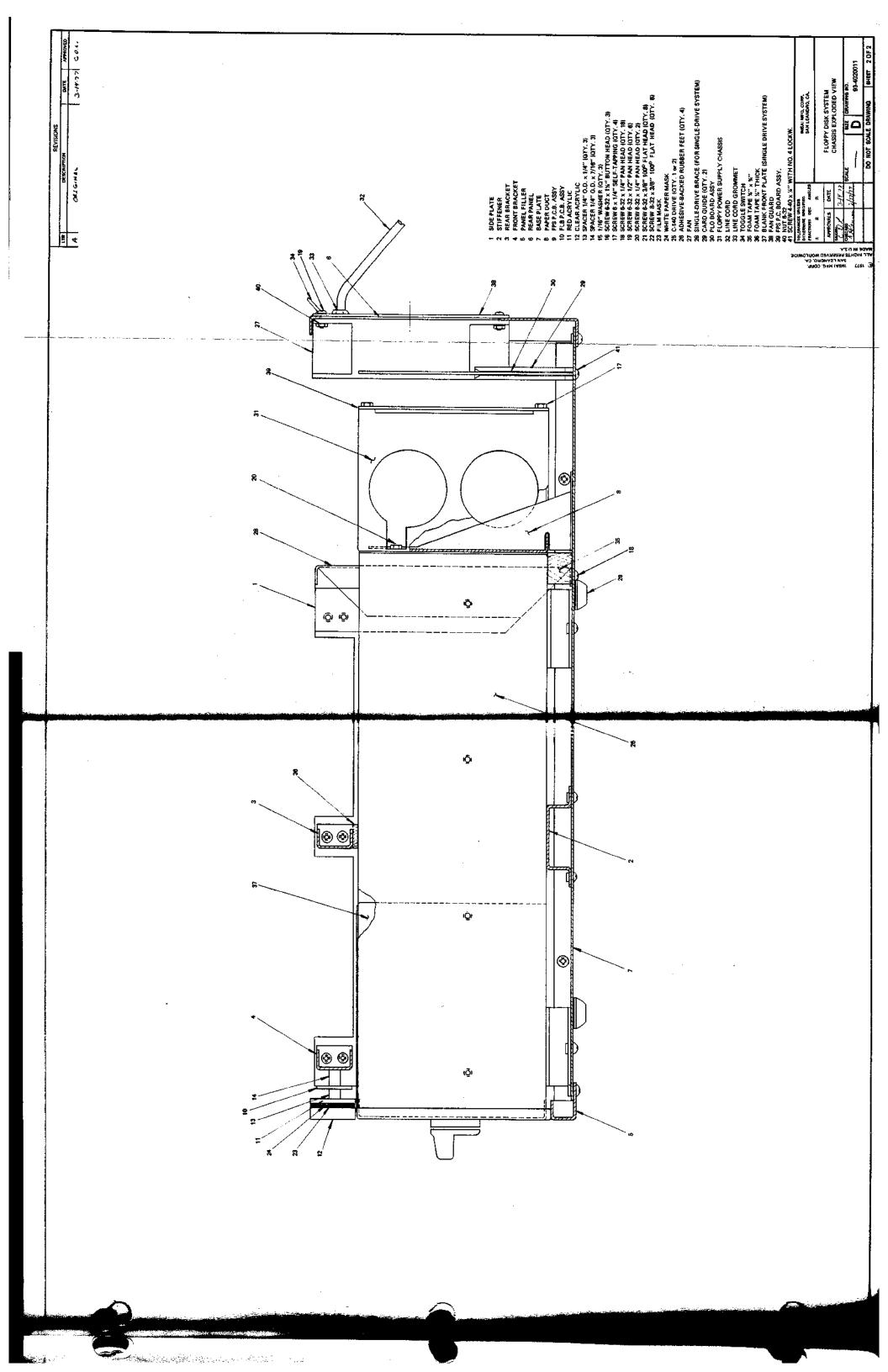

FLOPPY CABINET Functional Description. Assembly Instructions

### APPENDICES------

APPENDIX A CalComp OEM Reference Manual PURPOSE.....The IMSAI FLOPPY DISK MANUAL was designed as an aid and reference source to be used in understanding, assembling, and using the IMSAI FLOPPY DISK SYSTEM.

SCOPE.....It is assumed that the User is familiar with the operation of the IMSAI 8080 MICROCOMPUTER SYSTEM. Recommended references: 1. IMSAI 8080 USER MANUAL 2. INTEL 8080 Microcomputer Systems User Manual 3. Introduction To Micro-

processors - Osborne and Associates

- 1. THE SYSTEM

- 2. COMPONENTS OF THE . SYSTEM

THE SYSTEM section covers the operation of the IMSAI FLOPPY DISK as a SYSTEM.

THE COMPONENTS OF THE SYSTEM section covers the operation of the individual components which make up the IMSAI FLOPPY DISK SYSTEM.

FDM - 15

WHAT TO DO WHEN YOU GET YOUR SYSTEM------

- If you ordered an assembled FIF and FDC, proceed as follows:

- a. Turn to SYSTEM CONFIGURATION AND TESTING (p. 1 19).

- If you ordered and FIF kit and an assembled FDC, proceed as follows:

- a. Assemble the IFM as per the IFM ASSEMBLY INSTRUCTIONS (p. 2 - 17).

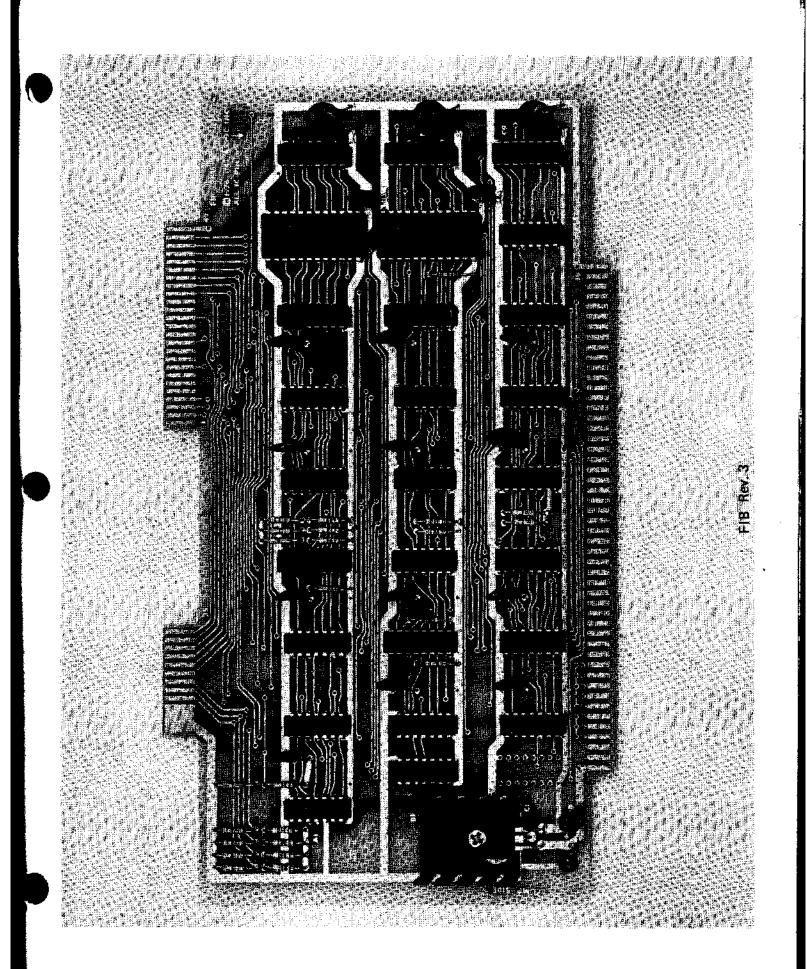

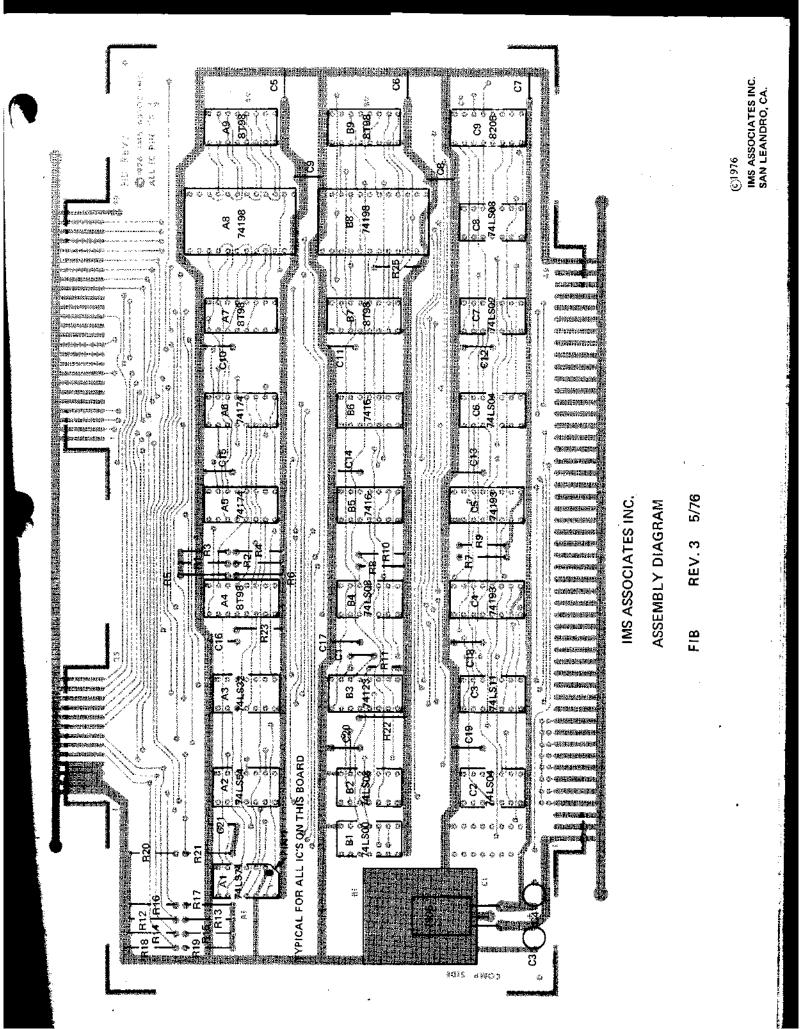

- b. Assemble the FIB as per the FIB ASSEMBLY INSTRUCTIONS (p. 3 - 23).

- c. Turn to SYSTEM CONFIGURATION AND TESTING (p. 1 - 19).

- If you ordered an FIF kit and an FDC kit, proceed as follows:

- a. Assemble the IFM as per the IFM ASSEMBLY INSTRUCTIONS (p. 2 - 17).

- b. Assemble the FIB as per the FIB ASSEMBLY INSTRUCTIONS (p. 3 - 23).

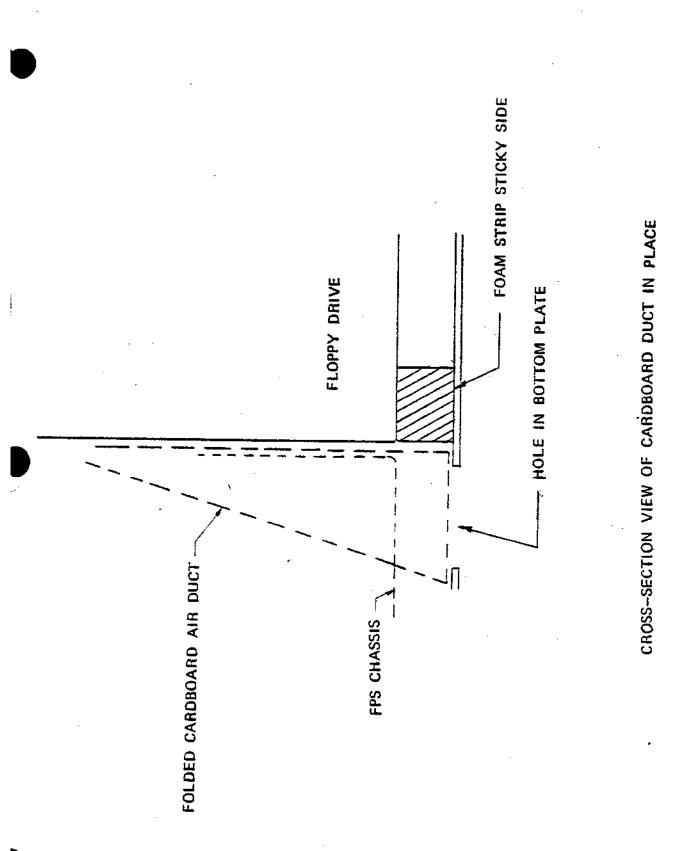

- c. Assemble the FPS as per the FPS ASSEMBLY INSTRUCTIONS (p. 5 - 29).

- d. Assemble the FLB as per the FLB ASSEMBLY INSTRUCTIONS (p. 6 - 17).

- e, Assemble the Floppy Cabinet as per the FLOPPY CABINET ASSEMBLY INSTRUCTIONS (p. 7 - 11).

- f. Turn to SYSTEM CONFIGURATION AND TESTING (p. 1 - 19).

# IMSAI FLOPPY DISK SYSTEM

# PART 1

# SYSTEM MANUAL

# FLOPPY DISK SISTEM Functional Description

### FUNCTIONAL DESCRIPTION

The IMSAI Floppy Disk System provides for control of up to 4 flexible disk drives from the IMSAI 8080 System.

Data formats are fully compatible with the IBM 3740 format, providing a total storage capacity of 1.94 M bits per flexible disk. This is organized as 77 tracks with 26 sectors per track. Each sector contains 128 bytes of data.

To allow for non 3740 compatible formats, provision is made for reading all clock and data bits in an unformatted mode. The firmware may also be changed by reprogramming to support varying densities and formats.

The IMSAI Floppy Disk System utilizes an intelligent dedicated controller with a DMA capability to free the main processor from the overhead associated with floppy disk control processing.

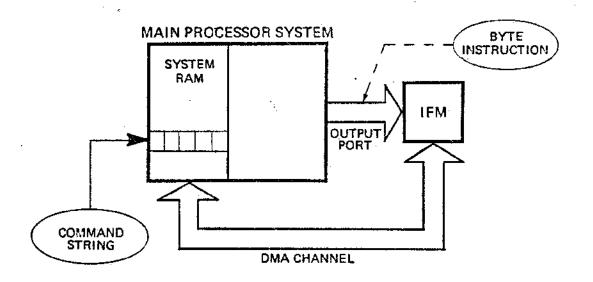

<u>Commands</u> to the Floppy Disk System are <u>initiated</u> from the main processor by means of an output instruction to the controller (Byte Command). The actual command is <u>executed</u> from a command string located in the main system memory. Up to 16 different command string pointers may co-exist at any one time, with the values of these command string pointers being User definable.

$1 - \bar{3}$

### SYSTEM COMPONENTS

The IMSAI Floppy Disk System consists of a <u>Controller Set</u> and a Drive Assembly.

The Controller Set is composed of two boards, the IFM (Interface Master) and the FIB (Floppy Interface Board).

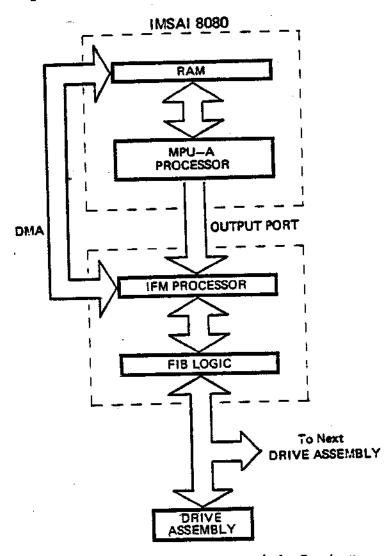

The IFM is a separate 8080 based processor used to control floppy disk functions. It contains the 8080, 512 bytes of RAM, 2K bytes of EPROM, and all support logic for the 8080 chip. Communications with the main system processor takes place through the DMA channel or the single output port.

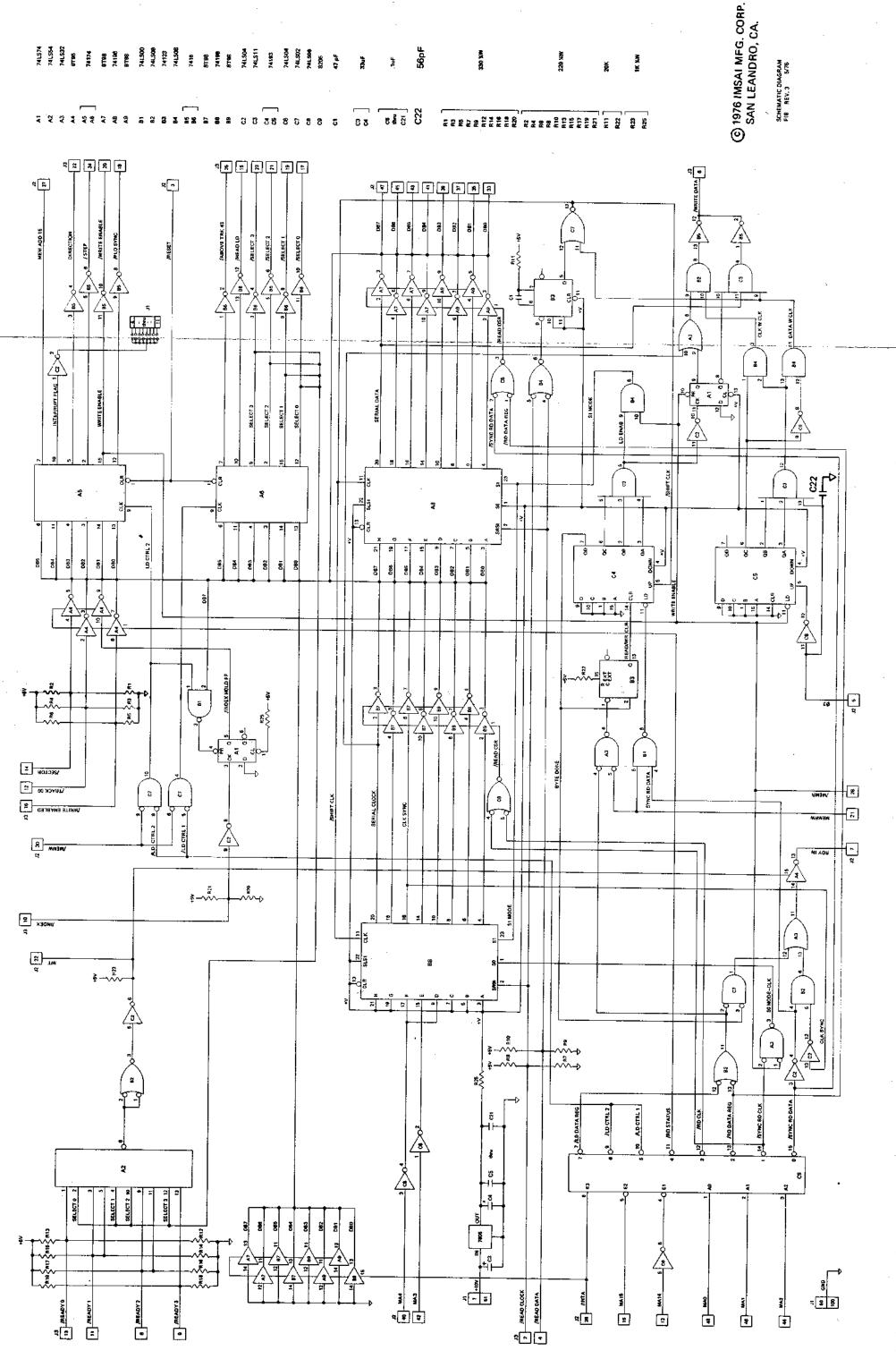

The <u>FIB</u> contains all the control logic necessary to drive the floppy disk from the IFM processor.

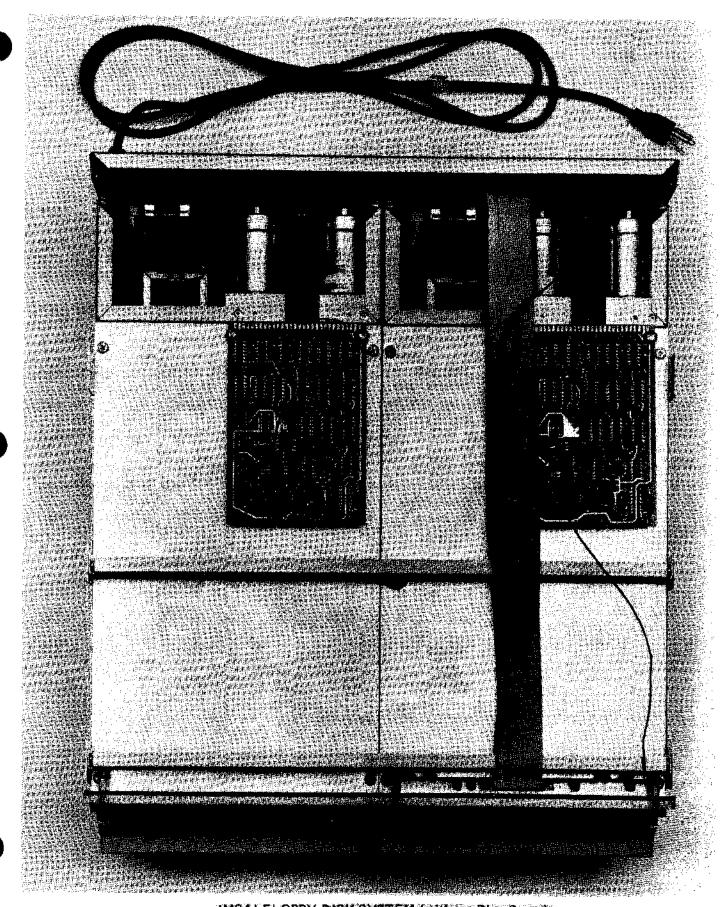

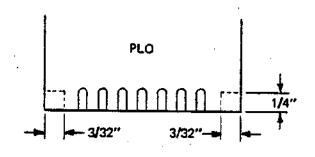

The Drive Assembly is composed of the Floppy Disk Drive, the Floppy Disk Cabinet, the FPS (Floppy Power Supply), the FLB (Floppy Light Board), and the PLO (data separator).

Each Floppy Cabinet houses up to two complete floppy drives with power supplies and a single FLB. In addition, the cabinet which houses Drive 0 contains a single PLO board which may be shared by up to 4 drives.

The Floppy Drive used in the system is the CalComp Model 140 providing up to 3.21 M bits of storage space (1.94 M bits with the IBM 3740 Format). Access times are 6ms track to track with a 10ms head stabilization.

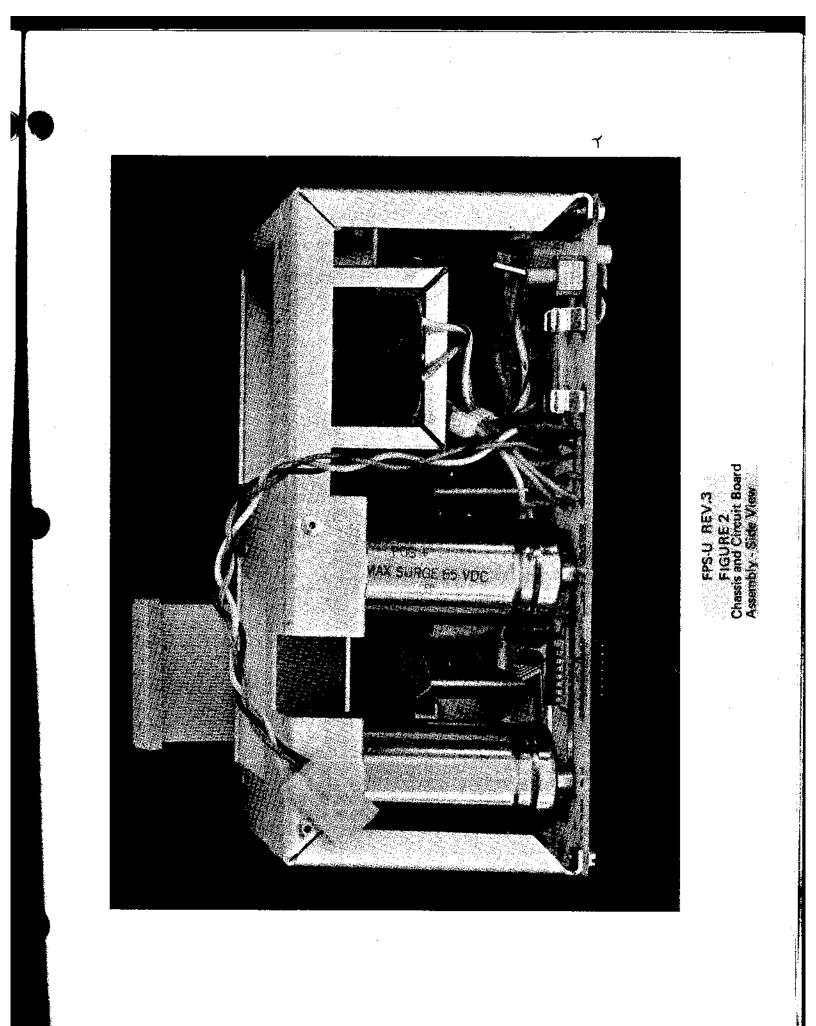

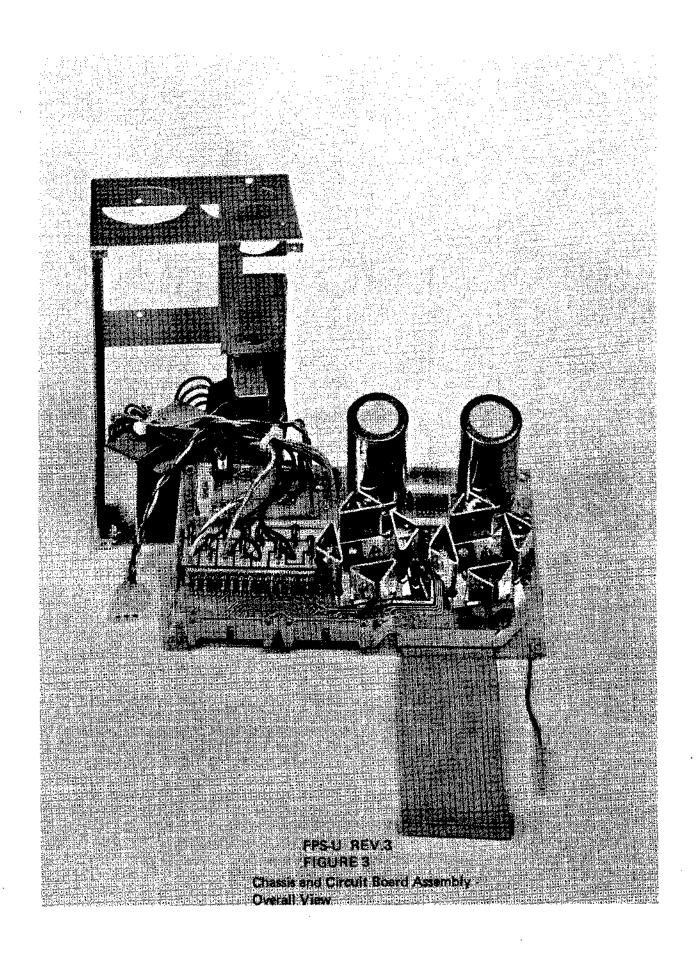

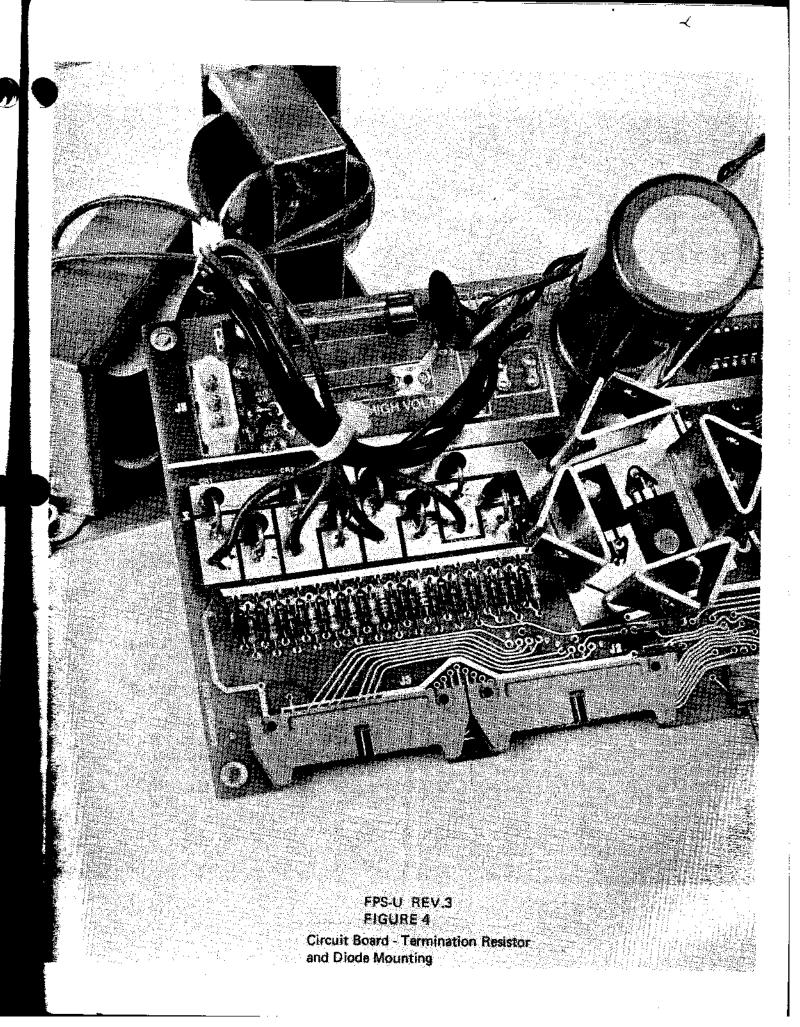

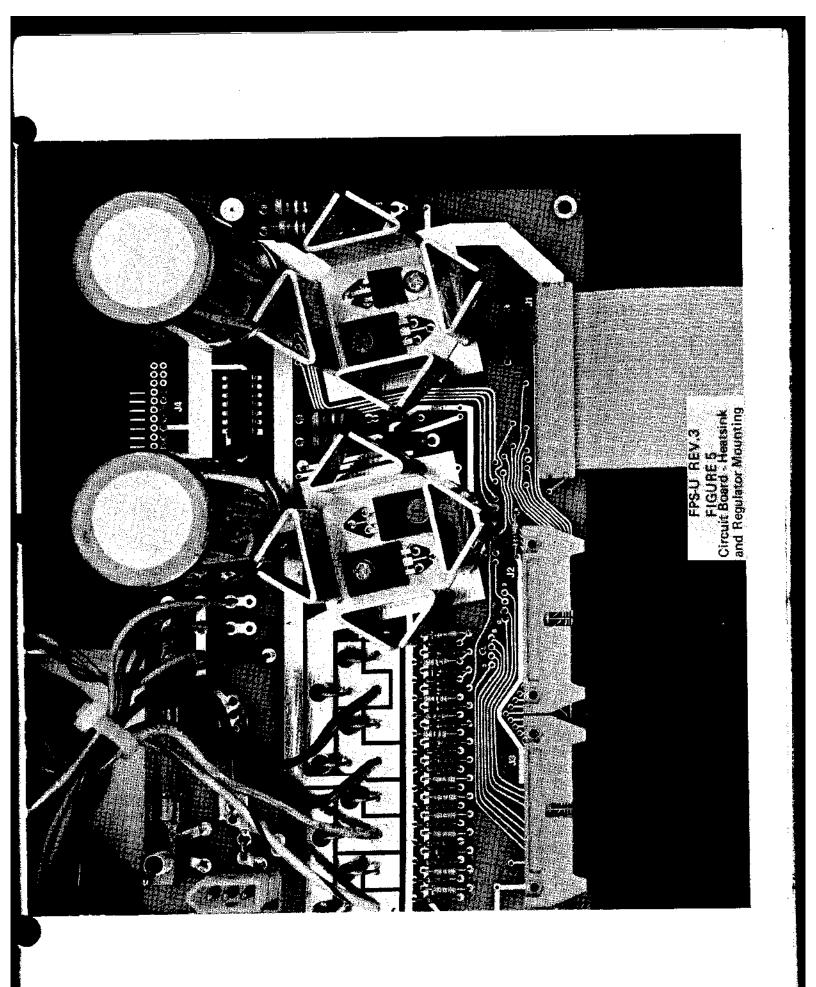

The FPS provides all power needed to run the floppy disk drives and FLB. Provision is also made to terminate all control and signal lines from the Floppy Controller Set.

The PLO Board ensures a high level of data integrity and allows for the detection of missing clock patterns as used with the IBM 3740 Data and Address Marks. SYSTEM THEORY OF OPERATION

Copyright 1977 IMSAI Manufacturing Corporation 14860 Wicks Boulevard San Leandro, California 94577

### THEORY OF OPERATION

### PREFACE

This section is intended to help the User gain a general understanding of how the IMSAI Floppy Disk System functions as a whole. The operation of a theoretical floppy disk system is first presented to convey a general understanding of the principles involved in floppy disk transfers. Once this is achieved the operation of the IMSAI Floppy Disk System is explained.

Systems Operation does not cover the detailed logic and timing functions. If this information is desired the User should reference the Theory of Operations section for the individual system component.

### I. FLOPPY DISK SYSTEMS IN GENERAL

A floppy disk system allows for the storage and retrieval of blocks of data between the main system memory and a storage medium, the floppy diskette.

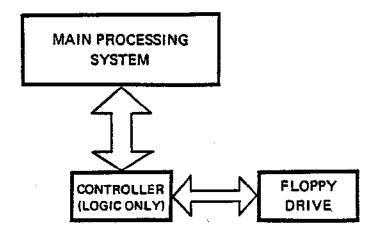

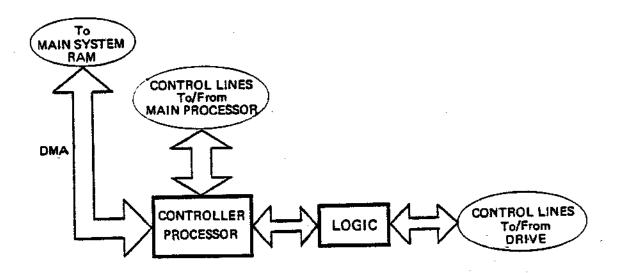

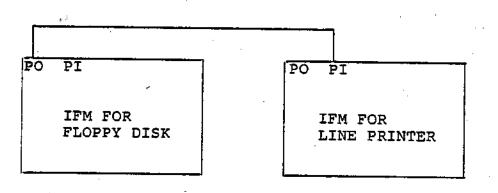

The floppy disk system shown in Figure 1 provides the framework for a discussion of the processes involved in general floppy disk transfers. This floppy disk system is assumed to interface to a main processing. system and is composed of two major elements:

- 1) a controller

- 2) a drive

FIGURE 1, a simple floppy disk system

The <u>controller</u> contains all of the logic necessary to interface the floppy disk drive with the main processing system. All transfer routines are taken care of by the main processor. Note that control resides with the main processor only.

The <u>drive</u> contains the floppy disk storage unit which utilizes a moveable read/write head to access information stored on a flexible diskette.

# DATA FORMATS

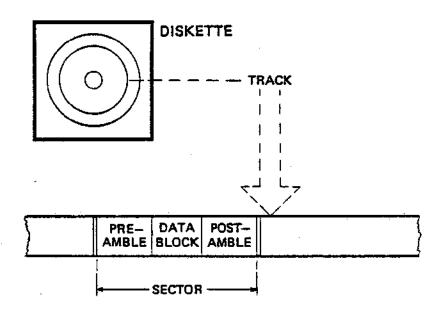

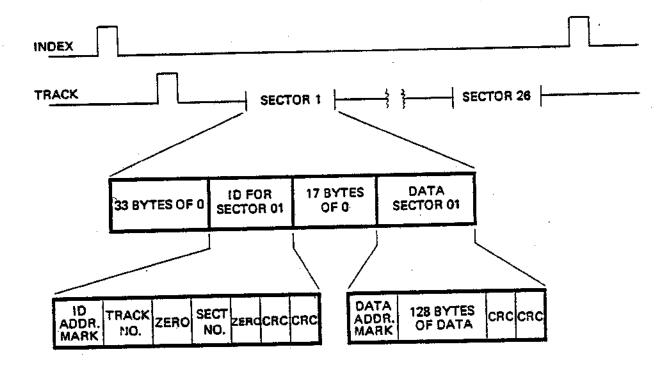

The data on the diskette is organized into tracks and sectors.

A track can be conceived of as a circular ring with its center located at the physical center of the diskette. If the read/write head is located a "distance" n from the center of the diskette, the nth track is defined as the area passing directly under the head in one complete revolution of the diskette.

Each track consists of a number of <u>sectors</u>. A sector is composed of preamble information, a data block, and postamble information. (See figure 2.)

A preamble information will normally contain: 1) a set pattern to indicate the start of a sector; 2) the track address; and 3) the sector address.

The data block contains the actual data transferred from the system's main memory.

The postamble information will normally include: 1) a number of check characters and 2) a gap to fill the end of a sector.

WRITE PROCESSES in a simple floppy disk system.

Assume there exists a block of data located in the system RAM which is to be stored on a floppy diskette. For simplicity, assume that the block size is equal to the sector data block size. In order to set up the transfer, the processor needs to get the address of the data block in system RAM and the location of the destination on the diskette (track and sector). Prior to executing the transfer, the processor needs to compute check characters for the block of data to be

FIGURE 2, tracks and sectors

transferred. The check characters are used to verify the validity of the data when the block is read back into memory.

At this point the processor tells the floppy controller to position the head over the destination track and sector on the diskette. Once the floppy acknowledges it has positioned the head over the correct location, the processor sets the write enable and executes the transfer a word at a time until the block transfer is complete.

The check characters are then stored in the postamble, and the write enable is turned off. The process of writing onto the diskette is complete.

READ PROCESSES in a simple floppy disk system.

Transferring a block of data stored on diskette to the main processor's memory involves a similar process. The processor first needs to get the location of the data block on the diskette (track and sector) and the address of the destination in the system RAM.

The processor then commands the floppy to position the head over the desired track and sector. When the floppy acknowledges it has found the requested track and sector, the processor begins reading the data from the diskette into a previously defined storage area until the block read is complete.

The check characters (CRC) are then read and checked to insure the validity of the data. If the CRC is correct, the processor transfers the data from the storage area to the desired destination in the system RAM, thus completing the block read process.

# ADDITIONAL HARDWARE FEATURES

With a basic understanding of the processes involved in floppy disc transfers, we can upgrade and improve the floppy disc system shown in figure 1 by: 1) using a separate processor in the controller; and 2) providing the controller with a DMA channel to the main system RAM.

Use of a separate processor in the controller to control floppy disc transfers will free up the main processor from the overhead associated with the previously discussed control processes and floppy housekeeping routines.

FIGURE 3, proposed floppy controller

Introducing a DMA channel into the proposed design of the controller allows for a <u>direct</u> access into the main system memory. The process of accessing system RAM then becomes essentially transparent to the main processor.

# II. THE IMSAI FLOPPY DISK SYSTEM

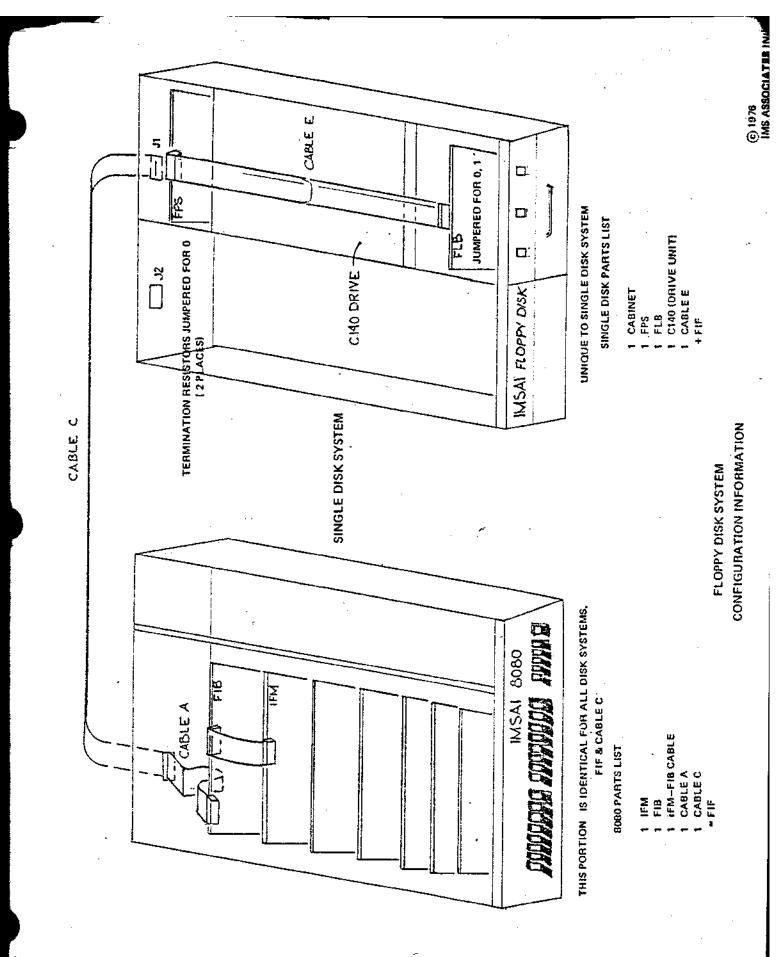

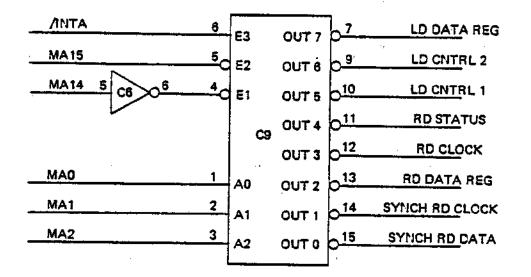

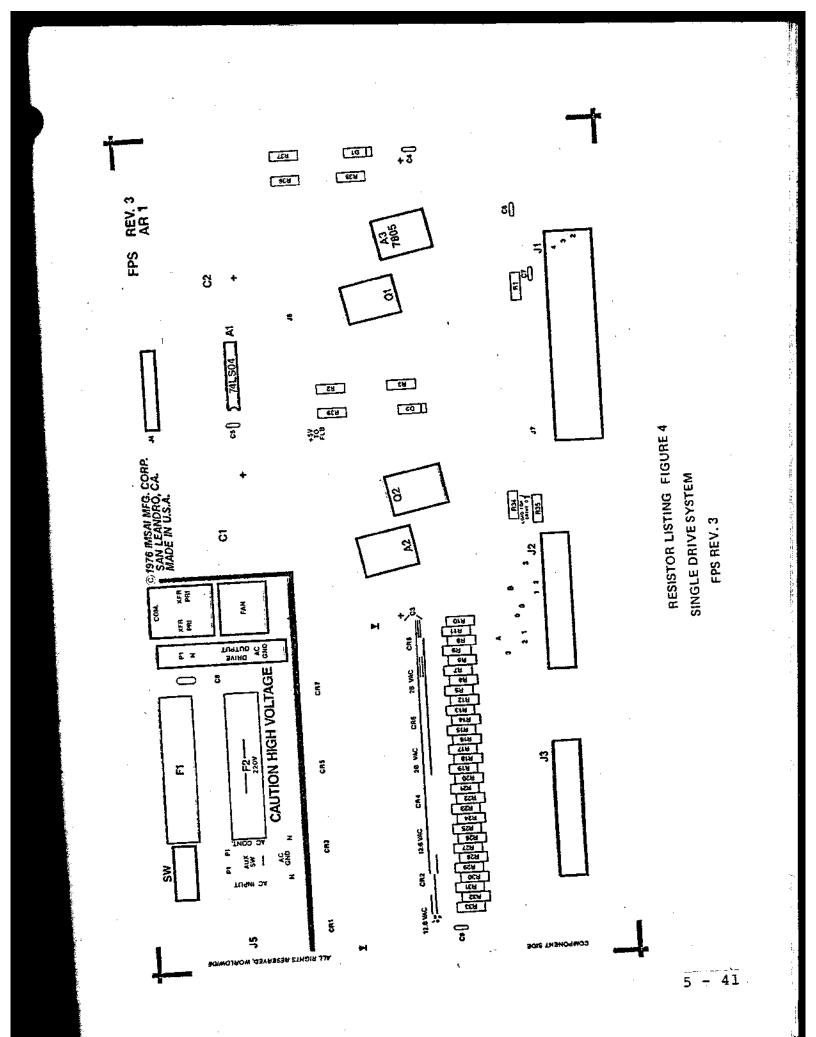

The IMSAI Floppy Disk System consists of a Controller and Drive Assembly shown in figure 4.

The Controller contains an 8080 based processor and all logic necessary to interface up to four floppy disk drives from the 8080 microprocessor. The firmware, located in the Controller's 2K bytes of EPROM, contains the driving program for the IFM processor and supports the IBM 3740 Data Format.

FIGURE 4, IMSAI Floppy Disk System

# IBM 3740 FORMAT

The IBM 3740 format is organized into 77 tracks. Track 0 is used for Data Set Labels which contain descriptive information regarding data residing on tracks 01 through 76. Tracks 01 through 73 and 75 to 76 contain 26 sectors each with 128 data bytes per sector. Track 74 is not used.

Each data track has an Index Mark, a preamble, 26 sectors and a postamble. The organization of each sector is shown in figure 5. Both the ID Address Mark and the Data Address Mark consist of a particular pattern of missing clock pulses. These are used by the controller for synchronization.

For more detailed imformation refer to IBM publication GA21-9190.

FIGURE 5, IBM Data Format

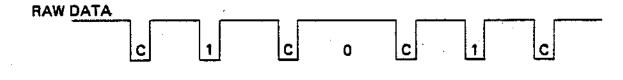

### RECORDING FORMAT

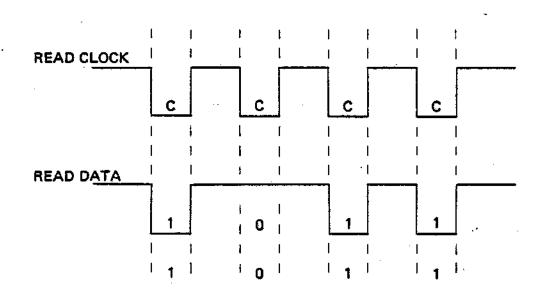

In the IMSAI Floppy Disk System, both clocks and data are recorded on the disk utilizing a double frequency (FM) recording format. This format utilizes clocks to define bit cell times. The presence of a flux reversal between clocks is defined as a "one" bit. The absence of a flux reversal between clocks is defined as a "zero" bit. Figure 6 is an example of FM encoded data written on the disk.

### FIGURE 6, Raw Data

### Data Recovery with the IBM 3740 Format

To allow recovery of data when using IBM 3740 formats, a PLO data separator is used. When synchronized, the PLO takes raw data from the disk and provides separated, coincident data and clock pulses to the FIB board. Figure 7 is an example of data and clock outputs from the PLO. A "one" bit may be detected as coincident pulses occurring on the data and clock lines.

Separated data and clock lines allow for the detection of ID and Data Address Marks which utilize a missing clock pattern. All missing clock patterns of significance in the 3740 format have a missing clock pulse in bit 5. Therefore, an ID or Data Address Mark is detected by checking for a missing clock pulse in this bit position.

1 - 11

### FIGURE 7, PLO outputs

# MAIN PROCESSOR CONTROL OF FLOPPY DISK FUNCTIONS

Execution of a disk transfer operation is determined by Command Strings which reside in the main processor's memory. The execution of these Command Strings are initiated from the Main Processor by means of an output instruction.

The byte output to the IFM processor will contain a BYTE COMMAND number of 0 in the high 4 order bits and a pointer number to a particular Command String in the low 4 order bits.

Upon receipt of this Byte Command, the IFM processor will DMA the Command String pointed to in main memory and execute the command defined therein.

### WRITE PROCESSES IN THE IMSAI FLOPPY DISK SYSTEM

### MAIN SYSTEM PROCESSES

Assume there exists a block of data located in the main system RAM to be transferred to floppy disk. The main processor needs to first set-up the COMMAND STRING in main memory with 1) the command number for a sector write; 2) zero in the Status Byte; 3) the destination track and sector number and 4) the address in memory of the data block to be transferred.

The main processor then outputs a BYTE INSTRUC-TION 0 to the IFM output port to initiate the execution of the write. The acknowledgement of a completed operation will be indicated by a nonzero value being stored in the status word of the COMMAND STRING. Thus once the processor issues the BYTE COMMAND 0, it only need wait for the status word to go non-zero before proceeding with another disk operation.

### CONTROLLER PROCESSES

When the IFM board receives the output instruction (BYTE COMMAND 0), it lowers the Main Processor's READY line. The Main Processor goes into a WAIT state and the IFM Processor reads the output word from the system data bus into its own accumulator. Once the BYTE COMMAND is read the IFM Processor raises the System READY line to allow the SYSTEM to continue. The output word 0 is decoded by the IFM firmware as being a command to execute from the COMMAND STRING located in the System RAM.

### DMA FUNCTIONS

The IFM processor will present a HOLD REQUEST to the System, and the System will respond with HOLD ACKNOWLEDGED. At this point the System is in a HOLD STATE and the IFM processor will disable all of the Main Processor's address, data, and status lines (with the exception of PHLDA). The IFM processor then gates its own address, data and status lines onto the System Bus.

The COMMAND STRING is now transferred to the IFM RAM from the System RAM, and the HOLD REQUEST is released, allowing the System to continue with its own processing activity.

The Command Number is decoded as a Write operation. The IFM processor transfers the Data block to the IFM RAM. This transfer is accomplished by DMA'ing a Byte at a time in the HOLD MODE during state T3 (or the state following T3) of the main processor's machine cycle.

To proceed with the WRITE operation, the IFM processor computes and stores the CRC characters in its own RAM.

# TRACK POSITIONING

A request is issued to the FIB to load the head, sync the PLO, and then to synchronize on the ID Address Mark. The FIB then places the IFM Processor in a WAIT State until it has found the desired missing clock pattern.

Once the FIB has recognized the Address Mark, it raises the IFM READY line, allowing the IFM processor to read and check the track address. A compare is made to see if the head is positioned over the desired track. If not, the direction and Step lines are used to reposition the head over the destination track.

### SECTOR POSITIONING

Once again the IFM Processor issues a request to the FIB to synchronize on the ID Address Mark. The IFM is again placed in a WAIT State until the ID Address Mark is recognized. Once the IFM is allowed to continue, it reads and checks track and sector number, this time looking for the destination sector. If the head is verified to be positioned over the desired sector, the IFM processor waits 12 bytes before writing the remaining five 0 bytes, the Data Address Mark, 128 bytes of data, and the 2 CRC characters according to the IBM 3740 Data Format.

# COMPLETION OF THE OPERATION

At this point, the Write operation is complete and the IFM board will indicate the results of the operation to the Main System by storing a non-zero value in the Status Word of the COMMAND STRING, via the DMA channel.

# READ PROCESSES IN THE IMSAI FLOPPY DISK SYSTEM

# MAIN SYSTEM PROCESSES

To prepare for a Read operation the main processor sets up the COMMAND WORD in its RAM with:

- 1) The Command Number for a sector Read;

- 2) zero in the Status Byte;

- 3) the track and sector number for the data block to be read from the diskette;

- 4) the Address of the destination in Main memory.

The main processor then issues an output instruction (BYTE COMMAND 0) to initiate the READ operation. The main processor waits until the Status Byte of the COMMAND STRING goes nonzero before proceeding with another disk operation.

## CONTROLLER PROCESSES

As before, the IFM processor will receive the output instruction from the main processor and decode it as an execute from COMMAND STRING.

The COMMAND STRING will be transferred from the System RAM to the IFM memory via the DMA access channel. The Command Number is decoded as a READ operation and the IFM processor positions the read/write head over the desired track and sector as before. Once the head is correctly positioned, the IFM processor waits for the Data Address Mark.

When the Data Address Mark is recognized, 128 bytes of data are read into the IFM RAM. The two CRC characters are then read and checked to verify the data block. If the data block is verified, it is written into the main processor's RAM via the DMA channel.

To acknowledge completion of the READ operation, the IFM processor will store a non-zero value in the Status Byte. This value is then passed to the COMMAND STRING located in the main system RAM via the DMA channel.

# SYSTEM CONFIGURATION

# AND TESTING

Copyright 1977 IMSAI Manufacturing Corporation 14860 Wicks Boulevard San Leandro, California 94577

# CONFIGURATION INFORMATION

Constant and the

| FIF-1 CONSISTING OF:                             |                                                                                                                                                                                    | ORDER:                                                                                                                                         |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 IFM                                            | 1 CABINET                                                                                                                                                                          | l FIF                                                                                                                                          |

|                                                  | 1 FPS (#0)                                                                                                                                                                         | 1 FDC 2-1 (#0)                                                                                                                                 |

| 1 CABLE A                                        | 1 FLB (#0-1)                                                                                                                                                                       |                                                                                                                                                |

| 1 CABLE C                                        | 1 C140 DRIVE UNIT                                                                                                                                                                  |                                                                                                                                                |

| 1 CABLE F                                        | 1 CABLE E                                                                                                                                                                          |                                                                                                                                                |

| THA DEAK ANATH                                   | · ·                                                                                                                                                                                |                                                                                                                                                |

| TWO DISK SYSTEM                                  |                                                                                                                                                                                    |                                                                                                                                                |

| FIF-1 AS PER                                     | l CABINET                                                                                                                                                                          | ORDER:                                                                                                                                         |

|                                                  | 2 FPS (#0)                                                                                                                                                                         |                                                                                                                                                |

|                                                  | (#1)                                                                                                                                                                               | l FIF l FIF                                                                                                                                    |

|                                                  |                                                                                                                                                                                    | 1 FDC 2-1 OR 1 FDC 2-                                                                                                                          |

|                                                  | 2 CABLE E                                                                                                                                                                          | 1 FDC                                                                                                                                          |

|                                                  | 2 C140 DRIVE UNITS                                                                                                                                                                 | (DRIVE 0,1)                                                                                                                                    |

|                                                  |                                                                                                                                                                                    |                                                                                                                                                |

|                                                  |                                                                                                                                                                                    |                                                                                                                                                |

| THREE DISK SYSTEM                                |                                                                                                                                                                                    | <b>*************************************</b>                                                                                                   |

| FIF-1 AS PER                                     | CABINET WITH 2 DRIVES                                                                                                                                                              | ORDER:                                                                                                                                         |

| ABOVE                                            | AS PER ABOVE AND                                                                                                                                                                   |                                                                                                                                                |

|                                                  |                                                                                                                                                                                    |                                                                                                                                                |

|                                                  |                                                                                                                                                                                    | סדסן סדסן                                                                                                                                      |

| <br>-<br>-                                       | 1 CABINET                                                                                                                                                                          | 1 FIF 1 FIF                                                                                                                                    |

| <br>                                             | 1 FPS (#2)                                                                                                                                                                         | 2 FDC 2-1 1 FDC 2-                                                                                                                             |

| · · ·                                            | 1 FPS (#2)<br>1 FLB (#2-3)                                                                                                                                                         | 2 FDC 2-1 1 FDC 2-<br>1 FDC <u>OR</u> 1 FDC 2-                                                                                                 |

| · · · ·                                          | 1 FPS (#2)<br>1 FLB (#2-3)<br>1 C140 DRIVE UNIT                                                                                                                                    | 2 FDC 2-1 1 FDC 2-                                                                                                                             |

|                                                  | 1 FPS (#2)<br>1 FLB (#2-3)<br>1 C140 DRIVE UNIT<br>1 CABLE E                                                                                                                       | 2 FDC 2-1 1 FDC 2-<br>1 FDC <u>OR</u> 1 FDC 2-<br>1 CABLE C                                                                                    |

|                                                  | 1 FPS (#2)<br>1 FLB (#2-3)<br>1 C140 DRIVE UNIT                                                                                                                                    | 2 FDC 2-1 1 FDC 2-<br>1 FDC <u>OR</u> 1 FDC 2-                                                                                                 |

|                                                  | 1 FPS (#2)<br>1 FLB (#2-3)<br>1 C140 DRIVE UNIT<br>1 CABLE E<br>1 CABLE C                                                                                                          | 2 FDC 2-1 1 FDC 2-<br>1 FDC <u>OR</u> 1 FDC 2-<br>1 CABLE C                                                                                    |

| FOUR DISK SYSTEM                                 | 1 FPS (#2)<br>1 FLB (#2-3)<br>1 C140 DRIVE UNIT<br>1 CABLE E<br>1 CABLE C                                                                                                          | 2 FDC 2-1 1 FDC 2-<br>1 FDC <u>OR</u> 1 FDC 2-<br>1 CABLE C<br>(DRIVE 0,1,2)                                                                   |

| <u>Four disk system</u><br>Fif-1 as per          | 1 FPS (#2)<br>1 FLB (#2-3)<br>1 C140 DRIVE UNIT<br>1 CABLE E<br>1 CABLE C                                                                                                          | 2 FDC 2-1 1 FDC 2-<br>1 FDC <u>OR</u> 1 FDC 2-<br>1 CABLE C                                                                                    |

|                                                  | <pre>1 FPS (#2) 1 FLB (#2-3) 1 C140 DRIVE UNIT 1 CABLE E 1 CABLE C CABINET WITH 2 DRIVES AS PER ABOVE AND 1 CABINET</pre>                                                          | 2 FDC 2-1 1 FDC 2-<br>1 FDC <u>OR</u> 1 FDC 2-<br>1 CABLE C<br>(DRIVE 0,1,2)                                                                   |

| <u>FOUR DISK SYSTEM</u><br>FIF-1 AS PER          | 1 FPS (#2)<br>1 FLB (#2-3)<br>1 C140 DRIVE UNIT<br>1 CABLE E<br>1 CABLE C<br>CABINET WITH 2 DRIVES<br>AS PER ABOVE AND                                                             | 2 FDC 2-1 1 FDC 2-<br>1 FDC <u>OR</u> 1 FDC 2-<br>1 CABLE C<br>(DRIVE 0,1,2)<br>ORDER:<br>1 FIF 1 FIF                                          |

| <u>Four disk system</u><br>Fif-1 as per          | <pre>1 FPS (#2) 1 FLB (#2-3) 1 C140 DRIVE UNIT 1 CABLE E 1 CABLE C CABINET WITH 2 DRIVES AS PER ABOVE AND 1 CABINET</pre>                                                          | 2 FDC 2-1 1 FDC 2-<br>1 FDC <u>OR</u> 1 FDC 2-<br>1 CABLE C<br>(DRIVE 0,1,2)<br>ORDER:<br>1 FIF 1 FIF                                          |

| <u>Four disk system</u><br>Fif-1 as per          | <pre>1 FPS (#2)<br/>1 FLB (#2-3)<br/>1 C140 DRIVE UNIT<br/>1 CABLE E<br/>1 CABLE C<br/>CABINET WITH 2 DRIVES<br/>AS PER ABOVE AND<br/>1 CABINET<br/>2 FPS (#2)</pre>               | 2 FDC 2-1 1 FDC 2-<br>1 FDC <u>OR</u> 1 FDC 2-<br>1 CABLE C<br>(DRIVE 0,1,2)<br>ORDER:<br>1 FIF 1 FIF<br>2 FDC 2-1 <u>OR</u> 2 FDC 2-          |

| <u>FOUR DISK SYSTEM</u><br>FIF-1 AS PER<br>ABOVE | <pre>1 FPS (#2)<br/>1 FLB (#2-3)<br/>1 C140 DRIVE UNIT<br/>1 CABLE E<br/>1 CABLE C<br/>CABINET WITH 2 DRIVES<br/>AS PER ABOVE AND<br/>1 CABINET<br/>2 FPS (#2)<br/>(#3)</pre>      | 2 FDC 2-1 1 FDC 2-<br>1 FDC <u>OR</u> 1 FDC 2-<br>1 CABLE C<br>(DRIVE 0,1,2)<br>ORDER:<br>1 FIF 1 FIF<br>2 FDC 2-1 <u>OR</u> 2 FDC 2-<br>2 FDC |

| <u>FOUR DISK SYSTEM</u><br>FIF-1 AS PER<br>ABOVE | <pre>1 FPS (#2) 1 FLB (#2-3) 1 C140 DRIVE UNIT 1 CABLE E 1 CABLE C  CABINET WITH 2 DRIVES AS PER ABOVE AND 1 CABINET 2 FPS (#2)         (#3) 1 FLB (#2-3) 2 C140 DRIVE UNITS</pre> | 2 FDC 2-1 1 FDC 2-<br>1 FDC <u>OR</u> 1 FDC 2-<br>1 CABLE C<br>(DRIVE 0,1,2)<br>ORDER:<br>1 FIF 1 FIF<br>2 FDC 2-1 <u>OR</u> 2 FDC 2-<br>2 FDC |

### FLOPPY DISK SYSTEM System Configuration

IMSAI FLOPPY DISK SYSTEM CONFIGURATION GUIDE -----

The information here is presented to serve as a reference in configuring an IMSAI Floppy Disk System once its components have been assembled.

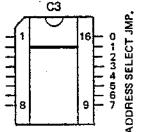

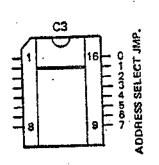

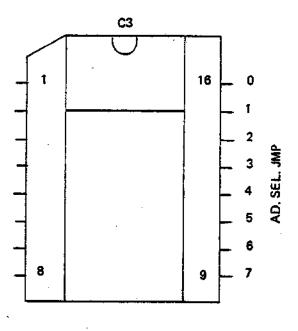

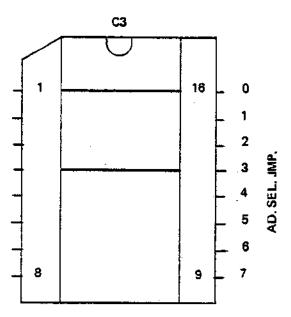

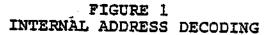

SET THE ADDRESS for the IFM output port by configuring the header for the address jumper socket in position C3 (IFM). IMSAI standard Floppy address is FD (Hex).

•2. INSERT THE IFM AND FIB BOARDS into two slots in the IMSAI 8080 Motherboard.

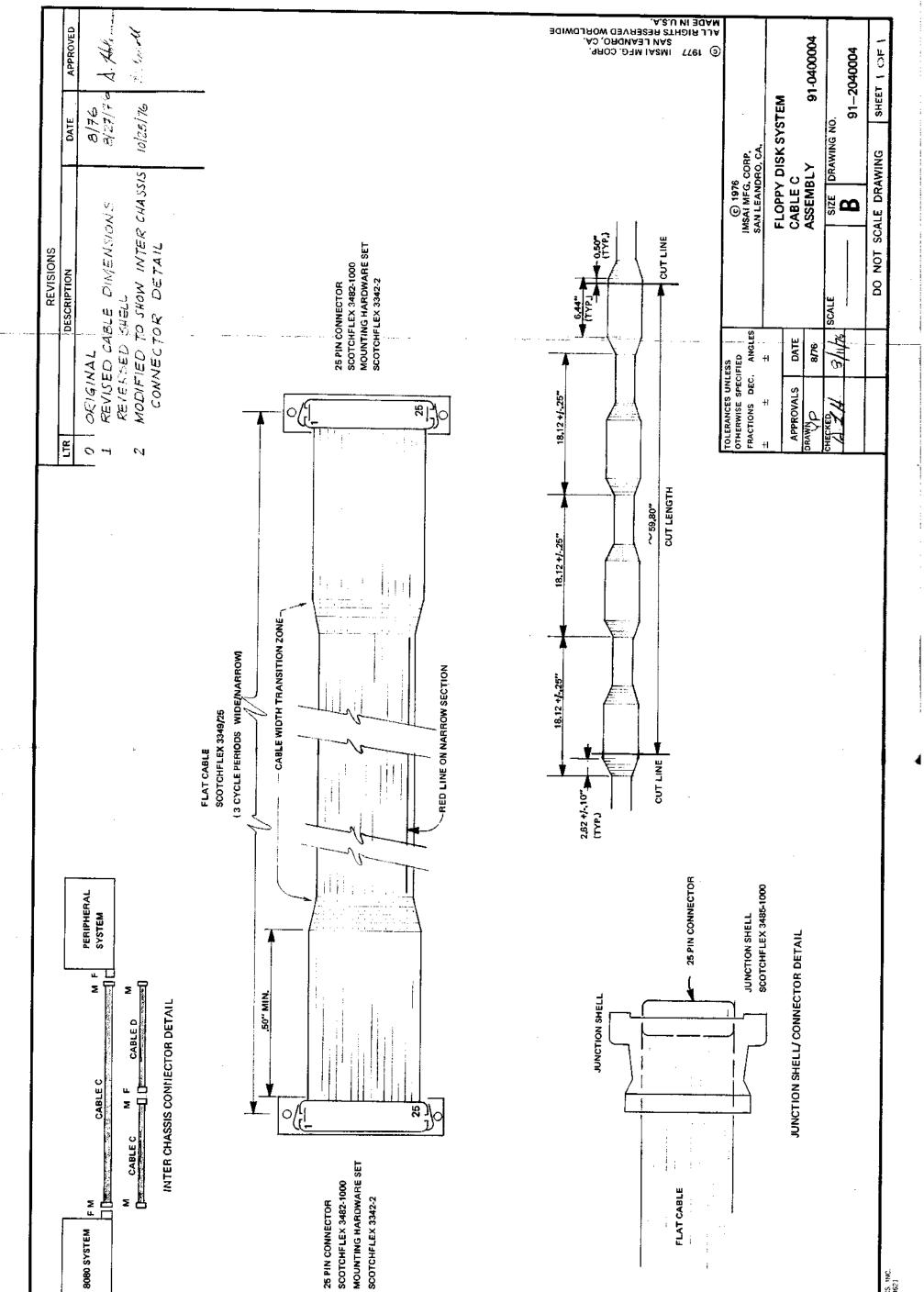

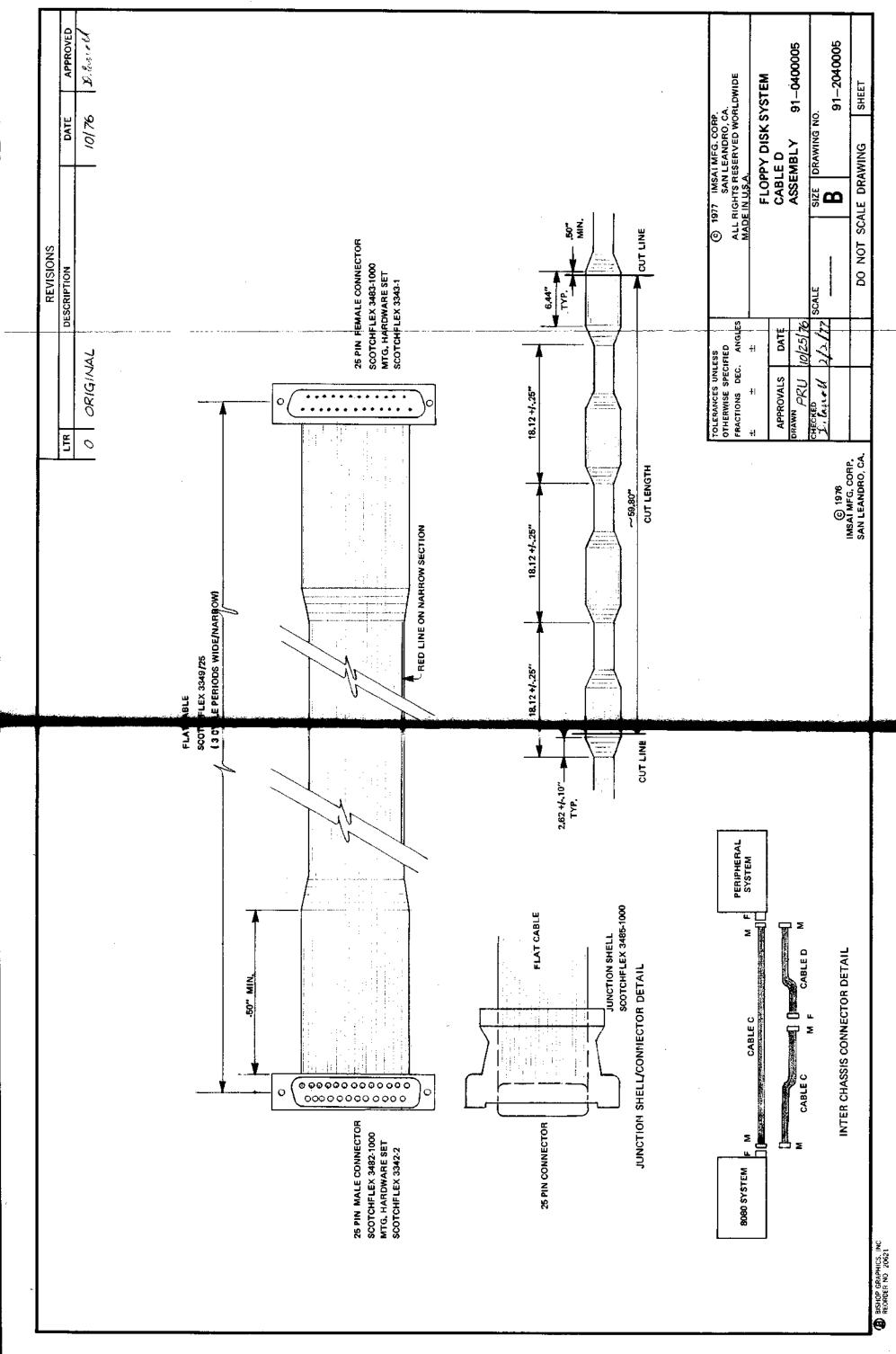

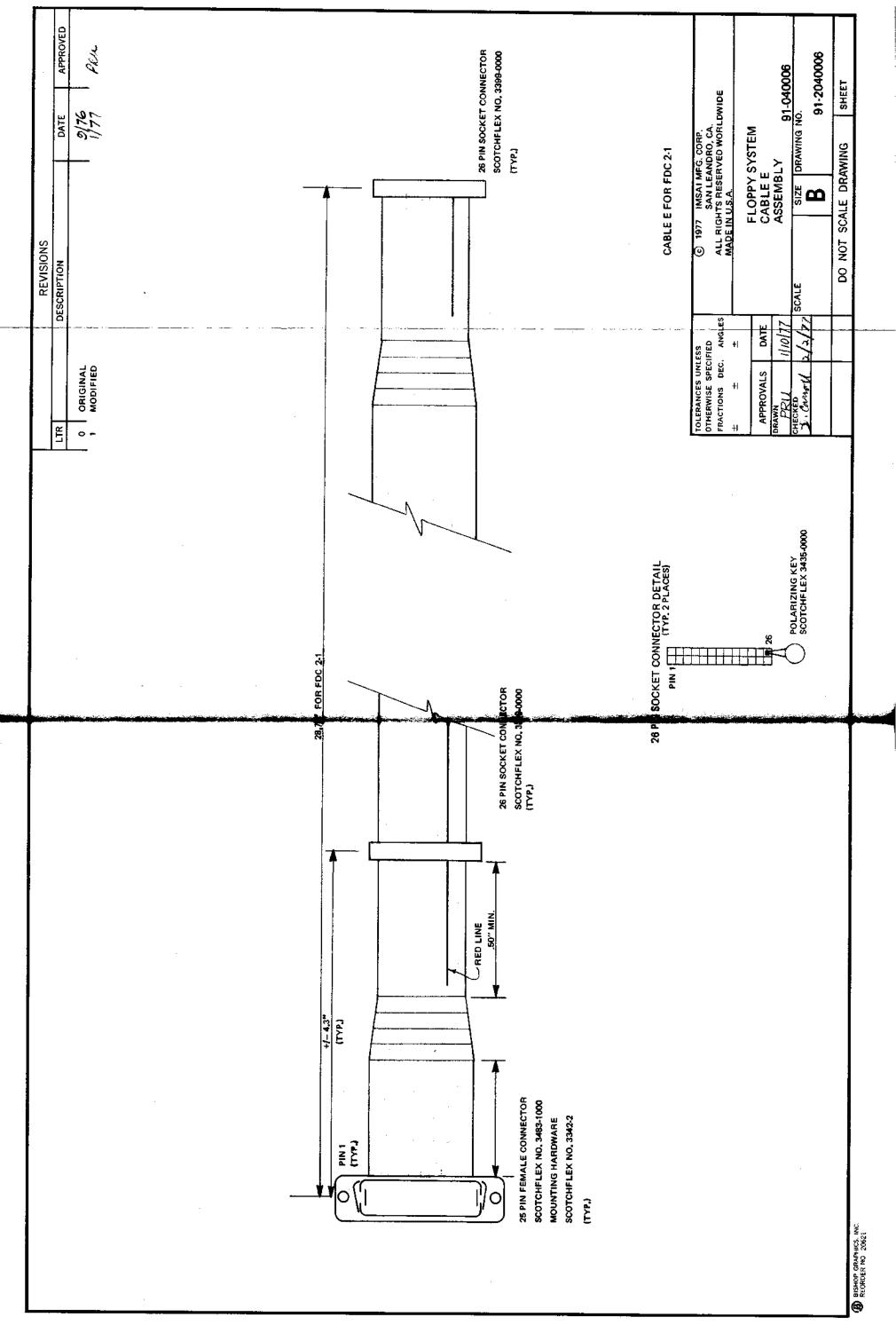

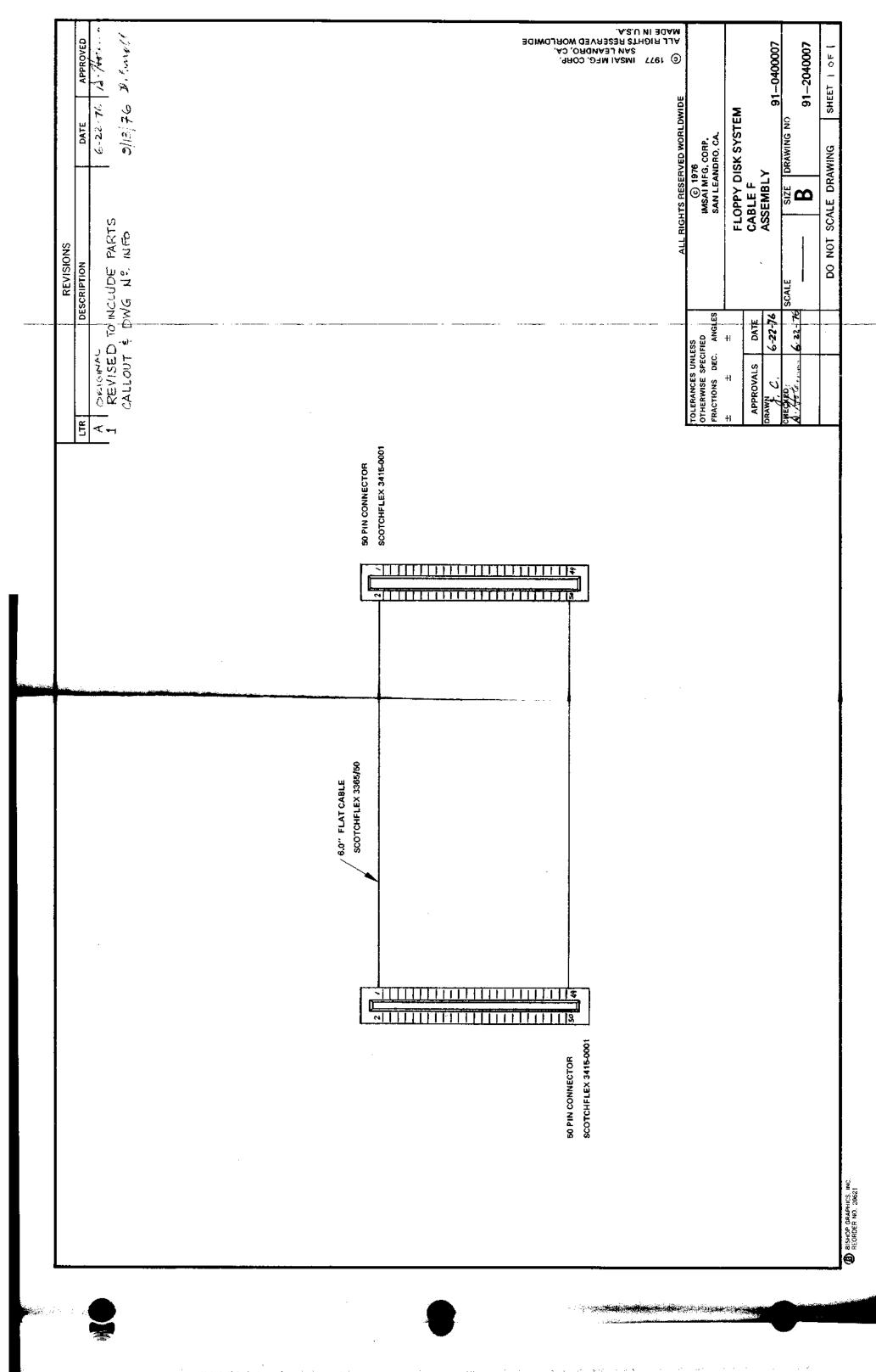

3. IDENTIFY THE THREE CABLES used in the System as follows:

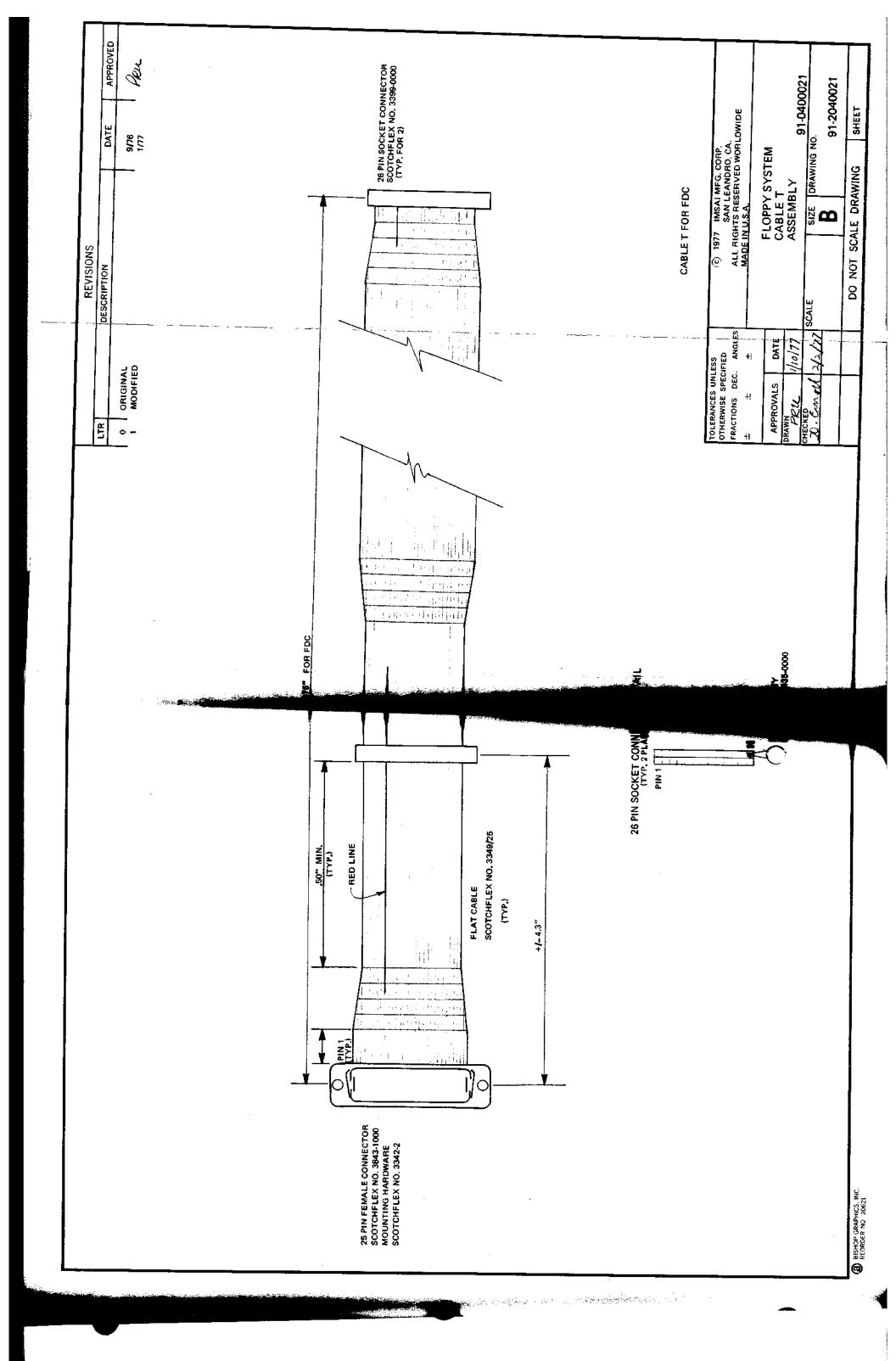

- CABLE A- CABLE A is a 12", 25 conductor cable with an EIA D Type connector on one end and a 26 pin board edge connector on the other end.

- CABLE C- CABLE C is a 3', 25 conductor cable with an EIA D Type connector on each end. NOTE: 3 and 4 Drive systems require 2-Cable C's.

CABLE F- CABLE F is a 4", 50 conductor cable with a 50 pin board edge connector on each end.

- 4. ATTACH CABLE F between the IFM and FIB Boards. When attaching Cable F, verify that pin 1 on each connector corresponds to pin 1 on the board edge connector.

- 5. MOUNT THE EIA D TYPE CONNECTOR of Cable A to the rear of the 8080 chassis with the hardware provided.

- 6. ATTACH THE REMAINING END OF CABLE A to the FIB Board. The 26 pin edge connector mates with the edge connector located in the upper left hand corner of the FIB Board. Verify that pin 1 of the connector mates with pin 1 of the board edge connector.

### FLOPPY DISK SYSTEM System Configuration

IMSAI FLOPPY DISK SYSTEM CONFIGURATION GUIDE-----

### SINGLE DRIVE SYSTEM

7. CONNECT CABLE C between the rear of the IMSAI 8080 chassis and the Floppy Drive Chassis as follows. Attach one end of Cable C to the D Type connector of Cable A. The remaining end will connect to the D Type connector located at the rear of the Floppy Chassis BEHIND DRIVE 0, (located on the right as you face the front of the Floppy Chassis).

### TWO DRIVE SYSTEM

7. CONNECT CABLE C between the rear of the IMSAI 8080 chassis and the Floppy Drive Chassis as follows. Attach one end of Cable C to the D Type connector of Cable A. The remaining end will connect to the D Type connector located at the rear of the Floppy Chassis BEHIND DRIVE 0, (located on the right as you face the front of the Floppy Chassis).

### THREE DRIVE SYSTEM

7. CONNECT ONE CABLE C between the rear of the IMSAI 8080 chassis and the Floppy Drive Chassis as follows: Attach one end of Cable C to the D Type connector of Cable A. The remaining end will connect to the D Type connector located at the rear of the Floppy Chassis, (containing Drives 0 and 1), BEHIND DRIVE 0, (located on the right as you face the front of the Floppy Chassis).

CONNECT THE SECOND CABLE C between the two Floppy Drive Chassis' as follows. Attach one end of Cable C to the D Type connector BEHIND DRIVE 1, (located on the left as you face the front of the Floppy Drive Chassis containing Drives 0 and 1). The remaining end of this Cable C will connect to the D Type connector BEHIND DRIVE 2, (located on the right as you face the Floppy Drive Chassis containing Drive 2).

FLOPPY DISK SYSTEM System Configuration

IMSAI FLOPPY DISK SYSTEM CONFIGURATION GUIDE-----

### FOUR DRIVE SYSTEM

7. CONNECT ONE CABLE C between the rear of the IMSAI 8080 chassis and the second Floppy Drive Chassis as follows. Attach one end of this Cable C to the D Type connector of Cable A. The remaining end will connect to the D Type connector located at the rear of the Floppy Chassis, (containing Drives 0 and 1), BEHIND DRIVE 0, (located on the right as you face the front of the Floppy Drive Chassis).

CONNECT THE SECOND CABLE C between the two Floppy Drive Chassis' as follows. Attach one end of this Cable C to the D Type connector located at the rear of the Floppy Chassis BEHIND DRIVE 2, (located on the right as you face the front of the Floppy Chassis containg Drives 2 and 3). The remaining end will connect to the D Type connector located at the rear of the Floppy Chassis BEHIND DRIVE 1, (located on the left as you face the front of the Floppy Chassis containing Drives 0 and 1).

THE IMSAI FLOPPY DISK SYSTEM IS NOW CONFIGURED AS REQUIRED FOR SYSTEM TESTING AND CP/M OPERATION.

### SYSTEM INITIALIZATION-----

The following procedure should be used when powering up the System.

- Insure that the diskettes are removed from the Drives.

- 2. Power up the 8080.

2. 27

- 3. Connect the power cord from the Drive Assembly.

- 4. Insert a diskette in the Drive.

- 5. The following events should be observed:

- a. When the drive becomes Ready, a faint, audible click should be heard as the drive is restored by the Firmware.

- b. Status Lights: TRACK 00 should be active; WRITE ENABLED should be active; HEAD LOADED should be inactive; WRITE should be inactive.

c. Ready and Select:

Both SELECT's should be active. The READY should be active for the drive being used.

27

IF THESE EVENTS ARE NOT OBSERVED, check the following points:

- a. Check all supply voltages on the IFM and FIB Boards.

- b. Check and verify all cable connections.

- c. Check and verify the EPROM located in

- position Al0 of the IFM Board (PROM00).

- d. Insure that an address jumper has been placed in socket C3 of the IFM Board.

- e. Check and verify that the IFM processor is in the RUN state (A1-3).

- f. If the problem still exists, use the firmware listing as a guide in troubleshooting the Scan Loop. The Scan Loop code begins at SCLP and is described in the FIB Firmware section under the heading STRAIGHT LINE DESCRIPTION OF THE PROGRAM.

### SYSTEM TESTING

### TEST MODULES

System testing described in this section consists of : 1) testing a single track format operation; 2) testing a sector write; 3) testing a sector read; and 4) testing the head positioning operation.

The test procedure is written so that the User must start with Test Module 1 to test single track format operations. Each succeeding module may be added to the existing code to test succeeding disk functions.

The complete test procedure requires 512 bytes of RAM beginning at address 1800H. The Command String resides at address 1880H, and the 128 byte buffer begins at 1800H.

If an error occurs when running the Test Modules, the Status Word in the Command String should indicate the type of error encountered. This information may be used to narrow down the possible sources of trouble given in the following section.

If the Status Word remains 0 when a failure occurs, the firmware has not completed, or perhaps even started, the operation. Check the DMA control circuits. Reference the IFM Theory of Operations.

### TEST MODULE 1

1. Set the address jumper at C3 on the IFM board for the address FD (Hex).

FIGURE 13, C3 Address Jumper (IFM)

2. Load the Test Module 1 beginning at 1889H.

- 3. RESET

- 4. EXAMINE 1889H.

- 5. Set the Drive Select Number in the Programmed Input Switches as follows:

01H to select Drive 0 02H to select Drive 1 04H to select Drive 2 08H to select Drive 3

- 6. Load the Diskette and close the door on the Drive. Wait for the Drive to come READY.

- 7. RUN.

When operating correctly, Track 0 is continuously formatted.

TEST MODULE 2

- 1. Load the Test Module 2 beginning at 18CDH.

- 2. Note that Test Module 1 MUST be loaded prior to using Test Module 2.

- 3. EXAMINE 1889H.

- 4. Set the Drive Select Number in the Programmed Input Switches.

- 5. Load the Diskette and wait for the Drive to come READY.

- 6. RUN.

Test Module 2 will Write from the buffer area at 1800H onto Track 0, Sector 1.

TEST MODULE 3

- 1. Load Test Module 3 beginning at 18E2H.

- 2. Test Modules 1 and 2 MUST be loaded prior to using Test Module 3.

3. EXAMINE 1889H.

- 4. Set the Drive Select Number in the Programmed Input Switches.

- 5. Load the Diskette and wait for the Drive to come READY.

- 6. RUN.

Test Module 3 will Read from Track 0, Sector 1 into the Buffer Area at 1800H.

TEST MODULE 4

- 1. Load Test Module 4 beginning at 18F0H.

- 2. Test Modules 1, 3 and 3 MUST be loaded prior to using Test Module 4.

- 3. EXAMINE 1889H.

- 4. Set the Drive Select Number in the Programmed Input Switches.

- 5. Load the Diskette and wait for the Drive to come READY.

- 6. RUN.

Test Module 4 will format Track 76 to test the head positioning routines.

### ERROR DEBUGGING

If an error occurs when running Test Module 1, the following points should be checked.

### GROUP 1

- Check FIF blue wire modifications (IFM Rev. 2 and 3, FIB Rev. 2 and 3).

- 2. Check and verify that the diskette is not damaged.

- 3. Check and verify the firmware in the IFM PROM.

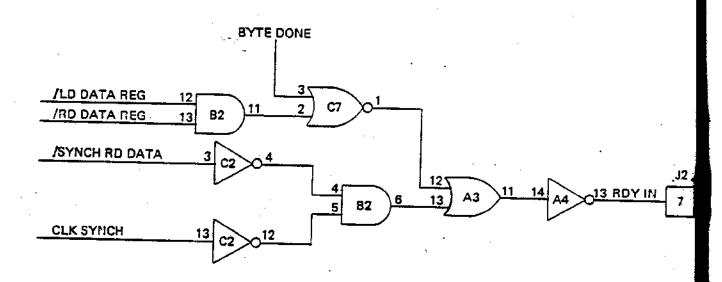

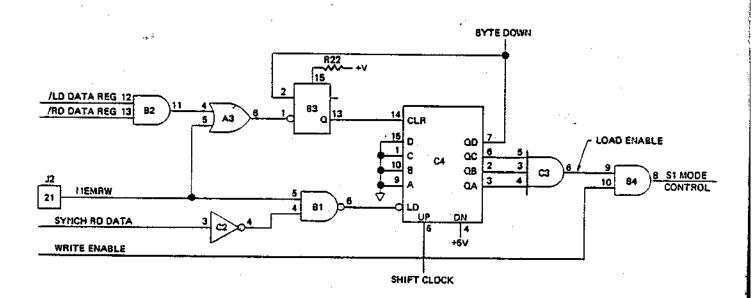

- 4. Check the OUTPUT COMMAND CONTROL CIRCUIT on the IFM board. Use the IFM Theory of Operation as a reference in troubleshooting.

- 5. If the Status Word in the Command String remains

0 when the failure occurs, or if the test program is lost/destroyed when running the test module, check the DMA CONTROL CIRCUIT. Use the IFM Theory of Operations as a reference in troubleshooting.

- Insure that the address jumpers have been correctly configured in position C3 of the IFM board.

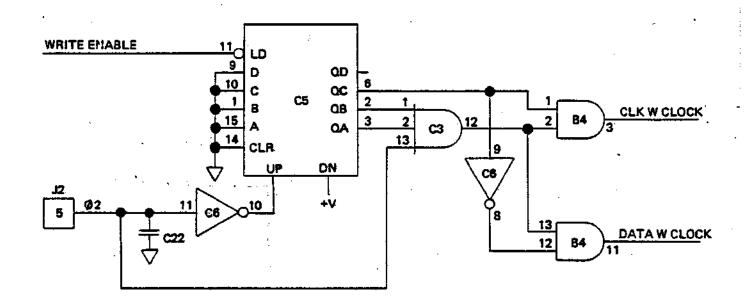

- Check the LOAD CONTROL CIRCUITS on the FIB Board. Reference the FIB Theory of Operations.

- 8. Check the INDEX MARK DETECTION CIRCUIT on the FIB board. Reference FIB Theory of Operations.

- 9. Check the IFM RAM CHIPS B9 and B12.

IF AN ERROR OCCURS with the addition of Test Module 2, check all items listed in GROUP 1 and the following.

### GROUP 2

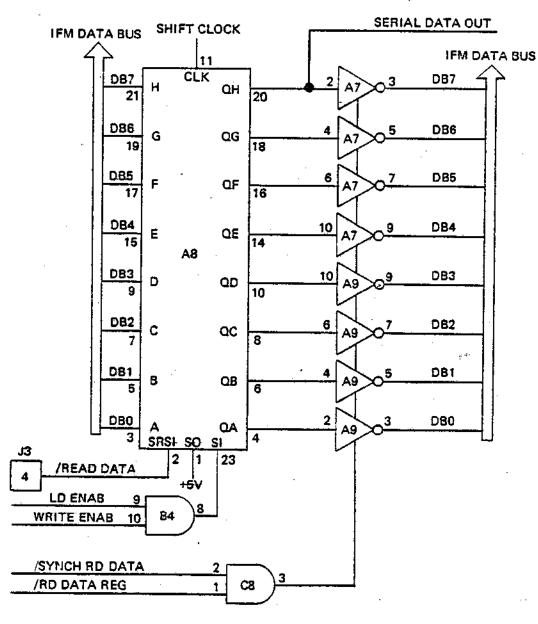

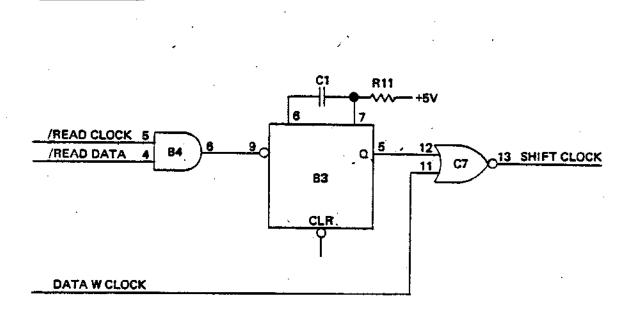

- Check the SYNCH READ DATA CIRCUIT on the FIB Board. Reference the FIB Theory of Operations.

- 2. Check the PLO operation and the PLO SYNCH circuit on the FIB Board.

IF AN ERROR OCCURS with the addition of Test Module 3, check all items in GROUPS 1, 2, and the following.

### GROUP 3

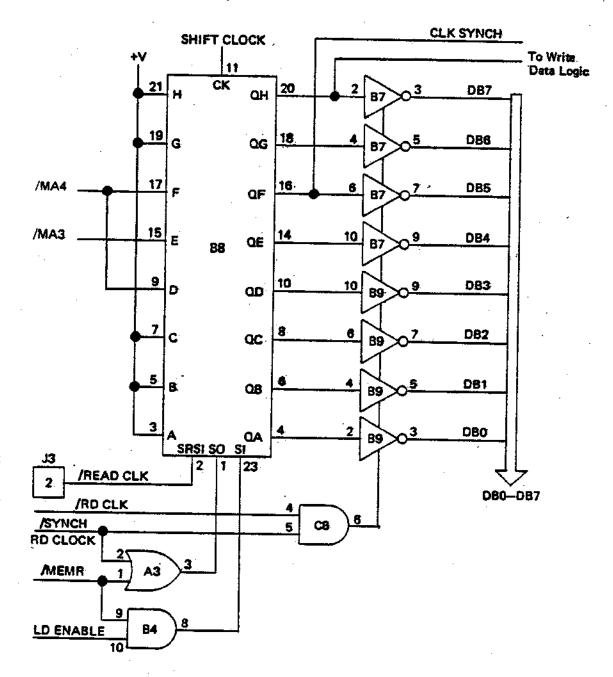

- 1. Check the READ DATA CIRCUIT on the FIB. Reference the FIB Theory of Operations.

- 2. Check the BYTE DONE CIRCUITS on the FIB. Reference the FIB Theory of Operations.

IF AN ERROR OCCURS with the addition of Test Module 4, check all items in GROUPS 1, 2, 3, and the following.

### GROUP 4

Check the Direction and Step Lines on the FIB Board. Refer to the CALCOMP OEM Manual for specs.

USE OF THE FIRMWARE LISTING IS RECOMMENDED AS A GUIDE IN TROUBLESHOOTING INDIVIDUAL DISK OPERATIONS. B: TMODI, PRN

;

PAGE 1

33

|                            | 7                                       | TEST MODULE 1                                                                |                |

|----------------------------|-----------------------------------------|------------------------------------------------------------------------------|----------------|

|                            | 3                                       | SETS UP THE COMMAND<br>STRING AND FORMATS                                    |                |

|                            | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | TRACK 3<br>VERSION 1.3 13/76                                                 |                |

|                            | ;<br>•                                  | •                                                                            |                |

| 1337                       | <b>9</b>                                | 026 13204                                                                    |                |

|                            | BUFA                                    | EQU S                                                                        |                |

| 1300                       | DOPA                                    | DS 128 ;BUFFER AREA                                                          |                |

|                            | IFMIO                                   | EQU JEDH ;IFM I/O PORT                                                       |                |

| 1880 =                     | CMD                                     | 20U \$                                                                       |                |

| 1880 '                     |                                         | DS 9 ;COMMAND STRING                                                         |                |

| 1869 039018                |                                         | JMP START ;START FROGRAM                                                     |                |

| 1380 97                    | ISSUE                                   | SJB A ;ZERO ACC                                                              |                |

| 1820 D370                  |                                         | OUT IFMIO : FXEC COMMAND                                                     |                |

| 1887 JA8118<br>1892 B7     | STLF                                    |                                                                              |                |

| 1892 fr<br>1893 GAEF18     |                                         | ORA A SET FLAGS                                                              | _              |

| 1896 F2                    |                                         | JZ STLP ;WAIT FOR STATUS<br>RP                                               | 2              |

| 1397 D3FF                  |                                         | OUT JFFE ;OUT ERROR STATU                                                    | t. <del></del> |

| 1399 033018                |                                         | JMP BEGIN                                                                    | 12.            |

| 1890 31F31B                |                                         | LXI 6,13739 ;SETUP STACK                                                     |                |

| 1897 97                    |                                         | SUB A ;ZERO ACC                                                              |                |

| 13AJ 328218                |                                         | SIA CMD+2 ;ZERO BYTE 3 OF                                                    | 25             |

| IBA3 212313                |                                         | - LXI H.BUFA :GET BUFFER ADDR                                                | {              |

| 18A6 228518                |                                         | SHER CMC45                                                                   | -              |

| 1849 JE13                  |                                         | MVI A,10H                                                                    |                |

| 16AB D3FD                  |                                         | OUT IFMIO ; PYTE CMD 1                                                       |                |

| 16AD 218318                |                                         | MVI A,12H<br>OUT IFNIO ;PYTE CMD 1<br>LXI H.CMD ;JET CMD SFR ADD<br>MOV A.L. | )R             |

| 1830 7D                    |                                         |                                                                              |                |

| 1381 D3FD<br>1833 70       |                                         | OUT IFMIO ;CUT LO CS ADDR                                                    |                |

| 1834 D3FD                  |                                         | MOV A,H ;<br>OUT IFMIO ;OUT HI CS ADDR                                       |                |

| 18FE DBFF                  |                                         |                                                                              |                |

| 1333 F620                  |                                         | IN OFFE ; INPUT DR. NO.<br>ORI 20H                                           |                |

| 18BA D3FD                  |                                         | OUT IFMIO ; OUTPUT RESTORE                                                   | สหภ            |

|                            | BEGIN                                   | IN OFFE JET DR. NO.                                                          | 901.5          |

| 183E F83 <i>J</i>          |                                         | ORI 3-JH ; IOR(1AT C(1D.                                                     |                |

| 1900 329013                |                                         | STA CMD ;STORE CMD NO.                                                       |                |

| 1803 97                    |                                         | SUB A ;ZERO ACC                                                              |                |

| 1304 328118                |                                         | STA CMD+1 ;ZERO STATUS                                                       |                |

| 1307 328313                |                                         | STA CMD+3 ;ZERO TRACK                                                        |                |

| 180A 008018<br>1802 038018 |                                         | CALL ISSUE ; ISSUE CMD                                                       |                |

| 7201 000019                |                                         | JMP BEGIN                                                                    |                |

B: CHODE.PRN

C

Ċ

Ċ

C

$\langle \hat{\ }$

$\mathbf{C}$

C

$\sum_{i=1}^{n}$

C ·

$\mathbf{C}$

Ċ.

(\_\_\_\_

$\bigcirc$

Ç,

Ċ

Ċ

Ċ

Ċ

C

Ċ

1 - 34

TEST MODULE 2

## WRITES TRACZ 2 VIRSION 1.2 13/78

| 180D<br>1880 =<br>1880 =<br>1800 =<br>1800 DSF<br>1800 F61<br>1804 S7<br>1805 328<br>1805 328<br>1805 328<br>1807 008 | 0<br>018<br>110<br>318 | EQU<br>EQU<br>EQU<br>IN<br>ORI<br>STA<br>STA<br>STA<br>STA<br>STA<br>STA<br>CALL |       | ; IN DR. NG.<br>; GR IN WRITE CMD<br>; STORT OML NO.<br>; ZERO ACC<br>; ZIRO STATUS<br>; ZERO TRACK<br>; SEGTOR 1<br>; IXLC OMD |

|-----------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------|

| 18DF CD8<br>1832 C33                                                                                                  |                        | JMP                                                                              | BEGIN | ,                                                                                                                               |

.

|                                                                                                                                       | - 7<br>- 7<br>- 7<br>- 7<br>- 7<br>- 7<br>- 7<br>- 7<br>- 7 | READS                                                       | MODULE<br>TRACK<br>ON 1.3                                                              | 3                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 1852<br>1882 =<br>1880 =<br>1880 =<br>1852 DBFF<br>1854 F622<br>1856 328318<br>1859 97<br>185A 328118 -<br>1852 CD8016<br>1853 C38016 | ;<br>ISSUE<br>BEGIN                                         | ORG<br>EQU<br>EQU<br>IN<br>CRI<br>STA<br>STA<br>CALL<br>JHP | 1822H<br>1880H<br>1880H<br>1880H<br>277H<br>20H<br>CML<br>A<br>CMD+1<br>15SUZ<br>BEGIN | ;GET DR. NO.<br>;CR IN RYAD CMD<br>;STORE CML NO.<br>;ZERO ACC<br>;ZERO STATUS<br>;YKEC CMD |

| B:TMOD4                                                                                                                                                                                                                                                                                                                    | .PRN                                   | •                                                                                                                                  |                                                                                                                                 | PAGE 1            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------|

| C<br>C<br>C<br>C<br>19F3<br>1963 =                                                                                                                                                                                                                                                                                         | ;<br>;<br>;<br>;<br>;                  | TEST MODULE 4<br>FORMATS TRACK<br>VERSION 1.2 1<br>ORG 18F24<br>EQU 18624                                                          | . 7ĉ                                                                                                                            | <u>م</u> بو کرد ت |

| 1930 =         1380 =         1873 37         1871 328         1374 338         1376 328         1876 328         1877 1876 328         1878 503         1879 187         1879 187         1879 187         1879 187         1879 187         1879 187         1879 187         1879 187         1870 288         1933 031 | 10<br>1318<br>7F<br>50<br>1318<br>3018 | EQU 188CH<br>EQU 188CH<br>SUB A<br>STA CMD+1<br>MVI A,4CH<br>STA CMD+3<br>IN ØFFH<br>ORI 32H<br>STA CMD<br>CALL ISSUE<br>JMP BEGIN | ZERO ACC<br>ZERO STATUS<br>TRACK 76<br>STORE TRACK IN CS<br>JET DRIVE NO.<br>JOR IN FORMAT NO.<br>STORE CMD NO.<br>FAEC CMD STR | · · ·             |

|                                                                                                                                                                                                                                                                                                                            | ·<br>·<br>·                            |                                                                                                                                    | ·                                                                                                                               | ·<br>·            |

I

C

C

Ç,

C

C

Ċ.

Ç

Ć

**1** – 36

. ·

### FLOPPY DISK SYSTEM System Testing

AND NOW------

Once your System has passed the System Testing previously described, you may proceed in one of several ways.

- If you wish to bring up IMSAL CP/M, refer to the IMSAL CP/M USER MANUAL for further instructions.

- If you wish to write your own disk access programs, refer to the Programming Guide in the System User Guide section of this manual. In writing your own disk access programs, it is adviseable to read the System Theory of Operation to gain a general understanding of the System operation.

- If you wish to understand the operation of the System, the following sections of this manual may prove helpful.

System Theory of Operation IFM Theory of Operation FIB Theory of Operation FIB Firmware Theory of Operation Cal Comp OEM Reference Manual for the Model 140 Drive.

# SYSTEM USER GUIDE

Copyright 1977 IMSAI Manufacturing Corporation 14860 Wicks Boulevard San Leandro, California 94577

1 - 41

## CAUTION

Take Diskettes out of the drives during system power up or down to prevent any possible changing of data.

9/9/76

#### USER GUIDE-----

#### USER CONTROLS

POWER SWITCH: The AC power switch is located at the rear of each FPS. Assembled Drives are shipped with this switch in the power-on position.

LOADING AND REMOVING DISKETTES: In the center of the face of each Drive is a simple, thumb operated pushbutton which is depressed to allow the springloaded front cover to open. The Flexible Disk may then be inserted or removed as appropriate. The cover may then be closed manually.

NOTE: Remove the Diskette from the drive before power is applied to or removed from the Controller Boards.

LIGHT DISPLAY: The Light Display monitors the READY and SELECT Lines for each Drive in the cabinet. The states of the four signal lines TRACK00, HEAD LD, WRITE, and WRITE ENABLED are monitored for the selected Drive.

SELECT: A SELECT line will become active when the Controller raises the Select Line for the appropriate Drive. Both Select Lines will appear to be continuously active since the Controller uses these lines in a polling process to determine if a Drive has become Ready.

**<u>READY</u>:** This will become active when a diskette is loaded and the cover is closed on a selected Drive.

TRACK 00: The TRACK 00 line will become active when the Read/Write head on the selected drive is positioned over Track 00.

HEAD LOAD: The HEAD LOAD line will become active when the Controller issues a request to the selected Drive to load the Read/Write head.

$\frac{\text{WRITE:}}{\text{the WRITE line will become active when the Controller issues a command to the selected drive to enable the Write line.}$

WRITE ENABLED: The WRITE ENABLED line will become active when the selected Drive acknowledges that the loaded diskette is not write protected. Circuitry in the Drive to support this feature is not standard.

#### SYSTEM INITIALIZATION

The following procedure should be used when powering up the System.

- 1. Insure that the diskettes are removed from the Drives.

- 2. Power up the 8080.

- 3. Connect the power cord from the Drive Assembly.

- 4. Insert a diskette in the Drive.

- 5. The following events should be observed:

- a. When the Drive becomes Ready, a faint, audible click should be heard as the drive is restored by the Firmware.

- b. Status Lights: TRACK 00 should be active; WRITE ENABLED should be active; HEAD LOADED should be inactive; WRITE should be inactive.

- c. Ready and Select: Both SELECT's should be active. The READY should be active for the drive being used.

45

# SYSTEM BOOTSTRAP (IFM REV 3 FIRMWARE ONLY)

A "bootstrap" is a short program which reads another program from some storage medium into system RAM and executes it. This simple, yet general procedure gives the user freedom to load in any kind of operating system s/he desires. The IMSAI Floppy Disk System bootstrap reads sector 1 of track  $\emptyset$  from drive  $\emptyset$  into system RAM at  $\emptyset$ -7F and then jumps to location  $\emptyset$ .

The following procedure should be used when bootstrapping from an IMSAI CP/M System Diskette.

- 1. Insure that the diskettes are removed from the drives.

- 2. Power up the 8080.

- 3. Power up the floppy disk drive.

- 4. Insert a system diskette in drive  $\emptyset$ .

- 5. When the drive becomes READY, press RESET.

- Set the ADDRESS switches for ØØØØ and press EXAMINE. A "C3" should appear in the DATA lights.

7. Press RUN.

At this point, the operating system should be loaded and run.

If a hardware error occurs, the error code (see FIB Software section) will be displayed in the PROGRAMMED OUTPUT lights. The bootstrap will be retried until it is successful, or until it is stopped. If unable to bootstrap, check the points described at the end of the SYSTEM INITIALIZATION section.

If REV 3 Firmware is not available, a Bootstrap Simulator is described in the IMSAI CP/M Documentation.

#### PROGRAMMING GUIDE

#### A. Introduction

An Assembly Language Program stored in the 8080 System Memory is necessary to access the Floppy Disk. To use the IMSAI Floppy Disk System, the User must understand how to write such a program.

In order to accomplish this, the User may think of the Floppy Disk as a SINGLE OUTPUT PORT from the 8080 Microprocessor System.

The program which will access the Floppy Disk System utilizes TWO TYPES OF INSTRUCTIONS:

1. BYTE INSTRUCTIONS and

2. A COMMAND STRING INSTRUCTION.

BYTE INSTRUCTIONS are OUTPUT INSTRUCTIONS to the output port of the Floppy Disk System.

A COMMAND STRING is a series of consecutive words located in the System Memory.

The processes which need to take place within this program are described as follows.

START....SET UP THE COMMAND STRING IN RAM FOR A PARTICULAR DISK OPERATION

> ISSUE THE BYTE COMMAND (OUTPUT INSTRUC-TION) TO INITIATE THE EXECUTION OF A DISK OPERATION

CHECK THE STATUS WORD IN THE COMMAND STRING FOR AN INDICATION THAT THE DISK OPERATION IS COMPLETE

END.....

The sections of the USER GUIDE which follow give the detailed information necessary to WRITE THE FLOPPY DISK ACCESS PROGRAM.

#### B. Command Types

Control of the IMSAI Floppy Disk System from the 8080 Microcomputer System is of two types: 1) the BYTE COMMAND and 2) the COMMAND STRING.

BYTE COMMAND instructions are directly executable and are passed to the IFM board from the Main Processor via an OUTPUT instruction.

COMMAND STRING instructions are indirectly executable and are stored in variable length COMMAND STRINGS in the Main System RAM.

A COMMAND STRING instruction is executed when a BYTE COMMAND of 0 is output to the IFM board. At that time the IFM processor will get the COMMAND STRING from the Main Processor's memory via the DMA channel and execute the instruction contained therein.

يحردرني

FIGURE 8, Control in the IMSAI FDS

User Guide

C. BYTE COMMANDS

1 - 48

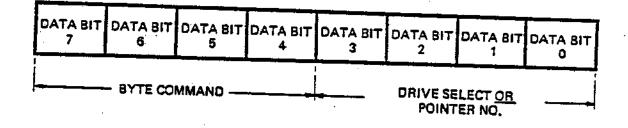

The Byte instruction is an eight bit word structured so that the upper four bits contain the BYTE INSTRUCTION NUMBER and the lower four bits contain either a pointer number or a drive select number, depending on the command used. (See figure 9.)

# FIGURE 9, Byte Command

The Byte Instructions are listed below according to the Byte Instruction Number (the hex number contained in the upper four bits of the Byte Instruction).

<u>COMMAND 0</u>: Execute Command String from pointer. This command will take the pointer number from 0 to 15 and execute the Command String pointed to by that pointer. Note that prior to using this command the pointer address must have been initialized using Command 1.

<u>COMMAND 1</u>: This command will cause the floppy controller to take the next two bytes passed to it by the master microprocessor and use these as the new address for the pointer specified. Note that three bytes must be output to the IFM I/O port from the main processor to properly execute this command. (BYTE COMMAND NUMBER, LOW ORDER ADDRESS, HIGH OR-DER ADDRESS)

- <u>COMMAND 2</u>: Restore Drive causes the floppy controller to execute a restore command (position the head over track 0) on any or all drives selected.

- <u>COMMAND 3</u>: Set Software Write Protect causes the controller to set a Write Protect on any of the drives which are selected. Note that in a power on condition, all drives come up WRITE ENABLED and therefore the WRITE PROTECT must be reset whenever power goes on.

- <u>COMMAND 4</u>: Software WRITE ENABLE causes the microprocessor or the floppy controller to remove the WRITE PROTECT on any or all drives selected.

- <u>COMMAND 5</u> through <u>COMMAND 15</u> perform no operation, except to reset interrupt if interrupt mode is being used. IMSAI standard RESET INTERRUPT command is command 5.

#### POINTERS

The pointer is a number from 0 to 15 which signifies that one of 16 addresses be used as the address of the Command String in Main Memory. Byte Commands 0 and 1 will take the lower four bits of the Byte Instruction Word as a pointer number to a Command String address. Note that Byte Command 1 is used to initialize the addresses of the pointers, while Byte Command 0 will execute the Command String pointed to by the lower four bits of the Byte Command Word.

On system power-up or RESET, the sixteen pointers are initialized with the following default values (all in hexadecimal).

| Ø: | øø8ø | 4: | 4ØØØ | 8: | 8øøø | C: | сøøø |

|----|------|----|------|----|------|----|------|

| •  | løøø |    | 5000 | 9: | 9øøø | D: | døøø |

|    | 2000 |    | 6øøø | A: | AØØØ | Е: | eøøø |

|    | зøøø |    | 7øøø | B: | вøøø | F: | føø  |

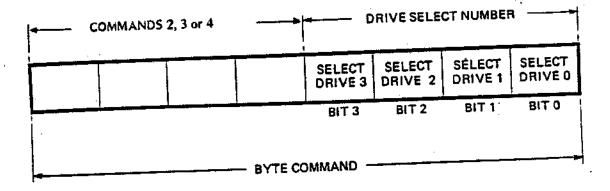

#### DRIVE SELECT NUMBERS

Byte Commands 2, 3 and 4 will take the lower four bits of the Byte Instruction Word as a Drive Select number. A drive is selected (0-3) if its corresponding bit is a 1. A command with no drives selected does no operation.

49

FIGURE 10, Drive Select Numbers

# D. COMMAND STRING INSTRUCTIONS

Command String Instructions are indirectly executable and are stored in a variable length Command String in the Main System RAM.

The Command String is a series of from 4 to 9 consecutive 8 bit bytes in the main processor's memory. Its length or structure is dependant on the command used.

| SYSTEM R   | AM     |        |        |               |        |        |

|------------|--------|--------|--------|---------------|--------|--------|

| <b>∤</b> ∙ | REQU   | IRED   |        | ۱ <del></del> |        |        |

| WORD 1     | WORD 2 | WORD 3 | WORD 4 | WORD 5        | ][     | WORD 9 |

| L          | ·····  |        |        | AS            | PTIONA |        |

|            | _      |        |        |               |        | ~~~~   |

# FIGURE 11, Command String Instructions

All Command Strings consist of at least four bytes of information. The definition of each 8 bit byte in the Command String is given below.

BYTE 1 - Command Byte

This byte contains a command number in the upper hexadecimal digit and the drive select number in the lower digit. The operation for each Command Number is defined in the next section and a drive is selected (0-3) if its corresponding bit is a one (bits 0-3).

#### BYTE 2 - Status Byte

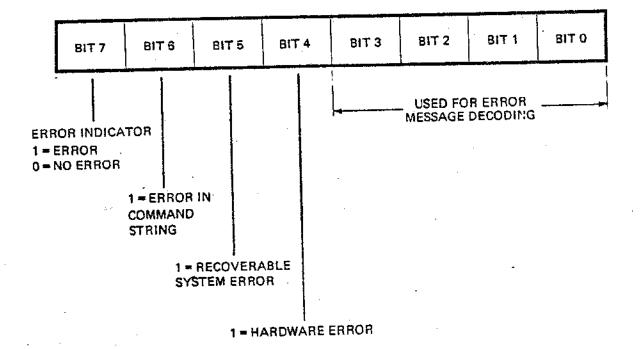

This byte indicates to the master microprocessor the status of the present disk operation. It must be SET EQUAL TO 0 prior to executing the single Byte Command 0. This byte is set non-zero at the completion of the Command String by the IFM processor. If bit 7 is set, it indicates that the operation was not completed successfully. Bit 0 only is set on successful completion.

#### BYTE 3 and 4 - Track Address

Two Bytes are allowed for the track address for future expansion. At this time, Byte 3 must be 0, and Byte 4 contains a value from 0 - 76 to specify on what track the operation should be performed. Note that to maintain IBM media compatibility, it is possible to have the logical and physical track address differ. For commands to process this type of data, Bytes 3 - 4 contain the physical track address number.

Care must be exercised in operating with the logical and physical track address being different, and the user must be totally familiar with the format s/he is working with to perform any operation of this nature. For commands which specify no further track address, these two bytes contain both the physical and logical track address numbers.

#### BYTE 5 to 9

Bytes 5 to 9 of the Command String are defined according to the Command used.

#### COMMAND TYPES

The individual Command String commands are listed below by the command numbers - the upper four bits of the Command Byte.

COMMAND 0

The <u>READ ALL</u> command causes the IFM to delay the number of milliseconds contained in Byte position 5 from the physical index poles of the floppy disk and then to read 64 bytes. For each data byte, the corresponding clock byte is also read and is stored in the next sequential location in memory (i.e., stored are data from byte 1, clock from byte 1, data from byte 2, clock from byte 2, etc.). Hence, 128 bytes are transferred to the main processors memory at the data buffer location pointed to in Bytes 6 and 7. The delay in Byte 5 can be from 0 to 255 ms.

Note that the 64 bytes on the floppy disks consume approximately 2 ms and that software recognition for repositioning of the data is required to completely reconstruct the data pattern which is on the floppy disk. This command should be used with caution, and the user should be totally familiar with format contained on the floppy disk s/he is referencing before attempting to use the command. It is normally used only in cases of extreme difficulty or to decipher an unknown diskette format.

#### COMMAND 1

The <u>WRITE SECTOR</u> command causes the floppy controller to write the data from the location pointed to by Bytes 6 and 7. Byte 6 contains the least significant half of the data buffer location, and Byte 7 contains the most significant half. The data is written in the sector specified in Byte 5 (from 1 to 26).

#### COMMAND 2

READ SECTOR: The sector number contained in Byte 5 (from 1 to 26) is read and, upon successful completion of the read, the data is transferred to the data buffer location contained in Bytes 6 and 7. Byte 6 contains the least significant half of the data buffer location, and Byte 7 contains the the most significant half.

#### COMMAND 3

The FORMAT TRACK command uses no additional bytes and causes the floppy controller to write an IBM compatible format on the selected track number. This command destroys all previous information on the track and should be used with caution to initialize new diskettes.

#### COMMAND 4

The VERIFY SECTOR command causes the floppy controller to read and verify the redundancy check on the selected sector. NO DATA TRANSFER to the main processor's memory is initiated. Byte 5 for this command contains the sector number (from 1 to 26) which is to be verified.

#### COMMAND 5

The WRITE DELETED DATA SECTOR MARK command causes the floppy controller to write a deleted data mark in the data portion of the sector number contained in Byte 5. This command is used to indicate a defective sector, and the user should be completely familiar with the IBM format prior to initiating this command.

#### COMMAND 7 through 11

Commands 7 through 11 are identical with commands 1 through 5 and are used to read diskettes which have the logical and physical track address physically different. The logical track address to be used is always contained in the two bytes directly following the other command data called for in the COMMAND STRING (0-5). For example, if the basic command uses just 4 bytes, then the logical track number would be in bytes 5 and 6. If the basic command used 7 bytes, then the logical track address number would be in bytes 8 and 9.

The command will cause the controller to reference the physical track called out in bytes 3 and 4. But to compare the track address received off this physical track or to write the track address onto this physical track, it will use the logical track number contained in the appropriate bytes.

Note that up to 16 Command String Pointers may coexist in IFM memory at any one time. When a BYTE INSTRUCTION 0 is output to the IFM processor, the upper 4 bits of the BYTE INSTRUCTION will be the BYTE COMMAND NUMBER (in this case 0). The lower

53.

4 bits will be the pointer number. The Command String to be taken from main memory and executed begins at the address contained in the specified pointer.

E. USE OF THE COMMAND STRING INSTRUCTIONS

Use of the Command String Instructions is detailed in the following discussion.

1. SET UP A POINTER TO A COMMAND STRING

By using Byte Command 1, the processor may set the value of a pointer. The processor will output a 1X to the IFM board where X is a pointer number (0-15). Following this will be an output of LL and then an HH where LL is the low order 8 bits and HH is the high order 8 bits of the address.

Once this is accomplished, the Command String beginning at address HHLL may be referred to by the pointer number X.

2. SET UP THE COMMAND STRING WITH ALL REQUIRED INFORMATION

- a) Load the Command Number and Drive Select Number in BYTE 1.

- b) Load a zero in the Status Byte (BYTE 2).

- c) Load a zero in BYTE 3.

- d) Load the track number in BYTE 4.

- e) Load BYTES 5-9 as required by the operation being performed.

- 3. ISSUE A BYTE COMMAND 0 TO INITIATE THE EXECUTION OF A COMMAND STRING

The processor will output a 0X to the IFM board where X is a pointer number causing the Command String pointed to by X to be executed.

4. WAIT FOR THE COMPLETION FO THE OPERATION