#### Table of Contents MULTIPLIERS/DIVIDERS

| Contents for Section 10 10-2                          |  |

|-------------------------------------------------------|--|

| Multiplier/Divider Selection Guide 10-2               |  |

| "Five New Ways to Go Forth and Multiply 10-3          |  |

| SN54/74S508 8x8 Multiplier/Divider 10-8               |  |

| SN74S516 16x16 Multiplier/Divider 10-21               |  |

| SN54/74S556 Flow-Thru™ Multiplier Slice 10-37         |  |

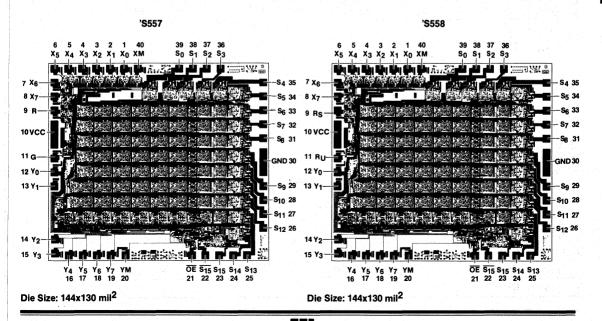

| SN54/74S557 8x8 High Speed Schottky Multipliers 10-50 |  |

| SN54/74S558 8x8 High Speed Schottky Multipliers 10-50 |  |

| Die Configuration                                     |  |

|                                                       |  |

# Multiplier/Divider Selection Guide

# **Co-Processor Multiplier/Divider with Accumulator**

|         | PART NUMBER          | MAX MULTIPLICATION TIME/<br>MAX DIVISION TIME | PINS |

|---------|----------------------|-----------------------------------------------|------|

| 8 Bits  | SN74S508<br>SN54S508 | 0.8 μs/2.2 μs                                 | 24   |

| 16 Bits | SN74S516             | 1.5 μs/3.5 μs                                 | 24   |

# **Cray Multipliers**

| DESCRIPTION              | PART NUMBER | MAX DELAY                                                     | PINS |

|--------------------------|-------------|---------------------------------------------------------------|------|

| 8x8 Multiplier (latched) | SN74S557    | 60 ns (X <sub>i</sub> , Y <sub>i</sub> , to S <sub>15</sub> ) | 40   |

| 8x8 Multiplier (latched) | SN54S557    | 60 ns                                                         | 40   |

| 8x8 Multiplier (latched) | SN74S558    | 60 ns                                                         | 40   |

| 8x8 Multiplier (latched) | SN54S557    | 60 ns                                                         | 40   |

| 16x16 Multipliers        | SN74S556    | 90 ns                                                         | 84   |

# **Five New Ways to Go Forth and Multiply**

## **Our Multiplier Population Explosion**

Recently it has seemed as if every time you turned around Monolithic Memories was announcing *another* new multiplier. Want to catch your breath, and find out where each of these fits into the overall scheme of things? Read on.

Actually, there have been five new multipliers in all within the last three years, plus two which had previously been available for several years. In time order of introduction, these are:

| Parts No.     | Description <sup>A</sup>                                                                |

|---------------|-----------------------------------------------------------------------------------------|

| 57/67558      | 150-nsec 8x8 Flow-Through Cray Multiplier <sup>B</sup>                                  |

| 57/67558-1    | 125-nsec 8x8 Flow-Through Cray Multiplier <sup>B</sup>                                  |

| 54/74S508     | 8-Bit Bus-Oriented Sequential Multiplier/<br>Divider                                    |

| 54/74S558     | 60-nsec 8x8 Flow-Through Cray Multiplier                                                |

| 54/74S557     | 60-nsec 8x8 Flow-Through Cray Multiplier with<br>Transparent Output Latches             |

| 54/74S516     | 16-Bit Bus-Oriented Sequential Multiplier/<br>Divider                                   |

| 54/74S556     | 90-nsec 16x16 Flow-Through Cray Multiplier<br>with Transparent Input and Output Latches |

| NOTES: A. Tim | es are worst-case times for commercial-temperature-range                                |

parts.

B. Obsolete. 54/74S558 replaces these in both new and existing designs.

You will notice that the above parts fall into two categories: flow-through Cray multipliers, and bus-oriented sequential multiplier/dividers. Although all of these parts get referred to rather casually as "multipliers," there are major differences between the two general types; see Table 1 below.

## **The Cray Multipliers**

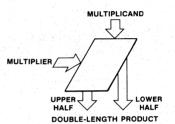

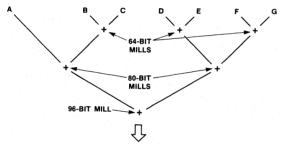

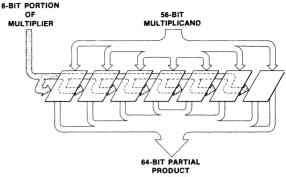

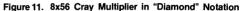

The essential idea of a Cray multiplier, as originally put together by Seymour Cray in the late 1950s with discrete logic at Control Data Corporation, is to wire up an array of full adders in the form of a binary-arithmetic-multiplication pencil-and-paper example.<sup>3</sup> That is, everywhere that there is a "1" or a "0" in a longhand binary-multiplication example, the Cray type of multiplication uses a full adder. One may visualize a Cray multiplier functionally as a "diamond," as follows:

Figure 1. Pencil-and-Paper Analogy to Cray-Multiplier Operation

|                         | Flow-Through Cray Multiplier                                                                                                                                          | <b>Bus-Oriented Sequential Multiplier/Divider</b>                                                                                                                                         |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Role in<br>System       | Building-block role — as many as 34 parts used in one super-<br>minicomputer (NORD-500 from Norsk Data').                                                             | Co-processor role — one, or occasionally two, parts used in one microcomputer <sup>2</sup> .                                                                                              |

| Internal<br>Operation   | Static arithmetic-logic network; multiplies without being clocked? using eight bits of the multiplier at a time.                                                      | State machine; requires clocking to operate; contains edge-<br>triggered registers; sequenced by a state counter; multiplies<br>using two bits of the multiplier at a time <sup>4</sup> . |

| External<br>Control     | Controlled by several mode-control input signals.                                                                                                                     | Controlled by sequences of micro-opcodes which come from<br>a microprocessor, a registered PAL, or some other sequential-<br>control device.                                              |

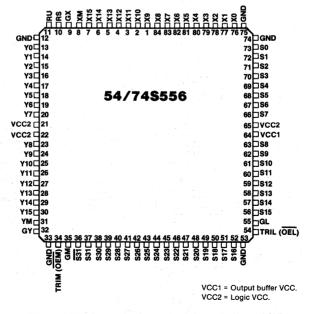

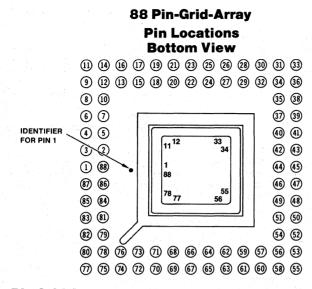

| Package                 | 40-pin DIP ('S557/8); 84-pin LCC or 88-pin PGA ('S556)                                                                                                                | 24-pin DIP.                                                                                                                                                                               |

| Operations<br>Performed | Can only perform multiplication.                                                                                                                                      | Can perform multiplication, division, and multiplication-with-<br>accumulation.                                                                                                           |

| Storage<br>Capabilities | Either no storage capabilities ('558 types), or optional storage<br>for the double-length product only ('557 type), or full<br>product and input storage ('556 type). | Four full-length registers; capable of storing both input oper-<br>ands and the double-length product.                                                                                    |

| Second<br>Sources       | 8x8, Multiple-sourced (AMD, Fairchild, Monolithic Memories).                                                                                                          | Sole-sourced; only bipolar dividers on the market.                                                                                                                                        |

| Where<br>Used           | Initial usage has been in high-end minicomputers, array pro-<br>cessors, and signal processors.                                                                       | Initial usage has been in industrial-control microcomputers,<br>digital modems, military avionics, CRT graphic systems, video<br>games, and cartographic analysis systems.                |

| Future<br>Prospects     | Potential large market today since these parts are now low-<br>cost and multiple-sourced, and should be used in all new mini-<br>computer designs!                    | Potential huge world-wide market for enhancement of micro-<br>processor, bit-slice processor, and microcomputer capabilities<br>and for small-scale signal processing!                    |

Table 1. A comparison of the two types of Monolithic Memories Multipliers

10

10-3

Our 57/67558, introduced in the mid-1970s, was the original *single-chip* Cray multiplier. To achieve what was for that time very high performance for a Schottky-TTL-technology part, the internal design of the 57/67558 also exploited other speed-freak multiplication techniques such as Booth multiplication<sup>4</sup> and Wallace-Tree addition<sup>5</sup>. All of these techniques achieve increased speed through extensive parallelism, and can be used at the system level as well as within LSI components. Subsequently, process improvements made it possible to offer a faster final-test option, the 57/67550-1, which attained a sales-volume level essentially equal to that of the original part.

About five years ago, AMD paid us the sincere compliment of second-sourcing these parts with the 75-nsec 25S558. Three years ago, we returned the compliment with the 60-nsec 54/74S558. All of these '558 parts, and the 70-nsec 54/74F558 announced by Fairchild, are fully compatible drop-in equivalents except for the variations in logic delay.

"ALL OF THESE TECHNIQUES ACHIEVE INCREASED SPEED THROUGH EXTENSIVE PARELLELISM."

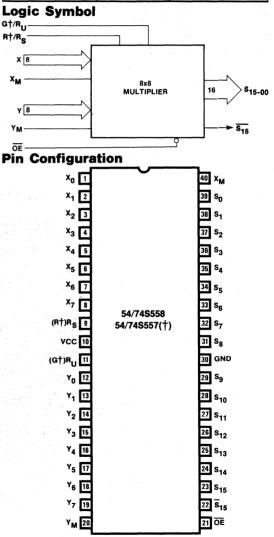

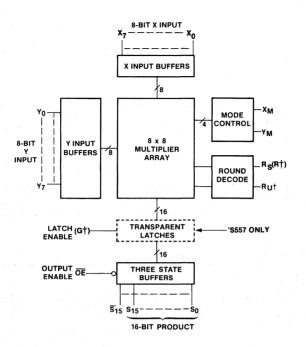

When AMD introduced the 25S558, they introduced along with it the 80-nsec 25S557, a "metal option" of the same basic design with "transparent" output latches to hold the double-length product. "Transparent" means that the latches go away when you don't want them there; a latch-control line like that of the 54/74S373 controls whether these output latches store information, or simply behave as output buffers. Anyway, when we introduced our 54/74S558, we followed it within a few weeks with the 60-nsec 54/74S557, which is a much faster drop-in replacement for AMD's part. And subsequently, Fairchild has announced a 70-nsec 54/74F557.

Because AMD's 'S557 has the output latches implemented in TTL technology *after* the ECL-to-TTL converters, whereas our 'S557 has them implemented in ECL technology *before* the conversion, the latches operate much faster in ours. Our 'S557 is typically only about a nanosecond slower than our 'S558, whereas the logic-delay difference between AMD's two parts is considerably greater. Consequently, our margin of superiority over AMD for the 'S557 is even greater than for the 'S558.

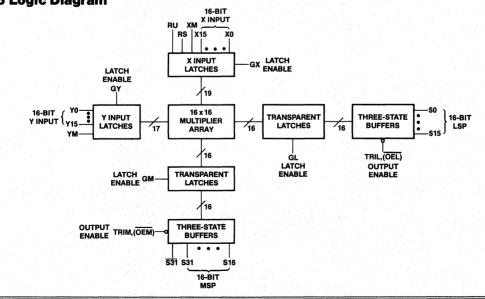

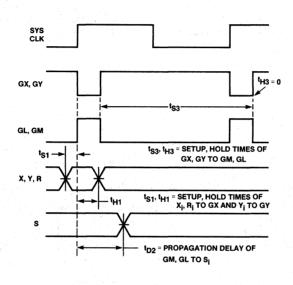

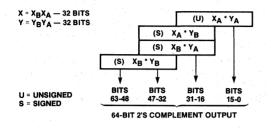

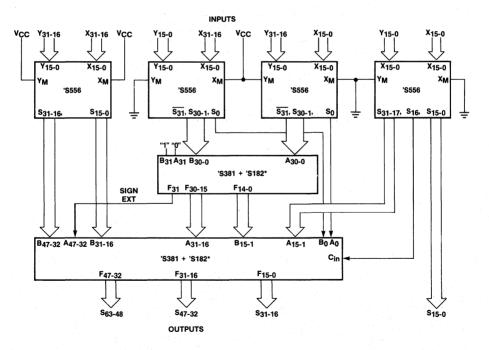

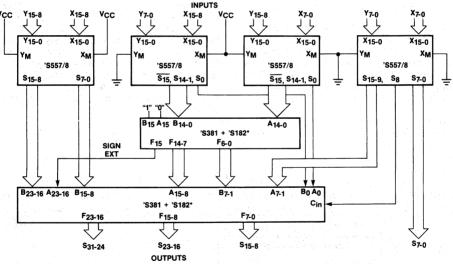

More recently, we introduced the 90-nsec 'S556, which is a 16x16 direct size-upgrade of the 'S557/8 architecture, with the addition of input latches. In a "pipelined" mode, an 'S556 can produce a new 32-bit product every 75 nsec.

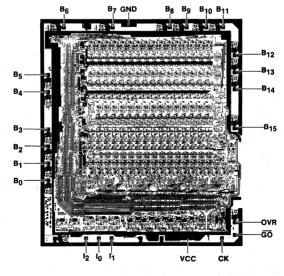

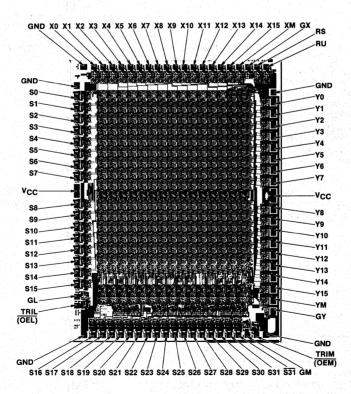

'S557/8 Cray multipliers come in a 40-pin dual-inline package, either ceramic or plastic. Worst-case power-supply current is 280 mA. The 'S556 comes in your choice of an 84-pin LCC (Leadless Chip Carrier) or an 88-pin PGA (Pin-Grid Array) package. Worst-case power-supply current is 800 mA (900 mA over military temperature range). The data-bus outputs can sink up to 8 mA IOL, for all of these multipliers.

Monolithic

References 5 and 6 discuss technical approaches to using Cray multipliers in high-performance minicomputers. The 'S558, together with PROMs organized in a 'Wallace-tree' configuration, can sail right along at the rate of four 56x56 multiplications every microsecond, on the basis of fixed-point arithmetic with no renormalization. (See table 7 on page 16 of reference 5; the multiplication time is 238 nsec for a 'division step,' which is a fixed-point multiplication, and 319 nsec for a floating-point multiplication where extra time is required for renormalization and correction of the exponent of the product.) 34 'S558s or 'S557s are required to perform this multiplication if the computer system architecture does not call for the computation of the least-significant half of the double-length product; 49 are required if it does.

The "local" architecture of the multiplier section of a digital system can take two rather different forms. A minicomputer, which executes an unpredictable mixture of arithmetic and logical instructions one after the other, typically needs to be able to get the complete multiplication over and done with before going on to the next program step—which is probably not another multiplication. An array processor or digital correlator, however, tends to do very regular iterative computations; and the performance of such a system can often be greatly increased by a technique called "pipelining," in which the arithmetic unit consists of stages with registers or latches in between each stage, and partial computational results move from one stage to the next on each clock.

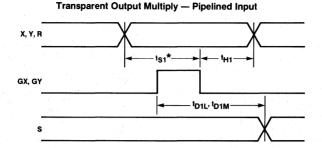

The "flow-through" architecture of the 'S558 works equally well in synchronous or asynchronous pipelined systems, but registers or latches must be provided externally. The 'S557, however, is actually a *superset* of the 'S558, and the added internal-output-latch feature adapts it particularly well to pipelined systems. The 'S556 provides latches at *both* ends.

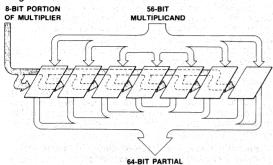

Even a smaller-scale system can make effective use of these parts. To return to the case of 56x56 multiplication, which corresponds to the word-length needed for multiplying mantissas in several popular floating-point-number formats, an iterative clocked scheme using just seven 8x8 multipliers, some adders, and an accumulator register can form the entire 112-bit doublelength product in just seven multiply/add cycles. A number of mid-range minicomputers today multiply in this manner. The multipliers are configured as suggested by the following block diagram:

64-BIT PARTIAL PRODUCT

#### Figure 2. 8x56 Cray Multiplier In Diamond Representation

There is even an occasional 8-bit or 16-bit microprocessorbased system with a need for *very* fast multiplication, where 'S557/8s or 'S556s may get used as microprocessor peripherals<sup>7,8</sup>. Digital-video systems, in particular electronic games, with 'vector graphic' capabilities are one example.

The world of 'S556/7/8 applications has turned out to include all sizes of minicomputers, digital video systems, and signal processors — FFT (Fast Fourier Transform) processors, voice recognition equipment, radar systems, digital correlators and filters, electronic seismographs, brain and body scanners, and so forth. And there are many unexpected off-beat applications, such as real-time data-rescaling circuits in instruments, altogether too numerous to list here. After all, an'S556 can multiply two 16-bit numbers together and output their entire 32-bit product in 90 nsec worst case...less time than it would take a speeding bullet to move the distance equal to the thickness of this piece of paper. How's that for Supermultiplier?

#### **The Multiplier/Dividers**

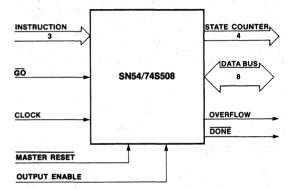

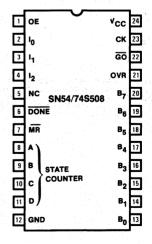

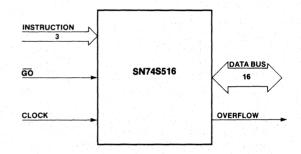

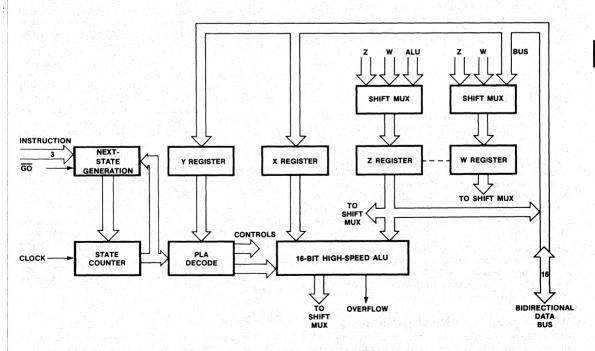

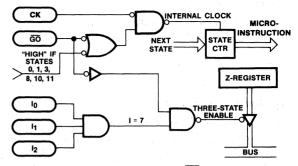

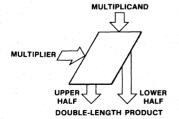

The Monolithic Memories 'S516 and 'S508 are state-of-theart TTL-compatible intelligent peripherals for microprocessors, somewhere between arithmetic sequential circuits and specialized bipolar microprocessors. The 'S516 and 'S508 each can perform any of 28 different multiply andmultiply-and-accumulate instructions, plus any of 13 different divide instructions, at bipolar speeds under the control of an internal state counter. (See Figure 2 of the 'S516 data sheet.) The state counter's sequence is in turn guided by 3-bit instruction codes which are external inputs to the 'S516/508. The 'S516 computes with 16-bit binary numbers, and the 'S508 computes with 8-bit binary numbers, as the part numbers nonetoo-subtly imply.

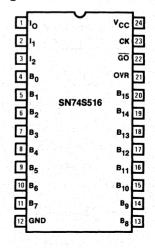

A 16-bit bi-directional data bus connects the S516 with the outside world for bringing in multipliers, multiplicands, dividends, and divisors; and returning products, quotients and remainders. It also has clock (CK) and run/wait (GO) inputs, and an overflow indication (OVR) output. The 'S508 has all of the above inputs and outputs also, except that it has only an 8-bit bidirectional data bus. Since it comes in the same 24-pin package as the 'S516, it obviously has eight more pins available for other purposes. Four of these are used to bring out the internal-state-counter value; one each is used for a completion (DONE) status output, an output-enable control (OE) input, and a master-reset (MR) control input; and one is not used at all.

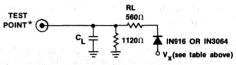

A simple, general interfacing scheme can be used to team a 'S516 with any of the currently popular 16-bit microprocessors, or an 'S508 with any 8-bit microprocessor. (See Figure 7 of the'S516 data sheet.) With a couple extra interface circuits, an'S516 can also be interfaced to an 8-bit microprocessor. Particularly if the system software is written in a highly-structured language such as PASCAL or FORTH, an'S516/508 can be retrofitted into an existing system with a large gain in performance and very little impact on either hardware or software — calls to the previous software-implemented one-step-at-a-time multiply and divide subroutines are simply rerouted to substitute a command from the microprocessor to the 'S516/508 to accept an operand and start its operation sequence.

The 'S516 and 'S508 are in fact two different "metal options" of one basic design; the 'S516 has twice as many data bits in each internal register. The 'S516 and 'S508 both have a worst-case clock rate of 6 MHz (commercial) or 5 MHz (military); the typical rate is 8 MHz. The simplest complete twos-complement 16x16 multiplication instruction can be performed in nine clock cycles by an 'S508, since 2-bits-at-a-time Booth multiplication is used;<sup>4</sup> thus, the worst-case time required by the 'S516 to multiply in this mode is 1.5  $\mu$ sec for a commercial part, and for an 'S508 it is 833 nsec. On the same basis, 32/16 division can be done in 21 clock cycles, or 3.5  $\mu$ sec worst-case, by an 'S516; and 16/8 division can be done in 13 clock cycles, or 2.2  $\mu$ sec worst-case, by an 'S508.

An 'S516/508 can perform either positive or negative multiplication or multiply-accumulation, and many of the instructions provide for "chaining" of successive computations to eliminate extra operand transfers on the bus; these features further enhance the computational speed of the 'S516/508 in particular applications. Arithmetic can be either integer or fractional with respect to positioning of the results.

An 'S516 can powerfully enhance the capabilities of *any* present-day 16-bit or 8-bit microprocessor in a computebound application. In fact, it can be used in any digital system where there is a need to multiply and divide on a bus. An 'S508 can likewise enhance the capabilities of any 8-bit microprocessor.

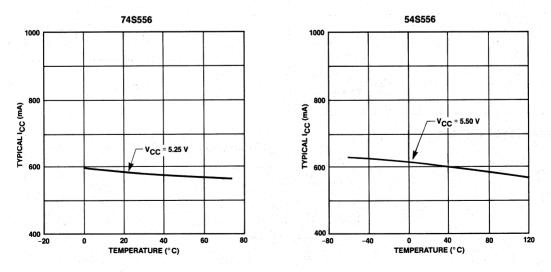

The 'S516 comes in an industry-standard 600-mil 24-pin dual-inline package, modified to include an integral aluminum heatsink which does not add appreciably to the package height. It requires only +5V and ground power connections, and draws a worst-case power-supply current of 450mA (commercial) or 500mA (military). Power consumption is greatest at cold temperatures, and decreases substantially as operating temperature increases. The 16 databus inputs require at most 0.25mA input current; the other inputs require at most 1mA. The 16 databus outputs can sink up to 8mA  $I_{\rm OL}$ . The 'S508 also fits the above description, except that its worst-case power-supply current is 380mA (commercial) or 400mA (military), and it has only 8 databus inputs and outputs.

In describing applications of these parts, it is difficult to know where to start — they can be used in almost any design where a microprocessor can be used, and you know how many places that is today. So, perhaps a good starting point is to see what uses customers have thought up all by themselves. One customer even used two 'S516s in "pingpong" mode on a single 16-bit bus! So, rather than merely speculating as to what these parts *might* be good for, here's a list of what Monolithic Memories's customers have already *proven* they are good for:

- Real-time control of heavy machinery<sup>9</sup>

- Low-cost, high-performance digital modems

- CRT graphics, including video games

- Military avionics

- Cartographic analysis

As it happens, the above are 'S516 applications, except that digital modem designs have been done with both the 'S516 and the 'S508. Several of the 'S516 designs are already in production. In each of these applications, the microprocessor could have coped all right with the computational complexity, albeit at its own less-than-tremendous speed, but a 'S516 used together with the microprocessor can provide extra muscle for handling formidable problems.

Competition? Well, since there are no second sources for the 'S516, and no competitor at present has a similar fast part capable of performing division as well as multiplication, right now the 'S516 has no *direct* competition. Indirectly, there are some competing parts which perform *only* multiplication, and would have to perform division by Newton-Raphson iteration to be usable for any application where division is required. However, the 'S516 is (as far as we know) by far the lowestpriced *bipolar* 16-bit multiplier, and the other microprocessor peripheral chips which can perform division as well as multiplication are relatively-slow MOS devices. In one case, an 8-bit cascadable CMOS part requires a 50% reduction in clock rate to do 16-bit arithmetic. And considerable numerical-analysis and programming sophistication are required to implement Newton-Raphson division with *fixed-point* operands. (It's easier with floating-point operands.) In contrast, the 'S516/508 can be easily interfaced to almost any microprocessor using one or two PALs,\* and can perform *either* multiplication or division on command?

The 'S516 is so much faster than the competing MOS chips that it can even take them on for *floating-point* computations (which some of them are designed to do) and *win*. A conference paper<sup>10</sup> describes the design of an 'S516-based S-100-bus card capable of beating an Intel 8087 2:1 on floating-point arithmetic.

Some competing parts, in particular the AMI 2811 and Nippon Electric  $\mu$ PD7720, include an on-board ROM which must be mask-programmed at the factory, which makes life difficult for small companies (or even larger ones) which are trying to get a microprocessor-based product to market quickly Also, some competing parts require sequencing by external TTL jellybeans.

And, as for using AMD/TRW 64-pin 16x16 Cray multiplier chips as microprocessor peripherals, these cost much more than the 'S516, occupy about three times the circuit-board space, multiply faster, don't divide at all except by Newton-Raphson iteration, and also require one or two "overhead" microprocessor instructions to interface for a given arithmetic operation. From a system viewpoint, when this overhead time is reckoned with, these chips provide little actual gain in multiply performance over the 'S516 at lots of extra cost, and an actual loss in divide performance: the 'S516 is much more cost-effective overall.

'S516s potentially fit into many, many places in commercial, industrial, and military electronics, particularly into small-scale real-time systems. The part is fast enough to enhance the performance of a 16-bit Motorola 68000, Zilog Z8000, or Intel 8086, as well as that of *any* 8-bit microprocessor. It is also fast enough to considerably improve the multiplication and division performance of 16-bit 2901-based "bit-slice" bipolar microcomputers, which are often used as processors in desktop graphics CRT terminals.

It is worth bringing the 'S516 to the attention of any designer who is developing:

- · A personal computer or small business computer.

- A word processor, or a more grandiose "office automation system."

- A cruise missile, or any other "smart weapon."

- · A digital modem.

- A small-scale speech-processing system. (These are very multiplication-intensive. We have one magazine article on the 'S516 in such an application!')

- · A smart instrument, which does data conversion.

- An industrial control system, particularly one which must do many coordinate transformations.

- · An all-digital studio-quality high-fidelity system.

- A cost-reduced computerized medical scanning system.

- A multiprocessor system for scientific computations<sup>12</sup>)

If an 'S516/508 is introduced into a system configured around an older microprocessor as a "co-processor" or

helpmate for the microprocessor, and the application is arithmetic-intensive, the end effect can be a major upgrading of performance at the system level.<sup>27</sup> Consequently, a major reason for designing these parts in is *microprocessor life-cycle enhancement*. In particular, many MOS microprocessors have single-length and double-length add and subtract instructions: but either they have no multiply or divide instructions at all, or else they perform their multiply and divide instructions so slowly as to jeopardize the ability of the entire system to handle its computing load in real time.

So picture, if you will, the entrepreneur or chief engineer of a firm making a successful microprocessor-based widget which has been on the market for a few months, which uses an older 8-bit microprocessor such as a 6800 or 8085 or Z80. Just when his/her sales are really taking off, here comes a new start-up competitor with a similar system, using a Motorola 68000, with added features and faster performance made possible by the 68000's 16-bit word length and multiply/divide capabilities. The 'S516 can, in this instance. serve as a "great equalizer"-it can be retrofitted into the older system as previously described, and provides even higher-speed multiplication and division than the 68000. (Enough so, actually, that there are designers using the 'S516 with the 68000.) Thus, the 'S516 can dramatically extend the life cycle of existing microcomputer systems based on microprocessors which either don't have multiplication and division instructions, or perform these operations relatively slowly.

"... THE 'S516 CAN DRAMATICALLY EXTEND THE LIFE CYCLE OF EXISTING MICROCOMPUTER SYSTEMS BASED ON MICROPROCESSORS WHICH EITHER DON'T HAVE MULTIPLICATION AND DIVISION INSTRUCTIONS, OR PERFORM THESE OPERATIONS RELATIVELY SLOWLY..." 'S508s are somewhat easier to control from a logic-design viewpoint than 'S516s; purely because they have more control inputs and outputs. However, the shorter 'S508 word length makes the part naturally fit into smaller-scale systems than those which might use an 'S516. Essentially, the 'S508 is optimized for small-scale systems.

Now that you know what these parts are, can't you think of at least half a dozen prime uses for them right in your own back yard?

# References (all available from Monolithic Memories)

- "Combinatorial Floating Point Processor as an Integral Part of the Computer," Tor Undheim, *Electro/80 Professional* Program Session Record, Session 14 reprint, paper 14/1.

- "SN54/74S516 Co-Processor Supercharges 68000 arithmetic," Richard Wm. Blasco, Vincent Coli, Chuck Hastings and Suneel Rajpal, Monolithic Memories Application Note AN-114.

- "How to Design Superspeed Cray Multipliers with 558s," Chuck Hastings, included within the SN54/74S557/8 data sheet.

- "Doing Your Own Thing in High-Speed Digital Arithmetic," Chuck Hastings, Monolithic Memories Conference Proceedings reprint CP-102.

- "Big, Fast, and Simple Algorithms, Architecture, and Components for High-End Superminis," Ehud Gordon and Chuck Hastings, Monolithic Memories Application Note AN-111.

- "Fast 64x64 Multiplication using 16x16 Flow-Through Multipliers and Wallace Trees," Marvin Fox, Chuck Hastings and Suneel Rajpal, Monolithic Memories Conference Proceedings reprint CP-111.

- "An 8x8 Multiplier and 8-bit μp Perform 16x16 Bit Multiplication," Shai Mor, *EDN*, November 5, 1979. Monolithic Memories Article Reprint AR-109.

- "Using a 16x16 Cray Multiplier as a 16-Bit Microprocessor Peripheral to Perform 32-Bit Multiplication and Division," Chuck Hastings, Monolithic Memories Conference Proceedings reprint CP-140

- "The Design and Application of a High-Speed Multiply/ Divide Board for the STD Bus," Michael Linse, Gary Oliver, Kirk Bailey, and Michael Alan Baxter, Monolithic Memories Application Note AN-115.

- "Minimum Chip-Count Number Cruncher Uses Bipolar Co-Processor," C. Hastings, E. Gordon, and R. Blasco. Monolithic Memories Conference Proceedings reprint CP-109.

- "Medium-speed Multipliers Trim Cost, Shrink Band-width in Speed Transmission," Shlomo Waser and Allen Peterson, *Electronic Design*, February 1, 1979; pages 58-65. Monolithic Memories Article Reprint AR-107.

- "A Synchronous Multi-Microprocessor System for Implementing Digital Signal Processing Algorithms," T.P. Barnwell, III and C.J.M. Hodges, Southcon/82 Professional Program Session Record, Session 21 reprint, paper 21/4.

Monolithic

# 8x8 Multiplier/Divider SN54/74S508

#### **Features/Benefits**

- Co-processor for enhancing the arithmetic speed of all present 8-bit microprocessors

- · Bus-oriented organization

- 24-pin package

- 8/8 or 16/8 division in less than 2.2 μsec

- 8x8 multiplication in less than .8 µsec

- 28 different multiplication instructions such as "fractional multiply and accumulate"

- 13 different divide instructions

- · Self-contained and microprogrammable

#### Description

The SN54/74S508 ('S508) is a bus-organized 8x8 Multiplier/ Divider. The device provides both multiplication and division of 2s-complement 8-bit numbers at high speed. There are 28 different multiply options, including: positive and negative multiply, positive and negative accumulation, multiplication by a constant, and both single-length and double-length addition in conjunction with multiplication. 13 different divide options allow single-length or double-length division, division of a previouslygenerated result, division by a constant, and continued division of a remainder or quotient.

The S508 is a time-sequenced device requiring a single clock. It loads operands from, and presents results to, a bidirectional 8bit bus. Loading of the operands, reading of the results, and sequential control of the device is performed by a 3-bit instruction field.

The 'S508 has the additional feature that operands and results can be either integers or fractions; when it deals with fractions, automatic scaling occurs. Results can be rounded if required, and an Overflow output indicates whenever a result is outside the normally-accepted number range.

For a simple multiplication of two operands and reading of the double-length result, the device takes five clock periods — one for initialization, and four for the actual multiplication. A typical clock period is 125 ns, which gives a multiplication time of 500 ns typical for 8x8 multiplication, plus 125 ns additionally for initialization, or 625 ns in all. More complex multiplications will take additional clock periods for loading the additional oper-; ands. A simple division operation requires 8 + 4 = 12 clock periods for a typical time of 1.5  $\mu$ s (16 bits/8 bits), also plus 125 ns of initialization, or 1.625  $\mu$ s in all.

## **Ordering Information**

| PART NUMBER | PACKAGE | TEMPERATURE |

|-------------|---------|-------------|

| SN54S508    | D24     | Military    |

| SN74S508    | D24     | Commercial  |

#### **Logic Symbol**

### **Pin Configuration**

TWX: 910-338-2376 2175 Mission College Blvd. Santa Clara, CA 95054-1592 Tel: (408) 970-9700 TWX: 910-338-2374 Monolithic

|                       |      | ENC |    | OPERATION                                | CLOCK |  |  |  |  |  |  |

|-----------------------|------|-----|----|------------------------------------------|-------|--|--|--|--|--|--|

| ARITHMETIC OPERATIONS |      |     |    |                                          |       |  |  |  |  |  |  |

| 10 g                  |      |     | 0  | X1 · Y                                   | 5     |  |  |  |  |  |  |

|                       |      |     | 1  | -X1 · Y                                  | 5     |  |  |  |  |  |  |

|                       |      |     | 2  | X1 · Y + K <sub>z</sub> , K <sub>w</sub> | 5     |  |  |  |  |  |  |

|                       |      |     | 3  | $-X1 \cdot Y + K_z, K_w$                 | 5     |  |  |  |  |  |  |

|                       |      |     | 4  | K <sub>z</sub> , K <sub>w</sub> /X1      | 13    |  |  |  |  |  |  |

|                       |      | 5/6 | 0  | X·Y                                      | 6     |  |  |  |  |  |  |

|                       |      | 5/6 | 1  | -X • Y                                   | 6     |  |  |  |  |  |  |

|                       |      | 5/6 | 2  | $X \cdot Y + K_z, K_w$                   | 6     |  |  |  |  |  |  |

|                       |      | 5/6 | 3  |                                          | 6     |  |  |  |  |  |  |

|                       |      | 5/6 | 4  | K <sub>w</sub> /X                        | 14    |  |  |  |  |  |  |

|                       |      | 5/6 | 5  | κ <sub>z</sub> /Χ                        | 14    |  |  |  |  |  |  |

|                       | 5/6  | 6   | 0  | X • Y + Z                                | 7     |  |  |  |  |  |  |

|                       | 5/6  | 6   | 1  | -X • Y + Z                               | 7     |  |  |  |  |  |  |

|                       | 5/6  | 6   | 2  | $X \cdot Y + K_z \cdot 2^{-8}$           | 7     |  |  |  |  |  |  |

|                       | 5/6  | 6   | 3  | $-X \cdot Y + K_z \cdot 2^{-8}$          | 7     |  |  |  |  |  |  |

|                       | 5/6  | 6   | 4  | Z, W/X                                   | 15    |  |  |  |  |  |  |

|                       | 5/6  | 6   | 5  | Z/X                                      | 15    |  |  |  |  |  |  |

| 5/6                   | 6    | 6   | 0  | $X \cdot Y + Z, W$                       | 8     |  |  |  |  |  |  |

| 5/6                   | 6    | 6   | 1  | -X • Y + Z, W                            | 8     |  |  |  |  |  |  |

| 5/6                   | 6    | 6   | 2  | X · Y + W <sub>sign</sub>                | 8     |  |  |  |  |  |  |

| 5/6                   | 6    | 6   | 3  | -X · Y + W <sub>sign</sub>               | 8     |  |  |  |  |  |  |

| 5/6                   | 6    | 6   | 4  | W/X                                      | 16    |  |  |  |  |  |  |

| 5/6                   | 6    | 6   | 5  | W <sub>sign</sub> /X                     | 16    |  |  |  |  |  |  |

| 5/6                   | 6    | 6   | 6  | (See Note 9 below)                       |       |  |  |  |  |  |  |

| 5/6                   | 5/6  | 6   | 7  | Load X, Load Z, Load W, Clear Z          | 3     |  |  |  |  |  |  |

|                       | 1000 |     |    | READING OPERATIONS                       |       |  |  |  |  |  |  |

|                       |      |     | 7  | Read Z                                   | 1     |  |  |  |  |  |  |

|                       |      | 7   | 7  | Read Z, W                                | 2     |  |  |  |  |  |  |

|                       | 7    | 7   | 7, | Read Z, W, Z                             | 3     |  |  |  |  |  |  |

| 7                     | 7    | 7   | 7  | Read Z, W, Z, W                          | 4     |  |  |  |  |  |  |

|                       |      | 5   | 7  | Round, then Read Z                       | 2     |  |  |  |  |  |  |

|                       | 5    | 7   | 7  | Round, then Read Z, W                    | 3     |  |  |  |  |  |  |

NOTES

1. X,Y are input multiplier and multiplicand.

2. X1 is the previous contents of the first rank of the X register, (either the old X or a new X).

Fractional or integer arithmetic is specified by having the next-to-the-last operand loaded using a 5 or 6 instruction respectively. All rows beginning with "5/6" in effect represent two instructions. 5 does fractional arithmetic and 6 does integer arithmetic.

- Z, W is a double-precision number. Z is the most significant half.Z, W represents addend upon input, and product (or accumulated sum) after multiplication.

- 5. K  $_{\rm Z},$  K  $_{\rm W}$  represents previous accumulator contents. K  $_{\rm Z}$  is the most-significant half.

- 6. Wsign is a single-length signed number, with sign extension.

- 7. Maximum clock cycle = 167 ns for al6-MHz clock.

- If n instruction codes are shown at the left under "instruction sequences," the number of clock cycles at the right is n+4 for multiplication and n+12 for division.

- 9. The code "5/6 6 6 6" represents an incomplete operation since it leaves the S508 in state 1 rather than in state 0, 8, or 10

Figure 1. 'S508 Instruction Set (Partial List)

|                                                                      | SUMMARY OF SIGNALS/PINS                |  |  |  |  |  |  |

|----------------------------------------------------------------------|----------------------------------------|--|--|--|--|--|--|

| B <sub>7</sub> -B <sub>0</sub> Bidirectional data bus inputs/outputs |                                        |  |  |  |  |  |  |

| 12-10                                                                | Instruction (sequential control) input |  |  |  |  |  |  |

| A, B, C, D                                                           | Internal-state-counter outputs         |  |  |  |  |  |  |

| CK                                                                   | Clock pulse input                      |  |  |  |  |  |  |

| GO                                                                   | Chip activation input                  |  |  |  |  |  |  |

| OE                                                                   | Output enable input                    |  |  |  |  |  |  |

| MR                                                                   | Master reset input                     |  |  |  |  |  |  |

| OVR                                                                  | Arithmetic overflow output             |  |  |  |  |  |  |

| DONE                                                                 | Arithmetic-operation completion output |  |  |  |  |  |  |

#### **Description** (continued)

The 'S508 device uses standard low-power Schottky technology, requires a single +5V power supply, and is fully TTL compatible. Bus inputs require at most  $250 \ \mu$ A input current, and control and clock inputs require at most 1 mA input current. Bus outputs are three-state, and are capable of sinking 8 mA at the low logic level. The 'S508 is available in both commercial-temperature and military-temperature ranges, in a 600-mil 24-pin dual-in-line ceramic package.

#### **Device Operation**

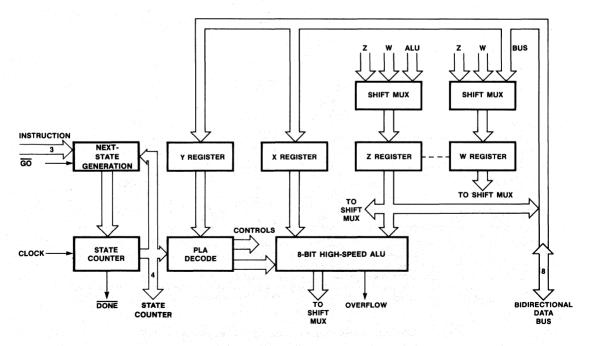

The 'S508 contains four 8-bit working registers. Y is the multiplier register; X is the multiplicand and divisor register; W is the least-significant half of a double-length accumulator, and holds the least-significant half of the product after a multiplication operation, or the remainder after a division operation; and Z is the most-significant half of this same accumulator. In addition to these registers, there is a high-speed arithmetic unit which performs addition, subtraction, and shifting steps in order to accomplish the various arithmetic operations; a loading sequencer; and a PLA control network.

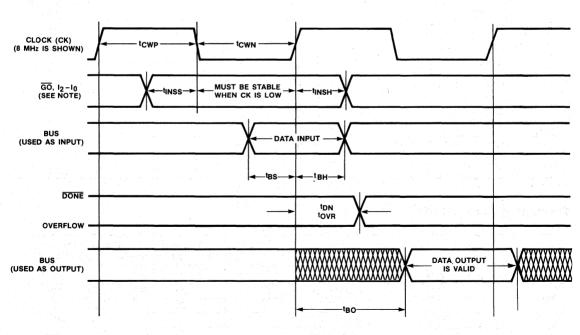

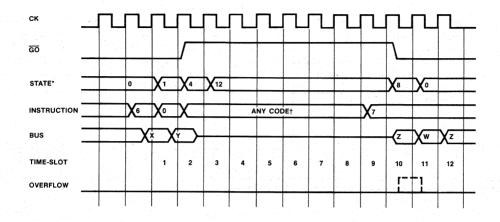

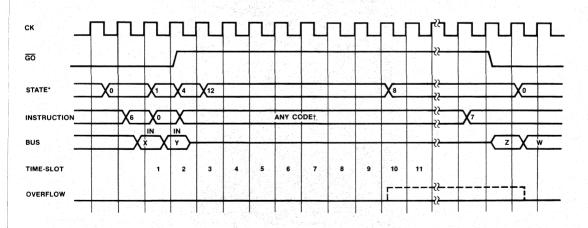

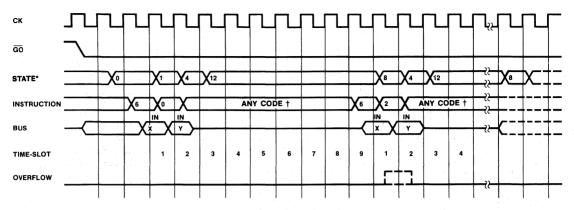

Operands are loaded into the working registers in time sequence at each clock period, under the control of this sequencer. The chip-activation signal GO must be LOW in order to begin the loading process and continue to the next step in the loading operation. If GO is continually held HIGH, the 'S508 remains in a wait state with its outputs held in their high-impedance states, so that the other devices attached to the bus may drive it. In this condition, the 'S508 does not respond to any codes on its instruction inputs; in effect, it does not "wake up" until GO goes LOW. Also, GO may change only when the clock input CK is HIGH. After all of the operands are loaded, the 'S508 jumps to the multiply routine, or to the divide routine, and performs the required operations as indicated in Figure 1. After 5 clock periods for a simple multiply or 13 clock periods for a simple divide, for example, the device is ready to place the result on the bus in time sequence.

Loop 3 times for multiplication.

Loop 6 times for fractional division, or 7 times for integer division.

#### KEY:

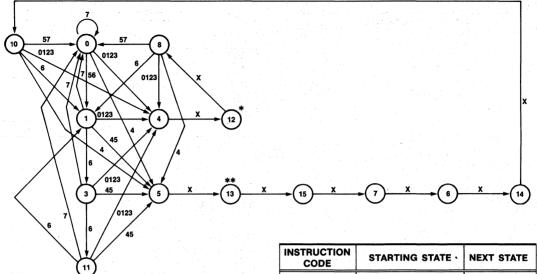

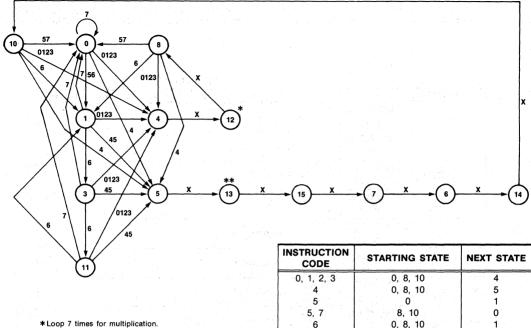

The numbers inside the circles indicate the *state* of the 'S508 multiplier/divider. These states are represented by a four-bit state counter, where A is the least-significant bit of this state counter and D is the most-significant bit. These four bits are available externally on the 'S508.

The next state of the 'S508 is a function of the present state and the instruction lines. For example if the 'S508 is at state 0 and the instruction is 0, 1, 2, or 3, then the next state is state 4 (multiply instruction); if the instruction is 4, the next state is state 5 (divide instruction); and so forth. The instructions which take the 'S508

| INSTRUCTION<br>CODE | STARTING STATE · | NEXT STATE |

|---------------------|------------------|------------|

| 0, 1, 2, 3          | 0, 8, 10         | 4          |

| 4                   | 0, 8, 10         | 5          |

| 5                   | 0                | 1          |

| 5, 7                | 8, 10            | 0          |

| 6                   | 0, 8, 10         | · 1        |

| 7                   | 0, 8, 10         | 0          |

from one state to another are indicated by the numbers written next to the state-transition path lines. "0123," for instance, implies that *any* of instructions 0, 1, 2, or 3 will take the 'S508 along the path marked "0123."

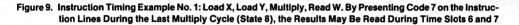

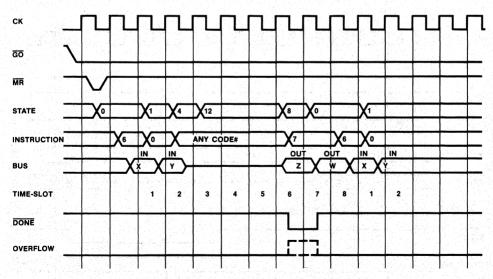

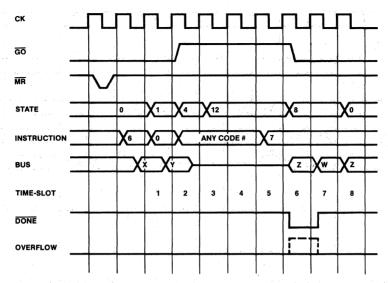

"X" next to a path implies that the path will be followed regardless of the value of the instruction inputs at that time. In other words, for the purpose of state transitions, X means "don't care." There are cases, however, where the particular instruction used may affect when the contents of the registers are available on the bus — see Figures 9 and 10 for contrasting examples of how this effect operates.

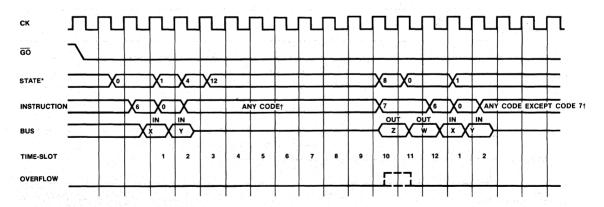

Figure 2. Transition Diagram for the 'S508 Multiplier/Divider

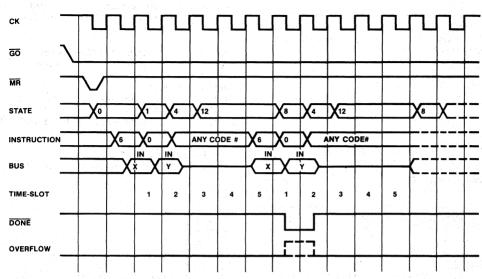

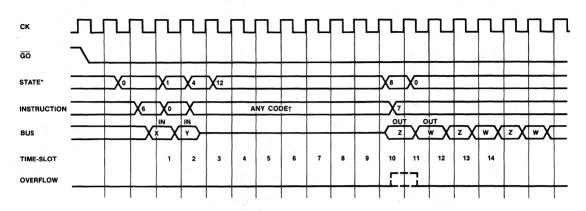

Three instruction inputs  $I_2$ ,  $I_1$ ,  $I_0$ , which may change only when the clock input CK is HIGH, select the required function and drive the sequencer from state to state. Thus, the action of the multiplier/divider at any clock period is a function of the machine state and the state of the control inputs. Figure 2 shows the multiply/divide state table, and all possible operations. After a Read or Round operation, the machine is driven back to state 0, and a new sequence of arithmetic operations is assumed. If a chain operation is being performed, such as accumulation of products, state 0 is bypassed, and loading of an operand or iumping to the next arithmetic operation occurs at the end of the previous arithmetic operation — at state 8 for a multiplication instruction, or at state 10 for a division instruction.

Register X is a dual-rank register, which allows the loading of an operand X during the multiplication or division process. If the machine enters the loading sequence and a new X operand has not been loaded, then the machine proceeds with the previously-loaded X, denoted in this text as "X1." This loading-while-processing capability allows a cycle to be saved during "chained" calculations, and also allows multiplication and division by a constant. (See Figure 13). (continued next page)

Monolithic

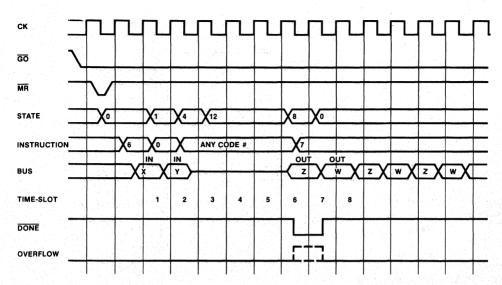

Figures 3 and 4 show the codes and durations for the 41 different possible arithmetic operations. These operations can be concatenated in strings to perform complicated 2s-com-

plement arithmetic operations at high-speed. Rounding and reading of results can be performed after any operation. Figure 5 is a block diagram of the 'S508 8x8 Multiplier/Divider.

(continued page after next)

|                                           |          |          |          |            | TIME       | E-SLC    | DT       |                |    |   |  |

|-------------------------------------------|----------|----------|----------|------------|------------|----------|----------|----------------|----|---|--|

| OPERATION                                 |          | 1        | 2        | 3          | 4          | 5        | 6        | 7              |    | 8 |  |

|                                           | INS CODE | 0        |          |            |            |          |          |                |    |   |  |

| X1 • Y                                    | BUS      | Y        | MULTIPLY |            |            |          |          |                |    |   |  |

| -X1 · Y                                   | INS CODE | 1        |          | יסיד וי    | V          |          |          |                |    |   |  |

| -XI • f                                   | BUS      | Y        | WIL      | ILTIPL     |            | а.<br>Да |          |                |    |   |  |

| V1 . V + K - K                            | INS CODE | 2        | 1        |            |            |          |          |                |    |   |  |

| К1 • Y + K <sub>Z</sub> , K <sub>W</sub>  | BUS      | Y        | ML       | LTIPL      | Y.         |          |          |                |    |   |  |

|                                           | INS CODE | 3        |          |            | V          | 1.1      |          |                |    |   |  |

| -X1 • Y + K <sub>Z</sub> , K <sub>W</sub> | BUS      | <b>Y</b> | MU       | LTIPL      | .Y         |          | 124      |                |    |   |  |

| ×·Υ                                       | INS CODE | 5/6      | 0        | MAL        |            | v        |          | 1              |    |   |  |

| N • T                                     | BUS      | X        | Y        | MU         | LTIPL      | -1       |          |                |    |   |  |

| -X · Y                                    | INS CODE | 5/6      | 1        | hat i      | LTIPL      | - 11 A.  |          |                |    |   |  |

| × · 1                                     | BUS      | X        | Y        | MU         | LIIPL      |          |          |                |    |   |  |

| X • Y + K <sub>Z</sub> , K <sub>W</sub>   | INS CODE | 5/6      | 2        | MI         | LTIPL      |          |          |                |    |   |  |

| ( · I + NZ, NW                            | BUS      | X        | Y        | NIO        | LIIFL      | <b></b>  |          | din.           |    |   |  |

| -х · ү + к <sub>Z</sub> , к <sub>W</sub>  | INS CODE | 5/6      | 3        | M          | וחודו      |          | 1        |                |    |   |  |

|                                           | BUS      | X        | Y        | MU         | LTIPL      | - T      |          |                | :  |   |  |

| X · Y + Z                                 | INS CODE | 5/6      | 6        | 0          | ML         |          |          |                |    |   |  |

| <b>ν τ τ Ζ</b>                            | BUS      | X        | Z        | Y          | IVIC       |          | 1.1.1    |                |    |   |  |

| -X • Y + Z                                | INS CODE | 5/6      | 6        | 1          | 1 MULTIPLY |          |          |                |    |   |  |

| ×·1·2                                     | BUS      | X        | Ζ        | Y          | IVIC       |          | LT       |                |    |   |  |

| Х • Y + K <sub>z</sub> • 2 <sup>-8</sup>  | INS CODE | 5/6      | 6        | 2 MULTIPLY |            |          |          |                |    |   |  |

|                                           | BUS      | X        |          | Y          |            |          | <u> </u> |                | _  |   |  |

| -X • Y + K <sub>z</sub> • 2 <sup>-8</sup> | INS CODE | 5/6      | 6        | 3          | M          | JLTIP    | i v      |                |    |   |  |

|                                           | BUS      | X        |          | Y          |            |          |          |                |    |   |  |

| (• Y + Z, W                               | INS CODE | 5/6      | 6        | 6          | 0          | M        | ULTIPI   | v              |    |   |  |

| <b>、 ι ζ, Ψ</b>                           | BUS      | X        | Z        | W          | Y          |          |          | - 1            |    |   |  |

| -X · Y + Z, W                             | INS CODE | 5/6      | 6        | 6          | 1          | M        |          | v.             |    |   |  |

| ······································    | BUS      | X        | Z        | W          | Y          | MULTIPLY |          |                |    |   |  |

| (•Y+W <sub>sign</sub>                     | INS CODE | 5/6      | 6        | 6          | 2          | M        | ULTIP    | v              |    |   |  |

| ` ' ''sign                                | BUS      | X        |          | W          | Y          |          | GLIIFI   | -•             | .: | 1 |  |

| -X • Y + W <sub>sign</sub>                | INS CODE | 5/6      | 6        | 6          | 3          | MA       | ULTIPI   | v              |    |   |  |

| sign                                      | BUS      | X        |          | W          | Y          | IVI I    | ULTIP    | <b>-</b> 1 (2) |    |   |  |

NOTES: 1) X1 is the previous contents of the first rank of the X register (either old X or a new X).

2) K<sub>Z</sub> · 2<sup>-8</sup> is a single-length signed number comprising the most-significant half of the previous double-length product and here gets added in at the least-significant end of the new result.

3) W<sub>sign</sub> is a single-length signed number, with sign-extension as needed.

4) Fractional or integer arithmetic is specified by having the next-to-last operand loaded using a 5 or 6 instruction respectively. All rows beginning with "5/6" in effect represent two instructions. 5 does fractional arithmetic and 6 does integer arithmetic.

Figure 3. Multiplication Codes and Times for 8x8 Multiplication in the 'S508

10

|                                                 | - X - 1  | 1.1 |   |     |      |      |      |     | I HALF. | -910 |    |    | 1.1 |        | -  |    | 1  |

|-------------------------------------------------|----------|-----|---|-----|------|------|------|-----|---------|------|----|----|-----|--------|----|----|----|

| OPERATION                                       |          | 1   | 2 | 3   | 4    | 5    | 6    | 7   | 8       | 9    | 10 | 11 | 12  | 13     | 14 | 15 | 16 |

| K- K/V                                          | INS CODE | 4   |   | IDE |      |      |      |     |         |      |    |    |     | 1      |    |    |    |

| к <sub>Z</sub> , к <sub>W</sub> /х <sub>1</sub> | BUS      | —   |   | IDE |      |      |      |     |         |      |    |    |     | 1      |    |    |    |

| K/V                                             | INS CODE | 5/6 | 4 |     | /IDE |      |      |     |         |      |    |    |     |        | 1  | ]  |    |

| K <sub>W</sub> /X                               | BUS      | X   |   |     | IDE  |      |      |     |         |      |    |    |     |        |    |    |    |

| K /V                                            | INS CODE | 5/6 | 5 |     | /IDE |      |      |     |         |      |    |    |     | den en |    |    |    |

| K <sub>Z</sub> /X                               | BUS      | X   |   |     | IDE  |      |      |     |         |      |    |    |     |        |    |    |    |

| Z, W/X                                          | INS CODE | 5/6 | 6 | 4   |      | /IDE | ·    |     |         |      |    |    |     |        |    | -  | ]  |

| 2, 11/1                                         | BUS      | X   | Z | W   |      | NDE  |      |     | 14      |      |    |    |     |        | -  |    |    |

| Z/X                                             | INS CODE | 5/6 | 6 | 5   |      | /IDE |      |     |         |      |    |    | 1   |        |    |    |    |

| 2/ 🔨                                            | BUS      | X   | Z |     |      | IDE  |      |     |         |      |    |    |     |        |    |    |    |

| W/X                                             | INS CODE | 5/6 | 6 | 6   | 4    | DI   | IDE  | 1.1 |         |      |    |    |     |        |    |    |    |

| W/A                                             | BUS      | x   | — | W   | _    | DIV  | IDE  |     |         |      |    |    |     |        |    |    |    |

| W /Y                                            | INS CODE | 5/6 | 6 | 6   | 5    | DI   | 'IDE |     | т       |      |    |    |     | • 1    | 1  |    |    |

| W <sub>sign</sub> /X                            | BUS      | x   | 0 | W   |      |      | IDE  |     |         |      |    |    |     |        |    |    |    |

TIME-SLOT

NOTES: 1) X1 is the previous contents of the first rank of the X register (either old X or a new X).

2) Fractional division divides a 16-bit 2s-complement number in 1 clock period less than integer division.

3) W<sub>sign</sub> is a single-length signed number, with sign-extension as needed.

4) Division operation W<sub>sign</sub>/X requires that the Z register be initialized with all-zero contents at the time Z is loaded.

5) Fractional or integer arithmetic is specified by having the operand loaded using a 5 or 6 instruction respectively. All rows beginning with "5/6" in effect represent two instructions, one of which does fractional arithmetic and one of which does integer arithmetic.

#### Figure 4. Division Codes and Time for 16/8 Division in 'S508

#### **Multiplication**

The 'S508 provides 2s-complement 8-bit multiplication, and can also accumulate previously-generated double-length products. No time penalty is incurred for accumulation, since the machine accumulates while the multiplication operation is proceeding. In addition to accumulation, the device can add into a product either a single-length or a double-length number. It can also use a previously-loaded operand as a constant, so that constant multiplication and accumulation is possible.

One key feature is the ability to perform both positive multiplications and negative multiplications, again without any speed penalty. This feature allows complex-arithmetic multiplications to be programmed with very little overhead. Another important feature is the ability to work with either fractions or integers.

#### Division

The 'S508 also provides a range of division operations. A double-length number in Z,W is divided by X; the result Q is stored in Z, and the remainder R in W. Again all numbers are in the 2s-complement number representation, with the most significant bit of an operand (whether single-length or double-length) having a negative weight. In order to facilitate repeated division, with the multiple-length quotient always keeping the same sign, the remainder is always the same sign as the dividend. Fractional or integer operation is possible, and division and multiplication operations can be concatenated. For example, the operations (AxB)/C, (A+B)/C can easily be performed. The dividend can be any previously-generated result — product, quotient, or remainder; or it may be a double-length or single-length signed operand.

#### **Reading Results**

The result of an arithmetic operation, or of a string of operations, can be read onto the 8-bit bus if the machine is at the end of an operation or at the start of a new sequence. The read operation requires that the  $\overline{GO}$  signal be held LOW so that the information is read out onto the bidirectional bus, when code 7 is specified. (See Figure 6.) Since there is a double-length accumulator Z,W, reading can take two cycles. First, register Z is read. After another clock has been received, if code 7 is still present, the least-significant half of the product from the W register is placed on the bus, or likewise the remainder if a division operation had been performed.

If the 'S508 is instructed to perform a read operation during the loading sequence, then the sequence is broken and the machine is forced back to state 0 ready to start the sequence again. Continual read operations at state 0 just swap the contents of register Z and W.

The 'S508 has a direct master reset input  $\overline{\text{MR}}$ . Alternatively, initialization of the 'S508 can also easily be performed by continually presenting instruction code 7, which after a maximum of 13 clock periods forces the machine back to state 0.

### **Integer and Fractional Arithmetic**

The 'S508 can work with either fractional or integer number representations. When working with integers, all numbers are scaled from the least-significant end and the least-significant bit is assumed to have a weight of  $2^{0}$ . For integer multiplication, accumulation, and division, all numbers are scaled from this least-significant weight, and results are correct if interpreted in this manner. The double-length register Z,W can therefore hold numbers in the range  $-2^{15}$  to  $+2^{15}-1$ ; the operands X and Y, and single-length results, are in the range  $-2^{7}$  to  $+2^{7}-1$ .

When working with fractions, the machine automatically performs scaling so that input operands and results have a consistent format. All numbers in the fractional representation are scaled from the most significant end, which has a weight of  $-2^0$  (*negative*). The binary point is one place to the right of this most-significant bit, so that the next bit has a weight of  $2^{-1}$ . The double-length register Z,W therefore holds numbers in the range -1 to  $+1-2^{-15}$  and the operands X and Y and single-length results are in the range -1 to  $+1-2^7$ . Since automatic scaling occurs, the product of two numbers always has the least-significant bit as a 0, unless an accumulation is performed with the least-significant bit being a 1.

During a chain operation with the partial results not being read onto the bus, the 'S508 will stay in either the fractional or integer mode. At the start of a sequence of operations, fractional or integer operation is designated by loading operands using instruction code 5 or instruction code 6 respectively.

Mixed fractional and integer arithmetic is also possible, by redefining the weight of the least-significant or most-significant bits. However, care must be exercised, due to the automatic scaling feature, when fractional arithmetic is programmed.

### Rounding

Rounding can be performed on the result of a multiplication or division. Generally rounding would only be called out during fractional operation, but nothing in the \$508 precludes forming a rounded result during integer arithmetic.

Rounding for multiplication provides the best single-length most-significant half of the product. Rounding occurs at the end of a multiplication, and is performed instead of a Load or Read operation when a code 5 is specified, instead of a code 7, to get from state 8 or state 10 back to state 0. (See Figure 2; also, note that this mode of operation precludes "stealing" a cycle according to the method illustrated in Figure 9.) The 'S508 looks at the most-significant bit of the least-significant half of the product  $W_7$ , and adds 1 to the most-significant half of the operation, the 'S508 is in state 0, so that the rounded product can be read, and the W register is clear.

Rounding for division is performed by forcing the leastsignificant bit of the quotient in Z to a 1 unless the division is exact (remainder is zero). This method of rounding causes a slightly higher variance in the result than having an additional iterative division operation, but is considerably easier to perform. Again, after rounding the 'S508 goes to state 0, so that a read operation can be performed, and the W register is clear.

#### **Overflow**

The S508 has an overflow output OVR which is cleared prior to each operation, and is set during an operation if the product or quotient goes outside the normally-accepted range.

For multiplication, overflow can only occur if the most negative number in the operand range is used: (-1)x(-1)=+1, which cannot be held in the S508's internal registers. Overflow can more easily occur during either positive or negative accumulation of products. For fractional arithmetic, if the product or accumulation goes outside the range of -1 to  $+1-2^{-15}$ , then the overflow flipflop will be set.

Overflow may also occur during division if the quotient goes outside the generally-accepted number range of -1 to  $+1-2^{-7}$  during fractional operation. This would occur if the divisor is less than the dividend, or equal to the dividend if a positive quotient is being generated. For integer arithmetic the numbers must be scaled by  $2^7$ .

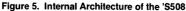

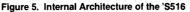

Figure 6. 'S508 Internal Circuitry of "GO" Line and Three-State-Enable

During the states 0, 1, 2, 3, 8, 10 and 11 if the "GO" line  $\overline{(GO)}$  is held at logic HIGH then the machine will be in a wait state until  $\overline{GO}$  goes to logic LOW.

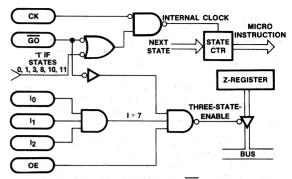

#### Figure 7. Interfacing the 'S508 to an 8-bit Microprocessor

Figure 7 shows the block diagram of a minimum 8-bit microprocessor system with its arithmetic capabilities enhanced by the use of a 'S508 8x8 multiplier/divider. The relatively small number of instruction lines (only 3) of the 'S508 provides a unique way to control the multiplier/divider. As may be seen from Figure 7, these three instruction lines are assigned to the three leastsignificant bits (LSBs) of the address bus, while the remaining address bits are decoded by a Programmable Array Logic (PAL®) circuit to determine when the multiplier/divider is selected. For example, suppose the 'S508 is assigned address 100; then any address in the range of 100-107 will enable the 'S508 (i.e., the GO line is LOW). Thus, if the address is 100 the 'S508 instruction is 0; if the address is 106 the 'S508 instruction is 0; and so forth.

# **Absolute Maximum Ratings**

| Supply voltage V <sub>CC</sub> |  |

|--------------------------------|--|

| Input voltage                  |  |

| Off-state output voltage       |  |

| Storage temperature            |  |

## **Operating Conditions**

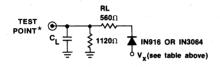

| SYMBOL            | PARAMETER                           | FIGURE | M<br>MIN | IILITAF<br>TYP | RY<br>MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | COM<br>MIN | MMER(<br>TYP | CIAL<br>Max | UNIT |

|-------------------|-------------------------------------|--------|----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|-------------|------|

| V <sub>CC</sub>   | Supply voltage                      |        | 4.5      | 5              | 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.75       | 5            | 5.25        | v    |

| TA                | Operating free-air temperature      |        | -55      |                | 125†                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0          |              | 75          | °C   |

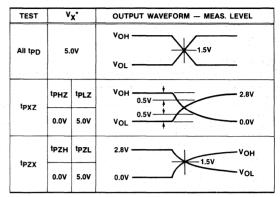

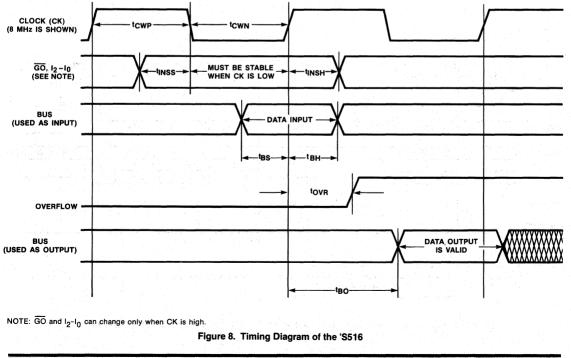

| fMAX              | Clock frequency                     | 8      | 5        |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6          |              |             | MHz  |

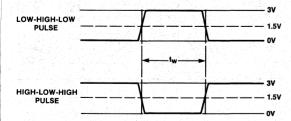

| <sup>t</sup> CWP  | Positive clock pulse width          | 8      | 90       |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70         |              |             | ns   |

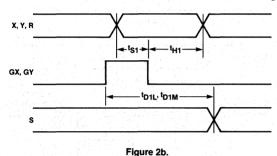

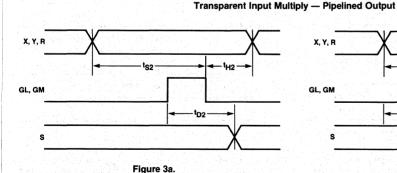

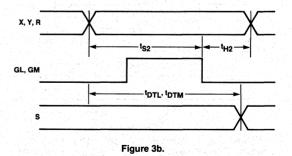

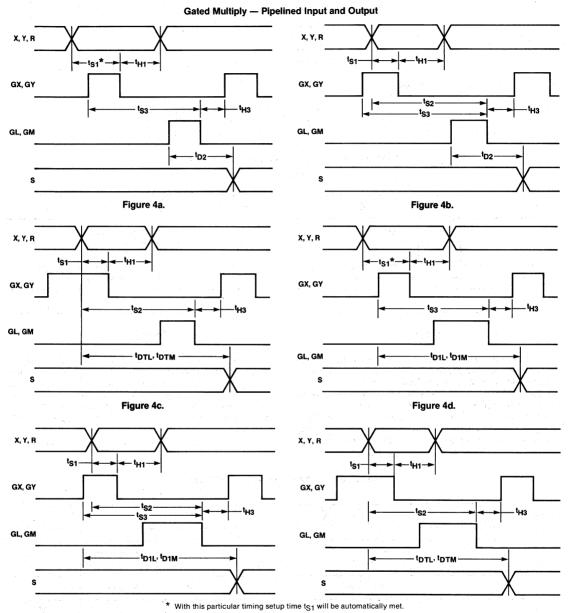

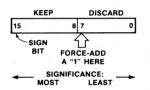

| tCWN              | Negative clock pulse width          | 8      | 60       |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50         |              |             | ns   |