## ADD ANALOG CAPABILITY TO YOUR COMPUTER WITH THE CROMEMCO D+7A I/O

by Roger H. Edelson

This month I will report on the Cromemco D + 7A I/Ocard (freely translated that's One Digital Plus Seven Analog Inputs/Outputs) and the associated Joystick Console. The D+7A I/O will be covered first, because without an analog channel you can't make use of the

Joystick Console.

The Cromemco D+7A I/O card allows you to input and output analog signals as easily as you would digital ones. One digital and seven analog input/output ports are provided, with five port address jumper wires used to select the starting port address of the board. The lowest port address is the location of the digital I/O port with the next higher seven locations setup for the seven analog I/O ports. Cromemco suggests selection of port 030 (octal) as the digital port with ports 031 through 037 as the seven analog ports.

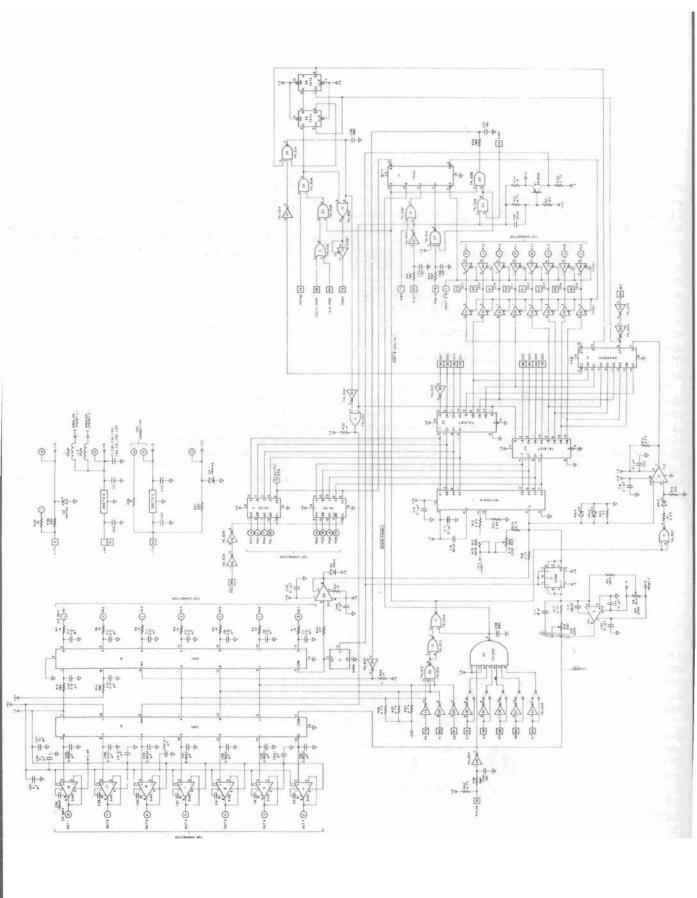

Let us begin our review of the D+7A I/O board with the single parallel digital I/O channel. Figure 1 provides the schematic diagram of Revision 3 of the board. Quad D flip-flops, Z1 and Z2 (74175's), are used as output latches and drivers. The Quad 2-Line to 1-Line Data Selectors/Multiplexers (Z25 and Z33 - 74LS157's) are used to place the digital word supplied by the computer on the input lines of the Quad D flip-flops. Being very sneaky, Cromemco, which has inverted DO7 (for reasons which will be explained later) has corrected this inversion by using the Q output of Q, on Z2 - verry tricky. The parallel digital input is buffered by the omnipresent 74367 Hex Buffers (the same animal as the possibly more familiar 8T97 series Hex Buffers). Input STB is used to strobe these buffers and is generated by Z12 (a 7442 BCD/Decimal Decoder). This strobe is produced by a Port 0 Iput command - that's port 030 if you have used the suggested port locations given by Cromemco. The strobe (or clock) to the digital output latches is generated by a port 0 output command. The digital channel is really nothing special, and only accounts for a small slice of the board space, but it does provide a convenient means of getting a digital word in and out of the computer. The real heart of this card is the seven analog Input/ouput channels.

The Cromemco D + 7A I/O board provides seven multiplexed channels of analog input/output including conversion to and from digital words. The analog-to-digital (A-to-D) conversion is performed by a successive approximation technique. As implemented in the D+7A I/O card an 8-bit multiplying digital-to-analog converter (MC 1408L-8) and an 8-bit successive approximation register (SAR) are used to provide an approximately ± 0.5% D-to-A/A-to-D converter.

Let's follow the functional operation of the analog/ digital conversion section, beginning with the analog output cycle, because it is the easiest.

Stripped to its basics, the digital-to-analog output conversion consists of applying eight bits of digital data to the input of the MC1408L-8 D-to-A converter. This produces a current of between 0 and 2ma. (depending on the value of the digital word) into pin 4. A balancing current, equal to 1/2 of the full-scale chip current) is sup-

plied by the A/D zero network to provide a zero-set and bi-polar operation. The result of these currents operating on resistor R<sub>18</sub> is to produce a voltage in the range of ± 2.56 volts to be applied to the analog output hold circuitry. These circuits are simply an operational amplifier connected as a voltage follower with a voltage holding capacitor on the input. An RCA 3140 BiMOS operational amplifier is used for this circuit to provide the characteristics needed for good operation. The 3140 device combines a MOS/FET input with a bipolar output (hence the name) to achieve low input currents with a high output drive capability. The typical electrical characteristics of the RCA 3140 are shown in Table 1. With ±5 volt supplies the input current should run around 22 amp. Using a 0.0022µfd, holding capacitor, the analog output droop caused by this current is given by V/t = I/C. Using the values provided this gives 22x10<sup>-12</sup>/0.0022 x 10th, or approximately 10 my per second droop because of the amplifier (a 1/2-bit or approximately .1% FS error in one second). Additional components of output droop are caused by output leakage current of the multiplexer switch and the capacitor and board leakages. While on the subject of the holding capacitor, the manual and the schematic both indicate that these components should be mylar. This is required both for leakage considerations and to minimize errors caused by dielectric relaxation. Unfortunately the capacitors supplied with my kit look suspiciously like ceramic types — a no-no. Cromemco does not provide a specification for analog output accuracy nor droop, other than to indicate that the refresh rate should be 1 Hz or faster.

Table I.

|                                                                |                | TEST<br>CONDITIONS                                                                    |          |          |          |          |

|----------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------|----------|----------|----------|----------|

| CHARACTERISTIC                                                 |                | V = + 15V<br>V = - 15V<br>YA = 25°C                                                   | CA3140B  | CA3140A  | CA3140   | UNITS    |

| Input Offset Voltage<br>Adjustment Resistor                    |                | Typ Value of Re-<br>sistor Between<br>Term 4 and 5 or<br>4 and 1 to Adjust<br>Max Vio | 43       | 18       | 47       | t ku     |

| Input Resistance                                               | R.             |                                                                                       | 1.5      | 1.5      | 15       | TO       |

| Input Capacitance                                              | C.             | ]                                                                                     | 4        | 4        | 4        | LF       |

| Output Resistance                                              | Ple .          |                                                                                       | 60       | 60       | 60       | 9        |

| Equivalent Wideband<br>Input Noise Voltage                     | en             | BW a 140 kHz<br>R <sub>S</sub> = 1 MQ                                                 | 48       | 48       | 48       | μV       |

| Equivalent Input<br>Noise Voltage                              | en             | f = 1 kH7 Rg L<br>I = 10 kH2 1000                                                     | 40<br>12 | 40<br>12 | 40<br>12 | nV/ Hz   |

| Short Circuit Current to<br>Opposite Supply Source<br>Sink     | ом •           |                                                                                       | 40<br>18 | 40<br>18 | 40<br>18 | mA<br>mA |

| Gain Bandwidth<br>Product                                      | ſŢ             |                                                                                       | 4.5      | 4.5      | 4.5      | MHz      |

| Slew Rate                                                      | SFI            |                                                                                       | 9        | 9        | 9        | V/µts    |

| Sink Current From Term<br>To Terminal 4 to Swing<br>Output Low |                |                                                                                       | 220      | 220      | 220      | μА       |

| Transient Response<br>Rise Time<br>Overshoot                   | l <sub>e</sub> | R <sub>L</sub> x 2 k9<br>C <sub>L</sub> = 100pF                                       | 0.08     | 0,08     | 0.08     | µ5.      |

| Settling Time<br>at 10 Vp-p-<br>(See Fig. 17) 10 mV            | 1 <sub>5</sub> | P <sub>L</sub> ± 2 k⊎<br>C <sub>L</sub> ± 190 pF<br>Vottage Follower                  | 4.5      | 4.5      | 4.5      | μS       |

Figure 1. Cromemco D + 7A I/O™ Schematic

The drive capability of the analog output is about 30 ma source and a 12ma sink; adequate enough for most applications. Again, Cromemco does not provide a specification for this function, I determined the value from the characteristics of the RCA 3140. The slew rate of the 3140 is fast enough (9  $V/\mu$ sec.) but its settling time is 4.5 $\mu$ sec. for a 1 mv. error. For this reason, 11 wait states (5.5 $\mu$ sec.) have been provided before allowing another command to be performed.

The actual operational cycle of the analog output begins when the CPU sends PSYNC and SOUT at the start of an analog output cycle in coincidence with a port address in the range 31 to 37, Z28 P5 goes high to indicate this event. Gating logic then causes PRDY to be pulled to a logic 0, causing the CPU to enter a wait state. One 02 cycle later, Z28 P8 goes low instructing the successive approximation register (SAR) to begin operation on the next 02 rising edge. The SAR then begins operation and holds down its CC output for an additional 8 02 cycles. During analog output, the SAR is used only as a timing device to generate a sufficient number of wait states to cause proper circuit operation. Its other outputs are ignored. The logic gating holds down PRDY until the SAR has completed operation and released its CC output. A total of 5.5µsec, of wait states are produced at 2MHz.

As a result of SOUT going to a logic 1, Z32 P12 goes to a logic 0. This signal switches most of the circuitry between input and output modes. In particular, pin 1 of Z25 and Z33 go low, selecting the A inputs, and Q1 produces +5V at the control inputs of Z21, turning its sections ON.

With Z25 and Z33 switched to their A inputs, the 8 data bits flow from the DO bus to the inputs of the D/A converter Z11. This causes a current to be pulled by the I/O output, pin 4, towards the -12V supply, with its magnitude proportional to the binary number at its inputs A1-A8. Resistors R12 and R13 provide the full scale reference current for the D-to-A converter, while R22 and R23 produce a half scale offset so that the code 10000000 at the D-to-A converter input produces 0 volts output. Inverter Z32 complements DO7 so that 0 volts output occurs for the code 00000000 on the DO bus, thereby giving 2's complement operation. This allows bipolar operation of the D-to-A converter with binary numbers the CPU can generate. Now we see the reason for inverting 007.

Since the CMOS transmission gate Z1 is ON, a resistance of about 30 ohms connects the D/A converter output to pin 2 of Z9. This amplifier then produces whatever voltage is needed at its pin 6 (in the range ± 2.56) so that the current though R16 and R17 exactly balances the D-to-A converter output current. The output voltage at Z9 P6 then goes to the output S/H multiplexer Z18 P3. The output port address bits A0-A2 direct the multiplexer Z18 to connect Z9 P6 to one of the .0022 voltage hold capacitors with a CMOS transmission gate. Current then flows to charge the selected holding capacitor to the desired output voltage. Charging is enabled only during the wait states of an analog output function. Voltage follower amplifiers with MOS inputs copy the holding capacitor voltages to the analog output pins,

thereby preventing drift due to loading.

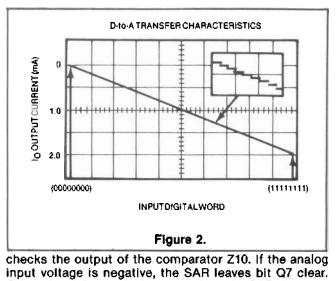

The analog input uses a successive approximation A-to-D conversion technique. Figure 2 provides a functional block diagram of this type of converter. The comparator is used as the decision element to control the state of the eight bits of the successive approximation register. When the conversion cycle starts, the SAR first sets its Q7 output to a logic 0 and outputs Q0 through Q6 to a logic 1. This causes the D-to-A to sink a current equal to one-half the full scale value of approximately 2mA. At the end of the first clock period, the SAR

Otherwise, it is set. At the same time, the SAR also sets Q6 to a logic 0. It then waits one clock cycle before using the comparator output to set the state of Q6, and clears Q5. In a similar manner, the successive approximation procedure continues until all bits Q0-Q7 have been set and subsequently tested. This procedure corresponds to the use of a set of 2 pan balance scales with binary weight values to weigh an object, and is the fastest procedure operating on only one bit at a time. Other procedures are available which operate on more than one bit at a time, at the expense of circuit complexity, and dual slope A-to-D convertors will provide more accuracy at the expense of time. The successive approximation technique is a good trade-off between circuit complexity and conversion time. At the end of the con-

sentation of the analog voltage.

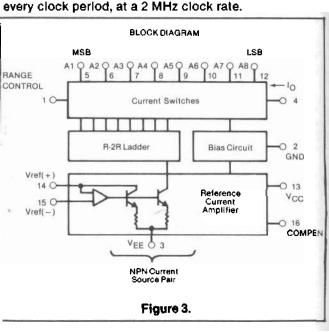

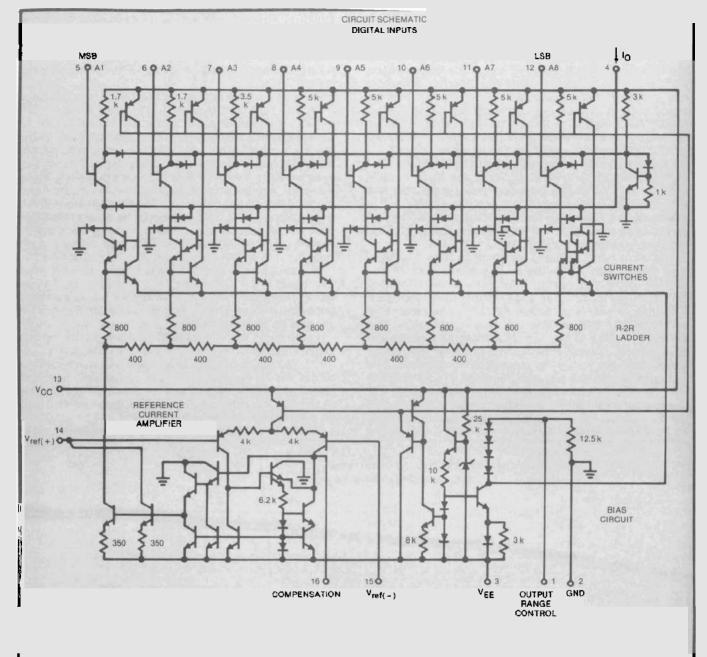

The heart of this A-to-D converter is the Motorola MC1408L-8 Eight Bit Multiplying Digital-To-Analog converter. Figure 3 provides a look at the block diagram of the MC1408L-8 and the D-to-A Transfer Characteristics. As can be seen from Table 2 (the electrical characteristics of the chip) this device provides a ±0.19% relative accuracy (to full scale). This accuracy is degraded by the scaling circuitry used on the board. Again, Cromemo does not provide an accuracy specification. The MC1408L-8 possesses a very fast settling time (300nsec to within ½ LSB). This allows a bit to be set

version cycle the SAR outputs contain the digital repre-

The MC1408L-8 consists of a reference current amplifier, anR-2R ladder network, and eight high-speed current switches. To use the device all that is necesary is to supply a reference voltage to pin 14 (done from +5X through the A/D gain network) and a reference resistor (R25) to pin 15. The switches are non-inverting, therefore a high state on the digital input line turns them on. High speed current steering switches are used in the selection of the current specified by the R-2R ladder. This ladder divides the reference amplifier current into binary-related components which are fed to the switches.

Let's take a look at the analog input cycle. At the start of the cycle the CPU sends PSYNC and SINP in coincidence with an analog port address. Z28 detects this event and initiates a cycle in a manner similar to the analog output sequence. In this case, however, the SAR output is connected by the multiplexers Z25 and Z33 to the D-to-A converter's data inputs.

The input port command for channels 1 to 7 is taken from A0 through A2 by the analog multiplexer Z8 and used to connect an analog input to the voltage follower Z20. In this case, Z21 is an open circuit. Voltage follower Z20 has a very low input current requirement in combination with a fast slewing capability. This prevents loading of the signal sources and allows full accuracy for source impedances of up to 10K ohms. Output from the voltage follower goes through R18 to inject current into the summing node at Z11 P4 and Z10 P2. After the 2-clock cycle time delay generated by Z28 to allow for settling of the input circuit, the SAR begins the conversion process which we have already discussed. At the end of the conversion cycle, the SAR outputs

contain the desired data word. The CC output goes to a logic 0, signalling the end of the conversion process and allowing the CPU to proceed. The CPU then inputs Q0 through Q7 as its data. Q7 is complemented to produce a 2's complement binary code and allow straightforward bipolar operation.

Let's now take a look at the D + 7A I/O mechanized as a kit. The card is of the same high quality material and construction as I have come to expect from the Cromemco kits. The board is high quality glass with all the etch tinned. The edge board connectors are gold plated for reliability. The solder masking and the component marking are excellent. The solder masking in particular is detalled enough to prevent many of the easily-made solder splash problems. The board in places looks unfortunately as if it were laid out by an engineer. This does not affect operation, and is probably necessary to assure good noise characteristics and reliable operation, but it is esthetically somewhat unappealing.

Construction is straightforward requiring only about 2½ hours from unpacking to board cleaning, a step which Cromemco fails to mention — but is extremely important in any analog board. Some small problems showed up during assembly:

1) Some of the IC's should be temporarily inserted when installing the 0.0022  $\mu$ fd. capacitors, particularly IC 18. This must be done or you will find it very difficult to get the IC inserted after the capacitors have been soldered in place. IC's 23 and 34 are also tight because of the two capacitors C38 and C39. Resistor R13 must be inserted before the potentiometer R12.

2) The board pads are not always correctly spaced,

Table II. ELECTRICAL CHARACTERISTICS FOR EQUIPMENT DESIGN At V  $^+$  = 15 V, V  $^-$  = 15 V, T<sub>A</sub> = 25 °C Unless Otherwise Specified

| OULANAOTERICTIC                                               |            | LIMITS                 |         |              |                        |      |              |                        |      | UNITS      |

|---------------------------------------------------------------|------------|------------------------|---------|--------------|------------------------|------|--------------|------------------------|------|------------|

| CHARACTERISTIC                                                |            | CA3140                 |         |              | CA3140                 |      |              | CA3140                 |      |            |

|                                                               | Min.       | Тур.                   | Max.    | Min.         | Тур.                   | Max. | Min.         | Тур.                   | Max. | 9          |

| Input Offset Voltage,  VIO                                    | -          | 0.8                    | 2       | -            | 2                      | 5    | -            | 5                      | 15   | m.V.       |

| Input Offset Current,  I <sub>IO</sub>                        | _          | 0.5                    | 10      | -            | 0.5                    | 20   | -            | 0.5                    | 30   | pA         |

| Input Current, I <sub>I</sub>                                 | -          | 10                     | 30      | _            | 10                     | 40   | -            | 10                     | 50   | pA         |

| Large-Signal<br>Voltage Gain, A <sub>OL</sub>                 | 50 k<br>94 | 100 k<br>100           | _       | 20 k<br>86   | 100 k<br>100           | -    | 20 k<br>86   | 100 k<br>100           | _    | V/V<br>dB  |

| Common-Mode<br>Rejection Ratio, CMRR                          | -<br>86    | 20<br>94               | 50<br>— | -<br>70      | 32<br>90               | 320  | -<br>70      | 32<br>90               | 320  | μV/V<br>dB |

| Common-Mode<br>Input-Voltage<br>Range, V <sub>ICR</sub>       | - 15       | - 15.5<br>to<br>+ 12.5 | 12      | - 15         | - 15.5<br>to<br>+ 12.5 | 12   | - 15         | - 15.5<br>to<br>+ 12.5 | 11   | v          |

| Power-Supply<br>Rejection △V <sub>IO</sub> /△V<br>Ratio, PSRR | -<br>80    | 32<br>90               | 100     | -<br>76      | 100<br>80              | 150  | -<br>76      | 100                    | 150  | μV/V<br>dB |

| Max. Output V <sub>OM</sub><br>Voltage V <sub>OM</sub>        |            | 13<br>- 14.4           | _       | + 12<br>- 14 | 13<br>- 14.4           | -    | + 12<br>- 14 | 13<br>- 14.4           | _    | v          |

| Supply Current, I +                                           | -          | 4                      | 6       | -            | 4                      | 6    | -            | 4                      | 6    | mA         |

| Device Dissipation, PD                                        | -          | 120                    | 180     | -            | 120                    | 180  | -            | 120                    | 180  | mW         |

| Input Current, I <sub>1</sub> ▲                               | -          | 10                     | 30      | -            | 10                     | -    | -            | 10                     | -    | nA         |

| Input Offset<br>Voltage V <sub>IO</sub> ▲                     | -          | 1.3                    | 3       | -            | 3                      | =    | -            | 10                     | -    | mV         |

| Large-Signal<br>Voltage Gain, A <sub>O1</sub> ▲               | 20 k<br>86 | 100 k<br>100           | _       | _            | 100 k<br>100           | _    | _            | 100 k<br>100           | _    | V/V<br>dB  |

| Max. Output VOM<br>Voltage, * VOM                             |            | + 19.5<br>- 21.4       | -       | -            | -                      | _    | -            | 1-                     | _    | v          |

| Large-Signal<br>Voltage Gain, A <sub>OL</sub> ‡*              | 20 k<br>86 | 50 k<br>94             | _       | -            | -                      | =    | =            | =                      | -    | V/V<br>dB  |

$<sup>\</sup>underline{\phantom{A}}$  At  $V_{O} = 26V_{p-p}$ , + 12V, - 14V and  $R_{L} = 2 \, k\Omega$ .

At R<sub>L</sub> = 2 kΩ.

<sup>▲</sup> At  $T_A = -55$  °C to ± 125 °C, V + = 15 V, V - = 15 V, V<sub>O</sub> = 26 V<sub>D-D</sub>, R<sub>L</sub> = 2 kΩ.

<sup>\*</sup> At V + = 22 V, V - = 22 V.

$<sup>^{\</sup>ddagger}$  At  $V_{O} = +19 V_{1} - 21 V_{2}$ , and  $R_{L} = 2 k Q_{2}$ .

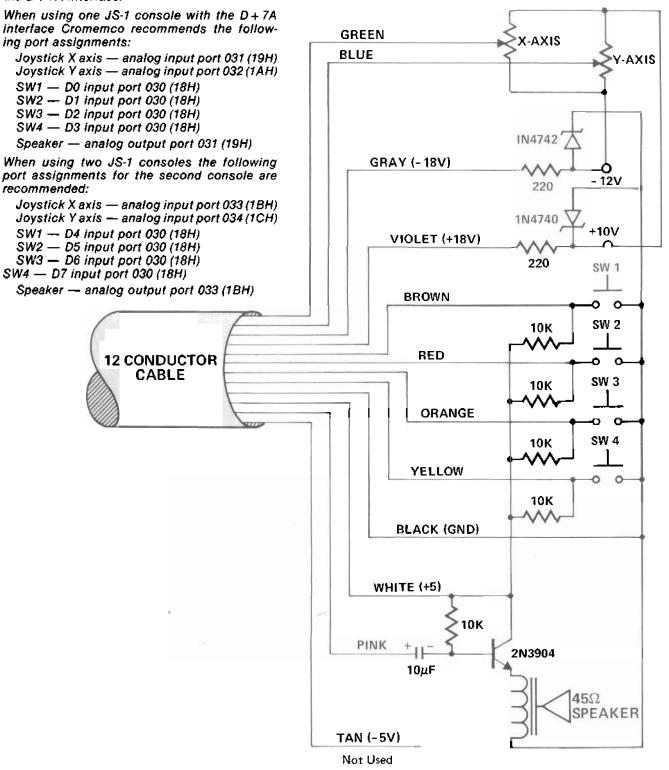

Figure 4. Circuit Schematic

or the 0.1 µfd capacitor lead spacing, making it difficult beal some of these capacitors.

3) No layout drawing is provided. The component marking on the board, as indicated earlier, is excellent making assembly a not difficult task. But I like a layout drawing also — it can't cost that much.

These gripes are really very minor and don't affect the kit in any way. They really don't much slow down construction either.

One nice feature — my CA3140 IC leads were already shaped, which made light work of inserting these devices. Again, though Cromemco doesn't mention it, don't forget to clean the solder resin off your board. This step is a must to reduce the board leakage current and achieve high-quality A-to-D operation.

After assembly of the board it is necessary to calibrate the analog/digital/analog channels. The calibration procedure begins with the A-to-D channel. Known voltages must be applied to the analog input and the A/D gain (R12) and A/D zero (R22) are adjusted until the digital value is correct. While this is straightforward, (even though R12 and R22 interact requiring an iterative

procedure) the instructions require an input of + 2.54 v and -2.56 volts — values not likely to be found lying around everyone's computer room. A variable power supply and a digital voltmeter will do the job — if you have one.

A possible alternative would be to set the analog input to 0 volts (short it) and adjust the R22 until the output of the selected digital port is "0". Then apply any known-or measured-voltage (a battery, etc.) and set the A-to-D gain (R12) until the digital value is the representation of the analog voltage supplied (remember, each bit = 20mv). Reversing the battery will provide a negative voltage to check both polarities. It may be necessary to readjust R22 to get the correct negative digital value. Remember, as the D+7A I/O uses two's complement representation, 10000000 (80<sub>H</sub>) is equal to -2.56V and FF<sub>H</sub> (11111111) is not "-0" but actually -20my. For this reason the negative full scale value is 20 mv. greater than the positive full scale (bit 8, the sign bit, provides the extra -20mv.). Figure 5 gives an example of some of the 8-bit two-s complement representation of analog voltages.

After the analog input channel has been calibrated the analog output is calibrated. An accurate voltmeter is all that is required for this simple operation. Using the program supplied by Cromemco R16 (D-to-A) gain is adjusted for full scale positive output. The program is then modified and the D-to-A zero pot. (R8) is adjusted for a zero output. This procedure may have to be repeated once or twice as these controls interact also.

Besides providing the digital and analog I/O channels at the top edge board connector (gold plated for reliability) Cromemco has also brought out several power supply voltages. Analog and digital grounds are separated to avoid placing digital return currents in the analog ground returns. Figure 6 shows the top connector pin assignments. Cromemco has also thoughtfully provided the female counterpart to the top-edge connector. This connector is equipped with a nice handle for easy insertion and removal.

| 01111111 | + 2.54 volts |

|----------|--------------|

| 0000001  | + 0.02 volts |

| 00000000 | 0 volts      |

| 11111111 | - 0.02 volts |

| 10000000 | - 2.56 volts |

Figure 5.

The D+7A I/O card is a well-thought-out addition to your computer, which will expand the capabilities of your present installation and allow you to handle analog signals as easily as digital. Some of the more popular applications for this card would be oscilloscope graphics, process control, music or voice synthesis, and joystick interfaces. In line with the last mentioned application, Cromemco provides a Joystick Console (JS-1) which is set up to interface with the D+7A I/O card.

As can be seen in the schematic, the JS-1 provides four switches as digital inputs, two pots (with mechanical trim adjustments) arranged as a two-axis joystick as analog inputs, and an emitter follower driving a 45-ohm speaker as one analog output. The digital switches operate to provide +5 volt in their open condition and ground in the energized state. The emitter follower is AC coupled with a time constant of about 50msec.

Construction is extremely easy. However, I don't much care for unsupported components. I wish Cromemoo had provided a standoff for the 10K resistors. Initial checkout is also a snap. The instructions are more than adequate.

With the JS-1 Cromemco also provides the software for Dazzle-Doodle<sup>TM</sup>, a program which is designed to allow the user to draw full-color pictures on the screen of an ordinary TV under joystick control. The hardware required is a D+7A I/O to interface the joystick, and a Cromemco TV Dazzler<sup>TM</sup> for the TV display interface. The computer must supply 2K of static RAM for picture element storage, and another approximately 128 bytes of program storage.

Cromemco also provides software support for the joystick console including Dazzle-Doodle, Track, Chase!, and Spacewar, complete with documentation. Each of these games is available on paper tape with the documentation for \$15 a piece.

The JS-1 provides an easy and lowcost way to provide an analog input to your D+7A I/O card. When these two units are combined, it is easier to enter analog inputs into your computer than digital — and in some cases more fun.

## CONNECTOR PIN ASSIGNMENTS

| COMPONENT SIDE     |    | PIN No. | П   | PIN No.                | SOLDER SIDE           |  |  |

|--------------------|----|---------|-----|------------------------|-----------------------|--|--|

| ANALOG GROUND      |    | A       | 11  | - 1                    | ANALOG GROUND         |  |  |

| ANALOG INPUT 7     |    | В       |     | 2                      | ANALOG OUTPUT 7       |  |  |

|                    | 6  | С       |     | 3                      | • 6                   |  |  |

|                    | 5  | D       | 76  | 4                      | 5                     |  |  |

|                    | 4  | £       | Πſ  | 5                      | 4                     |  |  |

|                    | 3  | F       | 71  | 6                      | 3                     |  |  |

|                    | 2  | н       | 10  | 7                      | 2                     |  |  |

| ANALOG INPUT       | 1  | J       | 7   | 8                      | ANALOG OUTPUT I       |  |  |

| -12 V REGULATED    |    | К       | 7   | 9                      | +12V REGULATED        |  |  |

| ANALOG GROUND      |    |         | 70  | 10                     | ANALOG GROUND         |  |  |

| -ITV UNREGULATED   |    | М       | 76  |                        | +17 V UNREGULATED     |  |  |

| - 5V REGULATED     |    | N       | 76  | 12                     | + 5V REGULATED        |  |  |

| INPUT STB          | 3  | P       |     | 13                     | OUTPUT STA            |  |  |

| PARALLEL INPUT BIT | 7- | R       | 11  | 14                     | PARALLEL OUTPUT BIT 7 |  |  |

|                    | 6  | S       | 7 [ | 15                     | 6                     |  |  |

| Lawrence Ben Law   | 5  | T       |     | 16                     | 5                     |  |  |

|                    | 4  | U       |     | 17                     | 4                     |  |  |

|                    | 3  | ٧       |     | 18                     | 3                     |  |  |

|                    | 2  | W       |     | 19                     | 2                     |  |  |

|                    | 1  | ×       |     | 20                     |                       |  |  |

| PARALLEL INPUT BIT | 0  | Y       |     | 21 PARALLEL OUTPUT BIT |                       |  |  |

| DIGITAL GROUND Z   |    | 7       | 22  | DIGITAL GROUND         |                       |  |  |

PC BOARD

Figure 6.

The Cromemoo JS-1 joystick console is a general purpose I/O device designed specifically for use with mini and microcomputers. A Cromemoo D+7A analog interface can be used to interface one of two JS-1 consoles to any computer using the S-100 Microcomputer Bus.

Each joystick console includes a two-axis joystick, four push button switches, and an audio amplifier and speaker in an attractive, finished enclosure. A 12-conductor cable is included to connect the console to the top edge connector of the D + 7A interface.

Figure 7. The Schematic Diagram of the JS-1

68 INTERFACE AGE JULY 1977