Owner's Manual

**Model 2422**

# Multimode Floppy Disk Controller

California Computer Systems

# CCS MODEL 2422 FLOPPY DISK CONTROLLER OWNER'S MANUAL

COPYRIGHT 1980

CALIFORNIA COMPUTER SYSTEMS 250 CARIBBEAN DRIVE SUNNYVALE, CA 94086

MANUAL NO. 89000-02422

# TABLE OF CONTENTS

| CHAPTER | 1 | INTRODUCTION<br>1.1 BUS COMPATIBILITY 1-1<br>1.2 DISKETTE COMPATIBILITY 1-1<br>1.3 USER OPTIONS 1-2<br>1.4 THE BOOT/MONITOR ROM 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

|---------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| CHAPTER | 2 | <pre>SETUP AND INSTALLATION 2.1 2422 SETUP</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |

| CHAPTER |   | THE 2422 ROM-RESIDENT FIRMWARE       3-1         3.1 COLD-START ENTRY       3-1         3.2 PAGE 0 RAM USED BY FIRMWARE       3-1         3.3 THE FIRMWARE DISK ROUTINES       3-2         3.3.1 Diskette Format       3-2         3.3.2 The Primitive Disk Routines       3-3         3.3.3 Disk Parameters For Disk       0perations         0perations       3-4         3.4 THE BOOTSTRAP LOADER       3-4         3.5 THE MONITOR       3-5         3.5.1 The Monitor's Memory Space       3-5         3.5.2 The IOBYTE and the Basic I/O       3-6         3.5.3 Bringing Up The Monitor       3-8         3.5.4 Monitor Commmands       3-8         3.5.5 Error Messages       3-9         3.5.6 Command Description       3-11 | L |

| CHAPTER | 4 | THEORY OF OPERATION         4.1 THE 2422 REGISTERS       4-1         4.2 THE SYSTEM INTERFACE       4-2         4.2.1 The Bank Select Circuitry       4-2         4.2.2 Selecting the 2422 Registers       4-3         4.2.3 Memory-Mapped I/O       4-3         4.2.4 Selecting the ROM       4-4         4.2.5 The Board Select Line and LED       4-5         4.2.6 PHANTOM* and FF Detect       4-5         4.2.7 The Data Bus       4-6                                                                                                                                                                                                                                                                                           | 3 |

i

# CHAPTER 1

# INTRODUCTION

California Computer System's 2422 Floppy Disk Controller is an S-100 compatible board which can control four drives in any combination of 5.25" and 8" two-sided or single-sided drives. It can read and write both single-density (FM) and double-density (MFM) soft-sectored diskettes. An on-board 2K ROM contains monitor firmware designed for systems using CCS's 2810 Z-80 CPU and bootstrap loader for loading in CP/M from disk.

# 1.1 BUS COMPATIBILITY

The 2422 is compatible with the IEEE proposed standards for the S-100 bus, thus making it bus compatible with most of the S-100 systems currently on the market. The drive busses are designed primarily to be plug-compatible with Shugart 800/850 and 400/450 drives and any drives using the same drive bus. However, some additional signals common to other drives have also been incorporated. See Appendix A for the signals used by the system and disk drive busses.

# 1.2 DISKETTE COMPATIBILITY

Western Digital's FD1793 disk controller chip used by the 2422 reads and writes diskettes which conform to the IBM 3740 format standard for single-density diskettes or the IBM System 34 format standard for double-density diskettes and which contain 128, 512, 256, or 1024 bytes per sector. Because of its format requirements, it cannot read diskettes formatted by the 1771 disk controller chip, although the 1771 can read diskettes formatted

and the second

. .

|                   |        | 4.2.8       ROM Wait Circuitry       4-6         4.2.9       Auto Wait       4-6         4.3       DISK DRIVE INTERFACE       4-8         4.3.1       The Clock Signal       4-8         4.3.2       The Read Clock Generator       4-8         4.3.3       Read Data Pulse Width       4-9         4.3.4       Write Precompensation       4-10         4.3.5       Head Load Timing       4-11 |

|-------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APPENDIX          |        | THE 2422 DISK CONTROLLER BUSSES<br>A.1 THE SYSTEM BUS A-3<br>A.1.1 Address and Data lines A-3<br>A.1.2 CPU Status Signals A-3<br>A.1.3 Control Inputs A-3<br>A.1.4 Control Outputs A-4<br>A.1.5 The Power Lines A-4<br>A.1.6 The 2422 System Bus Pin<br>Assignments A-5                                                                                                                          |

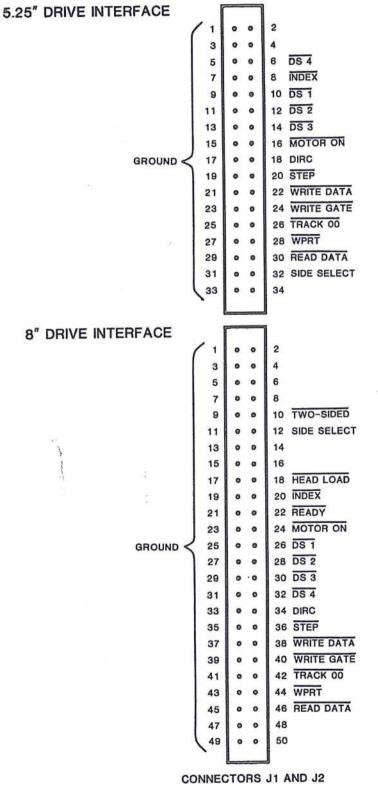

| ×                 |        | A.2 THE 2422 DISK DRIVE BUSSES A-6<br>A.2.1 The Disk Drive Busses Pin<br>Assignments A-8                                                                                                                                                                                                                                                                                                         |

| APPENDIX          | В      | 2422 PROGRAMMING INFORMATION<br>B.1 THE 2422 ADDRESSABLE REGISTERS B-3<br>B.1.1 Control Register 1 B-4                                                                                                                                                                                                                                                                                           |

|                   |        | B.1.2 Status Register 1 B-5<br>B.1.3 Control Register 2 B-6                                                                                                                                                                                                                                                                                                                                      |

| -14 <sup>61</sup> | *)<br> | B.1.4 Status Register 2 B-6<br>B.1.5 Bank Select Port B-8                                                                                                                                                                                                                                                                                                                                        |

| 2                 |        | B.2 DISKETTE FORMAT B-9                                                                                                                                                                                                                                                                                                                                                                          |

|                   |        | Diskette B-10                                                                                                                                                                                                                                                                                                                                                                                    |

|                   |        | B.2.2 Formatting a Double-density<br>Diskette B-11                                                                                                                                                                                                                                                                                                                                               |

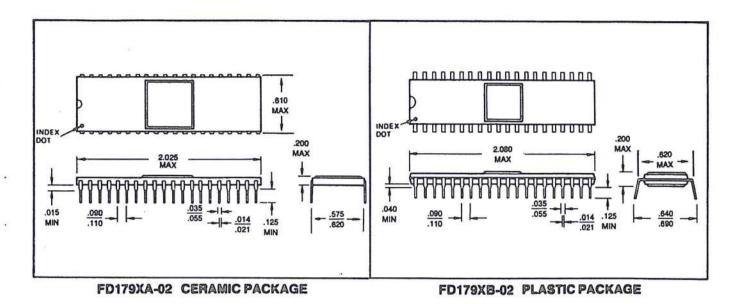

| APPENDIX          | С      | 1793 DATA SHEET                                                                                                                                                                                                                                                                                                                                                                                  |

| APPENDIX          |        | TECHNICAL INFORMATION<br>PARTS LIST                                                                                                                                                                                                                                                                                                                                                              |

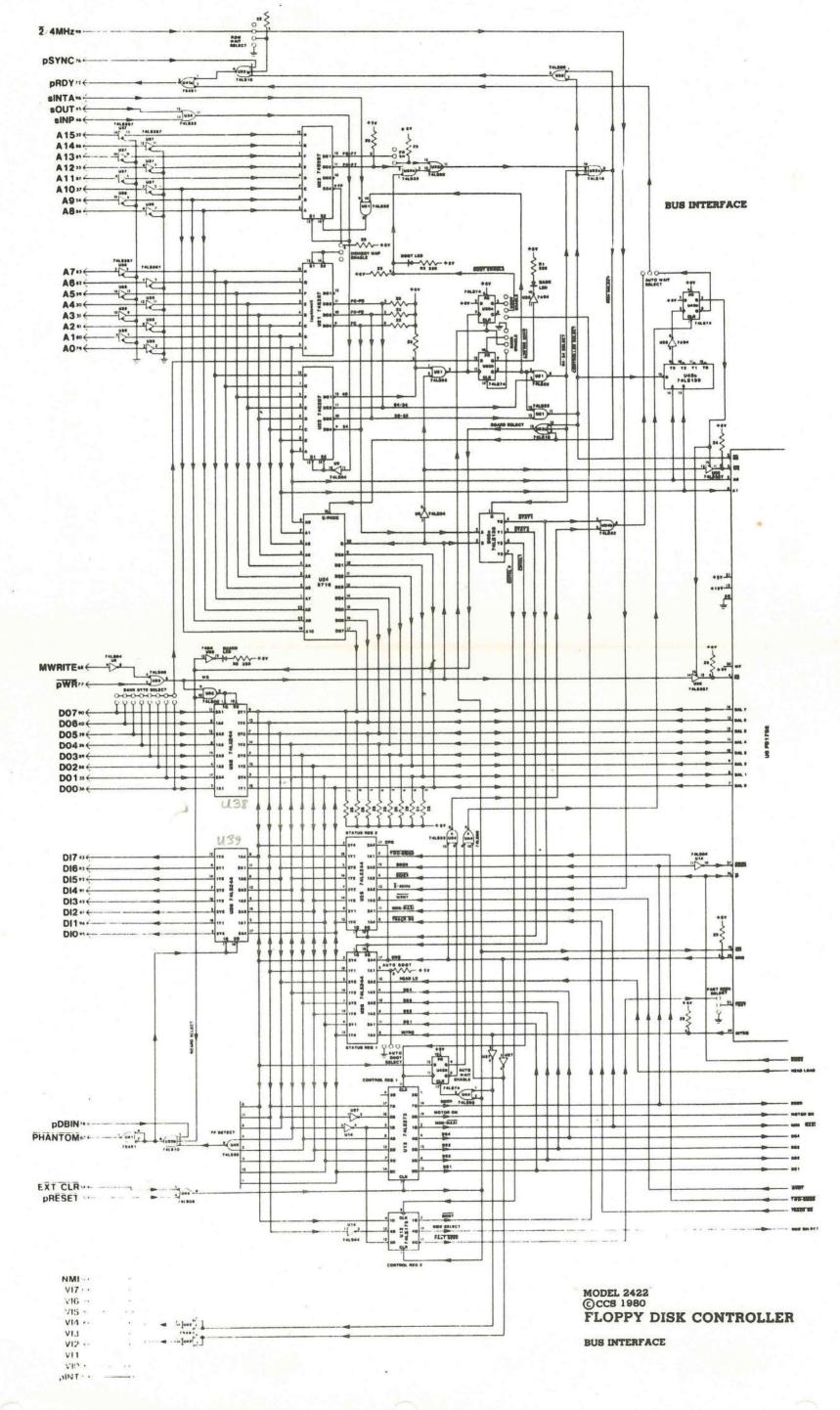

| 1                 |        | BUS INTERFACE SCHEMATIC C-7<br>DRIVE INTERFACE SCHEMATIC C-9                                                                                                                                                                                                                                                                                                                                     |

| APPENDIX          | E      | FIRMWARE LISTING                                                                                                                                                                                                                                                                                                                                                                                 |

| APPENDIX          | F      | LIMITED WARRANTY                                                                                                                                                                                                                                                                                                                                                                                 |

ii

#### INTRODUCTION

by the 1793. The utility program COPY provided with CCS's CP/M package reformats diskettes formatted by the 1771 so that the 1793 can read them.

#### 1.3 USER OPTIONS

The 2422 incorporates a number of optional features that are jumper-selected or configured. These are described fully in Chapter Two. In addition, CCS makes available an address decoding ROM that can be inserted in U21 to allow memory mapping of the 2422 registers to addresses FFF8h-FFFDh.

# 1.4 THE BOOT/MONITOR ROM

The on-board ROM contains a bootstrap loader for loading CP/M into memory from disk and the MOSS 2.2 Disk Monitor. Both the bootstrap loader and the MOSS monitor take advantage of the Both Z-80's large instruction set and thus cannot cannot be used with an 8080 CPU. The MOSS monitor is designed to work specifically with CCS's Model 2810 Z-80 CPU. The 2422 gives you the choice of having CP/M loaded automatically on system power-on and reset, or of having the monitor entered on power on or reset. The monitor command allows you to boot in CP/M from the monitor. Once Boot is loaded, the monitor and bootstrap loader can CP/M be software-disabled, the Loader program supplied with CCS's CP/M package doing so automatically. When the ROM is enabled and addressed, the ROM LED lights and the 2422 generates the PHANTOM signal which allows memory overlay of all devices which share the ROM's memory space and recognize the PHANTOM signal.

Those of you who want to alter the firmware or design your own will find programming information on the 2422 in Appendix B.

# CHAPTER 2

# SETUP AND INSTALLATION

#### 2.1 2422 SETUP

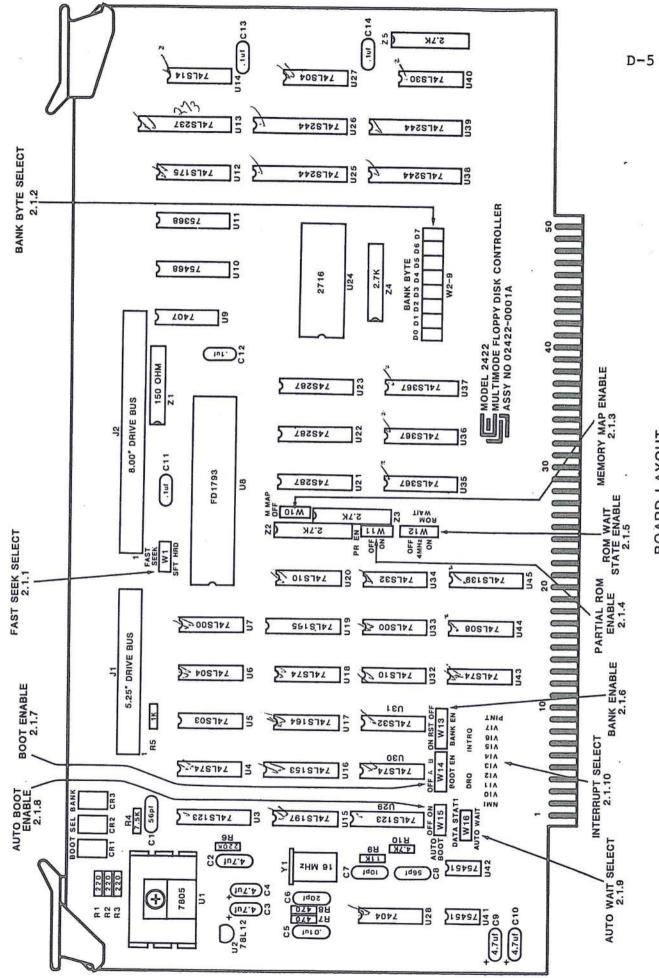

Your 2422 Floppy Disk Controller is designed to be flexible enough to fit different systems and different customer needs. This flexibility is achieved in part by on-board jumpers which allow you to selectively enable/ disable features or configure them to fit your needs. Each jumper-enabled or configured feature is discussed in a section below. In Appendix E, you will find a board layout on which the jumpers are clearly indicated, labeled, and referenced to the appropriate section below.

# 2.1.1 FAST-SEEK SELECT JUMPER

If you are not using a voice coil drive, remove the FAST SEEK jumper plug entirely. If you are using a voice coil drive, the FAST SEEK jumper allows you to either software-enable or hardware-enable the fast seek mode. Placing the jumper plug at the SFT position as shown in Figure 2-1 allows you to enable fast seeks by writing a 0 to bit 4 of Control Register 2. Placing the jumper plug at the HRD postion permanently enables fast seeks. If you are planning to use the CCS firmware/software supplied with the 2422, fast seeks will be enabled only if you set the jumper to the HRD position, since the CCS software does not enable the fast seek mode.

FIGURE 2-1

# 2.1.2 BANK-BYTE SELECT JUMPERS

The 2422 Disk Controller can be hardware assigned to one of eight banks, or levels of 64K. To do so, place the jumper plug on the BANK BYTE jumper header which corresponds to the bank level to which you want this board assigned. For example, putting the plug on header DO assigns this board to bank 0. Once you have assigned this board to a bank, you can in turn select that bank and enable the board by outputting to port 40 a data byte with a logic 1 in the bit position corresponding to the bank level. If you plan to use the version of CP/M supplied by CCS, assign the board to bank 0. The Loader program on disk disables the monitor and bootstrap loader firmware by outputting a hex 01 to port 40h. If you have your 2422 assigned to any other bank than bank 0, your board will be disabled.

#### 2.1.3 MEMORY-MAP ENABLE JUMPER

As mentioned in the introduction, CCS makes available to its 2422 users a control ROM which allows the registers on the 2422 to be memory mapped. If you plan to use the memory-map option, you can enable/disable memory mapping through the M MAP jumper. Position OFF of the M MAP jumper disables memory mapping; the opposite position enables it. The CCS firmware does not make use of memory mapping.

# 2.1.4 PARTIAL-ROM ENABLE JUMPER

By setting the PR EN jumper to ON, you allow the portion of the ROM containing the basic I/O routines and the primitive disk routines used by the monitor to be available after CP/M is loaded in. This portion of the ROM, located at F600h-F7FFh, contains essentially the same basic I/O routines as the CCBIOS on disk. If you are planning to tailor the CCBIOS to your system, you may wish to have your customized BIOS call some of the routines located in the ROM. This will give you the greater reliability of ROM memory and save some disk space. If you do not wish the basic I/O portion of the ROM to remain in memory after CP/M is loaded in, set the PR EN jumper to OFF.

# 2.1.5 ROM WAIT STATE ENABLE JUMPER

The on-board ROM has the relatively slow memory access time of 450 nsecs. A CPU running at 4 MHz will not provide the access time needed by the ROM. The access time of the 1793 registers when they are memory mapped is also slow, about 350 nsecs. The ROM WAIT jumper, when set to ON, allows you to place the CPU in one Wait state per cycle in which either the ROM or the 1793 is selected. Some CPUs, such as CCS's Model 2810 Z-80 CPU, use pin 98 of the bus to indicate whether the CPU is operating at 2 or 4 MHz. If your CPU does so, setting the jumper to 4 MHz allows the 2422 to place the CPU in a Wait state only when the CPU is operating at 4 MHz. OFF completely disables the ROM Wait circuitry.

# 2.1.6 BANK ENABLE JUMPER

jumper allows you three options in using the The BANK EN bank-select system to enable the board. Position ON makes the bank-select system fully operable, so that to enable the board, you must software-select the bank this board resides in by outputting the correct data byte to port 40h. Postion RST disqualifies the bank-select system on system power-on and reset, allowing the board to be enabled after you turn on or reset your system without its bank software-selected first. being Otherwise, the bank-select system functions as usual. Position completely disgualifies the bank-select system, permanently OFF enabling the board. Note that in the last two cases, the Bank LED will be lit when the board is enabled through disgualifying the bank-select system. If you are using the version of CP/M supplied by CCS, set BANK EN to RST or OFF, since the board must be enabled on reset. If you are operating with one disk controller in your system, the OFF position is probably the wiser choice since it eliminates the possibility of accidently disabling the board.

# 2.1.7 BOOT ENABLE JUMPER

The BOOT EN jumper allows you to choose between three methods of enabling/disabling the bootstrap loader and monitor firmware. If you set the BOOT EN jumper to OFF, neither the bootstrap loader or the monitor firmware can be accessed. If you have set the PR EN jumper to OFF, the entire ROM will then be disabled. If you set the BOOT EN jump to position A, the

bootstrap loader and monitor are enabled when your system is turned on or reset and disabled when any data byte is output to port 40h. Because port 40h is the Bank Select Port as well, you must also have the BANK EN jumper set to RST or OFF so that the board is enabled on reset or power on. If you are planning to use the CCS version of CP/M supplied with your board, set the BOOT EN jumper to position A. This allows the bootstrap loader and monitor to be disabled automatically when CP/M is loaded. Position B of the BOOT EN jumper allows the bootstrap loader and monitor to be enabled/disabled entirely through software control. Writing a 0 to bit 1 of Control Register 2 enables them; a 1 disables them.

# 2.1.8 Auto Boot Enable Jumper

If you are using the ROM-resident firmware, this jumper allows you to choose whether or not CP/M will be loaded or the monitor entered on power-on and reset. If you set this jumper to OFF, the monitor will be entered on power-on and reset. CP/M can then be loaded in under monitor control by use of the Boot command. For those who plan to use the 2422 in a system with a 2810 Z-80 CPU and wish to use the initialization firmware provided for the on-board port, the AUTO BOOT jumper should be set to OFF. This allows you to synchronize the baud rate of the 2810's port to the baud rate of your console device by hitting the carriage return key two to three times. This brings up the monitor, allowing CP/M to be booted in at will. If you set the AUTO BOOT jumper to ON, CP/M will be booted in on power-on and reset. Since only the bootstrap loader portion of the ROM will be accessed, this setting frees the user of the constraint of using the 2422 in a system with a 2810 Z-80 CPU. However, the user must then provide his own console initialization routine in the BIOS.

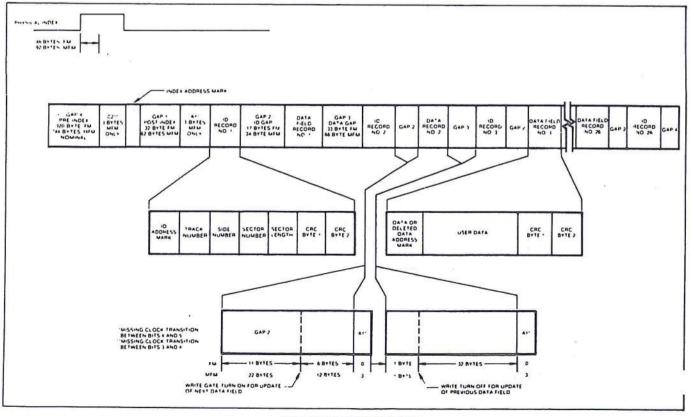

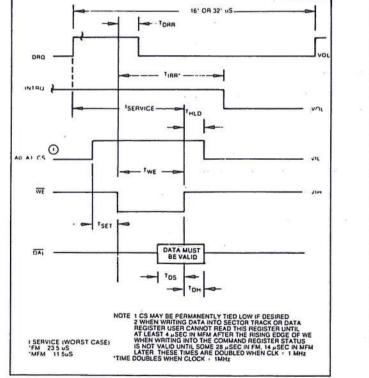

# 2.1.9 Auto Wait Select Jumper

The disk drive cannot read or write data on the disk as fast as the CPU can send or receive data. Thus there are times when the CPU must wait for the data register in the disk controller chip to become ready to receive a data byte from or transmit a data byte to the CPU. The state of the DRQ (Data Request) line from the 1793 indicates whether or not the data register is ready for data transfer. If it is low, the data register is not ready. If you set the AUTO WAIT jumper to DATA, you can force the CPU into a Wait state every time the CPU tries to read or

write to the data register when the DRQ line is low. By setting it to STAT1, you force the CPU into a Wait state every time it tries to read Board Status Register 1 when the DRQ line is low. In both cases, the CPU will remain in a Wait state until the DRQ line goes high again. Both forms of the Auto Wait are also enabled/ disabled through software control. Writing a 1 to bit 7 of Control Register 1 enables Auto Waits; a 0 to bit 7 disables them.

# 2.1.10 INTERRUPT JUMPERS

The interrupt jumpers allow you to tie DRQ and/or INTRQ to either the Interrupt line, pINT, the Nonmaskable Interrupt line, NMI, or any of the 8 Vectored Interrupt lines, VIO-VI7. INTRQ, when active, indicates that a command has been completed and that the 1793 is awaiting a new command. DRQ, when active, indicates that the data buffer either has a byte to be read or is empty and requires a new byte to transmit, depending on the nature of the disk operation in progress. Either or both of these lines can be used to generate interrupts and thus request servicing from the processor. To generate a Vectored Interrupt 2 by the active INTRQ, for example, run a bus wire from the INTRQ pad to the VI2 pad and solder it in.

# 2.2 SYSTEM SETUP FOR FIRMWARE COMPATIBILITY

In order for the bootstrap loader and monitor firmware to work as described in Chapter 3, you must have a power-on jump circuit somewhere in your Z-80 system set to force the CPU to jump to location F000h when you turn your system on or reset it. Any RAM sharing the ROM's memory space must be disabled while the firmware is being accessed. If your RAM board accepts the PHANTOM signal output by the 2422 when the ROM is selected, the RAM will automatically be disabled. On CCS memory boards, this entails jumper-enabling the PHANTOM signal. If your RAM board uses the same bank-select system as the 2422, you also can configure your board so that the memory block sharing memory space with the 2422 ROM is assigned to bank 0 and disabled on power-on or reset. When the Loader program from disk is loaded, it outputs a hex 01 to port 40h. This disables the bootstrap and monitor firmware as it enables the RAM. Please note that if you use this method you must have at least 256 bytes of low RAM memory enabled on reset; to be safe it would be wise to enable all RAM except that which directly conflicts with the ROM. For example, if you own CCS's Model 2065 64K Dynamic RAM board, you

would assign the board to bank 0 and configure it to be bank-disabled on reset, with the first three 16K blocks bank-independent and the last 16K block bank-dependent. Note that if you want the basic I/O portion of the ROM enabled after CP/M is loaded, you will have to use the PHANTOM line to disable the RAM sharing its memory space.

The monitor and basic I/O routines require some additional set up. They are designed to work in a system with a Model 2810 Z-80 CPU configured as follows: SER EN, JMP EN, and PHANTOM set ON and SER ADDRESS SELECT set to 20h. The 2/4 MHz switch should also be set to 4 MHz if you are planning to read or write doubledensity diskettes; the firmware design does not allow doubledensity diskettes to be read or written when the CPU is operating at 2 MHz. In addition, your terminal must be set as described in section 2.2.2 of the 2810 Owner's Manual to work with the console driver routines.

# 2.3 INSTALLATION

Because we can not anticipate what drive or drives you will be using the 2422 board with, we can not give specific installation instructions. However, there are some general instructions we can give. If you plan to use more than one drive, you must make sure that the common lines are terminated in the last drive on the cable only. This may mean removing jumper plugs or resistor packs: see your manual. You must also enable the appropriate Drive Select line to each drive, usually accomplished by moving a jumper plug. Some signals, such as TWO-SIDED, may also require some user-configuration to be enabled.

The cable assemblies needed to connect the 2422 with your drives are not not supplied with the 2422. For the 5.25" drives and the 8" drives you need 34 and 50 conducter flat-ribbon cables, respectively. The connectors you need are as follows:

Mating Connectors for the 2422:

5.25" drives (J1) = Ansley #609-3430 or equivalent 8" drives (J2) = Ansley #609-5030 or equivalent

Back Panel Connectors:

5.25" drives = Ansley #609-3416 or equivalent 8" drives = Ansley #609-5016 or equivalent

Mating Connectors to the Drive P. C. Board:

5.25" drives = Ansley #609-5015M or equivalent 8" drives = Ansley #609-3415M or equivalent

If you assemble your own cables, be sure that the pin 1 strip of the cable (usually marked by an outside colored stripe) matches pin 1 of all the connectors. Owners of Shugart, Memorex, and other bus-compatible drives can simply install the assembled cables and connect them, being careful to match pin 1s. Owners of the Per Sci drives will have to do some rewiring, since the Per Sci drive bus differs from the 2422. Section A.2.1 in Appendix A shows the pinouts for J1 and J2.

# CHAPTER 3

# THE 2422 ROM-RESIDENT FIRMWARE

# 3.1 COLD-START ENTRY

The firmware cold-start entry point is F000h. If you set a power-on jump circuit to this address, the CPU will jump to the cold-start entry point when your system is turned on or reset. The cold-start initialization routine loads the low RAM locations called to by the Z-80 restart commands with jump vectors to the It then finds the highest continuous restart error message. active RAM address and locates the monitor stack and work space Next it checks the state of the Auto Boot bit in the below it. board's Status Register 1; if the Auto boot bit is 0 the initialization routine passes control to the bootstrap loader, The monitor work which then loads in CP/M as described below. space is overwritten as CP/M is loaded in. If the Auto Boot bit is 1, the initialization routine continues, initializing the 2810 Z-80 CPU's serial port. When it has synchronized the serial port's baud rate to the console's baud rate, it turns control over to the monitor executive.

# 3.2 PAGE O RAM USED BY FIRMWARE

The following locations in page 0 of system memory are used by the the firmware. Except where noted, these locations should be reserved.

| Address                                                                                               | Contents                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000h-0002h                                                                                           | These locations contain the warm-start vector<br>for the monitor. When CP/M is loaded, they are<br>overwritten by the warm-start vector for CP/M.                                                                                                                                                                                                  |

| 0003h                                                                                                 | This location contains the Intel Standard IOBYTE loaded during cold-start initialization and used for monitor I/O (see section 3.5.2).                                                                                                                                                                                                             |

| 0008h-000Ah<br>0010h-0012h<br>0018h-001Ah<br>0020h-0022h<br>0028h-002Ah<br>0030h-0032h<br>0038h-003Ah | During cold-start initialization these locations<br>called by the Z-80 restart commands are loaded<br>with jump vectors to the restart error message<br>(see section 3.5.5.) They can be overwritten by<br>valid restart routines. In addition, locations<br>0008h-000Ah are used for software breakpoint<br>processing by the monitor GO command. |

| 0040h-0053h                                                                                           | These locations contain disk parameters used by<br>the bootstrap loader and the monitor. They are<br>described in more detail in section 3.3.1.<br>Locations 0040-004Fh are defined by CP/M as user<br>scratchpad locations; 0050-0053h are unused by<br>present versions of CP/M but are held reserved.                                           |

| 0080h-017Fh                                                                                           | Temporary buffer used by the bootstrap loader<br>and CP/M to store the Loader program from disk.                                                                                                                                                                                                                                                   |

# 3.3 THE FIRMWARE DISK ROUTINES

# 3.3.1 DISKETTE FORMAT

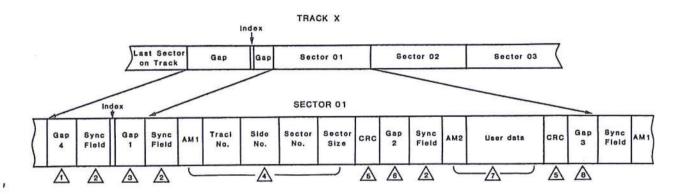

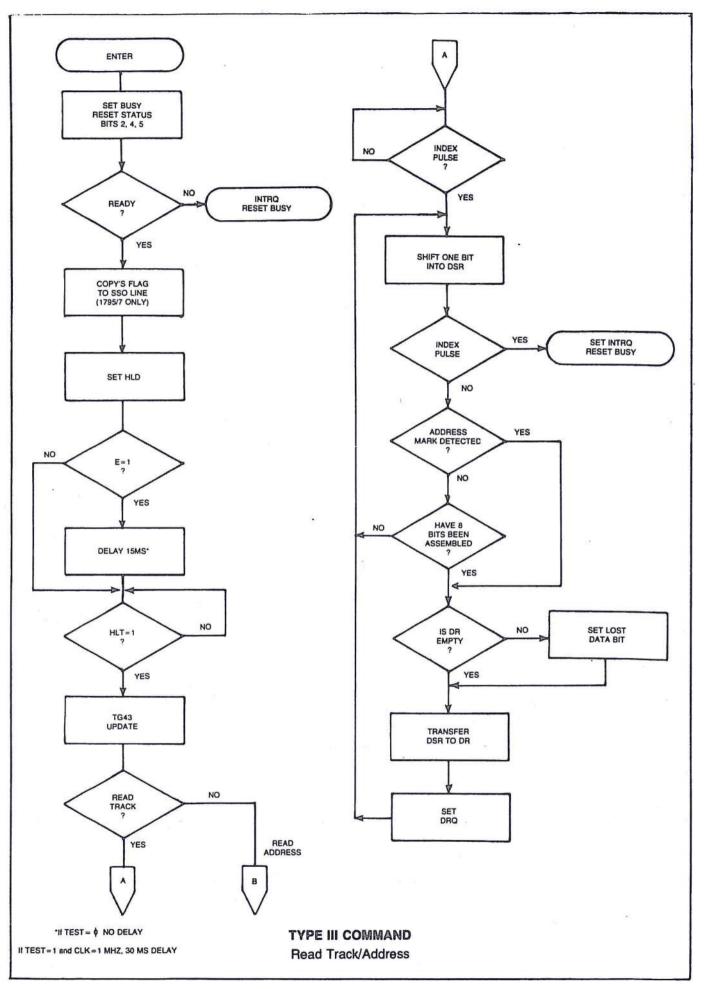

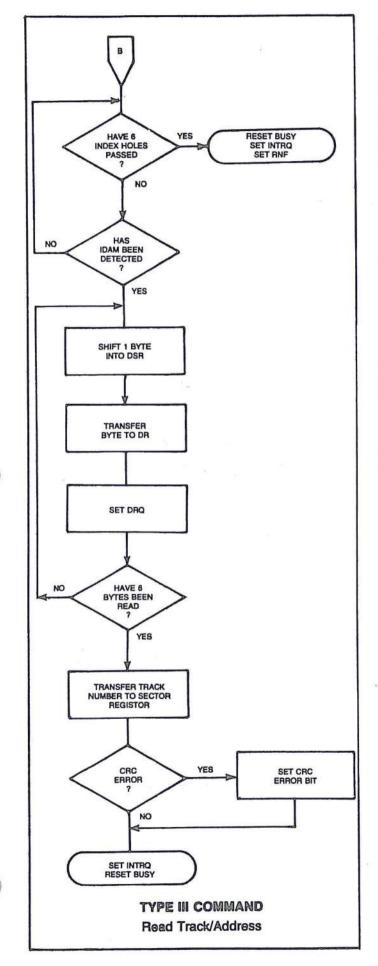

The primitive disk routines used by the monitor and the bootstrap loader are designed to read or write disks which conform to the IBM 3740 and System 34 standards for soft-sectored diskette format. Although strictly speaking these standard apply to 8" diskettes only, they can be adapted for 5.25" diskettes. Since the firmware routines are designed for diskettes conforming to the IBM format standards, it might be helpful if we discuss diskette format in general and the IBM standards in particular.

Track numbering on a diskette begins at its circumference with Track 00 and proceeds toward the center; thus the innermost

track on an 8" diskette with the standard 77 tracks is track 76. Each track on side 0 of a two-sided diskette has an associated track on side 1; these track-pairs are often called cylinders. Unlike track numbering, sector numbering starts with 1, the number given to the first sector immediately following the index pulse. The number of sectors on a track is dependent on disk size, data density, an number of bytes per sector.

The IBM 3740 standard for single-density diskettes allows sector sizes of 128, 256, and 512 bytes; the System 34 standard for double-density diskettes allow sectors sizes of 256, 512, and 1024 bytes. (The 1793 can format single-density diskettes in 1024-byte sectors and double-density diskettes in 128-byte sectors as well, but those additional sector sizes have no practical advantage.) Before each sector is an unique address or ID field specifying the track number, diskette side, sector number, and sector size. In addition, the ID fields and data fields must be separated by gaps and sync fields of a minimum length. Figure B-1 of Appendix B illustrates the IBM format standard for singledensity 8" diskettes. The 1793 adds an additional constraint to diskette format: it expects gaps to consist of FFh data bytes, followed by 00h. As a result it cannot read diskettes formatted by a 1771 disk controller chip. (The 1771 can, however, read disks formatted by the 1793.) The utility program COPY supplied by CCS with CP/M allows disks formatted by the 1771 to be reformatted so that the 1793 can read them.

# 3.3.2 THE PRIMITIVE DISK ROUTINES

The firmware contains two routines for sector reads and writes: DREAD and DWRITE. The bootstrap loader calls DREAD for reading the first two sectors of Track 00; the monitor Read and Write commands use both routines. DREAD and DWRITE both transfer sector at a time and automatically determine disk size, one sector size, and density format if the disk has not been accessed before. They conform to the CP/M calling conventions and return a 0 in the A register if the disk operation was successful and a non-zero if it was not successful after ten tries. Both routines reside in the upper 1/2K of ROM which can remain enabled after CP/M is loaded in. Thus they can be called to from a user's BIOS. The entry point for DREAD is F6EAh; for DWRITE, F6EBh.

# 3.3.3 DISK PARAMETERS FOR DISK OPERATIONS

DREAD and DWRITE use locations 0040h-0053h to store the disk parameters they need. Below are the definitions and addresses of some of the more useful disk parameters:

| Address         | Name   | Description                                                                                                        |

|-----------------|--------|--------------------------------------------------------------------------------------------------------------------|

| 0040h           | DISKNO | Stores the number of the currently-<br>selected drive: 0, 1, 2, or 3.                                              |

| 0041h           | TRACK  | Stores the number of the current track.                                                                            |

| 0042h           | SECTOR | Stores the number of the current sector.                                                                           |

| 0043h           | SIDE   | Stores the byte written to Control<br>Register 2 to select disk side. (90h =<br>side 0; D0h = side 1)              |

| 0045h           | TWOSID | Stores 0 if the disk in the currently-<br>selected drive is one-sided; 1 if it is<br>two-sided.                    |

| 004Ah           | CUNIT  | Stores the byte last written to Control<br>Register 1, giving information on the<br>currently-selected drive unit. |

| 004Ch           | HSTBUF | Stores the starting address in memory<br>for disk transfers to and from memory.                                    |

| 004Eh-<br>0053h | IDSV   | Stores the ID field information from a sector in the currently-selected drive.                                     |

# 3.4 THE BOOTSTRAP LOADER

The bootstrap loader, when entered at F55Eh, reads in at locations 80h through 17Fh the contents of the first two sectors of track 00, side 0 of the disk in drive A and then transfers control to them. The sectors must contain a Loader program for loading CP/M into memory and transferring control to it. In addition, Track 00 of this disk must be formatted in 128-byte single-density sectors. If the bootstrap loader encounters an error, it jumps to the Disk Error routine in the monitor portion of the ROM. If you were booting CP/M in from the monitor so that the 2810 CPU's serial port had been initialized, you will receive the Disk Error message as described in section 3.5.5 and control will be returned to the monitor. If you were booting in CP/M directly on system power-on or reset, your system will "hang." When it is finished reading in the Loader program, the bootstrap loader leaves some disk parameters in memory:

DISKNO=0 SIDE=0 TRACK=00 SECTOR=3 CUNIT=21 for a single-density 5.25" diskette 31 for a single-density 8" diskette 61 for a double-density 5.25" diskette 71 for a double-density 8" diskette IDSV + 3=00 if diskette sector size is 128 01 if diskette sector size is 256 02 if diskette sector size is 512 03 if diskette sector size is 1024

After it is loaded, the Loader program in the disk supplied by CCS outputs hex 01 to port 40h. If the BOOT EN jumper has been set to postion A, this simultaneously disables the bootstrap and monitor firmware and enables any RAM assigned to bank 0 and with a bank select port of 40h.

# 3.5 THE MONITOR

CCS's MOSS 2.2 Disk Monitor is designed to allow you to control a system using a 2810 Z-80 CPU from the console keyboard. It allows you to display a block of memory in hex and ASCII, to move, change, and verify memory, and to transfer control to another program in memory with breakpoints set. You can also output or input a data byte to or from any I/O port and command the monitor to read and write floppy disks.

For the MOSS 2.2 Monitor to work exactly as described below, your 2422 Disk Controller board and 2810 Z-80 CPU must be configured as described in sections 2.1 and 2.2.

# 3.5.1 THE MONITOR'S MEMORY SPACE

In addition to the memory the ROM occupies and the page 0 addresses specified in section 3.2, the monitor requires some high RAM locations for the system stack and temporary storage area. The monitor scans the available memory until it finds the highest active RAM address and then counts down 56 bytes to store the breakpoints, registers, and register restore routine. It locates the system stack below that: you should reserve at least 88 bytes of high RAM memory for the monitor's use.

# 3.5.2 THE IOBYTE AND THE BASIC I/O ROUTINES

The monitor's basic I/O routines are essentially the same as those used by CCBIOS. They are designed for a system using CCS's 2810 Z-80 CPU, configured as described in section 2.2. As with the primitive disk routines, they reside in the last 1/2K of the ROM, allowing them to be available after CP/M is loaded, should you wish them to be. Section 3.5.2.3 below contains information tailoring this portion of the ROM to fit your system's needs, on if your are using a system with a different CPU or wish to provide driver routines for other peripherals. Please note that the method of initializing the console interface's baud rate described in the sections on bringing up the monitor and in the Y command is highly dependent on the hardware configuration of the 2810's serial port. the description on the monitor's Thus operation in these sections will probably not be valid if you alter the firmware to work with a different console interface.

# 3.5.2.1 The IOBYTE

The basic I/O routines in this portion of the ROM implement IOBYTE function, as developed in the Intel MDS system and as the used by CP/M. The IOBYTE function allows the user to assign а physical device to one or more of four logical I/O categories: Console, List, Punch, and Reader. The current physical to logical device assignments are stored in the IOBYTE at location 0003h. The IOBYTE can be altered through the MOSS monitor Assign command or the CP/M STAT command. When an I/O routine, such as Console Input, is called, the routine loads the IOBYTE, using it to determine the currently assigned physical device, and then jumps to the driver routine called by the physical device assignment. For the allowable physical assignments in each logical category, see the Assign Command, section 3.5.4.1. In each logical category, the firmware provides only the Teletype assignment with driver routines. These routines are designed to drive the serial port on the 2810 CPU. Please note that the physical assignment names do not have to accurately describe the actual peripheral used; the actual physical device driven by the teletype assignment routines could easily be a CRT. For all physical device assignments other than the teletype, the I/O routines jump to location F462h, the location of the monitor I/O error message, resulting in the I/O Error message being displayed and control returned to the monitor as described in section 3.5.5.

# 3.5.2.2 The Basic I/O Routines

The user may call the following basic I/O routines from his own programs while in the monitor or from his own customized BIOS if the PR EN jumper is set ON.

| Name   | Address | Description                                                                               |

|--------|---------|-------------------------------------------------------------------------------------------|

|        |         |                                                                                           |

| CI     | F646    | Console Input                                                                             |

| *CONI  | F68F    | Console Input, strips ASCII parity bit                                                    |

| *CO    | F600    | Console Output                                                                            |

| *CSTS  | F623    | Console Status Input                                                                      |

| *LO    | F610    | List Output                                                                               |

| *LSTAT | F669    | List Status Input                                                                         |

| *RI    | F656    | Paper Tape Reader Input                                                                   |

| *PO    | F67C    | Papar Tape Punch Output                                                                   |

| PRTWA  | F698    | Prints ASCII string on console. String must be terminated by bit 7 set in last character. |

| PRTWD  | F695    | Same as above, only does carriage return, line feed first                                 |

| CRLF   | F6A9    | Generates carriage return, line feed sequence to start new line on console                |

The starred routines are CP/M compatible routines, basically the the same as the following routines used in the CCBIOS: CONIN, CONOUT, CONST, LIST, LISTST, READER, and PUNCH. They perform the basic IOBYTE handling as described above. Again, actual driver routines exist only for the teletype assignment for each logical category. These driver routines conform to the CP/M calling conventions, passing the data in the C register for any output and in the A register for any input. PRTWA, PRTWD, and CRLF are not routines used by a CP/M BIOS, however they are useful routines which are available as long as the Basic I/O portion of the ROM is accessible. CI is an alternative console input routine which does not strip the parity bit.

# 3.5.2.3 Customizing the Basic I/O Routines

As mentioned before, the monitor's basic I/O routines are designed to drive the console interface on the 2810 Z-80 CPU. Should you wish to add drivers for other peripheral devices or to use another console interface, you will have to alter the ROM firmware. There are two ways to do so. You can reprogram the ROM so that the jump instruction associated with a particular physical device assignment forces the CPU to jump to your peripheral's driver routine. For example, to add a line printer to your system, you would change the jump instructions at locations F61D and F676 so that they contained the beginning

address of your printer driver routines. Or you can, if you have CCS's 2810 Z-80 CPU and peripheral cards, use memory overlay techniques. Since the 2422 board generates, but does not receive, the PHANTOM signal, its ROM has to be moved to the CPU board. There the jump vectors called by the physical assignments can be overlaid with new jump vectors by the peripheral board's ROM.

# 3.5.3 BRINGING UP THE MONITOR

To enter the monitor, turn your system on or reset it. This results automatically in a cold-start entry into the monitor. Set your terminal to the baud rate at which you wish to operate. You have a choice of any baud rate between 2 and 56K baud. To allow the 2810 CPU's serial port to be initialized to the baud rate, hit the carriage return key until the monitor responds with

# MOSS VERS 2.2

The maximum number of carriage returns needed before the monitor responds is three. When the monitor prompt appears, you may start entering commands.

# 3.5.4 MONITOR COMMANDS

The MOSS Monitor commands must conform to a specific format. The general form is

# -CE1 E2 E3

where - is the prompt, C is the command character and El-E3 are the address and data entries, if any. The essential parts of a command are as follows:

THE COMMAND CHARACTER: The monitor is controlled by one-character commands entered from the keyboard in response to the monitor prompt, a dash (-). No space is allowed between the prompt and the command character.

ADDRESS AND DATA ENTRIES: The general form for an address is a four digit hex number; for data, a two digit hex number. Leading zeros need not be entered; the monitor will supply them. No space is allowed between the command character and the first address or data entry. Subsequent entries must be separated by a delimiter. The monitor looks at only the last four address

characters or last two data characters before a delimiter. So if you make a mistake while typing an entry, keep typing until the last two or four characters are correct.

DELIMITERS: The MOSS Monitor recognizes three delimiters: a carriage return [CR], a space, or a comma. A carriage return indicates to the monitor that the current command is complete and should be executed. Either a space or a comma can mark the end of an address or data entry. In our command examples we will generally use a space as a delimiter, unless a comma makes the command form clearer. Please note, however, that you can use the space and the comma interchangeably. In certain commands a space or a comma can also be interchanged with a carriage return. These are commands for which the Monitor expects a fixed number of entries (and hence delimiters) following the command character.

#### SAMPLE COMMAND

The following commands to display the block of memory OFFBh to 100Ah are all equivalent. Although the spacing is not free-form, some variety in the command form is allowed. Note that the display command requires two and only two address parameters, so that the last delimiter can be a comma or a space as well as a carriage return.

> -DOFFB 100A[CR] -DFFB,100A, -DFFB,100A[CR] -DFFB 100A[space] -D0EF0FFB,100A[space]

# 3.5.5 ERROR MESSAGES

The MOSS monitor detects four types of error conditions and responds with a different error message for each. They are as follows:

COMMAND ERROR: Should you make an invalid entry, the command will be aborted, a warm boot of the system will occur, and the error message

# ????

will be printed, followed by the monitor prompt.

I/O ASSIGNMENT ERROR: As described in section 3.3, the Assign command allows you to assign a physical device to a logical peripheral category. When an I/O routine involving the logical category is called, the CPU will jump to the driver routine indicated by the physical assignment. If there is no driver routine, it will jump instead to the I/O Assignment Error routine. This routine sets the IOBYTE to its default value, outputs the error message

# I/O ERR

and does a warm boot of the system.

RESTART ERROR: During cold-start initialization, jump-vectors to a restart error message are loaded in the memory locations called by the Z-80 restart instructions. This is done to prevent a jump to a restart address without code. A restart error causes the message

#### RST ERR

to be displayed and a warm boot of the system to occur.

DISK ERROR: The monitor, when executing the Read, Write, or Boot commands, will output the following error message and status information if it is unable to execute the command:

# DSK ERR U XX T XX S XX C XX E XX

The first three hex bytes identify which physical record the monitor was unable to read or write. U gives the unit or drive number (0-3), T the track number and S the sector number of the record where the error occured. C and E give the operation status at the time of the error. They reflect the contents of two of the 1793's internal registers: C shows the last command loaded in the Command register; E gives the contents of the Status register.

#### 3.5.6 COMMAND DESCRIPTION

# 3.5.6.1 Assign (A)

you The Assign command allows to change the physical-to-logical device assignments and thus choose the peripherals you wish to work with while in the monitor. The IOBYTE function as developed by Intel for the MDS systems divides peripherals into four logical categories: Console, typically a teletype or a CRT; Reader, a paper tape reading device; Punch, a paper tape punching device; and List, a hard-copy printing device. Each of the four logical categories may have one of four devices assigned to them. The possible physical physical-to-logical assignments are as follows:

- (C) Console

- (T) Teletype

- (C) CRT

- B) Batch Mode (input from logical reader device; output to logical list device)

- (1) User Console #1

- (R) Reader

- (T) Teletype

- (P) Paper tape reader

- (1) User reader #1

- (2) User reader #2

- (P) Punch

- (T) Teletype

- (P) High speed paper tape punch

- (1) User punch #1

- (2) User punch #2

- (L) List

- (T) Teletype

- (L) High speed line printer (CRT in CP/M)

- (1) User list #1 (High speed line printer in CP/M)

- (2) User list #2 (User list # 1 in CP/M)

To assign a physical device to a logical device category, enter

-AX

where X equals either C,R,P, or L, the logical device codes. If you enter a character other than these four, the computer will return with ???? and another prompt. If you enter a valid logical device code, the computer will return immediately with a prompt for the physical device code. Enter

-Y

where Y equals the physical device code. Should you enter a delimiter only or a nonvalid device code, the device assignment will remain the same.

EXAMPLE:

Entering

#### -AR-P

assigns a high speed paper tape reader to the Reader logical device category.

Since the firmware contains driver routines only for the teletype assignment, you should receive the I/O error message if you attempt I/O operations with any other physical device without having altered the firmware first.

3.5.6.2 Boot (B)

The Boot command allows you to load in CP/M from disk under console control. Entering

-B

causes the bootstrap loader to load CP/M in from the disk in drive A and control to be transferred from the monitor to CP/M. When CP/M is loaded, the CP/M sign on message will appear, followed by the CP/M prompt. Should the bootstrap loader be unable to read in the first two sectors on Track 00, it will respond with the Disk Error message.

3.5.6.3 Display (D)

This command allows you to display the contents of a specified block of memory. The general form for the command is

# -DA1 A2

where Al and A2 are the first and last bytes, respectively, of the memory block.

The resulting display divides the memory into 16 bytes per line. Each line begins with the starting address of the 16 byte block, followed by the hex contents and their ASCII equivalents. The contents of addresses with the same last hex digit are aligned in vertical columns. Periods represent data for which there are no ASCII equivalents. As the display fills the screen, it automatically scrolls up. To freeze the display, type a control-S. To start it again, hit any key on the keyboard. Should you wish to escape from the display mode, hitting any key on the keyboard will abort the routine and return control to the monitor.

#### EXAMPLE

Entering

# DF453 F4C8

# results in the following display:

E1 00 00 AF 32 45 52 D2 44 AD 20 53 AD 4D 4F 53 53 OF D3 24 11 A3 A3 C2 AD 7D B4 C2 BD E1 F9 C3 B5 52 3A AD 32 20 32 26 A3 19 E5 00 00 C3 2F 4F 20 AD 20 54 3F 3F BF 0D 8A 3E DB 26 2B DB 20 2B 83300044 5224 FF 90836051 04450EE 0600AE89 D20D529E 2455F2B9 ERRDSK ERR: E-. - S-MOSS .S\$.@.bj[&# ##B-te)\..e) }4B=ta>.S F4CO

# 3.5.6.4 Fill (F)

The fill command allows you to fill a block of memory with a specified constant. The general command form is

# -FA1 A2 C

where Al and A2 are the addresses of the first and last bytes of the memory block and C is the constant in hexidecimal.

# EXAMPLE

Entering

# -F10AA 10BB 1

fills the memory block 10AAh to 10BBh with the constant 1.

3-14

# 3.5.6.5 Goto (G)

The G command allows you to transfer control from the monitor to another program. It allows you to specify the entry address and to set up to two breakpoints for returning control to the monitor. When the monitor encounters a breakpoint, it saves the contents of the Z-80 registers in the system's temporary storage and outputs to the console device an asterisk followed by the address after the break. It then returns the prompt. You can use the Examine Register command (X) at this time to examine or change the saved registers.

The general form for the G command is

-GA B1 B2

where A is the entry address, and Bl and B2 are the addresses of the breakpoints. There are many allowed variations on this command, however, which makes it a powerful and convenient command. You have the option of establishing 0, 1, or 2 breakpoints: simply enter a [CR] when you have established the number of breakpoints you wish. If you enter the maximum, two, a delimiter (a comma or space) is all that is necessary to begin command execution.

You may also begin execution of the program at the PC address saved in the register storage area. Thus you can return control to the address where the program stopped when it encountered a breakpoint, or to the address you have loaded in the saved PC register through the Examine Register command. Note that since all breakpoints are cleared when any breakpoint is encountered, you must specify any desired breakpoints in the command if you use it this way. The form of the command for transferring program control to the address in the PC register is

> -G[CR] (no breakpoints) or -G,Bl,B2 (breakpoints set)

There are two more points regarding breakpoints that ought to be mentioned. Because breakpoints are generated by the monitor inserting a RST 8 instruction (CF) into the program at the breakpoint location, breakpoints can be set only in programs residing in RAM. Further, a breakpoint must be inserted at an op code location. If it is inserted in an operand or data field, it will not be executed.

# 3.5.6.6 Hex Number Addition (H)

This command provides an easy way to add or subtract hex addresses. Entering

# -HA1 A2

where Al and A2 are the hex addresses results in the output

# AS AD

where AS=Al+A2 and AD=Al-A2. Note that if the sum is greater than FFFF, the carried one is lost. If A2 is greater than Al, A2 will be subtracted from Al + 10000h.

3.5.6.7 Input (I)

This general purpose input command allows you to read a data byte from any input port. To do so, enter

-IA

where A is the port address in hex. The monitor will respond by printing the data byte in binary.

3.5.6.8 Move (M)

The M command moves a block of data to a specified address. The general form for the command is

# -MA1 A2 AD

where Al and A2 are the addresses of the first and last bytes of the memory block and AD is the destination address.

When using this command, be careful not to locate the destination address within the source block. Since the block is moved byte by byte, starting with the byte with the lowest address, the data being transferred will write over the original contents of the section of the source block that follows the destination address.

# 3.5.6.9 Output (O)

This general purpose output command allows you to output a data byte to any output port. Enter

-OA D

where A is the port address and D is the data in hex.

Please note that if the BOOT EN jumper is set to position A and you output to port 40h, you will disable the monitor portion of the ROM. The results of doing so are unpredictable.

# 3.5.6.10 Parameters (P)

The P command allows you to specify three parameters concerning the diskette selected for disk operations: the number of the unit it is in (U); the number of sectors it has per track; (S); and whether it is a one-sided or two-sided diskette. These parameters must be set before you attempt a disk read or write; however, they do not need to be reset until the parameters are no longer valid. The form of the command is:

# -PU S D

U is a number 0 through 3, where 0 selects drive A, 1 selects drive B, etc. If you try to assign a number greater than 3, the monitor will return with ???? and the prompt. S is the number of sectors per track in hex. It is dependent on the number of bytes per sector, the diskette size and the density format. The following table shows the allowable number of sectors per track for a diskette of a given size and format:

| BYTES  | 8" DISI        | KETTES         | 5.25" DISKETTES |                |

|--------|----------------|----------------|-----------------|----------------|

| SECTOR | SINGLE-DENSITY | DOUBLE-DENSITY | SINGLE-DENSITY  | DOUBLE-DENSITY |

| .128   | 1Ah (26d)      |                | 12h (18d)       |                |

| 256    | Fh (15d)       | 1Ah (26d)      | Ah (10d)        | 12h (18d)      |

| 512    | 8h             | Fh (15d)       | 5               | Ah (10d)       |

| 1024   |                | 8              |                 | 5              |

Note the firmware does not support 1024-byte sectors in double-density and 128-bytes in double-density. The last parameter, D, is 0 for a one-sided diskette; 1 for a two-sided diskette.

# 3.5.6.11 Parameters 2 (Q)

The Q command allows you to set the starting track, side, and sector number for disk reads or writes. Enter

# -QT D S

where T is the beginning track number, D is the disk side, and S is the beginning sector number. If you plan to be transferring contiguous data to or from the disk, these parameters need to be set only prior to the first disk access. They must be reset for noncontiguous memory or sectors. T is the track number in hexidecimal. In practice, T will probably be a number between 0 and 4Ch (76d), inclusive, although the monitor will accept any value up to FFh. D is either a 0 or 1, depending on which side of the disk you wish the read or write to be performed on. S is the sector number in hexidecimal. It will always be a number between 1 and 1Ah, inclusive. Should you assign a track number or sector number greater than the number of tracks or sectors on the disk, you will get the Disk Error message when you use the Read or Write commands.

# 3.5.6.12 Read (R)

The R command allows you to transfer data from a disk into a specified area of memory. The R command sets the memory parameters; the disk parameters must have already been set by the P and Q commands. Enter

# -RA1 A2

where Al is the start address in memory and A2 is the end The R command does only complete sector transfers. address. Thus if the end address is reached before a sector is completely transferred into memory, the data will overflow the specified memory area. If the diskette is single-sided and the last sector in a track is reached before the read into memory is complete, the drive head steps, in to the next track and the sector pointer is reset to 1. The number of sectors per track set by the P command determines whether or not the end of the track is In the case of track overflow on side 0 of а reached. double-sided diskette, the read continues on the same track on

side 1. A track overflow on side 1 causes the head to step in and read the next track on side 0.

Please remember that reading double-density diskettes requires a 4 MHz CPU.

# 3.5.6.13 Substitute (S)

The substitute command allows you to examine the contents of a specific memory location and alter them if you desire. Begin the S command by entering

-SA,

where A is the address of the memory location you wish to examine. The computer will immediately respond with the data contents followed by a prompt:

# -SA,D-

If you wish to leave the data unaltered, simply enter a delimiter. If the delimiter is a space or a comma, the computer will respond with the contents of the next consecutive memory location and another prompt. If it is a carriage return, the command is terminated and control is returned to the monitor. Should you wish to alter the data, enter the desired data followed by a delimiter: a carriage return if you want to terminate the command or a space or a comma if you wish to review the next memory location. You also have the option of reviewing the previous memory location by hitting the line feed key. You can continue examining and altering memory byte by byte in this way as long as you wish. To make it easier for you to keep track of where you are, on every 8-byte boundary (that is, an address ending with either 0 or 8, the monitor will do a line feed and print the address along with the data.

# 3.5.6.14 Test (T)

The test command provides a quick way to test RAM memory for hard data bit failures without destroying the contents of the RAM. To test a block of memory for bit failures, enter

# -TA1 A2

where Al and A2 are the addresses of the first and last bytes in the block, respectively. The monitor will respond by printing the address of any byte in error, followed by an 8-bit

representation of the byte in which a one indicates an erroneous bit. For example, should bit 4 of location A3F8h be in error, the monitor outputs the following display

# A3F8 00001000

If you wish to freeze the display type a Control-S. To start it again, hit any key. Hitting any key while the command is executing returns you to the monitor.

#### 3.5.6.15 Verify (V) -

You can use the V command to compare two blocks of memory and verify that they are the same. Type

# -VAl A2 AV

where Al and A2 are the addresses of the first and last byte in the source block and AV is the starting address of the block to be verified. Should the two blocks match, the monitor will return with the prompt. Should the contents of two bytes sharing the same relative address differ, the monitor will display the source address and byte, followed by a dash and the corresponding byte in the block being verified. During the execution of the command, the display can be frozen or control returned to the monitor as described in previous section.

### 3.5.6.16 Write (W) -

The W command allows you to transfer a specified block of memory to a disk. The W command sets the memory parameters; the disk parameters must have been already set by the P and Q commands. (Mind your P's and Q's before doing Reads and Writes). Enter

# -WA1 A2

where Al is the start address of the memory block and A2 is the end address. The write routine checks to see if the end address in memory has been reached only after it has completed a sector write. If the end address is reached before a sector write is completed, the routine will continue to pull data from memory until the sector is filled. During disk writes, track overflow is handled as described in the Read command. Please note the writing of double-density diskettes requires a 4 MHz CPU.

# 3.5.6.17 Examine (X)

The X command is a very useful command when used in conjunction with the G command's breakpoint facilities. Entering

-X[CR, space or comma]

causes the Z-80 registers currently stored in the system stack area to be displayed for examination. These registers are the main and alternate accumulator and general purpose registers, the Interrupt register (I), the Program Counter register (P), the Stack Pointer register (S), the two Index Registers (X and Y) and the Refresh register (R). In addition, the contents of the memory locations addressed by the main and alternate H and L registers are also displayed (M and M'). The registers are displayed in the following four-row format

> A-xx B-xx C-xx D-xx E-xx F-xx H-xx L-xx M-xx P-xxxx S-xxxx I-xx A'-xx B'-xx C'-xx D'-xx E'-xx F'-xx H'-xx L'-xx M'-xx X-xxxx Y-xxxx R-xx

where xx equals a two digit hex byte and xxxx equals a four digit hex address.

To examine or alter the contents of one register, enter

-Xr[CR, space or comma] or -X'r[CR, space or comma]

where r is a main register and r' is an alternate register. (Note that if you wish to examine the X, Y, or R registers, you must preface the register character with the prime mark.) The monitor will return with the contents of the register and a prompt:

#### -Xr,Dh-

As in the substitute memory command, you have the option of altering the memory (entering the desired contents followed by a delimiter) or leaving the contents unchanged (entering a delimiter). A carriage return terminates the command; a space or a comma causes the contents of the next register to be displayed. Note that altering the contents of the H and L registers changes the contents of the registers themselves; if you wish to alter the contents of the memory location pointed to by them, alter the M register.

# 3.5.6.18 Initialize Baud Rate (Y)

To change the baud rate of your system without a system reset, use the Y command. Enter

# -Y (no delimiter)

and then set the baud rate of your terminal to any baud rate between 2 and 56K baud. Hit the carriage return key until the monitor returns with the prompt. The maximum number of carriage returns required is three.

3.5.6.19 Zleep (Z)

You can use the Z command to prevent unauthorized use of your system. Entering

# -Z (no delimiter)

locks up the system so it will not respond to anything other than the ASCII bell character (control G). Entering two consecutive bell characters will unlock the system, returning control to the monitor without altering anything.

# CHAPTER 4

# THEORY OF OPERATION

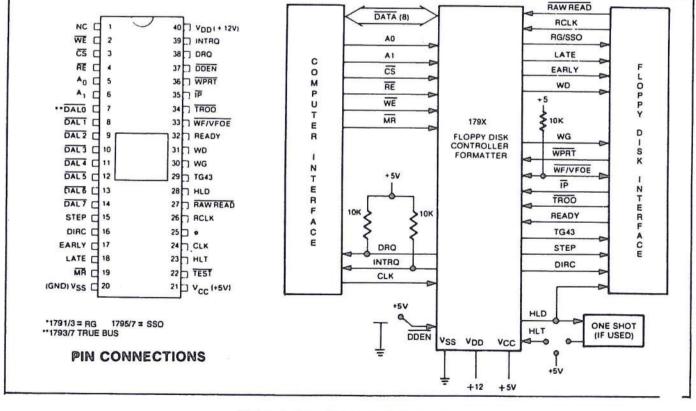

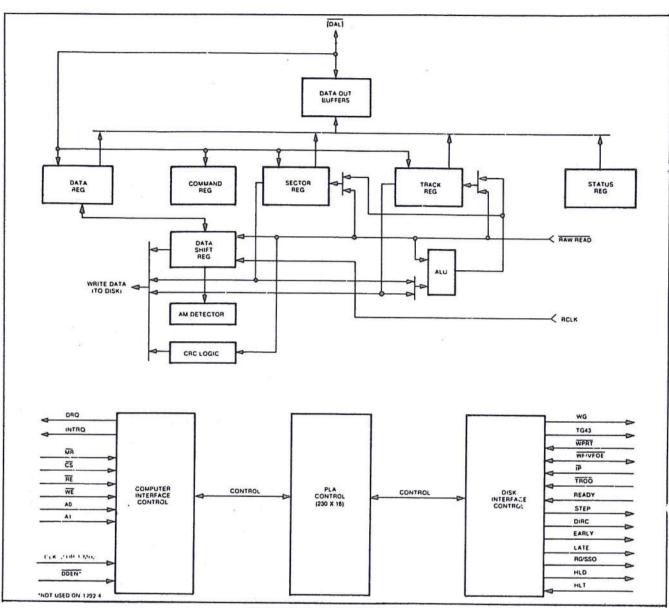

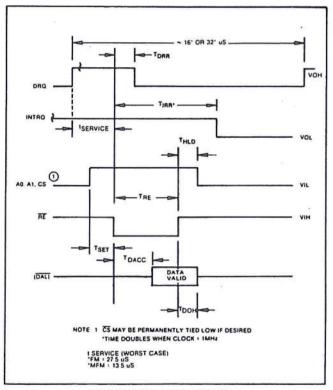

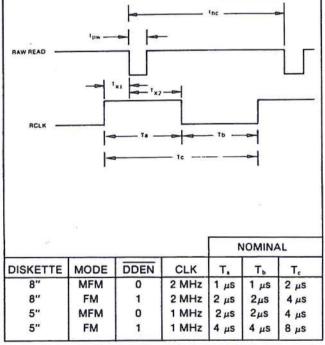

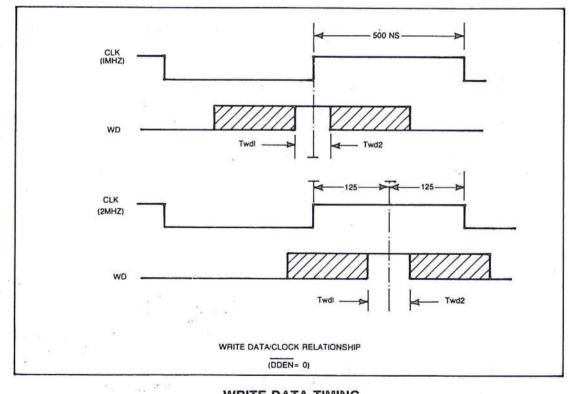

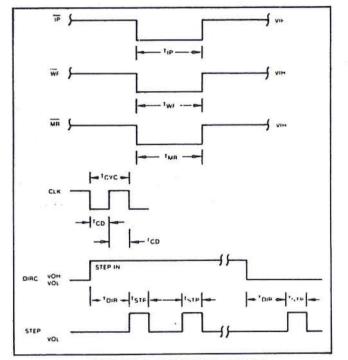

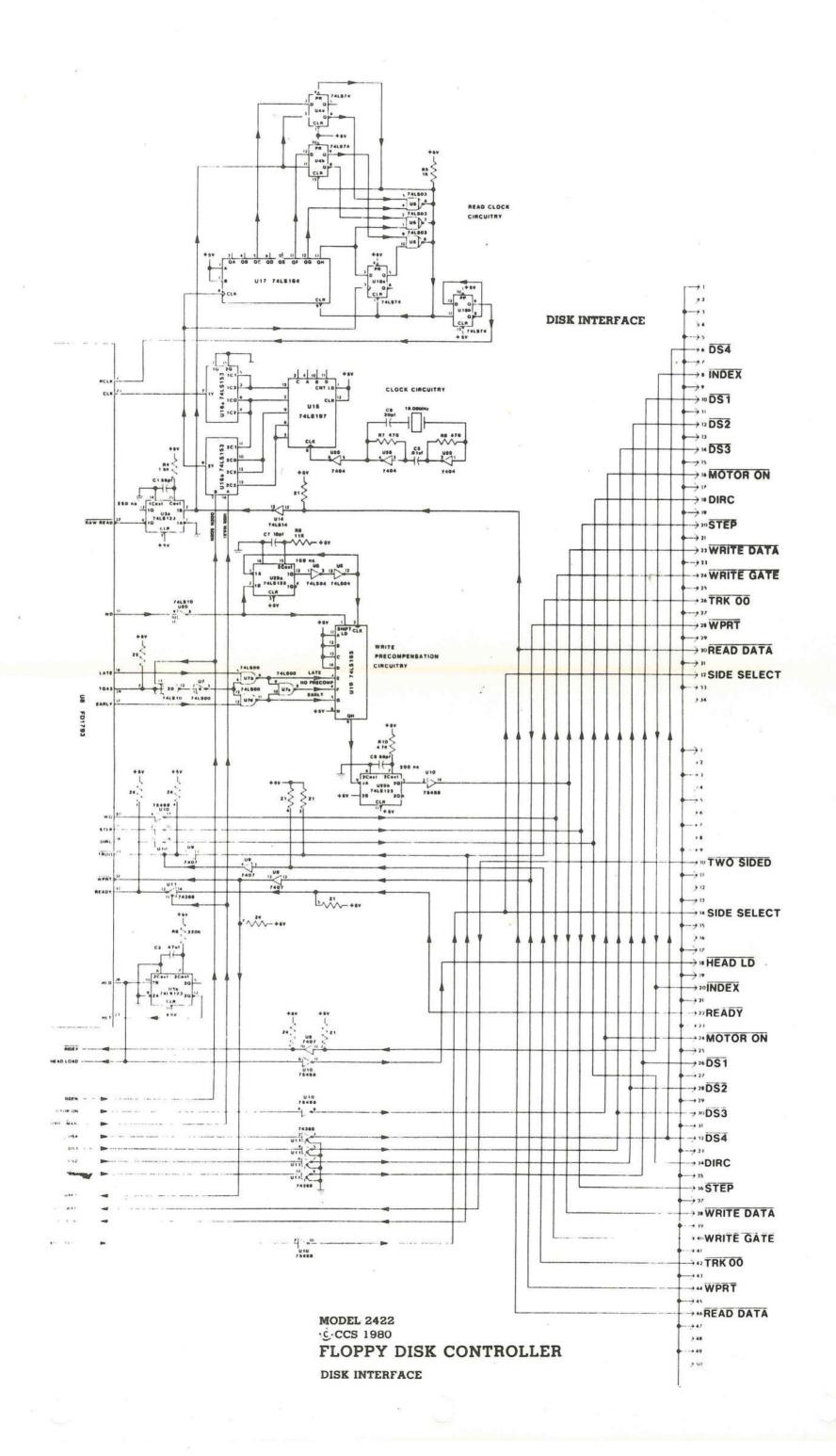

This chapter is organized into three parts: The 2422 program accessible registers, the system bus interface, and the disk drive interface. We do not discuss the operation of the 1793; such a discussion is beyond the scope of this manual. Instead we concentrate on our unique circuitry external to the 1793. We have, however, included its data sheet in Appendix C for those of you who need information on its operation. If you consult it, please keep in mind that the data sheet covers the entire 1790 family; certain portions may not be applicable to the 1793.

In this chapter, active-low signals are indicated with an asterisk following the signal name.

# 4.1 THE REGISTERS

The 1793 contains five addressable registers: the Command register (write only), the Status register (read only), the Track register, the Sector register, and the Data register. On the 2422, these registers are addressed as four I/O ports, 30-33h, the Command and Status registers sharing the same address. Programming information on these registers can be found in the 1793 data sheet in Appendix C. In addition, the 2422 contains four registers external to the 1793: Status registers 1 and 2 (read only) and Control registers 1 and 2 (write only). These registers are addressed as two I/O ports, 34h and 04h, the status registers being selected during Read cycles and the control registers during Write cycles. The status registers consist of two 8-bit buffers, U25 and U26. When enabled by being addressed during a Read cycle, these chips gate selected signals from the drive busses, the system bus, and the control registers onto the data, bus to be read by the CPU. Control registers 1 and 2, when

# THEORY OF OPERATION

addressed during a write cycle, latch the command bits on the data bus and output high or low signals to the disk drive busses, the CPU and drive interface circuitry, and the 1793. They are cleared by pRESET\* or EXT CLR\*. Control Register 1 consists of a 7-bit latch, Ul3, which latches data bits D0-D6, and an independent flip-flop, U34b, which latches D7, the Auto Wait bit. The Auto Wait bit is latched by a separate flip-flop so that it can be reset not only by pRESET\* and EXT CLR\*, but also by the INTRQ signal from the 1793 (see section 4.2.8, "Auto Wait"). Control Register 2 consists of a 3-bit latch, Ul2. For the bit definitions of the external control/status registers, see Appendix B.

# 4.2 THE SYSTEM INTERFACE

# 4.2.1 THE BANK SELECT CIRCUITRY

The 2422 registers and the on-board ROM cannot be selected unless the internal signal BANK SELECT\* is active low. This signal is the Q\* output of the flip-flop U30b; the complementary Q output is used to light the Bank LED. The conditions under which BANK SELECT\* is active low depend on the setting of the If the BANK EN jumper has been set to OFF, EN jumper. BANK disabling the bank select circuitry, the Preset input to flip-flop U30b is jumpered to ground, forcing BANK SELECT\* permanently low, thus circumventing the Bank Select circuitry. If the jumper is set to position ON, the Clear input to the flip-flop is jumpered to the pRESET\* and EXT CLR\* signals from system bus. If either goes low, as they both would during the power-on or system reset, the flip-flop is cleared, and BANK SELECT\* is forced inactive high. After both pRESET\* and EXT CLR\* release the Clear input, the BANK SELECT\* line can be set low if the flip-flop is clocked while its D input is high. The flip-flop is clocked when pWR\* goes high at the end of an I/O write cycle to port 40h. The state of the D input is determined by the Bank Select Byte being written to port 40h at this time. Only if the Bank Select Byte has a 1 in the bit position that is jumpered on BANK BYTE jumpers will the D input be high, resulting in the active BANK SELECT\*. Finally, if the BANK EN jumper has been set to RST, the flip-flop's Preset input has been jumpered to pRESET\* and EXT CLR\*. During power-on or reset, then, BANK SELECT\* is forced active low. In this case, BANK SELECT\* will go inactive high only if the flip-flop is clocked when its D input in other words, if the user selects another bank for is low; operation.

#### 4.2.2 SELECTING THE 2422 REGISTERS

The decoding of the port addresses is accomplished primarily by U22, an address-decoding ROM. When it is enabled by either the active sOUT or sINP, it decodes the register address on the low-byte address lines into one of four outputs. One output goes low for address 40h and is used for clocking the bank select flip-flop, as described in the previous section. Another output goes low for addresses in the 30-33h range. It is ORed with BANK SELECT\*; when both signals are low, the result is the active signal CONTROLLER SELECT\*. This signal is tied to the 1793's Chip Select input, enabling the 1793 when it is active. Selection of the individual registers within the 1793 is performed by address lines AO and Al, tied to the 1793's two address inputs.

The two remaining outputs of U22 are used to select the external registers. One goes low for either address 04h or 34h. When it is ORed with the active BANK SELECT\*, the result is the active 04/34 SELECT\* line. This line enables a 2- to 4-line decoder, U45a. The final output of U22, which goes low for address 34h, is input to this decoder, along with the WR line (high whenever MWRITE or pWR\* is active). U45a decodes these two inputs into the four enable lines to the external registers: CNTRL1\*, STAT1\*, CNTRL2\*, STAT2\*.

#### 4.2.2.1 Memory-mapping of the Registers

As mentioned before, the 2422 has optional memory-mapped I/O capabilities. U21, when installed, maps the all 2422 registers, expect for the Bank Select register, to the last six bytes but one of a 64K bank; that is, locations FFF8-FFFD. When U21 is enabled by an output of address-decoding ROM U23 going low in response to an FF on the high-order address line, U21 decodes a low-byte address in the F8-FD range into three outputs which correspond to the 30-33, 04/34, and 34 outputs of U22 and are tied to them. Thus if U21 receives an address in the range of F8-FB, for example, it pulls U22's 30-33 output low, resulting in CONTROLLER SELECT\* as described above. Table 4-1 shows the registers' memory locations and the corresponding port addresses.

| RAM Location | Port Address |

|--------------|--------------|

|              |              |

| FFF8         | 30           |

| FFF9         | 31           |

| FFFA         | 32           |

| FFFB         | 33           |

| FFFC         | 34           |

| FFFD         | 04           |

# TABLE 4-1 MEMORY-MAPPED I/O ADDRESSES

## 4.2.3 SELECTING THE ROM

The ROM has two enable inputs, both of which must be active low for the ROM to be enabled. One enable input is pulled low whenever pWR\* and MWRITE are both inactive. The other enable input is pulled low by ROM SELECT\*, the output of the ROM Select circuitry which is active whenever one of the enabled portions of the ROM is addressed while BANK SELECT\* is active. Once the ROM is enabled, address lines A0-AlO, input directly to the ROM itself, select one location in the ROM's 2K of memory.

The ROM Select circuitry is designed to distinguish the Basic I/O portion of the ROM so that it can be enabled independently of the monitor/bootstrap portion of the ROM. TO do so, U23, an address decoding ROM, decodes a high-byte address byte in the range of FO-F7 into two outputs when it is enabled by sINP, sOUT, and sINTA being inactive while BANK SELECT\* is active. One goes low for a high byte address of F6 or F7, indicating an address in the range of the Basic I/O portion of the ROM; the other goes low for any address in the ROM's range. Since the bootstap loader and monitor are needed only before CP/M loaded, the latter output of the decoding ROM is qualified by is the signal BOOT ENABLE\*. Only if BOOT ENABLE\* is low can the ouput pull ROM SELECT\* low.

state of the BOOT ENABLE\* line can be controlled one of The three ways, depending on the setting of the BOOT EN jumper. If the BOOT EN jumper is set to OFF, BOOT ENABLE\* is set permanently If the jumper is set to position A, the BOOT ENABLE line high. is jumpered to the Q output of flip-flop U30a. This flip-flop cleared by PRESET\* or EXT CLR\*, thus forcing the BOOT ENABLE\* is line low during system power-on or reset and enabling the ROM. The flip-flop can then be clocked by an I/O write to port 40h. BOOT Since the D input to the flip-flop is tied high, ENABLE\* goes high when the flip-flop is clocked. Because the bank the board resides in is also selected by an output to port 40h, the BANK SELECT\* line must be either set permanently low or set low

on reset if this method of enabling/disabling the bootstrap loader is to work. If the BOOT EN jumper is set to position B, BOOT ENABLE\* is jumpered to the BOOT\* signal from Control Register 2. Thus the state of BOOT ENABLE\* is entirely software controlled: writing a 0 to bit 7 of Control Register 2 pulls BOOT ENABLE\* low; a 1 pulls it high.

Once CP/M is loaded and BOOT ENABLE\* is high, disabling the monitor and bootstrap loader portions of the ROM, the basic I/O portion can still be accessed if the PR EN jumper is set ON. This allows the F6-F7 output of the address decoding ROM to pull ROM SELECT\* low when it goes low and thus enable the ROM.

# 4.2.4 THE BOARD SELECT LINE AND LED

CONTROLLER SELECT\*, 04/34 SELECT\*, and ROM SELECT\* are NANDed together by U32a, the output of which is BOARD SELECT. If any of these three lines is low, BOARD SELECT is pulled high, lighting the Board Select LED. BOARD SELECT, when inactive, disables the data bus buffers.

# 4.2.5 PHANTOM\* AND FF DETECT

The FF Detect circuitry is used to detect unused locations the on-board ROM so that when an unused location is addressed in PHANTOM\* is forced high, allowing another device to respond to the address. When an empty location in the ROM is addressed, the ROM outputs an FFh, or all ones. Only if an unused location is addressed will this be the case. An 8-input NAND gate, U40, monitors the internal data lines for this condition. As long as a non-FF byte is being transferred, the NAND gate's output is high. This high is in turn NANDed with pDBIN and BOARD SELECT. If both signals are high, the output of the NAND gate, PHANTOM\*, is low and enables the Data In buffer. When the internal data lines contain an FF, the FF-detect NAND gate goes low, disabling PHANTOM\* and the Data In buffer (input to the CPU). Thus another device can respond to the memory read without interference from the ROM.

#### 4.2.6 THE DATA BUS

During Write cycles, the 2422's internal bi-directional data is driven by U38, an 8-bit buffer. When enabled by either bus MWRITE or pWR\* being active when BOARD SELECT is active, this chip gates the data bits on the Data Out bus (output from the CPU) onto the 2422's internal data bus. When the chip is disabled, its outputs are in a high impedance state. The Data In is driven by U39, another 8-bit buffer. When enabled by bus BOARD SELECT, pDBIN, and the output from the FF Detect circuitry being high, this chip gates the data bits on the 2422's internal data bus onto the Data In bus. When disabled, its outputs are also in a high impedance state.

#### 4.2.7 ROM WAIT CIRCUITRY

The purpose of the ROM Wait circuitry is to increase the memory access time allowed to the ROM and to the registers in the disk controller when they are memory mapped. One Wait state per memory cycle in which either the ROM or the registers are addressed is sufficient for this purpose. If the ROM WAIT jumper is set to ON, pREADY is forced low only when either ROM SELECT\* or CONTROLLER SELECT\* is low when pSYNC is high. pSYNC is used to ensure that that pREADY is pulled low in every cycle in which the ROM or disk controller chip is selected and that it remains low only long enough to generate one Wait state. If the ROM WAIT jumper is set to 4 MHZ, the state of pREADY is further qualified by the 2\*/4 MHZ signal. Only when the 2\*/4 MHZ signal is high, indicating the CPU is operating at 4 MHZ, can pREADY go low.

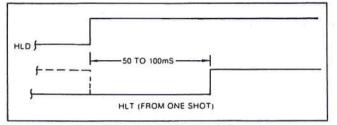

#### 4.2.8 AUTO WAIT CIRCUITRY