# 8800b-SM & -OM DOCUMENTATION

a subsidiary of Pertec Computer Corporation

# 8800b-Sm & -dm DOGUMENTATION

a subsidiary of Pertec Computer Corporation 2450 Alamo S.E. /Albuquerque, New Mexico 87106

. . . . .

#### NOTICE

Information contained within this document may not be reproduced, distributed or disclosed in full or in part by any person without prior approval of Pertec Computer Corporation, Microsystems Division.

Marketing Headquarters

Pertec Computer Corporation Microsystems Division 20630 Nordhoff Street Chatsworth, CA 91311 Phone (213) 998-1800 TWX (910) 494-2788

International Marketing Headquarters

Pertec Computer Corporation Business Systems Division 17112 Armstrong Avenue Irvine, CA 92714, USA Phone (714) 540-8340 TWX (910) 595-1912

### CHANGE RECORD

•

| Revision | Date       | Pages                                 |

|----------|------------|---------------------------------------|

| A        | June, 1978 | Initial Release                       |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            | - · · ·                               |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            |                                       |

|          |            | · · · · · · · · · · · · · · · · · · · |

N

TABLE OF CONTENTS

| Section                                   | <u> </u>                                     | age |  |  |  |  |

|-------------------------------------------|----------------------------------------------|-----|--|--|--|--|

| Part I. Introduction and Operator's Guide |                                              |     |  |  |  |  |

|                                           | 1. Introduction to This Manual               | 3   |  |  |  |  |

|                                           | 2. Introduction to the Standard System       | 4   |  |  |  |  |

|                                           | 3. Using This Documentation Package          | 10  |  |  |  |  |

| Part II.                                  | 8800b Turnkey Computer                       |     |  |  |  |  |

|                                           | 1. Introduction                              | 15  |  |  |  |  |

|                                           | 2. Theory of Operation                       | 21  |  |  |  |  |

|                                           | 2-1. General                                 | 23  |  |  |  |  |

|                                           | 2-2. CPU Board                               | 26  |  |  |  |  |

|                                           | 2-3. Turnkey Module                          | 29  |  |  |  |  |

|                                           | 3. Advanced Operations                       | 37  |  |  |  |  |

|                                           | 3-1. The Front Panel                         | 39  |  |  |  |  |

|                                           | 3-2. The Turnkey Module                      | 40  |  |  |  |  |

|                                           | 3-3. AUTO-START                              | 54  |  |  |  |  |

|                                           | 3-4. Miscellaneous Options                   | 55  |  |  |  |  |

|                                           | 3-5. The Power Supply                        | 57  |  |  |  |  |

|                                           | 4. Troubleshooting Hints                     | 59  |  |  |  |  |

|                                           | 4-1. Introduction                            | 61  |  |  |  |  |

|                                           | 4-2. Preliminary Considerations              | 61  |  |  |  |  |

|                                           | 4-3. CPU                                     | 62  |  |  |  |  |

|                                           | 4-4. Turnkey Module                          | 62  |  |  |  |  |

| Part III. Minidisk System                 |                                              |     |  |  |  |  |

|                                           | ]. Introduction                              | 67  |  |  |  |  |

|                                           | 1-1. MITS Altair Minidisk System Description | 69  |  |  |  |  |

|                                           | 1-2. Specifications                          | 69  |  |  |  |  |

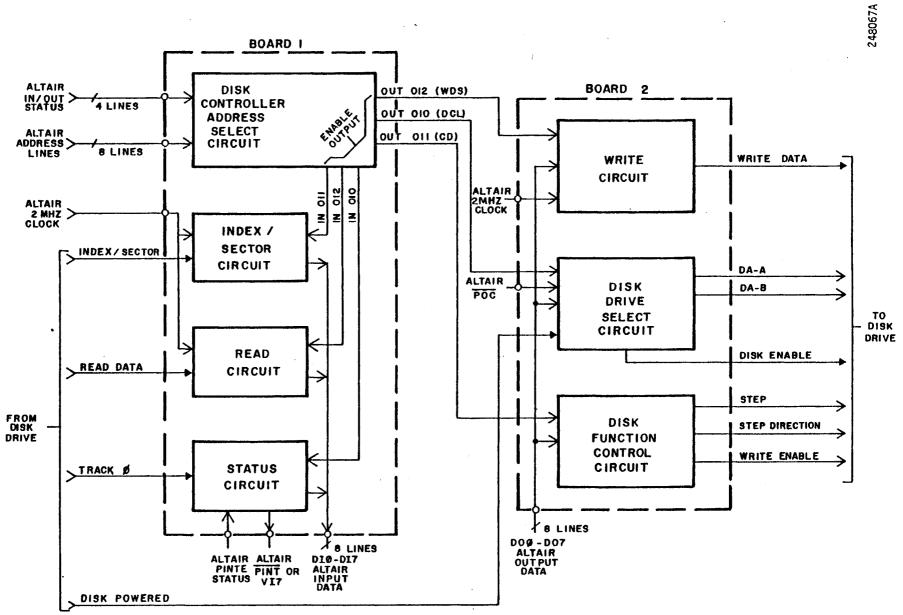

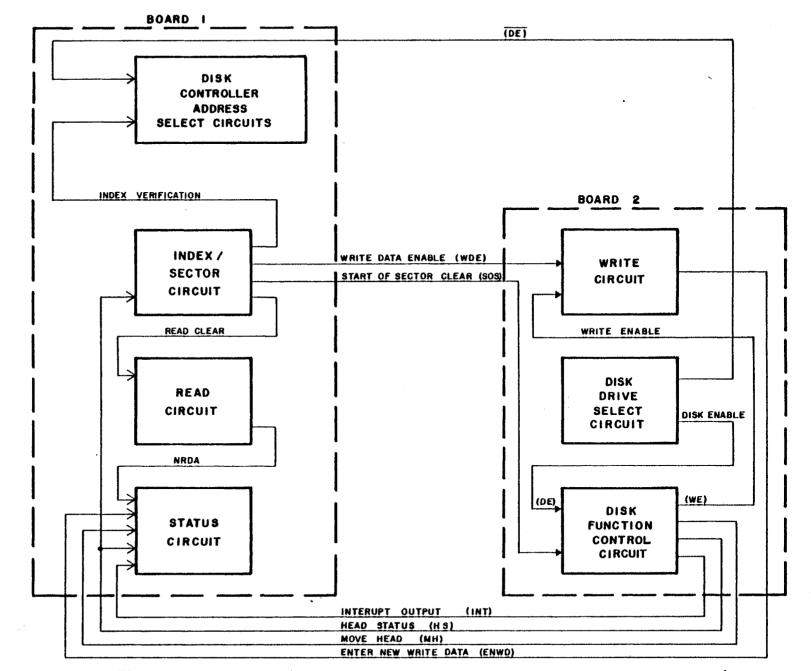

|                                           | 2. Theory of Operation                       | 73  |  |  |  |  |

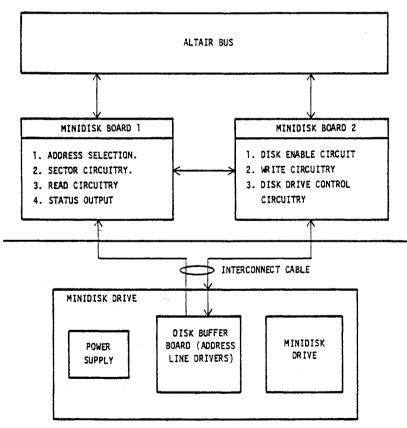

|                                           | 2-1. General                                 | 75  |  |  |  |  |

|                                           | 2-2. Logic Circuits                          | 75  |  |  |  |  |

|                                           | 2-3. Schematic Referencing                   | 75  |  |  |  |  |

|                                           | 2-4. Minidisk Block Diagram                  | 80  |  |  |  |  |

|                                           | 2-5. General System Operation                | 81  |  |  |  |  |

|                                           | 2-6. Minidisk Controller Block Diagram       | 82  |  |  |  |  |

|                                           | 2-7. Address Select Circuit                  | 87  |  |  |  |  |

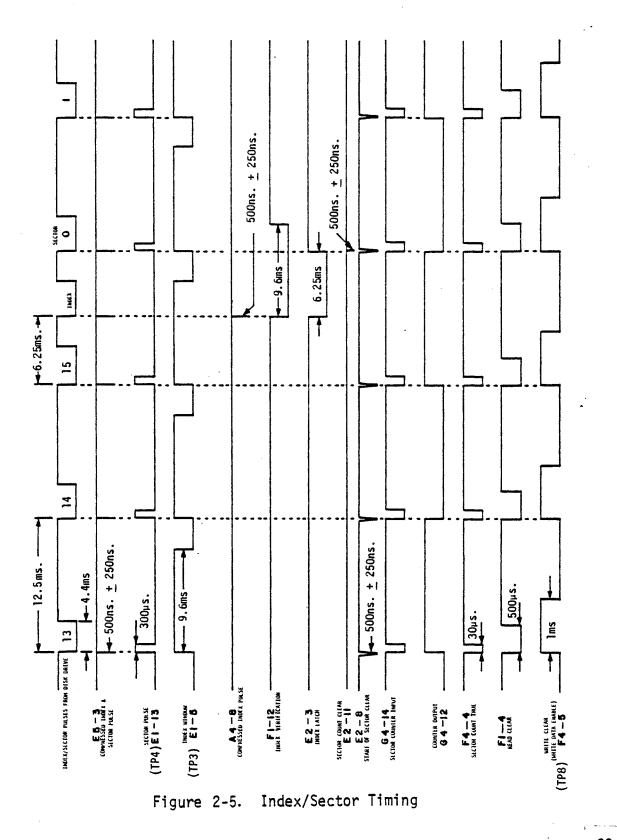

|                                           | 2-8. Index/Sector Circuit                    | 88  |  |  |  |  |

.

.

### <u>Section</u>

### <u>Page</u>

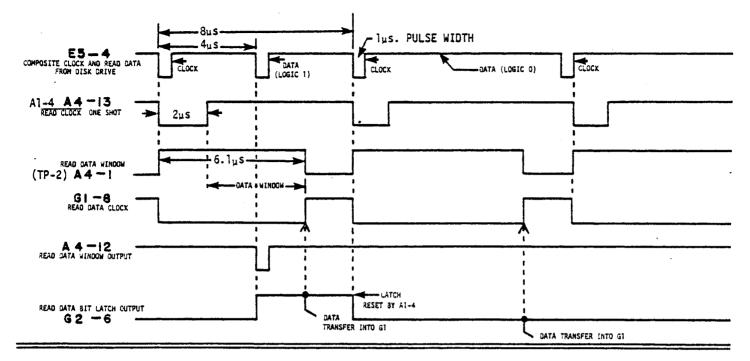

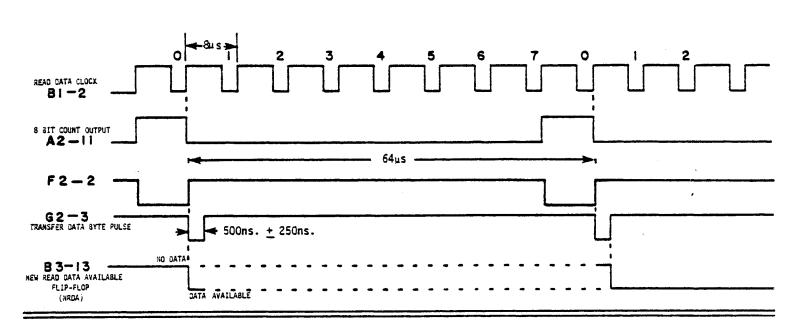

|                                               | 2-9. Read Circuit 9                    | 1  |  |  |  |  |

|-----------------------------------------------|----------------------------------------|----|--|--|--|--|

|                                               | 2-10. Status Circuit 9                 | 4  |  |  |  |  |

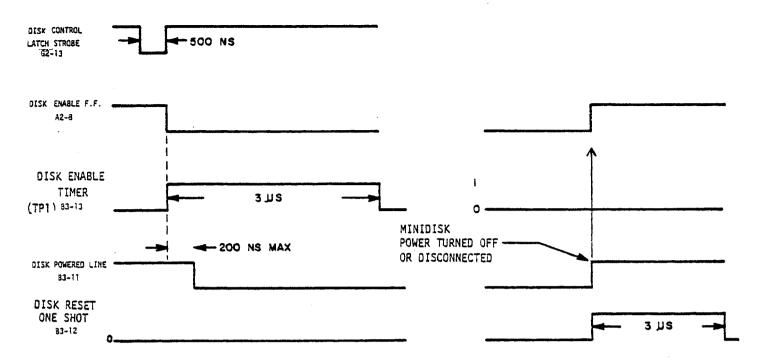

|                                               | 2-11. Disk Enable Circuit 9            | 4  |  |  |  |  |

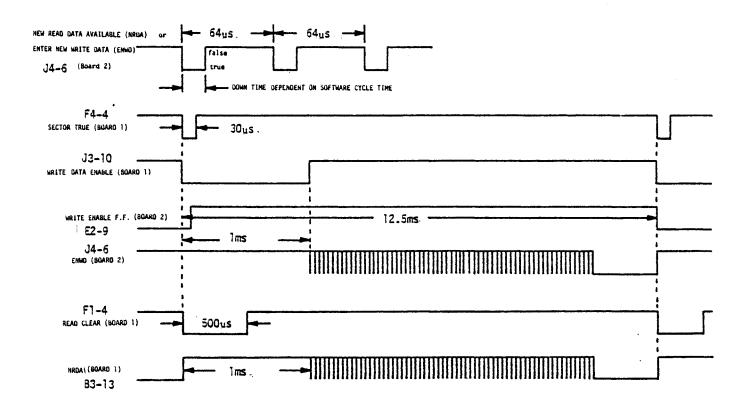

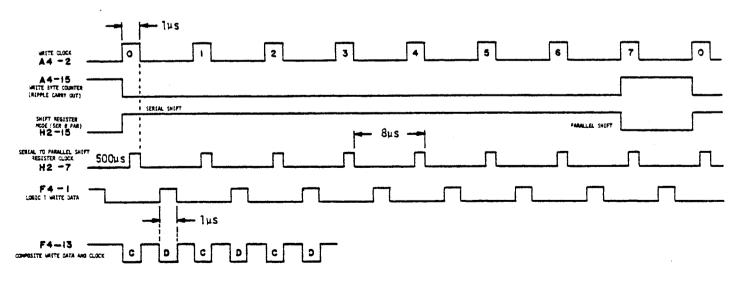

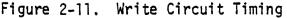

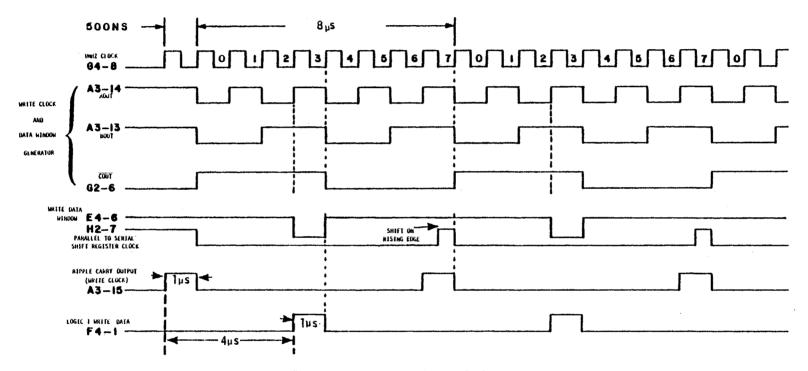

|                                               | 2-12. Write Circuit 9                  | 6  |  |  |  |  |

|                                               | 2-13. Disk Function Control Circuit 10 | 1  |  |  |  |  |

|                                               | 2-14. Head Stepping                    | 13 |  |  |  |  |

|                                               | 2-15. Disk Disable Timer 10            | 4  |  |  |  |  |

|                                               | 2-16. Move Head Status                 | )4 |  |  |  |  |

|                                               | 2-17. Head Status                      | )5 |  |  |  |  |

|                                               | 2-18. Enable Interrupts                | 15 |  |  |  |  |

| 3.                                            | Preliminary Checkout                   | )7 |  |  |  |  |

|                                               | 3-1. Disk Enable Test                  | )9 |  |  |  |  |

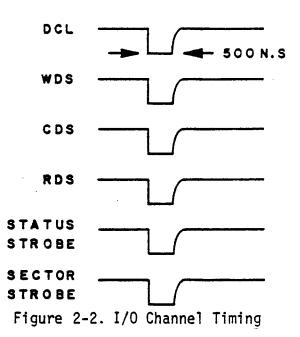

|                                               | 3-2. Altair Minidisk Controller Timing |    |  |  |  |  |

|                                               | Test Points                            | 0  |  |  |  |  |

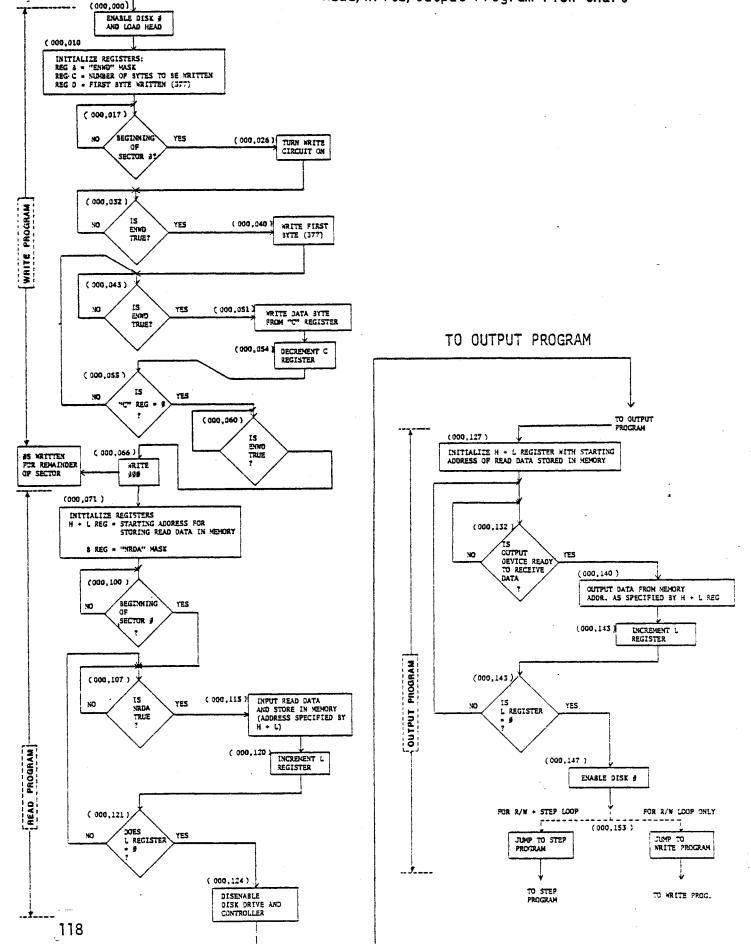

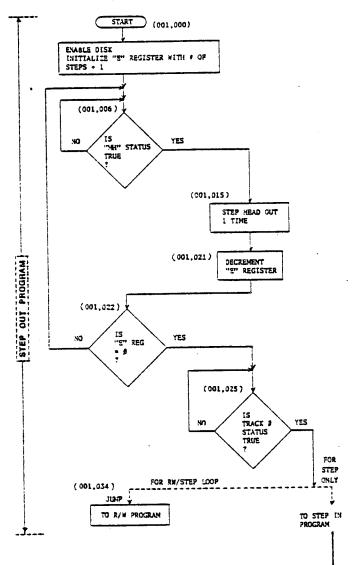

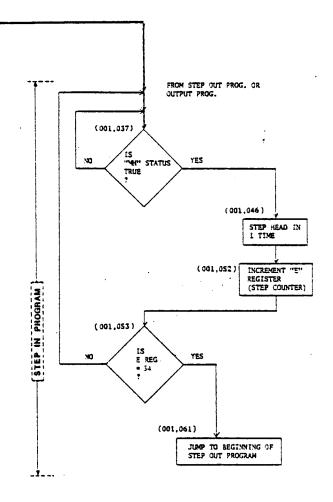

|                                               | 3-3. Altair Minidisk Test Programs 12  | 23 |  |  |  |  |

| Appendices                                    |                                        |    |  |  |  |  |

| Α.                                            | Altair 8800b Bus Assignments           | 25 |  |  |  |  |

| Β.                                            | Minidisk Programming                   | 29 |  |  |  |  |

| Intel 8080 Microcomputer System User's Manual |                                        |    |  |  |  |  |

## 8800b-sm-& -dm DOGUMENTATION PART 0 INTRODUCTION AND OPERATORS GUIDE

<u>.</u> . .

•

. . . •

· · · · ·

ĺ.

#### 1. Introduction

#### 1-1. Introduction to this Manual

The 8800b-sm and -dm are integrated computer systems that include the Altair 8800b Turnkey microcomputer along with either one (-sm) or two (dm) Altair Minidisk mass storage units.

The 8800b Turnkey computer includes the system power supply, the Central Processing Unit (CPU) with the 8080A microprocessor and a Turnkey Module board. The Turnkey Module is a multi-function board that includes 1K bytes of random access memory (RAM), provisions for up to 1K bytes of read only memory (PROM) (including the Minidisk Boot Loader PROM) and a serial input/output port (SIO) for connecting the computer to a terminal. Part II of this documentation package documents the 8800b Turnkey computer. Section 1 is a description of the components of the Turnkey computer, and Section 2 is a brief summary of its theory of operation. Section 3 is an advanced operation manual which details procedures for expanding and modifying the standard system. Section 4 is a brief guide to troubleshooting the electronics of the computer.

The Minidisk mass storage subsystem consists of one or two Minidiskk drives, a drive controller and an interface card for connecting the disk system to the computer. These are all described in Part III of this documentation package. Section 1 is a listing of the specifications of the Minidisk subsystem. Section 2 is a summary of the theory of operation and Section 3 is a description of procedures for initial checkout and fault diagnosis.

The Appendices include a description of the Altair bus, instructions for converting the power supply for use with 230 volts AC, a listing of the Minidisk Boot Loader PROM and aids for programming the Minidisk system in machine language.

Finally, the <u>Intel 8080A Microcomputer System User's Manual</u> details the structure, timing and instruction set of the 8080A microprocessor. It also gives technical information about some of the CPU's auxiliary circuits.

#### 1-2. Introduction to the Standard System

The standard 8800b-sm or -dm system consists of the 8800b-sm or -dm computer and either a Teletype<sup>TM</sup> or Cathode Ray Tube (CRT) terminal. This section shows how to assemble such a system from its components and how to load and run BASIC on the assembled system.

A. Setting up the system. Carefully lift the computer unit from its packing case and place it on a hard, flat surface. Leave enough space on all sides so that the flow of cooling air is not impaired. Do not connect the power cord until the terminal has been installed,

Remove the protective tabs from the Minidisk drives following the directions printed on the tabs.

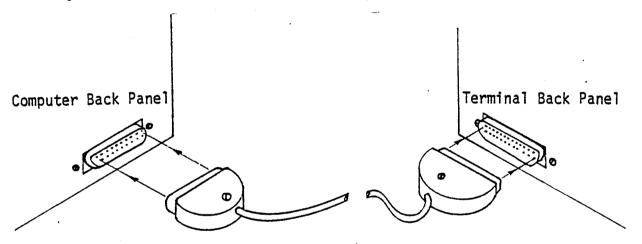

The computer is set at the factory to match the terminal shipped with it. Therefore, to install the terminal, it is only necessary to connect the computer and the terminal with the cable supplied with the terminal. The diagram below shows the 25 pin cable connectors and the matching connectors on the terminal and computer.

#### Figure 1-1. 25 Pin Cable Connectors

The power supply is protected by a 3 amp, slow-blow fuse mounted on the back panel of the computer. It should be replaced as necessary only by the same type of fuse. The power cord should be connected to a source of 115 volts, 50-60 Hz AC. (230 VAC operation is available as an option. See Appendix C).

After making sure the fuse is installed and the power cords for the terminal and computer are plugged in, insert the BASIC diskette into drive zero.

248067A

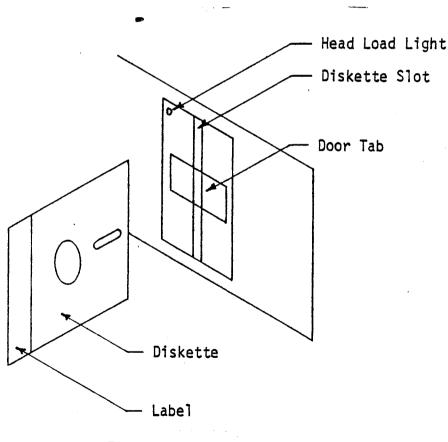

To do this, open disk drive zero by pulling out on the door tab (see Figure 1-2). Insert the edge of the diskette opposite the label into the drive with the label side toward the open tab. Push the diskette all the way into the drive and close the door tab.

Now, move the RUN/STOP switch on the front panel up to the RUN position and turn the power switch on. The power switch has three positions. At 12 o'clock, the unit is off and the key may be removed. At 3 o'clock, the power is on and the front panel switches are enabled. At 6 o'clock, the computer is on, but the front panel switches are disabled. In this position, the key may be removed.

With the power switch on, the Power indicator should light showing that the computer circuitry is receiving operating voltage from the power supply. If the Power indicator does not light, turn off the power switch and check the power cord and fuse.

B. Initializing BASIC. When the power is turned on, BASIC is loaded into memory automatically. When it has been loaded, BASIC prints

#### MEMORY SIZE?

on the terminal to begin the initialization dialog. This question asks the operator to specify the amount of memory to be used by BASIC programs. Typing a number and carriage return reserves that number of bytes. Typing just a carriage return directs BASIC to use all available read/write memory. BASIC now prints

LINEPRINTER?

The operator types a letter and carriage return to indicate the type of printer in use as follows:

| Letter | Printer |      |

|--------|---------|------|

| 0      | =       | LP80 |

| C      | =       | C700 |

| Q      | =       | Q70  |

If no printer is connected, any of the letters may be typed. If the response is not 0, C or Q, however, BASIC asks LINEPRINTER? again.

BASIC now asks

HIGHEST DISK NUMBER?

In a system with 1 disk, the highest number is 0. With 2 disks, the highest number is 1. Typing just a carriage return is equivalent to typing 0.

Now BASIC asks the number of disk data files (random access and sequential) to be open at one time:

HOW MANY DISK FILES?

The operator responds with the number of disk data files expected to be open at any one time. BASIC then prints

HOW MANY RANDOM FILES?

Here again, the operator responds with the number of random access files expected to be open at any one time.

Now BASIC is initialized and prints the following messages: ALTAIR MINI-DISK BASIC REVISION 4.1 JULY 1977 COPYRIGHT 1977 BY MITS, INC. 0K

BASIC is now ready for use.

At any time, BASIC may be reloaded simply by momentarily depressing the START switch.

C. Initializing New Diskettes. Because the BASIC code takes up so much diskette space, it is supplied on a "write protected" diskette. This means that no programs or data may be saved on the BASIC diskette.

In addition to BASIC, the BASIC diskette includes two programs, PIP and STARTREK, which are available to users. Before they can be run, the BASIC diskette must be mounted (see section D below). Since the BASIC diskette is write protected, mounting it causes a DISK I/O ERROR, but the reading process is not affected.

The desired program may now be read from the disk and loaded into memory. To do this, type the following command:

LOAD "<program name>",<disk number> where <program name> is the name of the desired program and <disk number> is the number of the disk drive into which the BASIC disk was inserted (usually zero).

To avoid inadvertant damage to the BASIC disk, type the following command:

UNLOAD<disk number>

where disk numbers is the drive number that appeared in the LOAD command above.

Now the BASIC diskette may be removed and another diskette inserted into the drive and mounted.

The program may be saved on the new diskette by typing the following command:

SAVE "<program name>",<disk number> where <disk number>is the number of the disk drive into which the new diskette was inserted.

Subsequent to saving the program, it may be run by typing the following command:

RUN "<program name>",<disk number> where <disk number>is the number of the disk drive into which the diskette bearing the program was inserted.

#### CAUTION

Do not attempt to write programs or data onto the BASIC diskette. This can result in FILE LINK ERRORS that can make the BASIC diskette unusable. Before writing anything on disk, unload and remove the BASIC diskette.

If the diskette has never been used it must be initialized before it can be used. This is done by typing the following command:

DSKINI <disk number>

where disk number is the number of the disk drive on which the blank diskette is loaded. The DSKINI command marks all the sectors on the diskette as being empty. BASIC reads these marks to determine sector boundaries.

#### CAUTION

Only new, blank diskettes need to be initialized. Using DSKINI on a diskette that contains files destroys all the files. DISKINI should, therefore, be used with extreme caution. The DSKINI process takes about 2 minutes per diskette. When it is finished, BASIC prints OK.

D. Mounting Diskettes. To ready a diskette for reading or writing, type the following command:

MOUNT <disk number>

Omitting the disk number causes all disks in the system to be mounted. After a few seconds, BASIC prints

0K

to indicate that the disk is ready for use.

Before removing a mounted disk from a drive, type the following command

UNLOAD <disk number>

Omitting the disk number unloads all mounted disks.

E. Diskette Specifications and Care. The 8800T sm and dm use 5 1/4", hard-sectored diskettes. Diskettes are available from MITS (Part number 102501) or may be purchased from any Altair Computer Center.

The notch on the side of the diskette engages a switch in the drive which enables the write circuitry. Covering the notch with a piece of tape makes writing on the diskette impossible. The BASIC diskette is protected in this manner.

#### CAUTION

Unprotecting the BASIC diskette can cause destruction of the BASIC interpreter. DO NOT remove the BASIC diskette protection tab.

Several handling precautions will maximize the life and usefulness of diskettes and drives.

- Return diskettes to their storage envelopes when they are not in use. Do not leave them in the drive.

- Keep diskettes away from magnetic fields. Fields may be caused by fluorescent lights, transformers or large pieces of magnetizable materials.

- 3. Mark the diskette label only with felt tip pen. Do not use ball point pen or pencil.

- 4. Keep dust and other particulate matter away from diskettes.

- 5. Keep diskettes away from excessive sunlight and heat.

- Never touch the diskette surface (through the head access window) or attempt to clean it.

F. Miscellaneous Information. Since the address of the Mini-Disk controller is the same as the standard size floppy disk controller (88-DCDD) the standard size disk drives may not be used in the 8800T-sm or-dm system.

A timing circuit in the Mini Disk Controller turns off the drive motor 6.4 seconds after the last access operation to minimize drive wear.

#### 1-3. Using this Documentation Package

The remainder of the documentation in this package contains reference material for operating and maintaining the components of the system.

Three commonly encountered situations which require the use of this reference material are 1) expansion of the system memory, 2) adding or modifying input/output peripheral equipment and 3) adding special purpose PROM functions. The procedures for making these modifications are sketched below along with references to more detailed information. The references are either to the manuals or to the page numbers in this documentation package in which the information may be found.

#### NOTE

Before working on the inside of the computer case make sure the power is off and the power cord disconnected from the line.

To remove the case cover, remove the two bolts in the upper corners of the back panel. Then slide the cover back and lift it off.

To remove a card, pull straight up on both ends of the card. Carefully remove any cable connectors when the board is free.

To insert a card, connect the necessary cables and position the board so the edge connector is down and the component side of the board is to the right as viewed from the front of the unit. Insert the card into the card guides and slide it straight down until it makes contact with the connector at the bottom of the slot. Apply firm, steady pressure to the upper edge of the card until the board seats in the connector. The top edge should be flush with the top of the card guides.

A. Expanding Memory. System memory expansion is accomplished by adding memory boards or replacing them with boards of higher capacity. Use the following procedure to make these changes:

- 1) Set the addresses of the new boards (memory board manual).

- 2) Insert the boards in the chassis (p.10).

- Change the address of the RAM block on the Turnkey Module board, if necessary to avoid conflicts with the new memory addresses (p. 40 ).

B. Modification of Input/Output Arrangements. Input and output arrangements can be changed either by adding new peripheral devices (terminals, mass storage, printers, etc.) along with their associated interface boards or by changing the device connected to the Turnkey Module SIO port.

- If a new interface board is being installed, set the port address, data transfer rate (or baud rate) and signal type (interface board manual).

- 2) Install all necessary cables and insert the board in the chassis (interface board manual and p. 10).

- If the SIO port is to be connected to a different device or otherwise changed, set the desired address, data transfer rate and signal type (p. 42ff).

- 4) If the new device is to be the console terminal for BASIC or DOS, set the sense switch on the Turnkey module board to conform to the device (p. 41 and BASIC or DOS manual).

السماد العم المحددين وليان أستعده يستاركان الإركان وال

C. Adding Special PROM Functions. The Turnkey Module has sockets for up to four 256 byte PROM chips. These PROMs can be used to store any programs or data that must be permanently retained. Several pre-programmed PROMs are available for the 8800 series microcomputers including a Turnkey PROM Monitor and a multi-purpose bootstrap loader for loading programs from paper tape and cassette. In addition, userwritten programs can be retained in PROM for use in dedicated applications. To install these PROM functions, use the following procedure:

Set the address of the Turnkey Module PROM block to the first location of the 1K byte block that includes the address of the new PROM (p. 40, PROM documentation).

- Insert the new PROM in the proper socket on the Turnkey Module board. The first address of the first PROM socket is the address set in step 1. The first address of the second socket is the board address plus 256 and so on (p.40).

- 3) Set the starting address of the new program in the AUTO-START switches, if the program is to be executed automatically when the power is turned on or when the START switch is actuated. Note that the Turnkey Module is supplied with the Mini Disk Boot Loader PROM at the AUTO-START address to automatically load BASIC or DOS. Changing the PROM or AUTO-START addresses will disable this feature (p. 54).

#### NOTE

A Turnkey PROM Monitor is a good investment for an expanded system. The Monitor allows examination and modification of any memory location from the terminal. It lets the operator dump the contents of any range of memory locations and transfer control of the computer's execution to any address. Putting the Monitor at the AUTO-START address allows the Monitor to be entered at any time, simply by actuating the START switch. This provides a useful reset function for BASIC programs. If a programs hangs in an infinite loop or an impossible I/O function, reentering the Monitor with the START switch and jumping to location zero causes BASIC to print OK and await further instructions.

## 8800b-sm & -dm DOGUMENTATION PART II 8800b TURNKEY COMPUTER

$\mathbf{x}^{*}$

# SEGTION 1 INTRODUCTION

15/(16 Blank)

. a. **~**...

#### 1. INTRODUCTION

The Altair 8800b Turnkey computer is housed in a standard Altair system case and contains the following elements:

-Power supply and motherboard assembly -CPU board with the 8080A microprocessor -Turnkey Module with memory and I/O circuitry -Front panel board

The heart of the computer is the Central Processing Unit (CPU) board (Figure 1-2) which holds the 8080A microprocessor and its associated circuitry. The 8080A performs all the logical and arithmetic computations for the system. It also supplies control and status signals for the other system components. Other circuitry on the CPU board provides clock signals and synchronization functions.

The Turnkey module (Figure 1-3) is a general support board for the Turnkey system which includes memory, I/O and AUTO-START control. The memory section has 1K bytes of random access memory (RAM) and positions for up to 1K bytes of read-only memory (ROM). Random access memory stores information that can be read, written or changed at will. RAM is volatile, however, and information is lost when power is interrupted. Programmable Read-only memory (PROM) is non-volatile. Information in PROM is always present whether the power is on or not. Thus, PROM can store programs and data which must be permanently retained. The computer cannot write information into PROM, however. A special PROM programmer must be used to do this, although factoryprogrammed PROMs are available for some widely used functions.

The serial Input/Output channel (SIO) connects the parallel data bus in the computer to serial input/output devices, such as Teletypes, CRT terminals, modems, etc. The SIO may be configured to accommodate a variety of terminal types and speeds to match virtually any serial I/O arrangement.

The AUTO-START feature is the key to the Altair 8800b Turnkey computer's ease of operation. When the computer's power is turned on or the START switch is actuated, the AUTO-START logic forces the computer to execute the instruction at a pre-selected address in PROM. The address could be the beginning of a series of instructions to load a program from an I/O device, the start of a monitor program or a dedicated application program.

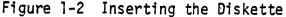

Front Panel switches (Figure 1-4) include the power switch, which provides system security as well as turning the power on or off, and switches that start and stop execution of programs. Indicators on the Front Panel monitor the computer system's operation.

Power, data, addresses, status and control signals and miscellaneous pulses are carried by the system bus on the motherboard. The bus is fully parallel, meaning that all signals are available to all boards plugged into the motherboard's sockets. This allows for easy and quick system expansion. The motherboard can accommodate the CPU and Turnkey Module boards plus up to 16 additional boards.

The Power Supply provides all the power voltages required by the Altair 8800b Turnkey system components. The supply has enough capacity to allow expansion of the sytem by addition of as many I/O and memory boards as will fit in the system case.

Figure 1-4 Front Panel Switches and Indicators

••

.

## SECTION 2 THEORY OF OPERATION

í

. a 2 2

#### 2. THEORY OF OPERATION

#### 2-1. General

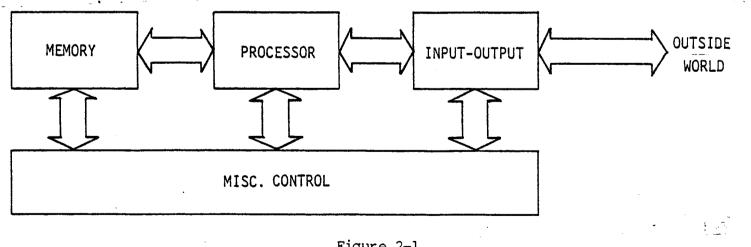

A generalized block diagram of a computer system is shown in Figure 2-1. The Control, Processor, Memory and I/O are arranged so that instructions in Memory cause the Control to direct the Processor to access and manipulate Memory data. The Control also directs the Processor to arrange for Input and Output of data.

The system in the diagram is stored-program computer. Its actions are directed by instructions that are stored in memory. The computer has the ability to change the order in which its instruction are executed and to modify the instructions themselves. This accounts, in part, for the great flexibility of stored program computers.

As the diagram shows, the Control and Processor elements are the heart of the system. All the other elements of the system communicate with and are controlled by the Control and Processor. In many computers, including the Altair 8800b Turnkey computer, the Control and Processor elements are combined in one unit, the Central Processing Unit. Moreover, in the Turnkey system, some of the memory and I/O functions are combined into the Turnkey Module.

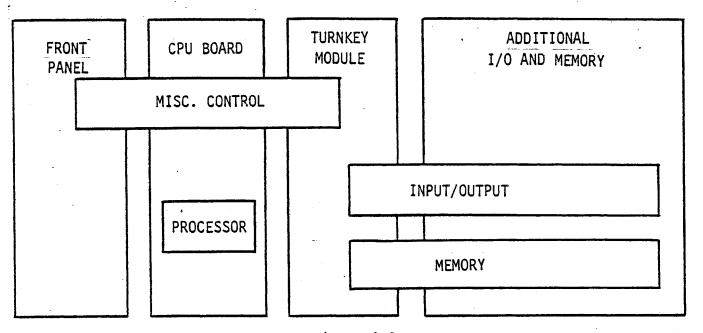

Figure 2-1 Typical Computer System Block Diagram Figure 2-2 is a diagram of the Altair 8800b Turnkey computer system showing how the functional parts are distributed among the physical units of the system.

One important feature of the Turnkey system's design is that it is based upon a bus. The Altair bus is a collection of conducting paths (lines) which distribute signals to all of the system's components. The pins of each board are connected directly to the corresponding pins of every other board. As a result, the system is easily expandable, since every board has access to all of the data, addresses, status and control information in the system.

The bus is located physically on a 100 conductor printed circuit motherboard. The printed circuit card edge connectors on the motherboard provide mechanical support for the system's circuit boards, as well as electrical connection to the bus.

Figure 2-2 Altair 8800b Turnkey System Function Distribution The bus has 16 Address lines, 8 Data-In lines carrying data to the CPU, 8 Data-Out lines carrying data from the CPU and lines carrying pulses that indicate the status of the system and serve various control functions. A list of the conductors on the Altair system bus is in the Appendix.

The activity on the bus corresponds to six machine cycles; Memory Read and Write, I/O In and Out, Interrupt and Halt. The functions of the various bus lines depend on what cycle is currently in progress.

In a Memory cycle, the address of the memory location to be read or written is carried on the address bus. The Data-In bus carries data or instruction codes from memory to the CPU during a Memory Read. The Data-Out bus carries data from the CPU during a Memory Write. In an I/O cycle, the Address bus carries the address of the I/O port through which the data transfer is to take place. The port address is only eight bits long, so it is carried both in the high and low order bytes of the 16 bit Address bus. The Data-In bus carries information from the port to the CPU during an Input cycle. Similarly, the Data out bus carries information from the CPU to the port in an Output cycle.

The Interrupt cycle is provided so that peripheral devices can gain access to the bus. In the absence of interrupts, the CPU can be programmed to check its peripheral devices periodically and service them as they have information to transfer. An input device, for example, waits until the CPU signals that it is ready for input. This arrangement is simple, but it is often inefficient, since the CPU is required to poll the I/O devices whether or not there is information to be transferred. In an interrupt driven system, on the other hand, the I/O device signals the CPU when it is ready to transfer data. This signal is called an Interrupt Request. If the CPU Interrupt Enable bit is set to 1, the CPU acknowledges the Interrupt Request. Otherwise, the request is ignored. In an Interrupt cycle, the CPU fetches an instruction which causes the computer to interrupt the execution of its current program and begin executing another program (called an interrupt service routine) at a special location in memory. The computer also stores the location of its current instruction so that it can return to the place where it left off when the interrupt service routine is completed. The interrupt scheme allows the computer to work on a program until a peripheral device has information to transfer. The CPU can then accept the information and take the necessary action without losing track of the program in progress.

A special machine cycle is provided for direct memory access. During the Hold state, the CPU is effectively disconnected from the bus. This allows a direct memory access device, if it is used, to take control of the bus and transfer information directly to and from memory. For more information on machine cycles, see the Intel 8080 machine cycles, see the <u>Intel 8080 Microcomputer System User's Manual</u> (abbreviated <u>IMSUM</u>), section 2, pp 3-11.

2-2. The CPU Board

#### NOTE

In the following descriptions, the names of signals appear in capital letters. Signal names which are barred ( $\overline{PRESET}$ , for example) are active LOW. That is, they are LOW ( $\emptyset$  volts) when activated and HIGH (+5 volts) otherwise. All other signals are active HIGH.

The address and data lines represent binary 1 as HIGH and binary  $\emptyset$  as LOW.

On the Turnkey module, the sense switches and the address switches for RAM, PROM and AUTO-START allow manual entry of data and addresses. The two states of each switch -on and off- correspond to the two states of a binary digit - 1 and 0. The bits represented by the sets of switches can, therefore, be treated by the computer in the same way as any other data or address bits. Moving a switch in the direction of the arrow next to each set of switches puts the switch in the 1 position.

248067A

•

| REF DESIG | TYPE         | VCC | GRD | OTHER | REF DESIG | TYPE       | VCC | GRD | OTHER    |

|-----------|--------------|-----|-----|-------|-----------|------------|-----|-----|----------|

|           |              |     |     |       | M         | 80808      | 20  | 2   |          |

| G,B       | 74LS04       | 14  | 7   |       | J,X,R,V,  | 74368      | 16  |     | 1        |

|           | 74LSI3       |     |     |       | N,U,P     | 0R<br>8798 | 16  | 8   | 1        |

|           | OR<br>74LS20 | 14  | [ 1 |       | K         | 8212       | 24  | 12  |          |

| S,Y       | 74LSI4       | 14  | 7   |       | D,E       | 8216       | 16  | 8   |          |

|           |              |     |     |       | F         | 8224       | 16  | 8   | VDD • 9  |

| P,W       | 74367        | 16  | 8   |       | A         | 4009       | ł   | 8   | VDD + 16 |

· . ·

The CPU board contains the 8080A microprocessor, its timing and auxiliary control circuits. It also contains buffers and line drivers for the system bus. The heart of the CPU (and the whole computer system) is the 8080A microprocessor. All of the other circuitry on the board serves to support the microprocessor and connect it to the rest of the system.

A. The Microprocessor. The 8Ø8ØA is IC M on the schematic, Figure 2-3a. For a complete description of the internal organization and timingod of the 8080A, see the IMSUM, Chapter 2. \_.

B. Clock and Synchronization. The 8224 clock generator (IC F on the schematic) provides the two-phase, 2 MHz clock for the  $8\emptyset 8\emptyset A$  at the required  $\emptyset$  and 12 volt levels. The master timing reference for the 8224 is an external 18 MHz crystal. The system timing frequency can be changed by replacing the crystal.

The clock generator also synchronizes the 8080A's READY and RESET inputs and provides a status strobe signal (STSTB) that is used to load the 8212 status latch. The READY signal is the logical product (AND) of bus signals XRDY, PRDY, XRDY2 and FRDY. Normally, only PRDY is used for memory synchronization; the others are set to logical 1 by pullup resistors. The bus signal PRESET is filtered, lengthened, shaped and synchronized by the 8224 to generate the RESET input for the 8080A. The STSTB signal is generated as soon as the status information is available on the 8080A data lines.

C. The Status Latch. At the beginning of each bus cycle, status information is presented momentarily on the 8080A data lines. This information is stored in the 8212 latch so that the data lines may be used for other information later. The 8212 is IC K on the schematic. For a complete description of the status information and its timing, see page 2-6 of <u>IMSUM</u>. The 8212 is described on page 5-101 of the same manual.

D. Buffers.

1) Bus splitters. Information is communicated to and from the 8080A through an eight-bit, bidirectional data bus. This bus is buffered by two 8216 bidirectional bus drivers to form a TTL compatible, bidirectional bus on the CPU board. The direction of the 8216's is controlled by PDBIN.

At the other end of the CPU bus are tri-state buffers that split the bidirectional data bus into Data-In and Data-Out busses which are brought out to the system bus. The buffers shown in zones B-3 and B-4 transfer data from the system Data-In bus to the bidirectional bus when both PDBIN and DIG1 are HIGH. (DIG1 is normally HIGH unless the bidirectional bus is being accessed through connector P3. When either PDBIN or DIG1 are LOW, the buffers are put in a high impedance state and no information is transferred through them. Similarly, the buffers in zones C-2 and C-3 transfer data from the CPU bus to the Data-Out system bus when the signal DO DSBL is HIGH.

If no information is present on the Data-In bus, all eight lines are pulled HIGH by resistors on the CPU board. When a interrupt is acknowledged, this forces a RST 7 instruction onto the bus if the Vector Interrupt Board is not used.

2) Input buffers. All input lines to the CPU board are buffered by TTL circuitry. Unused lines are pulled HIGH by resistors which also allow any one of several boards to pull any input line LOW. A line is normally pulled LOW either by an open collector driver or a tri-state driver, with the condition that no more than one tri-state driver may be enabled at one time.

Examples of these input lines are PINT and PHOLD in zone D-8, the READY lines (PRDY, etc.) in zone A-7, PRESET in zone A-6, and the driver disable lines throughout the schematic.

3) Output buffers. All outputs from the CPU board are buffered to drive 3Ø standard TTL loads. The lines are collected into four groups, Address lines, Data Out lines, Status lines and a Control group made up of PWR, PDBIN, PWAIT, PSYNC, PHLDA and PINTE. Each group of lines may be disabled as a group by signals from the bus.

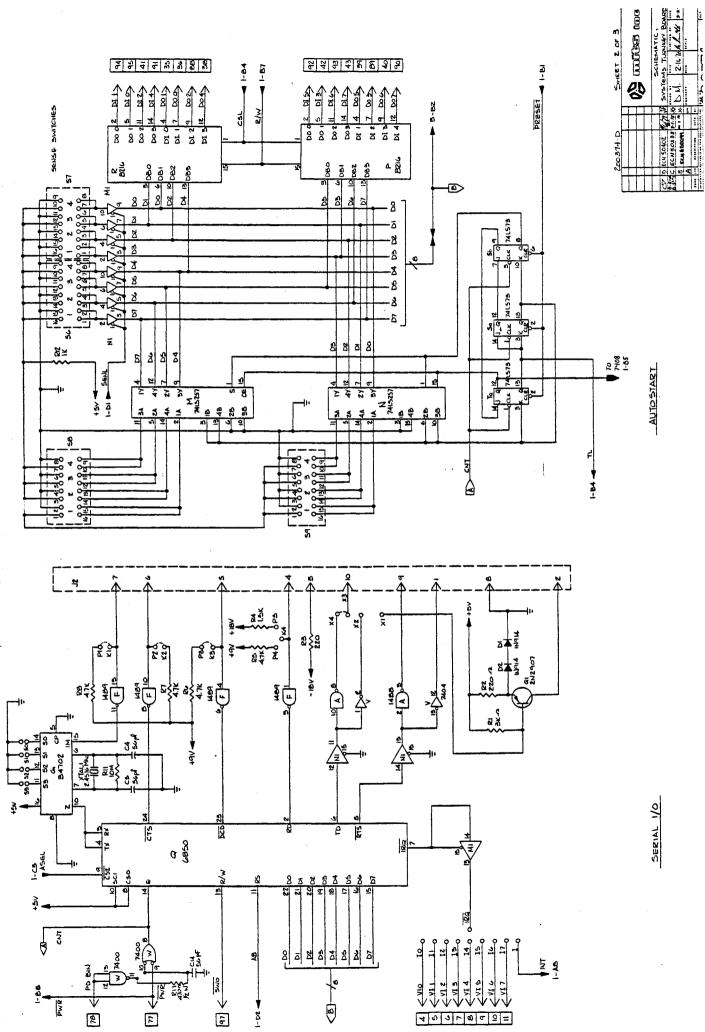

#### 2-3. The Turnkey Module

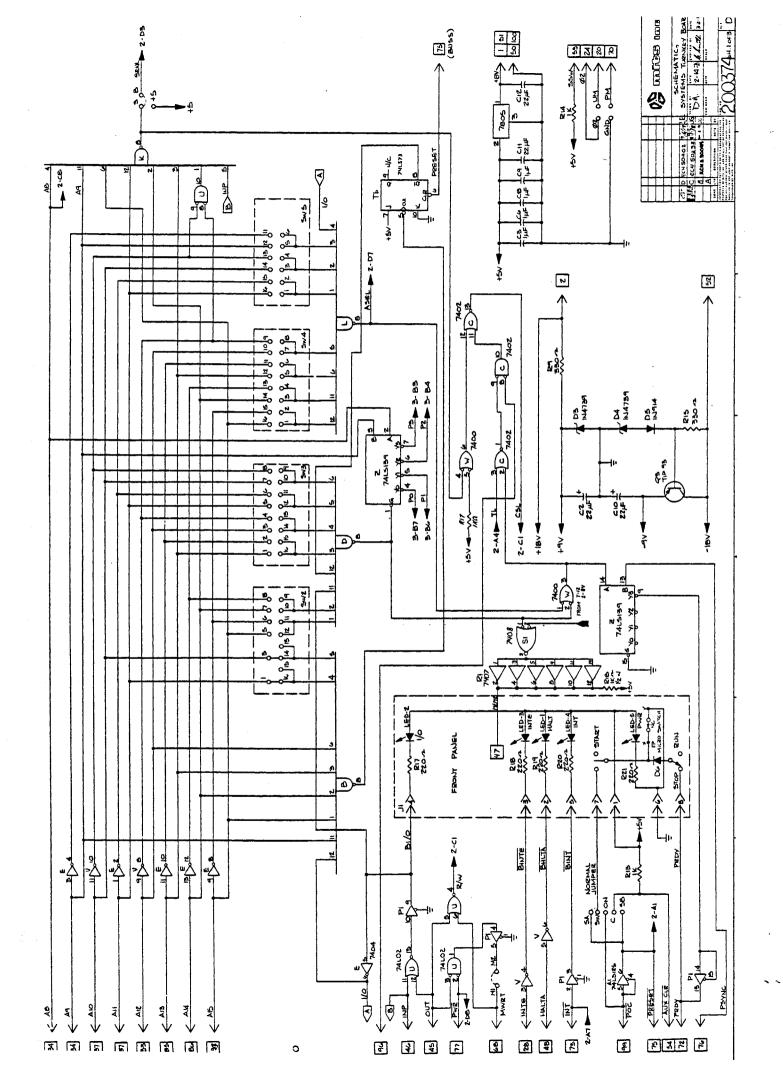

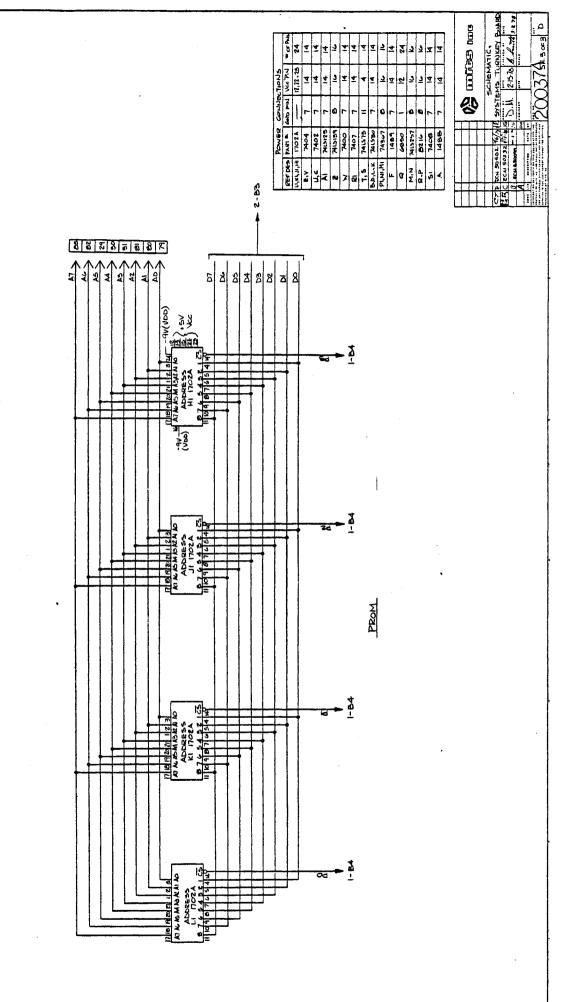

The Turnkey Module contains 1024 bytes each of RAM and PROM, a serial I/O channel, AUTO-START logic, sense switch, the front panel board and logic and miscellaneous logic. The Turnkey Module schematic is shown in Figures 2-4 a, b and c.

A. RAM and PROM. The RAM and PROM memories and their control logic are shown in the schematic diagrams, Figures 2-4 a and c.

1) The incoming PROM address is compared with the starting PROM address by the NAND gate IC D. If the incoming address is in the 1K block selected for PROM, the output of IC D, active LOW, enables the PROM address decoder, IC Za, which selects one of the PROM ICs. Up to four PROM chips may be installed. The output of IC D is also combined with the output of the I/O address detector in a NOR gate, the output of which causes the CPU to execute a WAIT state and enables the data bus interface, IC's P and R. The selected PROM drives the bidirectional data bus and the interfaces P and R put the selected data on the Data-In system bus.

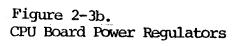

2) An address of a byte in RAM is detected by IC B. The output of IC B is active if a start sequence is not in progress and the current machine cycle is not an I/O cycle or an interrupt. Therefore, the only time a RAM address is detected is when the machine cycle is a memory cycle or a Halt cycle. The output of IC B enables the RAM ICs and the data bus interfaces P and R. The direction of the data bus is controlled by the MWRT pulse described in paragraph 2-3F. When RAM is selected, data at the address is put on the bidirectional bus. If the cycle is a memory read, the cycle is complete. If it is a write cycle, the direction of the data bus interfaces is momentarily reversed, overdriving the RAM output drivers. Pulsing the RAM write inputs then causes the data on the bus to be written in the addressed location. B. AUTO-START. The AUTO-START logic causes the computer to jump to the address designated by the AUTO-START switches when the power is turned on or the START switch is actuated. Figure 2-5 shows the arrangement of the AUTO-START logic. The switches represent the variable byte in a JMP instruction. The JMP instruction is generated by a multiplexer, ICs M and N, which is controlled by flip-flops Ta, Sa and Sb. The flip-flops are cleared by PRESET, a bus signal derived from POC or generated by the START switch on the front panel. Subsequent PDBIN pulses cause the flip-flops to change from one state to the next as shown in the sequence diagram, Figure 2-6. The pulses generated by the flip-flops cause the multiplexer to choose one of three possible bytes; 303 octal, 000 octal or byte designated by the AUTO-START switches.

Figure 2-5 AUTO-START Block Diagram

| Fi                     | lgure 2 | 2-6     |

|------------------------|---------|---------|

| Fi<br>AUTO-<br>Control | -START  | Logic   |

| Control                | State   | Diagram |

·

;

These bytes are placed on the bidirectional data bus in sequence and become the AUTO-START JMP instruction. Table 2-A shows the sequence of events in the AUTO-START procedure.

| Signal | Control |                                                                    |

|--------|---------|--------------------------------------------------------------------|

| In     | State   | Function                                                           |

| PRESET | 000     | Mux. outputs enabled, Bus interface enabled, 303 octal put on bus. |

| PDBIN  | ØTØ     | 000 put on bus.                                                    |

| PDBIN  | ØØI     | Byte in address switches put                                       |

|        |         | on the bus.                                                        |

| PDBIN  | 110     | First byte of PROM program                                         |

| PDBIN  | 111     | Next byte of PROM program                                          |

| •      | •       | •                                                                  |

| •      |         | •                                                                  |

| •      | •       | •                                                                  |

Table 2-A

During the three bytes of the JUMP instruction, the HIGH Q output of flip-flop Ta is used to drive transistor Q2 to hold MEMR low and keep memory data off the bus. Once the JUMP instruction is complete, Q goes LOW and memory instructions can be fetched.

C. Sense Switches. The sense switch circuitry is shown in Figure 2-4 a and b. IC K (Figure 2-4a) detects I/O port address 255 decimal (377 octal), which is reserved for the sense switches. The output, active LOW, enables the tri-state buffers connected to the sense switches (Figure 2-4b) putting the bits represented by the switch positions on the bidirectional bus. IC K also enables the bus interface, so the sense switch bits are placed on the Data-In system bus.

D. Serial I/O Channel (SIO). The SIO schematic is shown in Figure 2-4b. The heart of the SIO is the 685Ø Asychronous Communications Interface Adapter. The ACIA contains all the Status and Control registers discussed in section 3-2 and most of the timing and control circuitry. The bit rate is generated by a 34702 integrated circuit whose timing reference is a 2.4576 MHz crystal. Jumpers are provided to set the output rate of the 34702 at 1, 16 or 64 times the required bit rate.

Input signals are received by RS232 receivers that may be made compatible with TTL or current loop signals by means of jumper-selected pullup resistors. TTL or RS232 outputs may be selected by jumpers or by internal cable wiring.

E. Front Panel. The front panel logic is contained on the Turnkey Module board. The indicators and switches are connected to the Turnkey Module by a cable and Molex connectors. The schematic diagram for the front panel circuitry is in Figure 2-4a.

The bus signals PHLTA, PINTE and  $\overline{\text{PINT}}$  are buffered to drive the indicators HALT, INTE and INT, respectively. The I/O indicator is driven by the logical sum (OR) of the INP and OUT signals. The POWER indicator monitors the +5 volt supply on the Turnkey Module.

The bus signal PRDY is grounded when the RUN/STOP switch is in the STOP position. PRESET is grounded momentarily by the START switch which, in turn, initiates the AUTO-START sequence. Contact bounce is filtered out on the CPU board to generate a reset signal suitable for the CPU.

F. Miscellaneous Signals. Several miscellaneous signals are handled by the rest of the circuitry on the Turnkey Module. Some are optional and may be selected by jumpers.

- MWRT is generated if the jumper from M1 to M2 is installed. In the full front panel version, MWRT is generated by the front panel logic and is used by memory boards of write functions.

- 2. PROT and UNPROT are used on the standard model of the Altair 8800b for memory protect and unprotect functions. As supplied, the Turnkey Module grounds PROT and pulses UNPROT with phase 2 of the clock to unprotect all memory as it is accessed. This feature may be disabled by removing the jumpers from 2 to UM and from G to PM.

3. AUX CLR is normally pulled HIGH by a resistor on the Turnkey Modlue, but insertion of optional jumpers as described in section 3-4b allows the signal to be used.

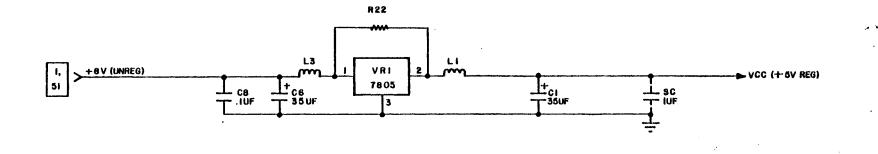

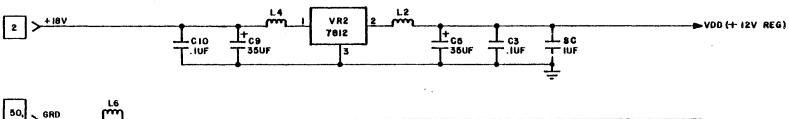

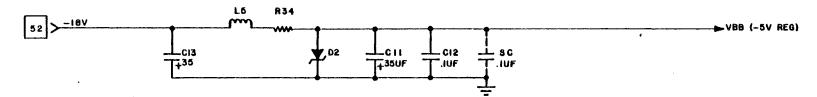

G. Power. All power used on the Turnkey Module and Front Panel boards comes from the +18 volt, -18 volt and +8 volt lines on the motherboard. The Turnkey Module's power regulator circuitry is shown in Figure 2-4a. The +5 volt supply is derived from the +8 volt line by an IC regulator. The +9 volt supply comes from the +18 volt line through a zener regulator and the -0 volt supply is derived by a transistor-zener regulator from the -18 volt line.

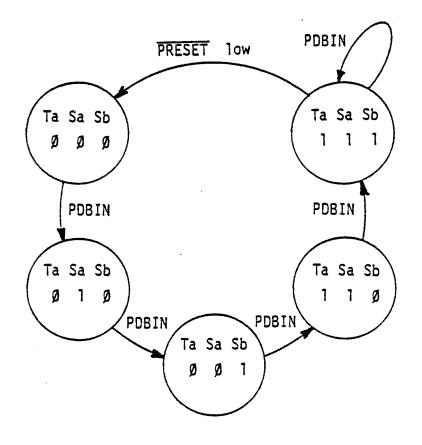

Figure 2-7 is the schematic for the power circuits in the 8800b case. The +18 and -18 volt supplies are pre-regulated. The +8 volt supply is not regulated, but it is adjusted by the taps on the secondary of the power transformer.

A780842

2

36

Power Supply Schematic

# SECTION 3 ADVANCED OPERATIONS

37/(38 Blank)

## 3. ADVANCED OPERATION

## 3-1. The Front Panel

The Front Panel contains the functional switches and status indicators for controlling and monitoring the computer. A list of the switches and indicators along with their functions follows: Power switch Turns power on and off. Key-lock switch Indicates that power is on. Monitors the +5 POWER indicator volt supply on the Turnkey Module. RUN/STOP switch Causes the computer to run the program in memory when placed in the RUN position. Execution stops in the middle of the next machine cycle after the switch is moved to the STOP position. Moving the switch back to RUN continues execution at the point where it was stopped. START switch When actuated, stops execution. When released, starts execution at the START address selected by switches on the Turnkey Module. If the switch is actuated when the RUN/STOP switch is in the STOP position, the computer stops in the middle of the START sequence. Moving RUN/STOP to RUN continues the START sequence. HALT indicator Indicates that the computer is stopped either because a HALT instruction has been executed or because the PRESET line is LOW. I/O indicator Indicates data transfer to or from an I/O port. INT indicator Indicates that an interrupt is being requested. INTE indicator Indicates that the Interrupt Enable bit is set in the CPU and that the computer may be interrupted. When the INTE indicator is off, interrupt requests have no effect.

# 3-2. The Turnkey Module

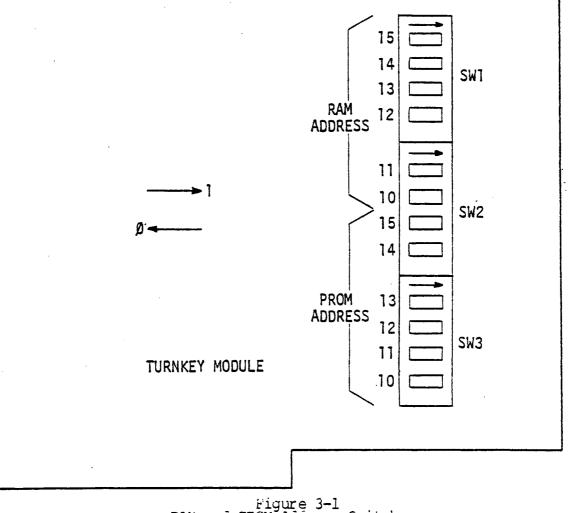

A. Memory. The Turnkey Module contains 1K bytes each of RAM and PROM. The starting address of each IK block is selected by 6 switches on the Turnkey Module board (Figure 3-1). In operation, the most significant 6 bits of the incoming address are compared with the settings of the switches. If they match, the remaining 10 bits are decoded to select the proper byte in that block.

Figure 3-1 RAM and PRCM Address Switches

To set the RAM and PROM address switches, first select the starting addresses for each block and convert them to binary. The starting addresses must be integral multiples of 1K (1024) so the low-order (rightmost) 10 bits of the addresses are zeros. The RAM and PROM addresses are zeros. The RAM and PROM addresses cannot be the same, nor may they overlap the addresses of any other memory in the system.

One starting address switch corresponds to each of the 6 high-order bits of the starting address (the most significant bit is bit 15). If the bit is one, the corresponding switch is moved in the direction of the arrow silkscreened on the board. If the bit is zero, the switch is moved in the opposite direction.

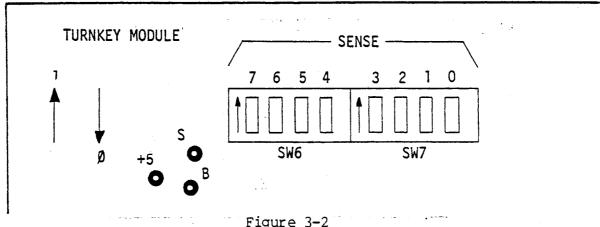

B. Sense Switches. There are eight sense switches on the Turnkey Module representing one byte of data. This byte may be read by program instructions and used as data or to select options in the program.

Sense switch settings are described in the documentation for the software products (such as Altair BASIC) that use the switches. Moving the Turnkey Module sense switches in the direction of the silkscreened arrow next to the switches is equivalent to moving a front panel switch up.

To allow use of the sense switches, there must be a jumper between points S and B on the Turnkey Module board as shown in Figure 3-2. If the Turnkey Module is being used in a standard model Altair 8800b computer, the front panel switches override the Turnkey Module sense switches. The sense switches may be read by the following instruction:

Assembly IN 255 Machine (octal) 333 377

Sense Switches and Jumper Pads

248067A

C. SIO Section.

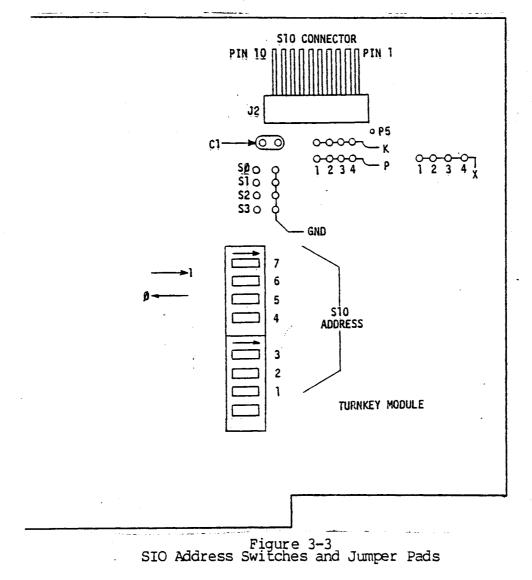

1) The Turnkey Module SIO channel appears to the CPU as two of the 256 possible I/O ports (see IMSUM, Section 3, pp. 8 -10). One of the ports is used for data transfer and the other for channel status and control information. Table 3-A is a summary description of the SIO ports.

The high-order seven bits of the I/O address are compared with the SIO address switch settings. If they match, the channel is enabled. The least significant bit selects the Data (bit zero=1) or Status/ Control (bit zero=0) port. To set the switches, convert the desired address to binary. Move each switch in the direction of the silkscreened arrow to represent one and in the opposite direction for zero. Switch 7 represents the most significant bit.

Table 3-A

| Address                                                                                                                      | Function when read during<br>an Input Operation     | Function when loaded<br>during an Output Operation |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------|--|--|--|--|--|

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                         | Receive Data Buffer<br>(Data is stripped of parity) | Transmit Data Buffer                               |  |  |  |  |  |

| s <sub>7</sub> s <sub>6</sub> s <sub>5</sub> s <sub>4</sub> s <sub>3</sub> s <sub>2</sub> s <sub>1</sub> 0                   | Status                                              | Control                                            |  |  |  |  |  |

| S <sub>1</sub> through S <sub>7</sub> refer to the binary representation of the positions of the SIO address select switches |                                                     |                                                    |  |  |  |  |  |

2) The Status Register. When the Status/Control port is read during an input operation, the Status Register contains information on the status of the Transmit Data Register, the Receive Data Register and error logic, and the peripheral/modem status inputs. The function of each bit of the status register is given in the table below.

a. Receive Data Register Full (RDRF), Bit  $\emptyset$ . Receive Data Register Full indicates that received data has been transferred to the Receive Data Register. RDRF is cleared after the CPU reads the Receive Data Register or by a master reset. The cleared or empty state indicates that the contents of the Receive Data Register are not current. RDRF also indicates empty if Data Carrier Detect is LOW.

b. Transmit Data Register Empty (TDRE), Bit 1. The Transmit Data Register Empty bit set to 1 indicates that the Transmit Data Register contents have been transferred and that new data may be entered. A zero indicates that the register is full and that transmission of a new character has not begun since the last write data command.

c. Data Carrier Detect ( $\overline{DCD}$ ), Bit 2. When the DCD input from a modem goes LOW to indicate that a carrier is not present, the Data Carrier Detect bit is set to 1. This setting causes an Interrupt Request to be generated if the Receive Interrupt Enable bit is set. After the DCD input returns HIGH,  $\overline{DCD}$  remains one until it is reset, either by reading first the Status Register and then the Data Register, or by a master reset. If the DCD input remains LOW after the Status and Data Registers have been read or a master reset occurs, the  $\overline{DCD}$  bit remains the inverse of the DCD input.

d. Clear-to-Send (CTS), Bit 3. The Clear-to-Send bit is the inverse of the Clear-to-Send input from a modem. Thus, zero in  $\overline{\text{CTS}}$  indicates that there is a Clear-to-Send from the modem. When the Clear-to-Send signal is LOW, the Transmit Data Register Empty bit is inhibited and the  $\overline{\text{CTS}}$  status bit is set to one. Master reset does not affect the  $\overline{\text{CTS}}$  bit.

e. Framing Error (FE), bit 4. A framing error occurs when the received character is improperly framed by a start and a stop bit. It is detected by the absence of the first stop bit. This indicates a synchronization error, faulty transmission or a break condition. The Framing Error flag, FE, is set during the receive data transfer time. Therefore, the error indicator is present throughout the time that the associated character is available. f. Receiver Overrun (OVRN), bit 5. OVRN is an error flag that indicates that one or more characters in the data stream were lost. That is, a character or a number of characters were received but not read from the Receive Data Register (RDR) before subsequent characters were received. The overrun condition begins at the midpoint of the last bit of the second character received without the RDR having been read. The OVRN bit is not set in the Status Register until the valid character prior to the overrun has been read. The RDRF bit remains set until OVRN is reset. The OVRN bit is reset when data is read from the Receive Data Register or by the master reset. Character synchronization is maintained during the overrun condition.

g. Parity Error (PE), bit 6. The Parity Error flag indicates that the number of ones in the character does not agree with the preselected parity. Odd parity is defined as the condition in which the total number of ones in the character is odd. Even parity means the number of ones is even. The parity error indication is present as long as the data character is in the RDR. If no parity is selected, then both the transmitter parity generator output and the receiver parity check results are inhibited.

h. Interrupt Request (IRQ), bit 7. IRQ indicates the state of the IRQ signal. Any interrupt condition, with its applicable enable, is indicated in this status bit. Anytime the IRQ signal is LOW, the IRQ bit is one to indicate the interrupt or service request status. Section 2-2.C.4. shows how to jumper the IRQ signal to an interrupt line on the bus.

3) The Control Register. When the Status/Control port is loaded during an output operation, the Control Register contains information which controls the functions of the receiver and transmitter, interrupt enables and the Request-to-Send peripheral/modem control input. The Control Register bits and their functions are shown below.

a. Counter Divide Select, bits  $\emptyset$  and 1. The Counter Divide Select Bits determine the clock divide ratios used in both the transmitter and receiver sections of the SIO. Additionally, these bits are used to provide a master reset for SIO which clears the Status Register (except for external conditions on the CTS and DCD lines) and initializes both the receiver and transmitter. Master reset does not affect other Control Register bits. Note that after power-on or a power failure/restart, these bits must be set HIGH to

reset the SIO. After reset, the clock divide ratio may be selected. The counter select bits provide for the following clock divide ratios:

| CR1 | CRØ | Ratio            |

|-----|-----|------------------|

| Ø   | Ø   | 1 (synchronized) |

| ø   | 1   | l6 (normal)      |

| 1   | Ø   | 64 (slow)        |

| 1   | 1   | master reset     |

Section 3-2.C.5. describes the use of these bits to select the baud rate.b. Word Select, bits 2, 3 and 4. The Word Select Bits are used tospecify word length, parity and the number of stop bits in each character.Word length, Parity Select, and Stop bit changes are not buffered and there-fore become effective immediately. The encoding format is as follows:

| CR4 | CR3 | CR2 | Function                          |

|-----|-----|-----|-----------------------------------|

| Ø   | Ø   | Ø   | 7 bits, even parity, 2 stop bits  |

| Ø   | ø   | 1   | 7 bits, odd parity, 2 stop bits   |

| ø   | 1   | Ø   | 7 bits, even parity, 1 stop bit   |

| Ø   | 1 1 | 1   | 7 bits, odd parity, 1 stop bit    |

| 1   | Ø   | Ø   | 8 bits, two stop bits             |

| 1   | Ø   | 1   | 8 bits, one stop bit              |

| 1   | ר   | Ø   | 8 bits, even parity, one stop bit |

| 1   | 1   | 1   | 8 bits, odd parity, one stop bit  |

c. Transmitter Control, bits 5 and 6. Two Transmitter Control Bits provide for control of the interrupt from the Transmit Data Register Empty condition, the Request-to-Send output, and the transmission of a break level (space). The setup of interrupt jumpers are shown in Section 3-2.C.4. The following coding is used:

| CR6 | CR5 | Function                                          |

|-----|-----|---------------------------------------------------|

| Ø   | Ø   | RTS = HIGH, Transmitting Interrupt disabled       |

| ø   | 1   | RTS = HIGH, Transmitting Interrupt enabled        |

| 1   | Ø   | RTS = LOW, Transmitting Interrupt disabled        |

| 1   | 1   | RTS = HIGH, transmits a break level on the trans- |

|     |     | mit data output, Transmitting disabled.           |

d. Receive Interrupt Enable, bit 7. Receive Data Register Full, Overrun and Data Carrier Detect interrupt requests are enabled by a 1 in the Receive Interrupt Enable Bit. The setup of interrupt jumpers is shown in Section 3-2.C.4.

46

248067A

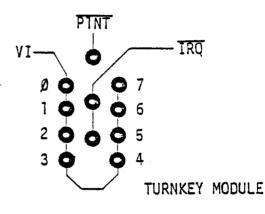

4) Interrupts. The SIO generates an interrupt signal that may be connected to an interrupt line on the bus by means of jumpers. The jumper pads are shown in Figure 3-4.

Figure 3-4 SIO Interrupt Jumper Pads

a. No jumper is installed if the SIO is not required to interrupt the CPU. Software can detect Status Register bits in this case and direct I/O operations without interrupts.

b. In systems not using the Vector Interrupt board, the signal IRQ may be connected to the PINT line. Then, if an SIO interrupt occurs, PINT will be pulled LOW until the condition that caused the interrupt no longer exists. If the Interrupt Enable bit in the CPU is set, then a RST 7 instruction is forced into the instruction sequence. Interrupt signals from other I/O circuits may also be connected to the PINT line if their outputs are effectively driven by open collector drivers. All Altair I/O boards currently manufactured and supported have open collector interrupt signal drivers. See the appropriate I/O board manual for more information.

c. In systems using the Vector Interrupt board, IRQ may be connected through a jumper to any pad marked VIØ through VI7. These represent the 8 interrupt priority levels. Interrupt signals from different boards may be connected to the same priority level if they are all driven by open collector drivers. See the Vector Interrupt board manual for further information.

5) Bit Rate Selection. In this section, 'bit rate' is defined as the maximum rate of level changes on the data signal line. Since the SIO is an asynchronous device, the bit rate determines the rate at which the bits within each character are received or sent, but not, in general, the average rate at which characters are handled.

The bit rate is selected by jumpers and by Control Register bits 1 and  $\emptyset$ . Table 3-B shows the resultant bit rate for every usable combination of jumpers and control bits. The jumpers S $\emptyset$ , S1, S2 and S3 are shown in Figure 3-3. If CR $\emptyset$  and CR1 are both zero and the external rate is not selected, then the SIO may only be used for transmission. Otherwise, the SIO may be used for both receiving and transmitting at the selected rate. If a rate above 3 $\emptyset$ 0 bits per second is selected, capacitor C1 should be removed.

If the external clock and the 1 counter are selected, then the data must be synchronized with the clock. The transmitted data line changes levels within one microsecond of the LOW to HIGH clock transition. Output jitter is about 500 ns. The SIO will sample the receive data line within 1 microsecond after the HIGH to LOW clock transition.

Table 3-B

|                                | Data Transmission Rates |    |      |                                   |                                 |                                         |  |  |

|--------------------------------|-------------------------|----|------|-----------------------------------|---------------------------------|-----------------------------------------|--|--|

| Jumpers<br>(X means installed) |                         |    | led) | CRO = 1<br>CR1 = 0<br>(normal; 16 | CR0 = 0<br>CR1 = 1<br>(slow; 64 | CRO = 0<br>CR1 = 0<br>(sychronous data; |  |  |

| S3                             | S2                      | S1 | S0   | counter selected)                 |                                 | l counter<br>selected)                  |  |  |

| -                              | -                       | -  | -    | 110                               | 27.5                            | 1760                                    |  |  |

| -                              | -                       | -  | x    | 150                               | 37.5                            | 2400                                    |  |  |

| -                              | -                       | x  | -    | 300                               | 75                              | 4800 ·                                  |  |  |

| -                              | -                       | х  | x    | 2400                              | 600                             | 38400                                   |  |  |

| -                              | x                       | -  | -    | 1200                              | 300                             | 19200                                   |  |  |

| -                              | x                       | -  | x    | 1800                              | 450                             | 28800                                   |  |  |

| -                              | x                       | x  | -    | 4800                              | 1200                            | 76800                                   |  |  |

| -                              | x                       | x  | x    | 9600                              | 2400                            | 153600                                  |  |  |

| x                              | -                       | -  | -    | 2400                              | 600                             | 38400                                   |  |  |

| x                              | -                       | -  | x    | 600                               | 150                             | 9600                                    |  |  |

| x                              | -                       | x  | -    | 200                               | 50                              | 3200                                    |  |  |

| x                              | -                       | x  | x    | 134.5                             | 33.375                          | 2152                                    |  |  |

| x                              | x                       | -  | -    | 75                                | 18.75                           | 1200                                    |  |  |

| x                              | x                       | -  | x    | 50                                | 12.5                            | 800                                     |  |  |

| x                              | x                       | x  | -    | External 16<br>rate               | External 64<br>rate             | External rate                           |  |  |

| x                              | x                       | x  | x    | (36,000 max)                      | (9000 max )                     | (400,000 max)                           |  |  |

ũ

.

.

49

:

. . . 6) Signal Types. The SIO can be configured to interface with peripheral equipment using 20 mA loop, RS232C and TTL signals. These signal options are selected by jumpers and internal cable connections. Table 3-C shows the I/O signal types. The locations of the jumpers are shown in Figure 3-3. The cable runs from the I/O connector on the Turnkey Module to the rear panel. The rear panel connector is the industry standard 25-pin data communications connector.

| Signal Type       | From    | To  | Notes                                     |

|-------------------|---------|-----|-------------------------------------------|

| TTY               | X1      | X2  |                                           |

| Compatible        | K4      | P5  |                                           |

|                   | K3      | P3  |                                           |

|                   | К2      | P2  |                                           |

| RS232             | X3      | X4  |                                           |

| Compatible        | К3      | P3  | Put in only if DCD signal is not used.    |

|                   | K2      | P2  | Put in only if CTS signal is not used     |

| TTL<br>Compatible | X2      | X3  |                                           |

| (3.2 mA max load  | K4      | P4  |                                           |

| 16 mA min drive)  | К3      | P3  |                                           |

|                   | K2      | P2  |                                           |

|                   | К1      | P1  | Not needed if external clock is not used. |

| Note: TTL inpu    | its are | two | unit loads; input is actually             |

| "TTL con          | patibl  | e." |                                           |

Table 3-C

Table 3-D shows the connections of the internal cable.

D. Interfacing. This section describes interfacing of the SIO through the 25 pin rear panel connector to modems, RS 232 terminals or current loop terminals. The terminal's instruction book should be consulted for the proper choice of signal types.

| From       | Molex            | To 25 Pin Connector |                     |                     |  |

|------------|------------------|---------------------|---------------------|---------------------|--|

| Pin Number | Function         | Female<br>TTY Cable | Male<br>RS232 Cable | Female<br>TTL Cable |  |

| 1          | TTL RTS          | 6                   |                     | 4                   |  |

| 2          | TTY XMIT         | 3                   |                     |                     |  |

| 3          | TTY REC          | 4                   |                     |                     |  |

| 4          | A11 REC          | 5                   | 2                   | 2 :                 |  |

| 5          | DCD              |                     | 8                   | 8                   |  |

| 6          | CTS              |                     | 5                   | 5                   |  |

| 7          | XTERNAL CLOCK    |                     | 15                  | 15                  |  |

| 8          | GND              | 2                   | 7                   | 7                   |  |

| 9          | RS232 RTS        |                     | 4                   |                     |  |

| 10         | RS232 + TTL XMIT |                     | 3                   | 3                   |  |

Table 3-D

1) Connection to a modem is through a male to female extension cable. The board and internal cable are set up for RS-232 I/O.

2) To connect to a Teletype, first unplug the Teletype, then loosen the three thumb-screws in the back and remove the roll of paper, the Mode Switch knob and the face plate. Remove the four screws under the nameplate and the small screw on the reader cover. The cover can now be removed.

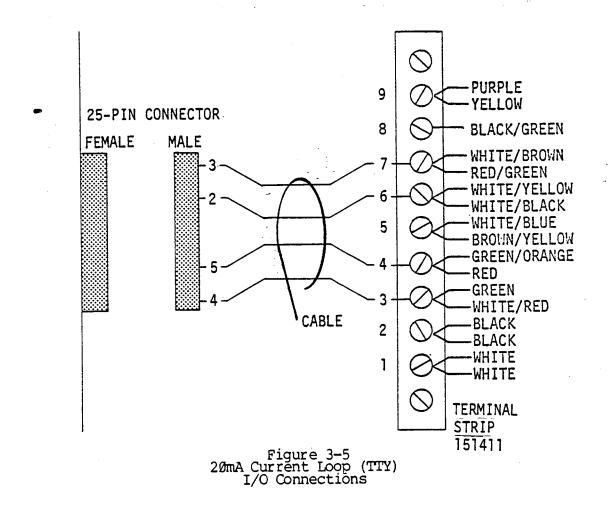

The interconnection between the computer's SIO and the Teletype is shown in Figure 3-5. Connection is made to terminal strip 1514111, which is at the right rear of the Teletype.

While the cover is off, check that the Teletype is wired for 2pmA, full duplex operation. The unit is set for full duplex if the Brown/Yellow wire is on terminal 5 and not on 3, and the White/Blue wire is on terminal 5 and not on 4 of terminal strip 1514111. The receiver current level is set to 2pmA if the Purple wire is connected to terminal 9 and not to 8. The correct connections are shown in Figure 3-5. The current source resistance for local mode should be connected as 145p ohms. This resistor is on the right hand side of the Teletype, halfway back.

After the connections and modifications are made, replace the cover, faceplate, knobs, paper roll and screws.

Be sure that the Turnkey Module and the internal cable have been set up for TTY I/0.

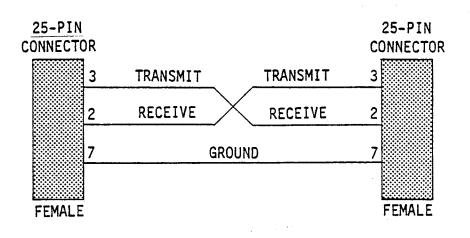

3) For RS-232 input/output, the cable is wired as shown in Figure 3-6. Note that the cable is symmetrical. The SIO of the Turnkey Module and the internal cable must be set up for RS-232 I/O.

Figure 3-6 RS-232 I/O Connections

# 3-3. AUTO-START

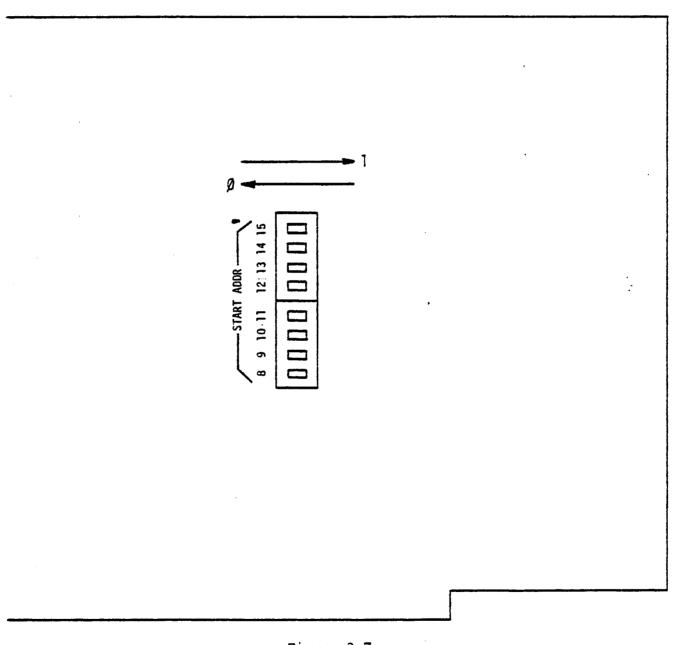

When power is turned on, or when the START switch is released, the start sequence logic forces the CPU to begin executing instructions at an address selected by a set of switches on the Turnkey Module. The switches are shown in Figure 3-7.

Figure 3-7 AUTO-START Address Switches

The AUTO-START switches are set in the same manner as the RAM and PROM address switches (see section 3-1). The AUTO-START address is the address of the first location of a routine in PROM. The address must be an integral multiple of 256, so the low order eight bits must be zeros. The eight AUTO-START switches correspond to the high-order eight bits of the AUTO-START address. Bit 8 is the least significant bit.

If the 8800b Turnkey Monitor PROM is installed, the AUTO-START address must be 176400 octal. Therefore, all the AUTO-START switches except switch 9 must be in the "1" position.

3-4. Miscellaneous Options

A. Use of Turnkey Module with Front Panel Model. The Turnkey Module may be used in the standard (full front panel) model of the Altair 8800b computer. To do this, the following jumpers must be removed from the Turnkey Module board:

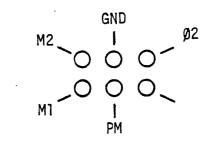

> M1 to M2 PM to GND Ø2 to UM

Figure 3-8 shows these jumpers.

Section 3-8 Miscellaneous Option Jumper Pads

Table 3-E

| Configuration J                                                                                                 | umpers    | Course         |               |

|-----------------------------------------------------------------------------------------------------------------|-----------|----------------|---------------|

|                                                                                                                 | umpers    | Cause          | Effect        |

| Normal S                                                                                                        | A to SW   | Power On       | POC pulse     |

|                                                                                                                 |           |                | START         |

|                                                                                                                 |           | START switch   | START         |

| Alternate #1 S                                                                                                  | SA to SW  | Power On       | POC pulse     |

| S                                                                                                               | B to C    |                | START         |

|                                                                                                                 |           |                | AUX CLR pulse |

|                                                                                                                 |           | START switch   | START         |

|                                                                                                                 |           |                | AUX CLR pulse |

| Alternate #2 0                                                                                                  | DN to SW  | Power On       | POC pulse     |

|                                                                                                                 |           | •              | START         |

|                                                                                                                 |           | START switch   | POC pulse     |

|                                                                                                                 |           |                | START         |

| Alternate #3 (                                                                                                  | DN to SW  | Power On       | POC pulse     |

| l s                                                                                                             | SB to C   |                | START         |

|                                                                                                                 | _ · · · · |                | AUX CLR pulse |

|                                                                                                                 |           | START switch   | POC pulse     |

|                                                                                                                 |           |                | START         |

|                                                                                                                 |           |                | AUX CLR pulse |

| Alternate #4                                                                                                    | SA to SW  | Power On       | POC pulse     |

|                                                                                                                 | DN to C   |                | START         |

| and the state of the |           | and the second | AUX CLR pulse |

|                                                                                                                 |           | START switch   | START         |

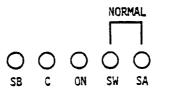

B. POC and AUX CLR options. As supplied, the computer generates the POC pulse when the power is turned on, but does not generate the AUX CLR pulse. This may be changed by jumpers between the pads marked C, ON, SA, SB and SW. These pads are shown in figure 3-8. Table 3-E shows the options available. The AUX CLR pulse is generated by a panel switch on the standard model of the 8800b computer and may be used by peripheral devices.

# 3-5. The Power Supply

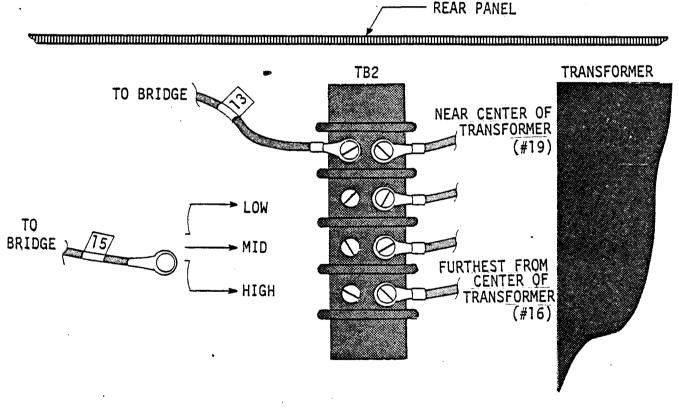

A. Adjusting for differing loads. The +18 and -18 volt supplies are pre-regulated, but the +8 volt supply must be adjusted for differing loads by moving the tap on the power transformer secondary. The transformer secondary taps are shown in Figure 3-9. The correct secondary tap

Figure 3-9 Power Transformer Secondary Taps

57 ′

is determined experimentally. The procedure for adjusting the tap is as follows:

- 1. Disconnect the computer from its A.C. supply.

- Connect wire 15 from the bridge rectifier to one of the secondary taps on the transformer as shown below:

| Number of Boards | Transformer |  |  |

|------------------|-------------|--|--|

| in the Computer  | Тар         |  |  |

| Ø-6              | low         |  |  |